(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018933C1 |

| Устройство для деления | 1991 |

|

SU1783523A1 |

| Устройство для деления | 1986 |

|

SU1357947A1 |

| Устройство для деления | 1985 |

|

SU1357946A1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

| Устройство для деления | 1985 |

|

SU1322264A1 |

| Устройство для деления | 1988 |

|

SU1520510A1 |

| Устройство для деления | 1986 |

|

SU1390608A1 |

| УСТРОЙСТВО ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 2012 |

|

RU2510072C1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

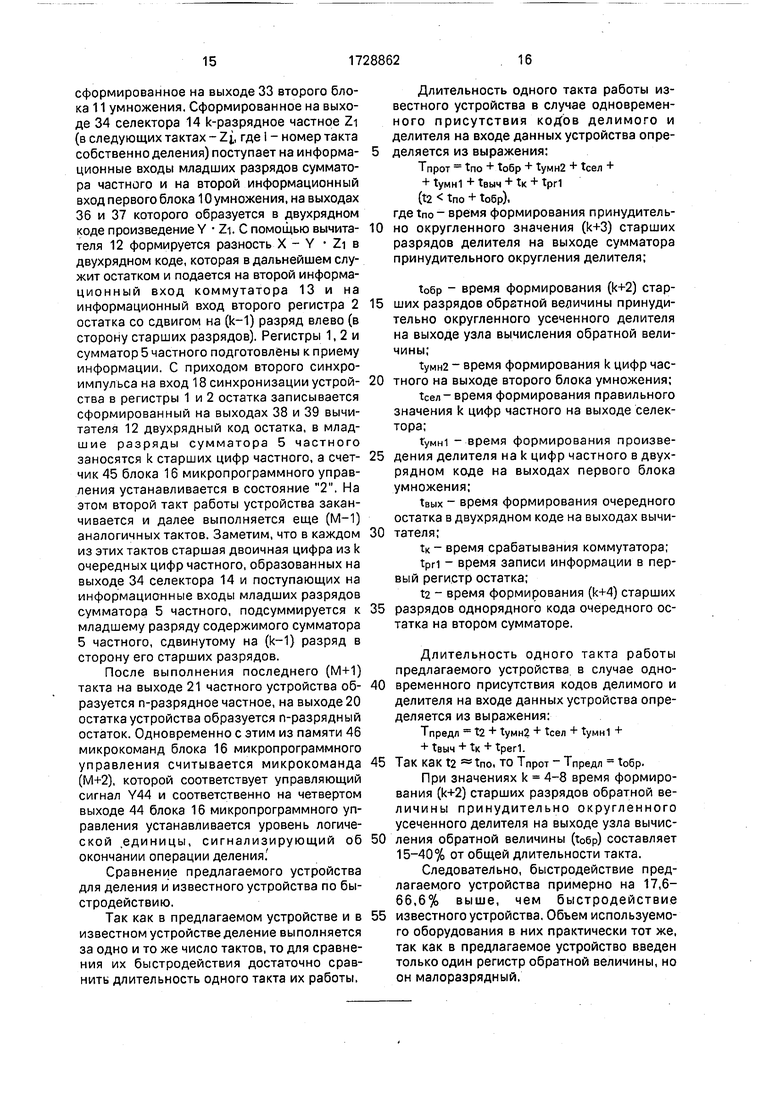

Изобретение относится к вычислительной технике и может быть использовано в быстродействующих арифметических устройствах для выполнения операции деления чисел. Целью изобретения является повышение быстродействия устройства путем сокращения длительности такта форми- рования цифр частного. Устройство содержит два регистра 1 и 2 остатка, регистр 3 делителя, сумматор 5 частного, сумматор 6 принудительного округления делителя, узел 7 вычисления обратной величины, два сумматора 8 и 9, два блока 10 и 11 умножения, вычитатель 12, коммутатор 13, селектор 14, элемент НЕ 15, блок 16 микропрограммного управления и введенный регистр 4 обратной величины. 3 ил.

го

00 00

о

го

Изобретение относится к вычислительной технике и может быть применено в быстродействующих арифметических устройствах для выполнения операции деления чисел.

Известно устройство для деления, формирующее в каждом такте k цифр частного

(где ,n- разрядность делимого

и делителя, х - ближайшее целое, большее или равное х), содержащее регистр делимого, регистр делителя, сумматор частного, сумматор принудительного округления делителя, блок деления усеченных чисел, блок умножения, сумматор, вычитатель, коммутатор и блок управления.

Недостатком этого устройства является низкое быстродействие, вызванное большой длительностью такта формирования k цифр частного и остатка.

Известно устройство для деления, формирующее в каждом такте k цифр частного

(где ,n- разрядность делимого

и делителя) и содержащее первый регистр остатка, второй регистр остатка, регистр делителя, сумматор частного, сумматор принудительного округления делителя, узел вычисления обратной величины, два сумматора, два блока умножения, вычитатель, элемент И-НЕ, два коммутатора и блок микропрограммного управления.

Быстродействие этого устройства недостаточно высокое из-за относительно большой длительности такта.

Наиболее близким по технической сущности к предлагаемому изобретению является устройство для деления, формирующее в каждом такте k цифр частного (где 2 k - ,

п - разрядность делимого и делителя) и содержащее два регистра остатка, регистр де- лителя, сумматор частного, сумматор принудительного округления, узел вычисления обратной величины, два сумматора, два блока умножения, коммутатор, селектор, вычитатель и блок микропрограммного управления, причем вход данных устройства соединен с информационным входом регистра делителя и с первым информационным входом коммутатора, выход которого соединен с информационным входом первого регистра остатка, выходы первого и второго регистров остатка соединены с первым и вторым информационными входами первого сумматора соответственно, выход которого является выходом остатка устройства и соединен с входом уменьшаемого вычита- теля, входы вычитаемого и заема которого соединены с выходами первой и второй групп первого блока умножения соответственно, первый информационный вход первого блока.умножения соединен с выходом регистра делителя, выходы разности и заема вычитателя соединены с вторым информационным входом коммутатора и информационным входом второго регистра остатка соответственно, выходы старших разрядов первого и второго регистров остатка соединены с первым и вторым инфор0 мационными входами второго сумматора соответственно, выход младших разрядов которого соединен с первым информационным входом второго блока умножения, выход старшего разряда второго сумматора

5 соединен с входом элемента НЕ, выход которого соединен с управляющим входом селектора, информационный вход которого соединен с выходом второго блока умножения, выход селектора соединен с информа0 ционным входом младших разрядов сумматора частного и с вторым, информационным входом первого блока умножения, выход старших разрядов регистра делителя соединен с информационным входом сум5 матора принудительного округления делителя, вход переноса которого соединен с входом логической единицы устройства, выход сумматора принудительного округления делителя соединен с информационным вхо0 дом узла вычисления обратной величины, выход которого соединен с вторым информационным входом второго блока умножения, вход синхронизации устройства соединен с синхровходами первого и второ5 го регистров остатка, регистра делителя, сумматора частного и блока микропрограммного управления, первый выход которого соединен с первым управляющим входом коммутатора и входами установки в нуль

0 второго регистра остатка и сумматора частного, выход которого является выходом частного устройстве, второй выход блока микропрограммного управления соединен с вторым управляющим входом коммутатора

5 и входами разрешения записи второго регистра остатка и сумматора частного, третий и четвертый выходы блока микропрограммного управления соединены с входами разрешения записи первого регистра остатка и

0 регистра делителя соответственно, пятый выход блока микропрограммного управления является выходом признака окончания деления устройства.

Недостаток известного устройства - от5 носительно низкое быстродействие, вызванное большой длительностью такта формирования k цифр частного в случае, когда на входе данных устройства одновременно находятся n-разрядные двоичные коды делимого X и делителя Y и загружаются

в первый регистр остатка и регистр делителя одновременно.

Цель изобретения - повышение быстродействия устройства путем сокращения длительности такта формирования к цифр частного при одновременной загрузке операндов в первый регистр остатка и регистр делителя.

Поставленная цель достигается тем, что в устройство для деления, содержащее два регистра остатка, регистр делителя, сумматор частного, сумматор принудительного округления делителя, узел вычисления обратной величины, два сумматора, два блока умножения, коммутатор, селектор, вычита- тель и блок микропрограммного управления, причем вход данных устройства соединен с информационным входом регистра делителя и с первым информационным входом коммутатора, выход которого соединен с информационным входом первого регистра остатка, выходы первого и второго регистров остатка соединены с первым и вторым информационными входами первого сумматора соответственно, выход которого является выходом остатка устройства и соединен с входом уменьшаемого вычита- теля, входы вычитаемого и заема которогр соединены с выходами первой и второй групп первого блока умножения соответственно, первый информационный вход первого блока умножения соединен с выходом регистра делителя, выходы разности и заема вычитателя соединены с вторым информационным входом коммутатора и информационным входом второго регистра остатка соответственно, выходы старших разрядов первого и второго регистров остатка соединены с первым и вторым информационными входами второго сумматора соответственно, выход младших разрядов которого соединен с первым информационным входом второго блока умножения, выход старшего разряда второго сумматора соединен с входом элемента НЕ, выход которого соединен с управляющим входом селектора, информационный вход которого соединен с выходом второго блока умножения, выход селектора соединен с информационным входом младших разрядов сумматора частного и с вторым информационным входом первого блока умножения, вход логической единицы устройства соединен с входом переноса сумматора принудительного округления делителя, выход которого соединен с входом узла вычисления обратной величины, вход синхронизации устройства соединен с синхровходами первого и второго регистров остатка, регистра делителя, сумматора частного и блока

микропрограммного управления, первый выход которого соединен с входом разрешения записи регистра делителя, с первым управляющим входом коммутатора и входами

установки в нуль второго регистра остатка и сумматора частного, выход которого является выходом частного устройства, второй выход блока микропрограммного управления соединен с вторым управляющим входом

0 коммутатора и входами разрешения записи второго регистра остатка и сумматора частного, третий выход блока микропрограммного управления соединен с входом разрешения записи первого регистра остат5 ка, четвертый выход блока микропрограммного управления является выходом признака окончания деления устройства, введен регистр обратной величины, выход которого соединен с вторым информацион0 ным входом второго блока умножения, выход узла вычисления обратной величины соединен с информационным входом регистра обратной величины, вход разрешения записи и синхровход которого соединены с

5 входом разрешения записи и синхровходом регистра делителя соответственно, выход старших разрядов делителя входа данных устройства соединен с информационным входом сумматора принудительного округ0 ления делителя.

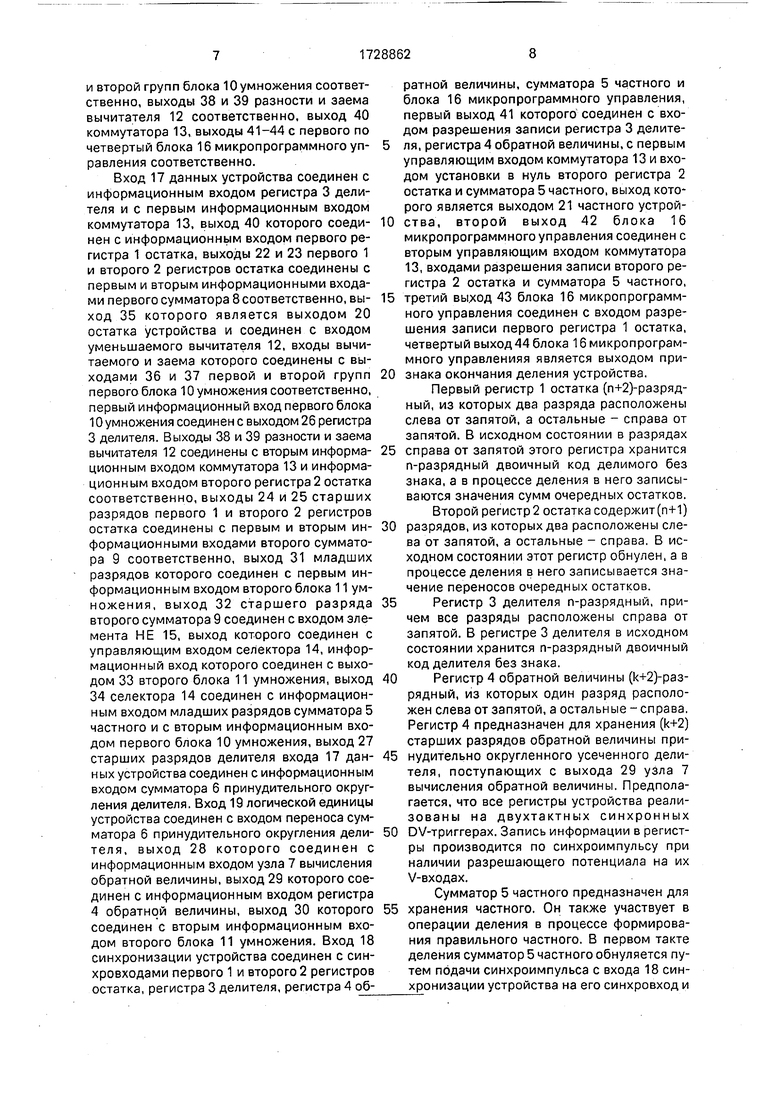

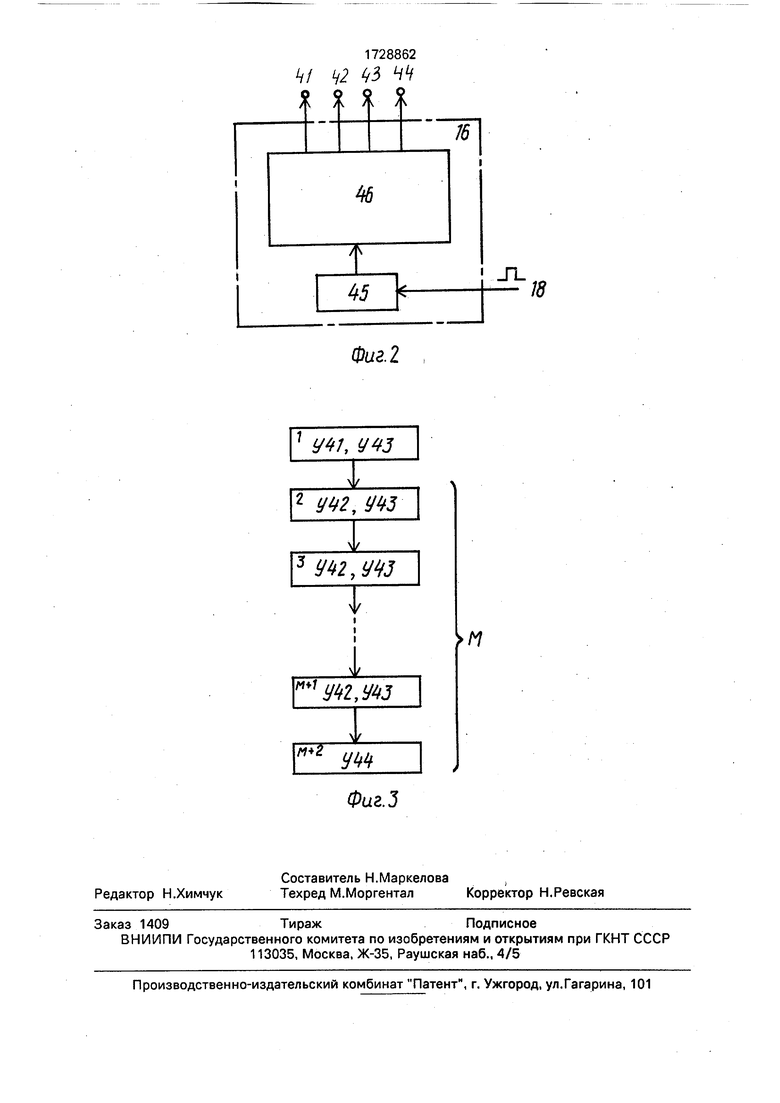

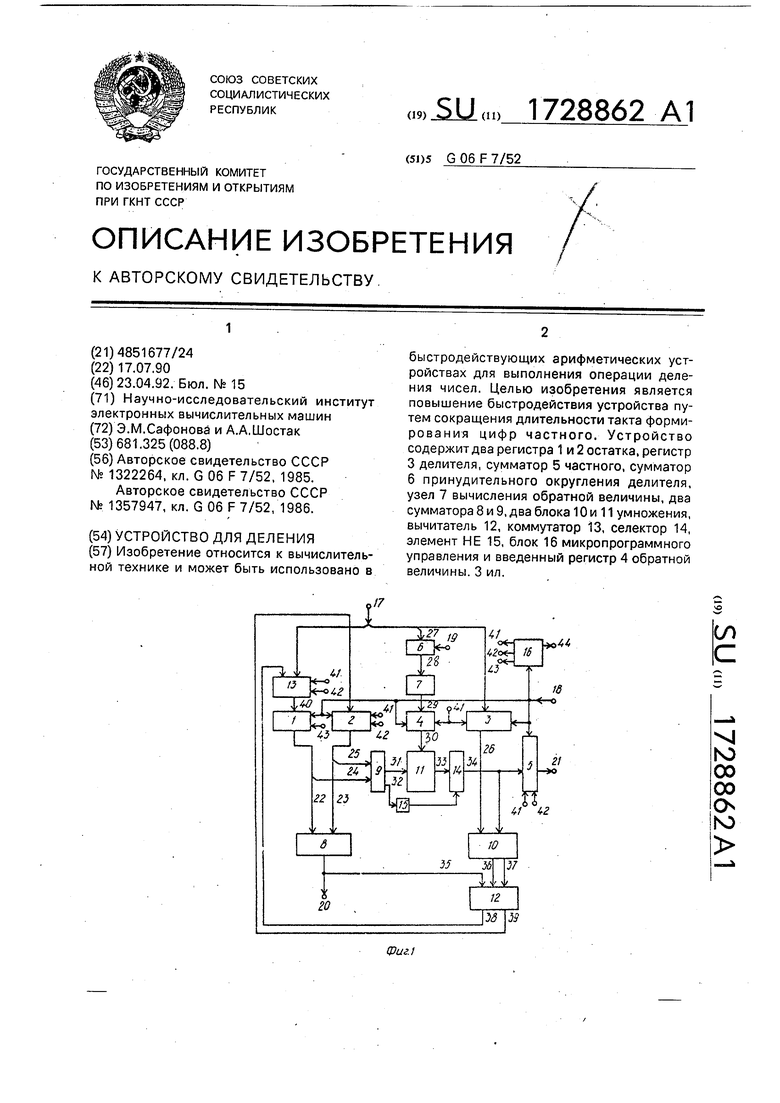

На фиг.1 приведена структурная схема предлагаемого устройства для деления; на фиг.2 -функциональная схема блока микропрограммного управления; на фиг.З - мик5 ропрограмма работы устройства.

Устройство для деления содержит (фиг.1) первый 1 и второй 2 регистры остатка, регистр 3 делителя, регистр 4 обратной величины сумматор 5 частного, сумматор 6

0 принудительного округления делителя, узел 7 вычисления обратной величины, первый и второй сумматоры 8 и 9 соответственно, первый и второй блоки 10 и 11 умножения соответственно, вычитатель 12, коммутатор

5 13, селектор 14, элемент НЕ 15, блок 16 микропрограммного управления, вход 17 данных устройства, вход418 синхронизации устройства, вход 19 логической единицы устройства, выходы 20 и 21 остатка и частного

0 устройства, выходы 22 и 23 регистров 1. и 2, выходы 24 и 25 старших разрядов регистров 1 и 2, выход 26 регистра 3, выход 27 старших разрядов делителя входа 17 данных устройства, выход 28 сумматора 6, выход 29 узла 7

5 вычисления обратной величины, выход 30 регистра 4, выходы 31 и 32 младших разрядов и старшего разряда сумматора 9 соответственно, выход 33 второго блока 11 умножения, выход 34 селектора 14, выход 35 первого сумматора 8, выходы 36 и 37 первой

и второй групп блока 10 умножения соответственно, выходы 38 и 39 разности и заема вычитателя 12 соответственно, выход 40 коммутатора 13, выходы 41-44 с первого по четвертый блока 16 микропрограммного управления соответственно.

Вход 17 данных устройства соединен с информационным входом регистра 3 делителя и с первым информационным входом коммутатора 13, выход 40 которого соединен с информационным входом первого регистра 1 остатка, выходы 22 и 23 первого 1 и второго 2 регистров остатка соединены с первым и вторым информационными входами первого сумматора 8 соответственно, выход 35 которого является выходом 20 остатка устройства и соединен с входом уменьшаемого вычитателя 12, входы вычитаемого и заема которого соединены с выходами 36 и 37 первой и второй групп первого блока 10 умножения соответственно, первый информационный вход первого блока 10 умножения соединен с выходом 26 регистра

3делителя. Выходы 38 и 39 разности и заема вычитателя 12 соединены с вторым информационным входом коммутатора 13 и информационным входом второго регистра 2 остатка соответственно, выходы 24 и 25 старших разрядов первого 1 и второго 2 регистров остатка соединены с первым и вторым информационными входами второго сумматора 9 соответственно, выход 31 младших разрядов которого соединен с первым информационным входом второго блока 11 умножения, выход 32 старшего разряда второго сумматора 9 соединен с входом элемента НЕ 15, выход которого соединен с управляющим входом селектора 14, информационный вход которого соединен с выходом 33 второго блока 11 умножения, выход 34 селектора 14 соединен с информационным входом младших разрядов сумматора 5 частного и с вторым информационным входом первого блока 10 умножения, выход 27 старших разрядов делителя входа 17 данных устройства соединен с информационным входом сумматора 6 принудительного округления делителя. Вход 19 логической единицы устройства соединен с входом переноса сумматора 6 принудительного округления делителя, выход 28 которого соединен с информационным входом узла 7 вычисления обратной величины, выход 29 которого соединен с информационным входом регистра

4обратной величины, выход 30 которого соединен с вторым информационным входом второго блока 11 умножения. Вход 18 синхронизации устройства соединен с син- хровходами первого 1 и второго 2 регистров остатка, регистра 3 делителя, регистра 4 обратной величины, сумматора 5 частного и блока 16 микропрограммного управления, первый выход 41 которого соединен с входом разрешения записи регистра 3 делителя, регистра 4 обратной величины, с первым управляющим входом коммутатора 13 и входом установки в нуль второго регистра 2 остатка и сумматора 5 частного, выход которого является выходом 21 частного устрой0 ства, второй выход 42 блока 16 микропрограммного управления соединен с вторым управляющим входом коммутатора 13, входами разрешения записи второго регистра 2 остатка и сумматора 5 частного,

5 третий выход 43 блока 16 микропрограммного управления соединен с входом разрешения записи первого регистра 1 остатка, четвертый выход 44 блока 16 микропрограммного управленияя является выходом при0 знака окончания деления устройства.

Первый регистр 1 остатка (п+2)-разряд- ный, из которых два разряда расположены слева от запятой, а остальные - справа от запятой. В исходном состоянии в разрядах

5 справа от запятой этого регистра хранится n-разрядный двоичный код делимого без знака, а в процессе деления в него записываются значения сумм очередных остатков. Второй регистр 2 остатка содержит (п+1)

0 разрядов, из которых два расположены слева от запятой, а остальные - справа. В исходном состоянии этот регистр обнулен, а в процессе деления в него записывается значение переносов очередных остатков.

5 Регистр 3 делителя n-разрядный, причем все разряды расположены справа от запятой. В регистре 3 делителя в исходном состоянии хранится n-разрядный двоичный код делителя без знака.

0 Регистр 4 обратной величины (к+2)-раз- рядный, из которых один разряд расположен слева от запятой, а остальные - справа. Регистр 4 предназначен для хранения (k+2) старших разрядов обратной величины при5 нудительно округленного усеченного делителя, поступающих с выхода 29 узла 7 вычисления обратной величины. Предполагается, что все регистры устройства реализованы на двухтактных синхронных

0 DV-триггерах. Запись информации в регистры производится по синхроимпульсу при наличии разрешающего потенциала на их V-входах.

Сумматор 5 частного предназначен для

5 хранения частного. Он также участвует в операции деления в процессе формирования правильного частного. В первом такте деления сумматор 5 частного обнуляется путем подачи синхроимпульса с входа 18 син- хронизации устройства на его синхровход и

разрешающего потенциала с первого выхо- да41 блока 16 микропрограммного управления на вход разрешения установки в нуль сумматора 5 частного. Во всех остальных тактах работы устройства в сумматоре 5 частного накапливается значение частного. Для этого к значению частного, сформированному на предыдущих тактах работы устройства и сдвинутому на (k-1) разряд влево (в сторону старших разрядов), прибавляется значение к цифр частного, сформированных на выходе 34 селектора 14 в текущем такте. Запись информации в сумматор 5 частного также осуществляется по синхроимпульсу при наличии разрешающего потенциала на его входе разрешения записи, который подключен к второму выходу 42 блока 16 микропрограммного управления. После завершения деления образованное в сумматоре 5 частное поступает на выход 21 частного устройства. Сумматор частного реализован так же, как и в известном устройстве, т.е. на комбинационном сумматоре и регистре.

Формирование k цифр частного в каждом такте работы устройства для деления производится путем умножения однорядного кода усеченного остатка, сформированного на выходе 31 младших разрядов второго сумматора 9, на значение старших разрядов обратной величины усеченного делителя, хранимое в регистре 4 обратной величины и подаваемое с выходов 30 регистра 4 обратной величины. Чтобы устранить возможность поступления в устройстве k цифр частного с избытком, значение старших разрядов делителя, поступающее с выхода 27 входа 17 данных устройства, увеличивается на единицу младшего разряда в сумматоре 6 принудительного округления делителя.

Пусть делимое X и делитель Y есть нормализованные двоичные дроби, т.е. 1/2 X 1 и 1 /2 Y 1. Это справедливо только в первом такте деления. В дальнейшем, когда в роли делимого выступают промежуточные остатки, возможно нарушение нормализации делимого как влево, так и вправо. В общем случае делимое X в предлагаемом устройстве может изменяться в пределах 0 X 2Y. Можно показать, что для получения на выходе 34 селектора 14 k двоичных цифр частного с точностью до единицы их младшего разряда достаточно обрабатывать (k+4) старших разрядов делимого (один разряд расположен слева от запятой, а остальные - справа от запятой), (k+З) старших разрядов делителя Y (все разряды расположены справа от запятой) и (k+2) старших разрядов обратной величины

принудительно округленного усеченного де- лителя (один разряд расположен слева от запятой, а остальные - справа от запятой). Сумматор 6 (к+3)-разрядный комбина5 ционного типа. В сумматоре 6 осуществляется принудительное округление делителя путем прибавления к значению (k+З) старших разрядов делителя, поступающих на информационный вход сумматора 6 с выхо0 да 27 входа 17 данных устройства, единицы в младший разряд, поступающей на вход переноса сумматора 6 принудительного округления делителя через вход 19 логической единицы устройства. На выходе 28 суммато5 ра 6 принудительного округления делителя образуется (к+4)-разрядный результат (один разряд расположен слева от запятой, а остальные - справа от запятой), который далее поступает на вход узла 7 вычисления обрат0 ной величины.

Узел 7 вычисления обратной величины производит вычисление значения (k+2) старших разрядов обратной величины от принудительно округленного значения (k+З)

5 старших разрядов делителя, поступающего на вход узла 7 вычисления обратной величины с выхода 28 сумматора 6 принудительного округления делителя. На выходе 29 узла 7 вычисления обратной величины формиру0 ется значение (k+2) старших разрядов обратной величины принудительно округленного усеченного делителя. Узел 7 может быть выполнен в виде комбинационной схемы, реализующей метод деления

5 Стефанелли, или же совместно с сумматором 6 на ПЗУ по соответствующей таблице истинности,

С помощью первого сумматора 8 комбинационного типа двухрядный код остатка, 0 хранимый в первом 1 и втором 2 регистрах остатка, преобразуется в однорядный код.

Второй сумматор 9 комбинационного типа осуществляет преобразование (k+5) старших разрядов двухрядного кода остат5 ка, хранимого в регистрах 1 и 2 остатка, в однорядный код (два разряда расположены слева от запятой и (k+З) разряда - справа от запятой). На выходе 31 младших разрядов второго сумматора 9 образуется одноряд0 ный код (k+4) старших разрядов остатка (один разряд - слева от запятой, (k+З) разрядов - справа от запятой), а на выходе 32 старшего разряда второго сумматора 9 образуется старший дополнительный разряд

5 остатка.

В первом блоке 10 умножения осуществляется перемножение k-разрядного частного, сформированного на выходах 34 селектора 14 и поступающего на второй ий- формационный вход первого блока 10 умножения, и значения n-разрядного делителя, хранимого в регистре 3 делителя и поступающего на первый информационный вход блока 10с выхода 26 регистра 3 делителя. На выходах 36 и 37 первой и второй групп первого блока 10 умножения образуется произведение в двухрядном коде (в виде двух чисел). Первый блок 10 умножения - комбинационного типа - может быть разработан хорошо известными методами, на- пример в виде многослойной структуры без распространения переносов внутри слоев. Он также может быть реализован в виде совокупности из n/k k-разрядных двоичных умножителей.

Во втором блоке 11 умножения производится умножение значения однорядного кода (к+4) старших разрядов остатка, поступающего на его первый информационный вход с выхода 31 младших разрядов второго сумматора 9, на значение (к+2) старших разрядов обратной величины принудительно округленного усеченного делителя, поступающее на его второй информационный вход с выхода 30 регистра 4 обратной вели- чины. На выходе 33 второго блока 11 умножения формируется значение к цифр частного. Значение k-разрядного частного, полученного на выходах 34 селектора 14, может быть либо равно значению старших к разрядов частного, получаемого при делении n-разрядных чисел, либо меньше его на единицу младшего разряда с весом 2. Второй блок 11 умножения - комбинационного типа - может быть разработан хорошо изве- стными методами, например в виде многослойной структуры с распространением переноса только в последнем слое.

В вычитателе 12 осуществляется вычи- тание из текущего остатка, сформированного в однорядном коде на выходе 35 первого сумматора 8, произведения делителя на k цифр частного, образованного в двухрядном коде на выходах 36 и 37 первой и второй групп первого блока 10 умножения. Результат этого вычитания является очередным остатком и получается на выходах 38 и 39 разности и заема вычитателя 12 в двухрядном к-оде. Вычитатель 12 - комбинационно- го типа без распространения заема, он может быть реализован как на одноразрядных двоичных вычитателях, так и на одноразрядных двоичных сумматорах. В предлагаемом устройстве предполагается, что вычитатель 12 реализован на одноразрядных двоичных сумматорах и на выходах 38 и 39 формируется остаток в двухрядном коде в виде суммы и переноса. Для этого необходимо информацию, поступающую на

его входы с выходов 36 и 37 первой и второй групп первого блока 10 умножения, проин- вертировать с добавлением единиц в соответствующие весовые позиции (для перевода обратного-кода в дополнительный).

С помощью коммутатора 13 осуществляется передача на информационные входы первого регистра 1 остатка либо делимого с входа 17 данных устройства, когда на первом выходе 41 блока 16 микропрограммного управления формируется сигнал логической единицы, либо результата, образованного на выходе 38 разности вычитателя 12, когда на втором выходе 42 блока 16 микропрограммного управления формируется сигнал логической единицы. Коммутатор 13 может быть реализован на элементах 2И-2ИЛИ. Так как в предлагаемом устройстве при формировании k цифр частного используются старшие разряды остатка, полученные при приведении на втором сумматоре 9 к однорядному коду старших разрядов двухрядного кода остатка, то возможно образование неправильного значения k цифр частного. Так, если значение старших разрядов приведенного остатка, полученного на выходах 35 первого сумматора 8, равно нулю, то при формировании однорядного кода старших разрядов остатка путем сложения на втором сумматоре 9 старших разрядов двухрядного кода остатка возможно получение значения суммы на выходе31 младших разрядов сумматора 9 меньшего, чем нуль на единицу младшего разряда, т.е. значения 1,11...1. Но

Ч-с-

в этом случае на выходе 32 старшего разряда второго сумматора 9 формируется логическая единица, а в случае, если значение старших разрядов приведенного остатка, полученного на выходе 35 первого сумматора 8, не равно нулю, на выходе 32 старшего разряда второго сумматора 9 формируется логический нуль. Для исключения возможности получения в первом случае неверного значения k цифр частного в устройстве предусмотрена блокировка (формирование значения k цифр частного, равного нулю) k цифр частного, полученных на выходах 33 второго блока 11 умножения, путем подачи на управляющий вход селектора 14 уровня логического нуля с выхода элемента НЕ 15. Уровень логического нуля на его выходе устанавливается в том случае, если на выходе 32 старшего разряда второго сумматора 9. устанавливается уровень логической единицы. Во всех других случаях на выход 34 селектора 14 пропускается значение k цифр частного с выхода 33 второго блока 11 умножения.

Селектор 14 производит формирование на выходе 34 значения k цифр частного, равного нулю, если на его управляющем входе присутствует сигнал логического нуля или же пропускает на выход 34 значение k цифр частного с выхода 33 второго блока 11 умножения. Селектор 14 реализован также, как и в известном устройстве, т.е. содержит k двухвходовых элементов И, имеющих один общий вход, служащий в качестве управля- ющего входа.

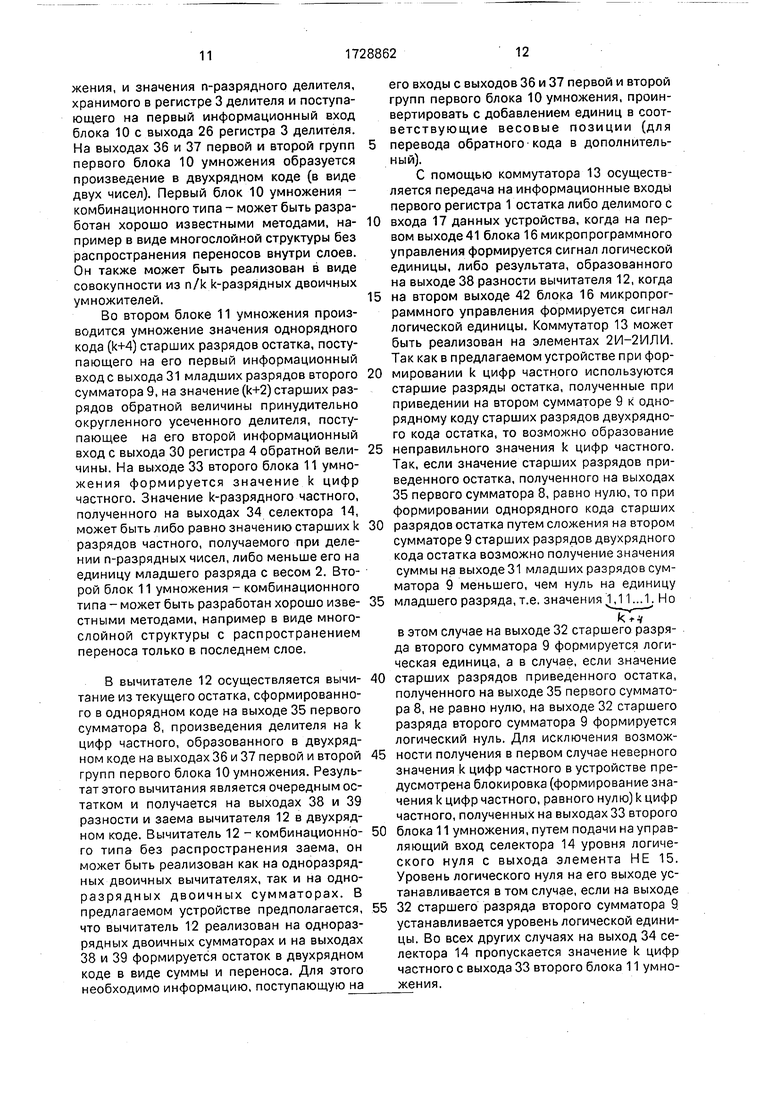

Блок 16 микропрограммного управления координирует работу узлов и блоков устройства при выполнении в нем операции деления, он может быть реализован различ- ными методами, например на счетчике 45 и памяти 46 микрокоманд (фиг.2). Счетчик 45 - накапливающего типа и предназначен для естественной адресации микрокоманд. Вход счета счетчика 45 соединен с входом 18 синхронизации устройства. В качестве памяти 46 микрокоманд может быть применена быстродействующая постоянная память емкостью (М+2) 4, где М .. -

число тактов собственно деления, в течение которых в устройстве формируется М (k- 1)+ 1 цифр частного; ближайшее целое, большее или равное X.

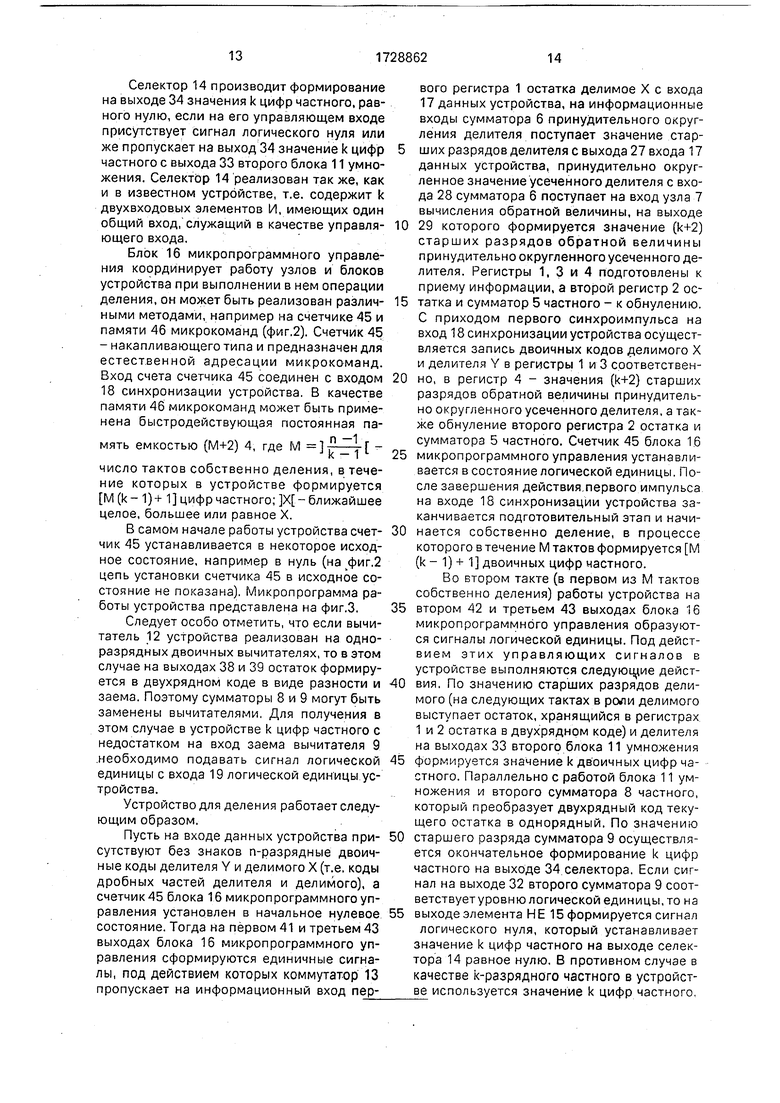

В самом начале работы устройства счет- чик 45 устанавливается в некоторое исходное состояние, например в нуль (на фиг.2 цепь установки счетчика 45 в исходное состояние не показана). Микропрограмма работы устройства представлена на фиг.З,

Следует особо отметить, что если вычи- татель 12 устройства реализован на одноразрядных двоичных вычитателях, то в этом случае на выходах 38 и 39 остаток формируется в двухрядном коде в виде разности и заема. Поэтому сумматоры 8 и 9 могут быть заменены вычитателями. Для получения в этом случае в устройстве k цифр частного с недостатком на вход заема вычитателя 9 .необходимо подавать сигнал логической единицы с входа 19 логической единицы устройства.

Устройство для деления работает следующим образом.

Пусть на входе данных устройства при- сутствуют без знаков n-разрядные двоичные коды делителя Y и делимого X (т.е. коды дробных частей делителя и делимого), а счетчик 45 блока 1.6 микропрограммного управления установлен в начальное нулевое состояние. Тогда на первом 41 и третьем 43 выходах блока 16 микропрограммного управления сформируются единичные сигналы, под действием которых коммутатор 13 пропускает на информационный вход первого регистра 1 остатка делимое X с входа 17 данных устройства, на информационные входы сумматора 6 принудительного округления делителя поступает значение старших разрядов делителя с выхода 27 входа 17 данных устройства, принудительно округленное значение усеченного делителя с входа 28 сумматора 6 поступает на вход узла 7 вычисления обратной величины, на выходе 29 которого формируется значение (k+2) старших разрядов обратной величины принудительно округленного усеченного делителя. Регистры 1, 3 и 4 подготовлены к приему информации, а второй регистр 2 остатка и сумматор 5 частного - к обнулению. С приходом первого синхроимпульса на вход 18 синхронизации устройства осуществляется запись двоичных кодов делимого X и делителя Y в регистры 1 и 3 соответственно, в регистр 4 - значения (k+2) старших разрядов обратной величины принудительно округленного усеченного делителя, а также обнуление второго регистра 2 остатка и сумматора 5 частного. Счетчик 45 блока 16 микропрограммного управления устанавливается в состояние логической единицы. После завершения действия,первого импульса на входе 18 синхронизации устройства заканчивается подготовительный этап и начинается собственно деление, в процессе которого в течение М тактов формируется М (k - 1) + 1 двоичных цифр частного.

Во втором такте (в первом из М тактов собственно деления) работы устройства на втором 42 и третьем 43 выходах блока 16 микропрограммного управления образуются сигналы логической единицы. Под действием этих управляющих сигналов в устройстве выполняются следующие действия. По значению старших разрядов делимого (на следующих тактах в роли делимого выступает остаток, хранящийся в регистрах 1 и 2 остатка в двухрядном коде) и делителя на выходах 33 второго блока 11 умножения формируется значение k двоичных цифр частного. Параллельно с работой блока 11 умножения и второго сумматора 8 частного, который преобразует двухрядный код текущего остатка в однорядный. По значению старшего разряда сумматора 9 осуществляется окончательное формирование k цифр частного на выходе 34 селектора. Если сигнал на выходе 32 второго сумматора 9 соот- ветствуетуровню логической единицы, то на выходе элемента НЕ Сформируется сигнал логического нуля, который устанавливает значение k цифр частного на выходе селектора 14 равное нулю. В противном случае в качестве k-разрядното частного в устройстве используется значение k цифр частного,

сформированное на выходе 33 второго блока 11 умножения. Сформированное на выходе 34 селектора 14 k-разрядное частное Zi (в следующих тактах - Zj,, где i - номер такта собственно деления) поступает на информационные входы младших разрядов сумматора частного и на второй информационный вход первого блока 10 умножения, на выходах 36 и 37 которого образуется в двухрядном коде произведение Y ZL С помощью вычита- теля 12 формируется разность X - Y Zi в двухрядном коде, которая в дальнейшем служит остатком и подается на второй информа- ционный вход коммутатора 13 и на информационный вход второго регистра 2 остатка со сдвигом на (k-1) разряд влево (в сторону старших разрядов). Регистры 1, 2 и сумматор 5 частного подготовлены к приему информации. С приходом второго синхроимпульса на вход 18 синхронизации устройства в регистры 1 и 2 остатка записывается сформированный на выходах 38 и 39 вычи- тателя 12 двухрядный код остатка, в младшие разряды сумматора 5 частного заносятся k старших цифр частного, а счетчик 45 блока 16 микропрограммного управления устанавливается в состояние 2. На этом второй такт работы устройства заканчивается и далее выполняется еще (М-1) аналогичных тактов. Заметим, что в каждом из этих тактов старшая двоичная цифра из k очередных цифр частного, образованных на выходе 34 селектора 14 и поступающих на информационные входы младших разрядов сумматора 5 частного, подсуммируется к младшему разряду содержимого сумматора 5 частного, сдвинутому на (k-1) разряд в сторону его старших разрядов.

После выполнения последнего (М+1) такта на выходе 21 частного устройства образуется n-разрядное частное, на выходе 20 остатка устройства образуется п-разрядный остаток. Одновременно с этим из памяти 46 микрокоманд блока 16 микропрограммного управления считывается микрокоманда (М+2), которой соответствует управляющий сигнал Y44 и соответственно на четвертом выходе 44 блока 16 микропрограммного управления устанавливается уровень логической единицы, сигнализирующий об окончании операции деления.

Сравнение предлагаемого устройства для деления и известного устройства по быстродействию.

Так как в предлагаемом устройстве и в известном устройстве деление выполняется за одно и то же число тактов, то для сравнения их быстродействия достаточно сравнить длительность одного такта их работы.

Длительность одного такта работы известного устройства в случае одновременного присутствия кодов делимого и делителя на входе данных устройства опре- деляется из выражения:

Тпрот tno + to6p + tyMH2 + tcefl +

+ Тумн1 + Т,выч + tic + tprl

(t2 tno + to6p),

где tno - время формирования принудитель- но округленного значения (k+З) старших разрядов делителя на выходе сумматора принудительного округления делителя;

to6p - время формирования (k+2) стар- ших разрядов обратной величины принудительно округленного усеченного делителя на выходе узла вычисления обратной величины;

tyMH2 - время формирования k цифр час- тного на выходе второго блока умножения; teen- время формирования правильного значения k цифр частного на выходе селектора;

tyMHi - время формирования произве- дения делителя на k цифр частного в двухрядном коде на выходах первого блока умножения;

Т-вых - время формирования очередного остатка в двухрядном коде на выходах вычи- тателя;

т.к - время срабатывания коммутатора; tprl - время записи информации в первый регистр остатка;

t2 - время формирования (k+4) старших разрядов однорядного кода очередного остатка на втором сумматоре.

Длительность одного такта работы предлагаемого устройства в случае одно- временного присутствия кодов делимого и делителя на входе данных устройства определяется из выражения:

Тпредл - t2 + 1умн2 + tcefl + tyMHi + + tebi4 + tK + tperl. Так как t2 tno, TO Тпрот Тпредл to6p.

При значениях k 4-8 время формирования (k+2) старших разрядов обратной величины принудительно округленного усеченного делителя на выходе узла вычис- ления обратной величины (to6p) составляет 15-40% от общей длительности такта.

Следовательно, быстродействие предлагаемого устройства примерно на 17,6- 66,6% выше, чем быстродействие известного устройства. Обьем используемого оборудования в них практически тот же, так как в предлагаемое устройство введен только один регистр обратной величины, но он малоразрядный.

Ф о р м у л а и з о б р ет е н и я Устройство для деления, содержащее два регистра остатка, регистр делителя, сумматор частного, сумматор принудительного округления делителя, узел вычисления обратной величины, два сумматора, два блока умножения, вычитатель, коммутатор, селектор, элемент НЕ и блок микропрограммного управления, причем вход данных устройства соединен с информационным входом регистра делителя и с первым информационным входом коммутатора, выход которого соединен с информационным входом первого регистра остатка, выходы первого и второго регистров остатка соединены с первым и вторым информационными входами соответственно первого сумматора, выход которого является выходом остатка устройства и соединен с входом уменьшаемого вычитателя, входы вычитаемого и заема которого соединены с выходами первой и второй групп соответственно первого блока умножения, первый информационный вход которого соединен с выходом регистра делителя, выходы разности и заема вычитателя соединены с вторым информационным входом коммутатора и информационным входом второго регистра остатка соответственно, выходы старших разрядов первого и второго регистров остатка соединены с первым и вторым информационными входами соответственно второго сумматора, выход младших разрядов которого соединен с первым информационным входом второго блока умножения, выход старшего разряда второго сумматора соединен с входом элемента НЕ, выход которого соединен с управляющим входом селектора, информационный вход которого соединен с выходом второго блока умножения, выход селектора соединен с информационным входом младших разрядов сумматора

частного и с вторым информационным входом первого блока умножения, вход логической единицы устройства соединен с входом переноса сумматора принудительного округления делителя, выход которого соединен с входом узла вычисления обратной величины, вход синхронизации устройства соединен с синхро входами первого и второго регистров остатка, регистра делителя,

сумматора частного и блока микропрограммного управления, первый выход которого сое- динен с первым управляющим входом коммутатора и входами установки в О второго регистра остатка и сумматора частного,

выход которого является выходом частного устройства, второй выход блока микропрограммного управления соединен с вторым управляющим входом коммутатора и входами разрешения записи второго регистра остатка и сумматора частного, третий выход блока микропрограммного управления соединен с входом разрешения записи первого регистра остатка, четвертый выход блока микропрограммного управления является

выходом признака окончания деления устройства, отличающееся тем, что, с целью повышения быстродействия, в него введен регистр обратной величины, выход которого соединен.с вторым информациейным входом второго блока умножения, выход узла вычисления обратной величины соединен с информационным входом регистра обратной величины, вход разрешения записи которого соединен с первым выходом блока микропрограммного управления и входом разрешения записи регистра делителя; синхровход которого соединен с синх- ровходом регистра обратной величины, вход старших разрядов данных устройства

соединен с информационным входом сумматора принудительного округления делителя.

1728862 W 42 43 W

Фиг. 2

| Устройство для деления | 1985 |

|

SU1322264A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления | 1986 |

|

SU1357947A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-04-23—Публикация

1990-07-17—Подача