iI:ui6pi Tei H( гт иоги i-: rih; ni(rin тслыюГ тсхиикр II м(1Ж( (ii.iTf, ripiiMe- иено в быстрбденствующих лрифмет} че- ских устроГютвах для выполнения операции деления чисел.

Цель изобретения - упрощение аппаратурных затрат устройства.

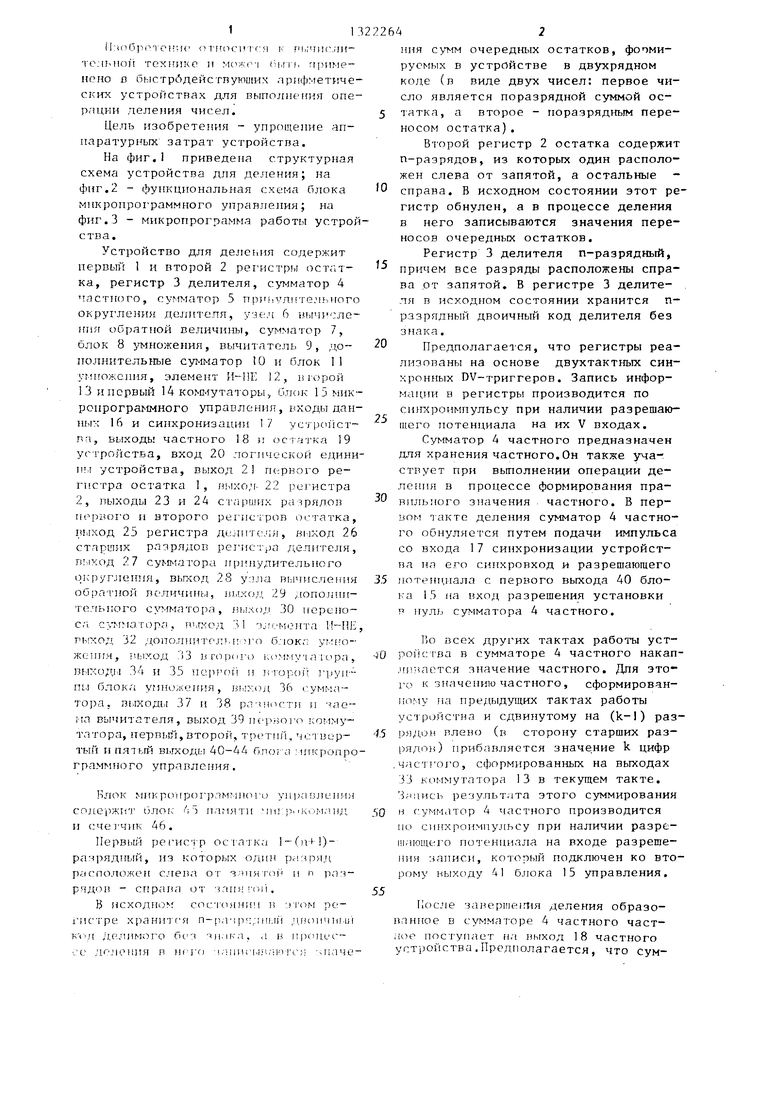

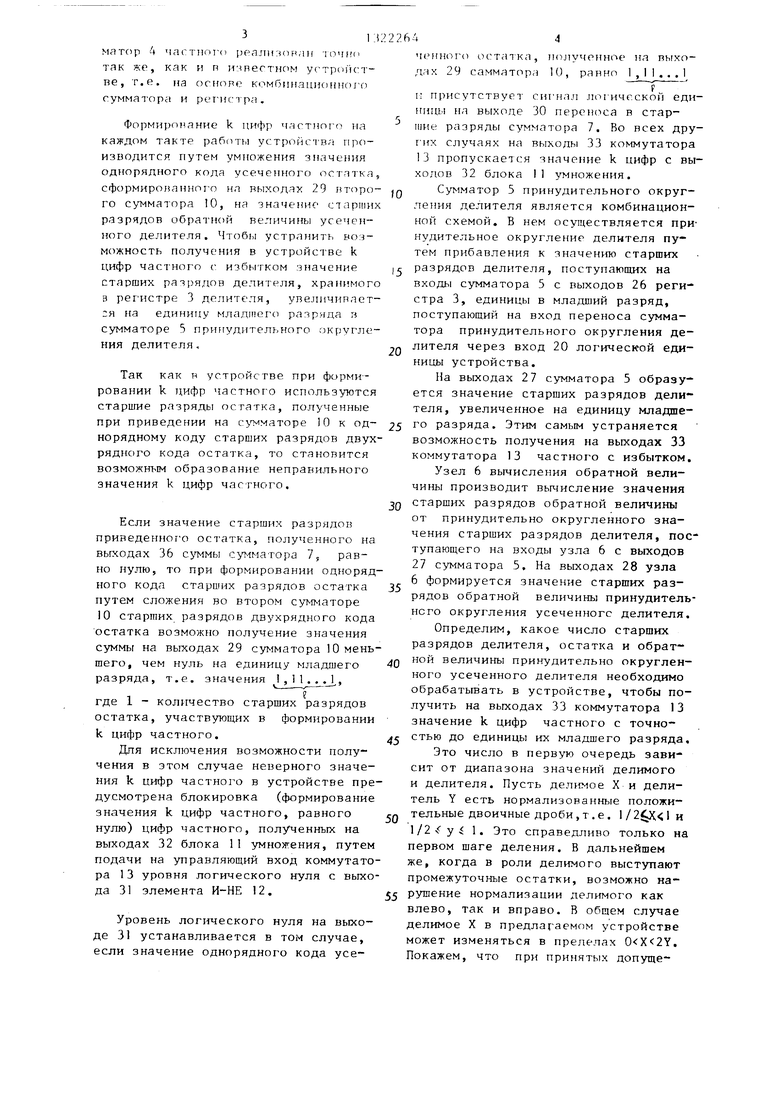

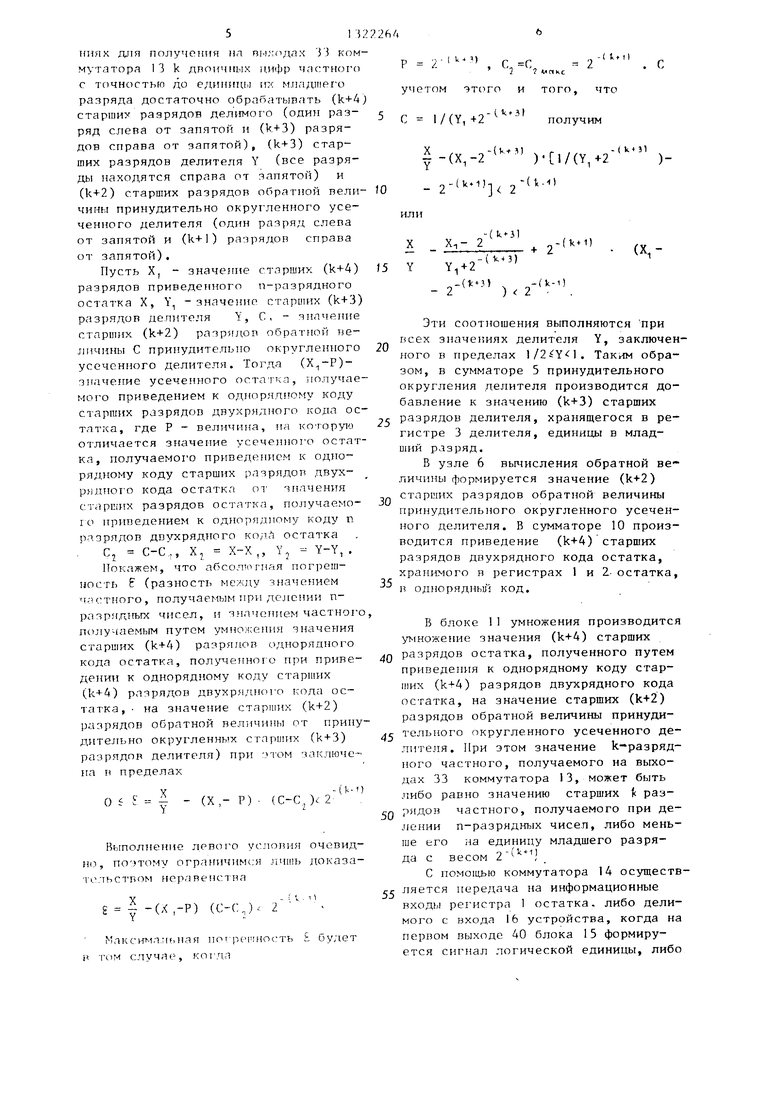

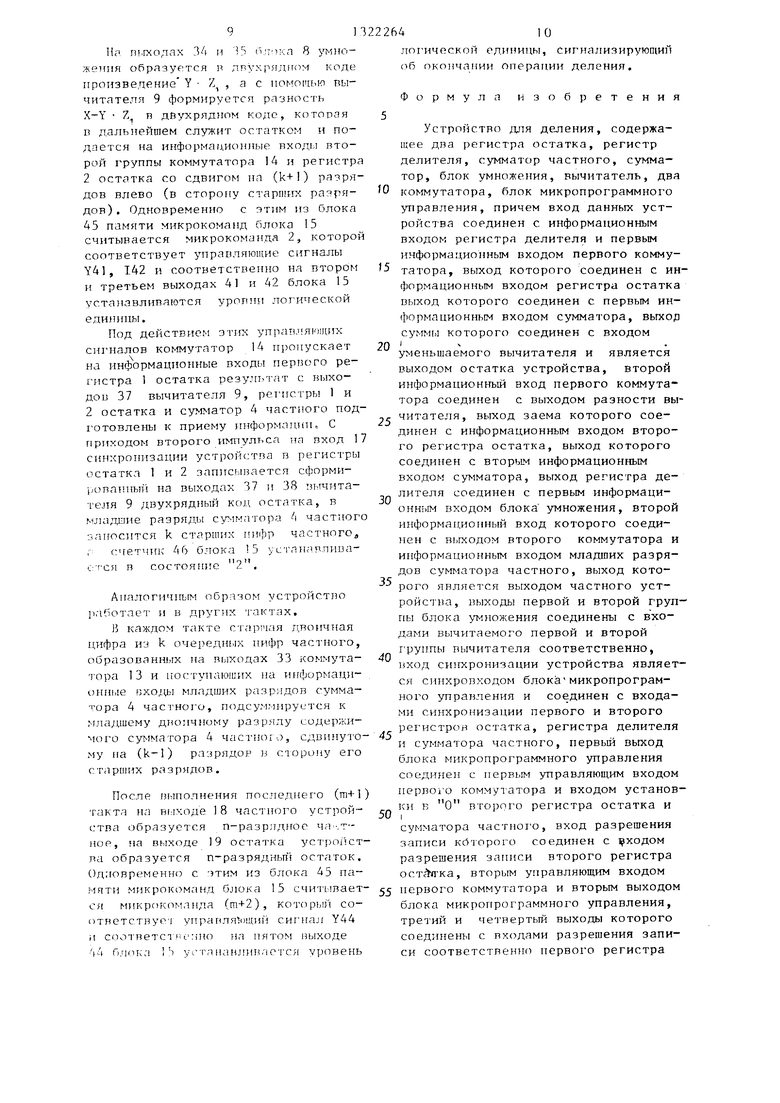

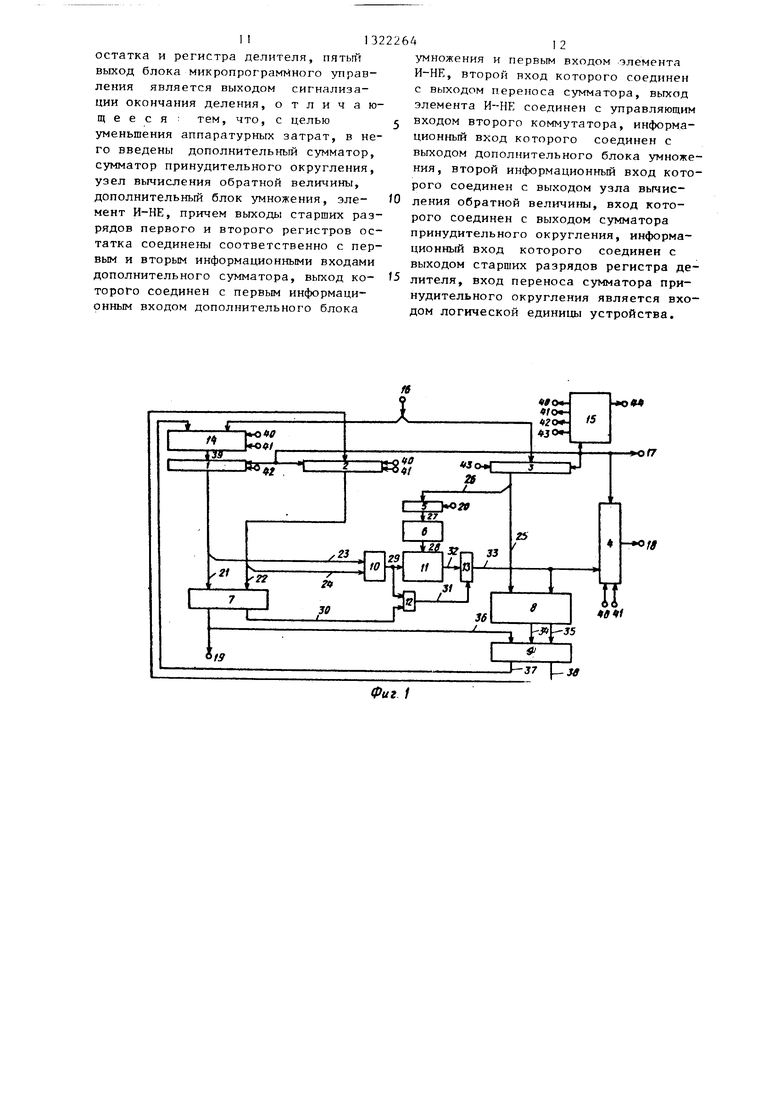

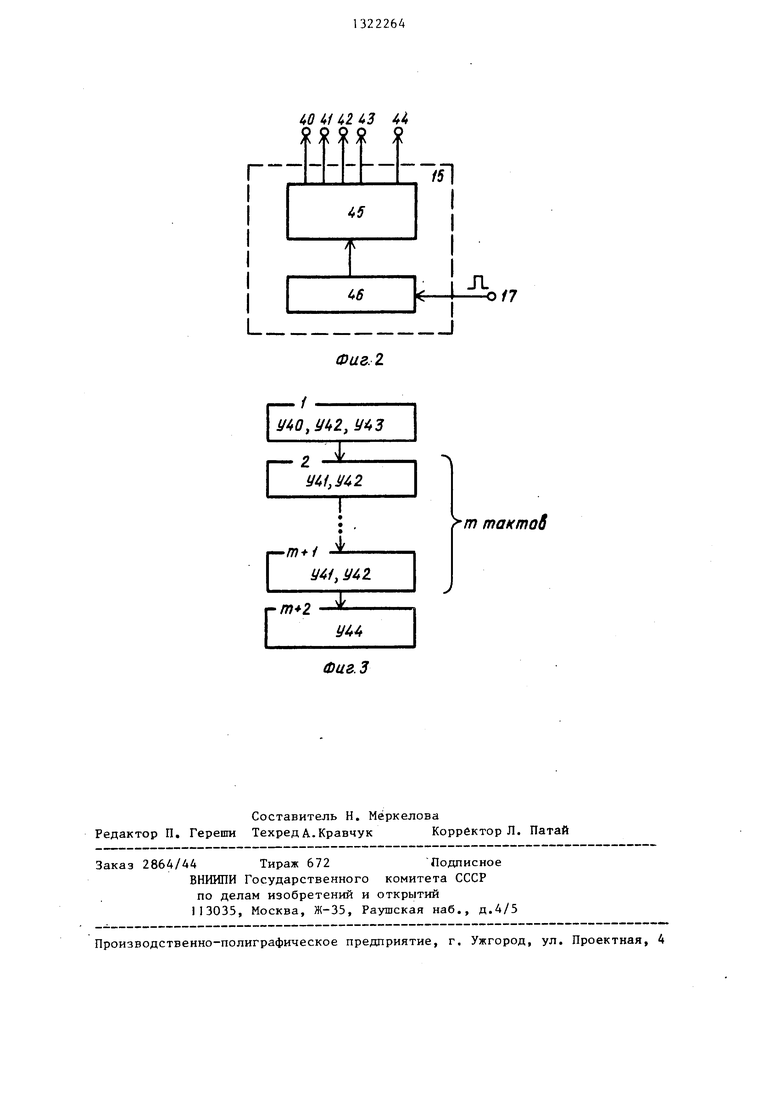

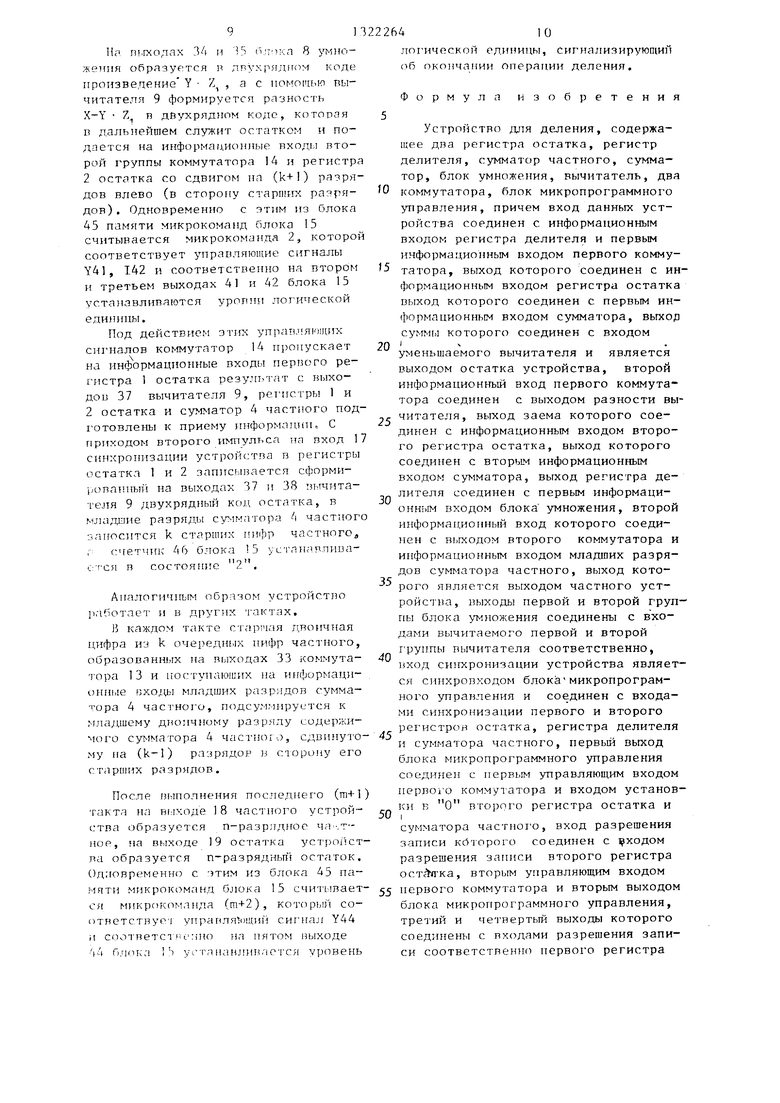

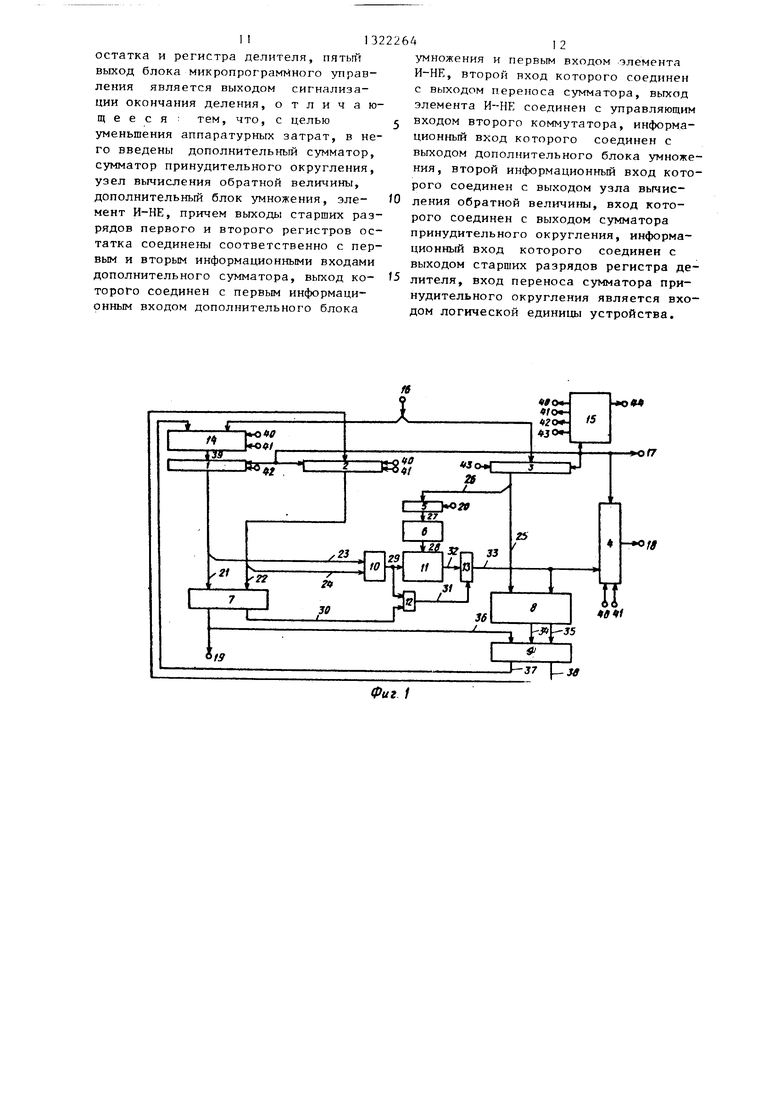

На фиг.1 приведена структурная схема устройства для деления; на фиг.2 - функциональная схема блока микропрО1 раммного управления; на фиг.3 - микропрограмма работы устройства.

Устройство для деления содержит первьп г 1 и второй 2 регистр) остатка, регистр 3 делителя, с умматор 4 частного, сумматор 5 приьул те:11:. окру1 ле {ия делителя, узел 6 пия обратной величи1а, сумматор 7, блок 8 гмножения, вычитатель 9, до- полнителышю сумматор 10 и блок 1 1 умножения, элемент 12, is горой 13ппсрвый 14 KONMyTaTopb J б,1()к 15 микропрограммного управления, входы данных 16 и синхронизации 17 устроГют- яп, выходы частного 18 и остатка 19 устройства, вход 20 логической едини I. устройства, выход 21 первого регистра остатка 1 , 22 рег истргг 2, выходы 23 и 24 старилгх разрядов нервох о и второго рел истров остатка, Л1ЛХОД 25 регистра , выход 26 старших разрядов регистра /целителя, пыход 27 сумматора при1гудительного О1ч ругленпя, выход 28 В 5 числеиия обрач ной величины, ги. ход 29 ,.опо) телгьного сумматора, )д 30 переноса с -мматора, выход 31 Jji.vMijHTa И-НЕ 32 ;Юполнитгл1. блок, ; уг. л-сеиия, ыход 33 Broixiro коммуi а гора , ,1 34 и 35 Hcprnii и liTopofr г||уи- - ru.i блока угпи,1;кеп я, Bhixoji; 36 С умма.- то1)а. П 1ходь 37 и 38 рачиости i чае-- ма вь читателя, выход 39 ( p:.ioro коммутатора, первьй, BTOpoii, трети/и чствер- ипятьш выходе; 40-44 бпог-а мтткропро rpaMfnioro управления.

Блок микроиро1 5лм;-П1(1ги у11раиле ия

содержи 45 1). , -,

и сче гчик 46.

Первьш регистр l-())- ра:- рядпь Й, из которых один разряд рас-положон слева от зчпягой п разрядов - справа от .

Б )сходноь; состоянии i реГИС Тре хранится П-ра МТЧЛН,

Де.мимого без ,, а к )(Ч,ис . С лг Л1:м1 1я в 4,.i;i. гс;; % 1ачения cyNfM очередных остатков, фопми- руемых в устройстве в двухрядном коде (в виде двух чисел: первое число является норазрядной суммой ос- татка, а второе - поразрядным переносом остатка).

Второй регистр 2 остатка содержит п-разрядов, из которых один расположен слева от запятой, а остальные - справа. В исходном состоянии этот регистр обнулен, а в процессе деления в него записываются значения переносов очередных остатков.

Регистр 3 делителя п-разрядный.

причем все разряды расположены спра

ва от запятой. В регистре 3 делителя в исходном состоянии хранится п- рззряднь й двоичный код делителя без знака.

Предполагается, что регистры реализованы на основе двухтактных синхронных DV-триггеров. Запись информации в регистры производится по сит роимпульсу при наличии разрешаю- потенциала на их V входах.

Сумматор 4 частного предназначен для хранения частного. Он также участвует при выполнении операции деления в процессе формирования праВ 1льного з ачения частного. В первом 1акте деления сумматор 4 частного обнуляе ся путем подачи импульса со входа 17 синхронизации устройства на его сипхровход и разрешающего

лотенп,1ала с первого выхода 40 бло- . а 15 на вход разрешения установки р 1уль сумматора 4 частного.

1)О всех других тактах работы уст- роГк; гва в сумматоре 4 частного накап- л иаотся значение частного. Для это- I o к значени о частного, сформирован- 1пму fia предыду1цих тактах работы ус1ройства и сдвинутому на (k-1) раз- рядов плево (в сторону старших разрядов) рибавляется значе.ние k цифр . час Т ог о, сформированных на выходах 33 коммутатора 13 в текущем такте. Запись результата этого суммирования сумматор 4 частного производится 1о с 1хроим ул ьсу при наличии разрс- потенциала на входе разреше- ии , который подключен ко второму 41 15 управления.

Пос.че занер 1 е1гия деления образованное в сумматоре 4 частного частное тоступает и.ч выход 18 частного устройства .Предг олагается, о сум3i;t2

матор 4 частиот о i)eajTH3()( точии так же, как и п нчнегтипм устр 1 1с:т- ве, т.е. на осиояе комбинационного сумматор; и рег испра.

Формиронание k цифр частного гга каждом такте работы устройств; производится нутем умножения значения однорядного кода усеченного остатка, сформиро1 анног о на выходах 29 второ- го сумматора 10, на значение старших разрядов обратной величины усеченного делителя. Чтоб|,| устранить возможность получения в устройстве k цифр частного с избытком значение старших разрядов делителя, хранимого в регистре 3 делителя, увеличипает- 2я на единицу младшего разряда п сумматоре 5 принудительного округления делителя,

Так как в устройстве при формировании k цифр частного используются старшие разряды остатка, полученные при приведении на с мматоре 10 к од- норядному коду старших разрядов двухрядного кода остатка, то становится возможным образование неправильного значения k цифр частного.

Если значение старших разрядов приведенного остатка, полученного на выходах 36 сукматора 7, равно нулю, то при формировании однорядного кода старших разрядов остатка путем сложения во втором сумматоре 10 старших разрядов двухрядного кода остатка возмо7кно получение значения суммы на выходах 29 сумматора 10 меньшего, чем нуль на единицу младшего разряда, т,е„ значения 1,11...

где 1 - количество старших разрядов остатка, участвующих в формировании k цифр частного.

Ддя исключения возможности получения в этом случае неверного значения k цифр частного в устройстве предусмотрена блокировка (формирование значения k цифр частного, равного нулю) цифр частного, полученных на выходах 32 блока 11 умножения, путем подачи на управляющий вход коммутатора 13 уровня логического нудя с выхода 31 элемента И-НЕ 12.

Уровень логического нуля на выходе 31 устанавливается в том случае, если значение однорядного кода усе Q о

5

0

5

0

5

Q

ченного ocTaiKa, полученное на выходах 29 самматора 10, равно 1,II...1

f-

li присутствует сигнал логической единицы на выходе 30 переноса в старшие разряды сумматора 7. Во всех дру- г их случаях на выходы 33 коммутатора 13 пропускается значение k цифр с выходов 32 блока II умножения.

Сумматор 5 принудительного округления делителя является комбинационной схемой, В нем осуществляется принудительное округление делителя путем прибавления к значению старших разрядов делителя, поступающих на входы сумматора 5 с выходов 26 регистра 3, единицы Б младший разряд, поступающий на вход переноса сумматора принудительного округления делителя через вход 20 логической единицы устройства.

На выходах 27 сумматора 5 образуется значение старших разрядов делителя, увеличенное на единицу младшего разряда. Этим самым устраняется возможность получения на выходах 33 коммутатора 13 частного с избытком.

Узел 6 вычисления обратной величины производит вычисление значения старших разрядов обратной величины от принудительно округленного значения старших разрядов делителя, поступающего на входы узла 6 с выходов 27 сумматора 5, На выходах 28 узла 6 формируется значение старших разрядов обратной величины принудительного округления усеченного делителя.

Определим, какое число старших разрядов делителя, остатка и обратной величины принудительно округленного усеченного делителя необходимо обрабатывать в устройстве, чтобы получить на выходах 33 коммутатора 13 значение k цифр частного с точностью до единицы их младшего разряда.

Это число в первую очередь зависит от диапазона значений делимого и делителя. Пусть делимое X и делитель Y есть нормализованные положительные двоичные дроби, т. е. 1 /2 1 и

yi 1. Это справедливо только на первом шаге деления. В дальнейшем же, когда в роли делимого выступают промежуточные остатки, возможно нарушение нормализации делимого как влево, так и вправо. В общем случае делимое X в предлагаемом устройстве может изменяться в пределах , Покажем, что при принятых допуще514

пнях для получения ил пы;:одах 33 коммутатора 13 k двоичных цифр частного с точностью до единиц,) их младшего разряда достаточно обрабатывать (k+4 старшие разрядов дел1гмого (один раз- ряд слева от запятой и (k+3) разрядов сцрава от запятой), (k+3) старших разрядов делителя Y (все разряды находятся справа от запятой) и (k+2) старших разрядов обратной вели- чины принудительно округленного усеченного делителя (один разряд слева от запятой и (k+1) разрядов справа от запятой).

Пусть X, - значение старших (k+4) разрядов приведенного п-разрядного остатка X, Y -значение crapunix (k+3) разрядов делителя Y, С, - значение старших (k+2) разрядов обратной величины С принудительно округленного усеченного делителя. Тогда ()- значение усеченного остатка, получаемого приведением к однорядному коду старших разрядов двухр дного кода остатка, где Р - величина, на которую отличается значение усеченного остатка, получаемого приведением к однорядному коду старших разрядов двух- ряднот о кода остатка от значения старших разрядов остатка, получаемого приведением к однорядному коду п разрядов дв гхрядного кодй остатка

г Г-Г X x-x

v я - L и., , л T л л j

V - Y-y 1 j 14

Потсажем, что абсолютная погрешность 6 (разность между значением частного, получаемым при делении п- разряд1шгх чисел, и значением частного получаемым путем умнол;енпя значения старших (k+4) разрядов однорядного кода остатка, положенного при приведении к однорядному коду старших (k+4) разрядов двухря/iHoro кода остатка, на значение старших (k+2) р.азрндов обратной величины от принудительно округленш,х стари их (k + 3) разрядов делителя) при гзтом заключена в пределах

о

I - (X,- Р)

(С-С„) 2

Выполнение левого условия очсвид- Н(3, поэтому ограничимся лишь доказательством неравенства

X- и-п

-(Х,-Р) (С-С,)

2

Макст-мльная погрешность будет 1Ч)М случае, ко1 ля

/ С Г - , -,,j - ky

етом этого и 1/(У,+2t MClkC

того.

- ( t 11

ЧТО

-ГУ

-

получим

) Cl/(

V.-i)

. (

X,- 2

-()

Y,+2

-(o)

+ 2

-(V+1)

(X,- 2

-()

) 2

-( V-1)

)5

20

Эти соотношения выполняются при всех значениях делителя Y, заключенного в пределах l/2iY l. Таким образом, в сумматоре 5 принудительного округления делителя производится добавление к значению (k+3) старших 25 разрядов делителя, хранящегося в регистре 3 делителя, единицы в младший разряд.

В узле 6 вычисления обратной величины формируется значение (k+2) старших разрядов обратной величины принудительного округленного усеченного делителя. В сумматоре 10 производится приведение (k+4) старших разрядов двухрядного кода остатка, хранимого в регистрах 1 и Z- остатка.

30

35

в однорядньш код.

В блоке 11 умножения производится умножение значения (k+4) старших

разрядов остатка, полученного путем приведения к однорядному коду старших (k+4) разрядов двухрядного кода остатка, на значение старших (k+2) разрядов обратной величины принудительного округленного усеченного делителя. При этом значение k- разряд- ного частного, получаемого на выходах 33 коммутатора 13, может быть либо равно значению старших t; разрядов частного, получаемого при делении п-разрядных чисел, либо меньше его на единицу младшего разряда с весом 2

С помощью коммутатора 14 осуществ-

ляется передача на информационные входы регистра 1 остатка, либо делимого с входа 16 устройства, когда на первом выходе 40 блока 15 формируется сигнал логической единицы, либо

713

результата, пГтрпчовалиого на вых(1длх 37 перлон групп.г т пштателя 9, когда на втором выходе 41 блока 15 формируется сигнал ло1 нческо11 е диннпы,

Устройстпг для деления работает следующим образом.

На вход 16 данных устройства поступают п-разрядные двоич1П)е коды делимого X и делителя Y(здесь предполагается, что дел1тмое и делитель правильные положительные дроби ), а счетчик 46 блока 15 установлен в исходное нулевое состояние.

По содержимому счетчика 46, которое служит адресом обращения к памяти микрокоманд блока 15, из блока 45 памяти микрокоманд считывается микрокоманда 1 , которой соответствуют управляющие сигналы Y40, Y 42, Y43 (фиг.4). R результате этого соответственно на перном, третьем и четвертом выходах 40, 42 и 43 блока 15 управления устанавливаются уровни логической единицы.

Под действием этих управляющих сигналов коммутатор 14 пропускает на информационные входы первого регистра 1 остатка делимое X с входа 16 устройства, регистры остатка 1 и делителя 3 подготовлены к приему ин- формации так как на их входах разрешения записи присутствуют потенциалы логической единицы, а второй регистр 2 остатка и сумматор 4 частного настроены на обнуление.

С приходом первого импульса на вход 17 синхронизации устройства производится запись двоичных кодов делимого X и делителя Y в регистры соответственно 1 и 3, а также обнуление регистра 2 остатка и сумматора 4 частного и установка счетчика 46 блока 15 в состояние 1. С момента окончания действия первого импульса на выходе 17 синхронизации устройства заканчивается подготовительный этап и начинается собственно деление, в процессе которого в течение m тактов формируется. m-(k-l)-t-l двоичных цифр частного.

В некоторых случаях целесообразно под1 отовительный этап организовывать двухшаговым, причем на его первом шаге осуществлять запись только делителя Y в регистре 3 делителя, а на втором шаге произвести запись делимого в регистр 1 остатка и обнупят

8

регистр 2 оста ) и сумматор 4 частного. Зтим самым обеспечивается меньшая длительность такта работы устройства, так как временная задержка сумматора 5 и уялл 6 не будет влиять в этом случае на временньш цикл работы устройства.

В тех же случаях, когда операнды не могут быть загружены в регистры

1 и 3 одновременно (например, при последовательной их выборке из памяти) необходимо всегда в первую очередь записывать делитель, а потом уже делимое.

В первом такте собственно деления по значению старших разрядов делимого X (на следующих тактах в роли делимого будет выступать остаток, хранящийся в регистрах 1 и 2 в двухрядном коде) и делителя Y на выходах 32 блока умножения 22 формируется k двоичных цифр частного. Параллельно с работой сумматора 10 и блока 11 умножения работает первый сумматор

7, который преобразует двухрядный код текущего остатка в однорядный код.

По значению сигнала переноса в старшие разряды этого сумматора, формируемого на выходе 30 сумматора 7, и значению однорядного кода усеченного остатка, полученного при проведении старших разрядов двухрядного кода остатка на выходах 29 сумматора 10, осуществляется окончательное формирование k цифр частного.

Если сигнал переноса в старшие разряды первого сумматора 7 соответ- ствует уровню логической единицы, а значение .() разрядов на выходах 29 сумматора 10 равно 1,1,.., на

)ГГ4

выходе 31 элемента И-НЕ 12 формируется сигнал логического нуля, который устанавливает значение k цифр частного на выходах 33 коммутатора 13, равное нулю.

Во всех других случаях в качест- ве k-разрядного частного в устройстве используется значение k цифр частного, сформированных на выходах 32 блока 11 умножения. Сформированное на выходах 33 коммутатора 13 k-раз- рядное частное Z , (на следующих тактах Z, где i - номер такта собственно деления) поступает на информационные входы младших разрядов сумматора 4 частного 4.

На пыходах 34 н 3S олмка 8 умножения образуется р лпухрядн(1м коде произведение Y 7. , а с помощью вы- читателя 9 формируется разность X-Y Z п двухрядном коде, которая в д,аль 1ейшем слуткнт остатком и подается на информацио)ные входы второй группы коммутатора 14 и регистра 2 остатка со сдвигом па (k+1) разрядов влево (в сторопу старших разрядов). Одновременно с этим из блока 45 памяти микрокоманд блока 15 считывается микрокоманда 2, которой соответствует управляющие сигналы Y41, 142 и соответственно на втором и третьем выходах 41 и 42 блока 15 устанавливаются уровни логической едипипы.

Под действием этих управд яющих сигпалов коммутатор 14 пропускает на информационные входы первого регистра 1 остатка резу.тпп-ат с выходов 37 вычитателя 9, регистры 1 и 2 остатка и сумматор 4 частного подготовлены к приему информадшь С приходом второго импульса на вход 1 синхронизадии устройства в регистры остатка 1 и 2 заппсы зается сформированный па выходах 37 и 38 вычитателя 9 двухрядный код остатка, в младшие разряды су:чматора 4 частного заносится k старших шиЬр частного, , счетчик 46 блока 15 устлнавлива- с: Г ся В состояние 2,

Аналогичным образом устройство таботает и в других тактах,

15 каждом такте старшая двоичная цифра из k оче1)едных пифр частпого, образованн,1х на выходах 33 коммутатора 13 и поступающих на ипформаци- onni.ie вхо;цз1 младших разрядов сумма- 4 частного, подсумгилруется к младшему двоичному содержи- сумматора 4 частного, сдвинуто му fia (k-I) разрядов м сюроиу его старших разрядов.

После выполнения последпег о (т+1) такта на выходе 18 частпого устройства образуется п-разрпднос .т- нор, на выходе 19 остатка ycTpoi jcT- ва образуется п-разряднгзШ остаток. ()диовременн(5 с этим из блока 45 пауменьшаемого вычитателя и является выходом остатка устройства, второй информапионньш вход первого коммутатора соединен с выходом разности вы- ,, читателя, выход заема которого соединен с информационным входом второго регистра остатка, выход которого соединен с вторььм информационг ым входом сумматора, выход регистра делителя соединен с первым информационным входом блока умножения, второй информационный вход которого соединен с выходом второго коммутатора и информационным входом младших разрядов сумматора частного, выход которого является выходом частного устройства, }зыходы первой и второй группы блока умножения соединены с входами вычитаемого первой и второй г рунпы вычитателя соответственно, вход си1гхронизации устройства является с1П1хровходом блока микропрограм- ного управления и соединен с входами синхронизации первого и второго регистров остатка, регистра делителя и сумматора частпого, первый выход блока микропрограммного управления соединен с первым управляющим входом первого коммутатора и входом установ50

ки в о второго регистра остатка и

сумматора частного, вход разрешения записи кйторого соединен с уходом разрешения записи второго регистра , вторым управляющим входом мяти микрокоманд блока 15 считывает- 55 первого коммутатора и вторым выходом си микрокоманда (т+2), который со- блока микропрограммного управления, ответствуо управля ощнй сиг нал Y44 третий и четвертый выходы которого и соответс (U :nio на пятом выходе соединены с входами разрешения запи- i4 Плпкл IS ycranaBjntB. ic TCH уровень си соответственно первого регистра

О

5

0

логической единиды, сигнализирующий (.б окончании операпии деления.

Формула изобретения

Устройство для деления, содержащее два регистра остатка, регистр делителя, сумматор частного, сумматор, блок умножения, вычитатель, два KONtMyTaTopa, блок микропрограммного управления, причем вход данных устройства соединен с информационным входом регистра делителя и первым информационным входом первого коммутатора, выход которого соединен с ин- формадионным входом регистра остатка выход которого соединен с первым ин- формапионным входом сумматора, выход cyMMi.i которого соединен с входом

0

0

5

уменьшаемого вычитателя и является выходом остатка устройства, второй информапионньш вход первого коммутатора соединен с выходом разности вы- , читателя, выход заема которого соединен с информационным входом второго регистра остатка, выход которого соединен с вторььм информационг ым входом сумматора, выход регистра делителя соединен с первым информационным входом блока умножения, второй информационный вход которого соединен с выходом второго коммутатора и информационным входом младших разрядов сумматора частного, выход которого является выходом частного устройства, }зыходы первой и второй группы блока умножения соединены с входами вычитаемого первой и второй г рунпы вычитателя соответственно, вход си1гхронизации устройства является с1П1хровходом блока микропрограм- ного управления и соединен с входами синхронизации первого и второго регистров остатка, регистра делителя и сумматора частпого, первый выход блока микропрограммного управления соединен с первым управляющим входом первого коммутатора и входом установ5

50

ки в о второго регистра остатка и

остатка и регистра делителя, пятьги выход блока микропрограммного управления является выходом сигнализации окончания деления, отличаю- щ е е с я : тем, что, с целью уменьшения аппаратурных затрат, в него введены дополнительный сумматор, сумматор принудительного округления, узел вычисления обратной величины, дополнительный блок умножения, элемент И-НЕ, причем выходы старших разрядов первого и второго регистров остатка соединены соответственно с первым и вторым информационными входами

дополнительного сумматора, выход ко- 15 лителя, вход переноса сумматора притороГо соединен с первым информационным входом дополнительного блока

умножения и первым входом элемента И-НЕ, второй вход которого соединен с выходом переноса сумматора, выход элемента И-НЕ соединен с управляющим входом второго коммутатора, информационный вход которого соединен с выходом дополнительного блока умножения, второй информационный вход которого соединен с выходом узла вычисления обратной величины, вход которого соединен с выходом сумматора принудительного округления, информационный вход которого соединен с выходом старших разрядов регистра денудительного округления является входом логической единицы устройства.

45 4/ 42 4 J 44 О

il

Г

45

II

Фиг. 2

Фиг. 3

Составитель Н. Мёркелова Редактор П. Гереши Техред А.Кравчук Корректор Л. Патай

Заказ 2864/44 Тираж 672 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

2 4 J 44

il-,.i

I A

0/7

m тактоб

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел | 1988 |

|

SU1580353A1 |

| Устройство для деления | 1988 |

|

SU1541598A1 |

| Устройство для деления | 1989 |

|

SU1667060A1 |

| Устройство для деления | 1990 |

|

SU1728862A1 |

| Устройство для умножения | 1986 |

|

SU1399729A1 |

| Устройство для деления | 1991 |

|

SU1783523A1 |

| Устройство для деления | 1986 |

|

SU1357947A1 |

| Устройство для деления чисел | 1985 |

|

SU1429109A1 |

| Устройство для деления чисел | 1990 |

|

SU1735844A1 |

| Устройство для деления | 1986 |

|

SU1429110A1 |

Изобретение относится к вычислительной технике и может быть применено для быстрого вьшолнення операции деления чисел. Целью изобретения является уменьшение аппаратурных затрат, что достигается введением в устройство дополнительных суммйторов и блока умножения, узла вычисления обратной величины и элемента И-НЕ. Приведение k однорядному коду очередного остатка осуществляется параллельно с образованием k очередных цифр частного.; В устройстве используются при формировании k цифр частного вместо двух блоков деления узел вычисления обратной величииы и блок умножения. 3 ил. S (Л и to ГС

| Устройство для деления | 1984 |

|

SU1249551A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления | 1985 |

|

SU1282117A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-07—Публикация

1985-09-16—Подача