Изобретение относится к вычислительной технике и может быть примене но в быстродействующих арифметически устройствах для выполнения операции деления чисел.

Цель изобретения. - сокращение количества оборудования.

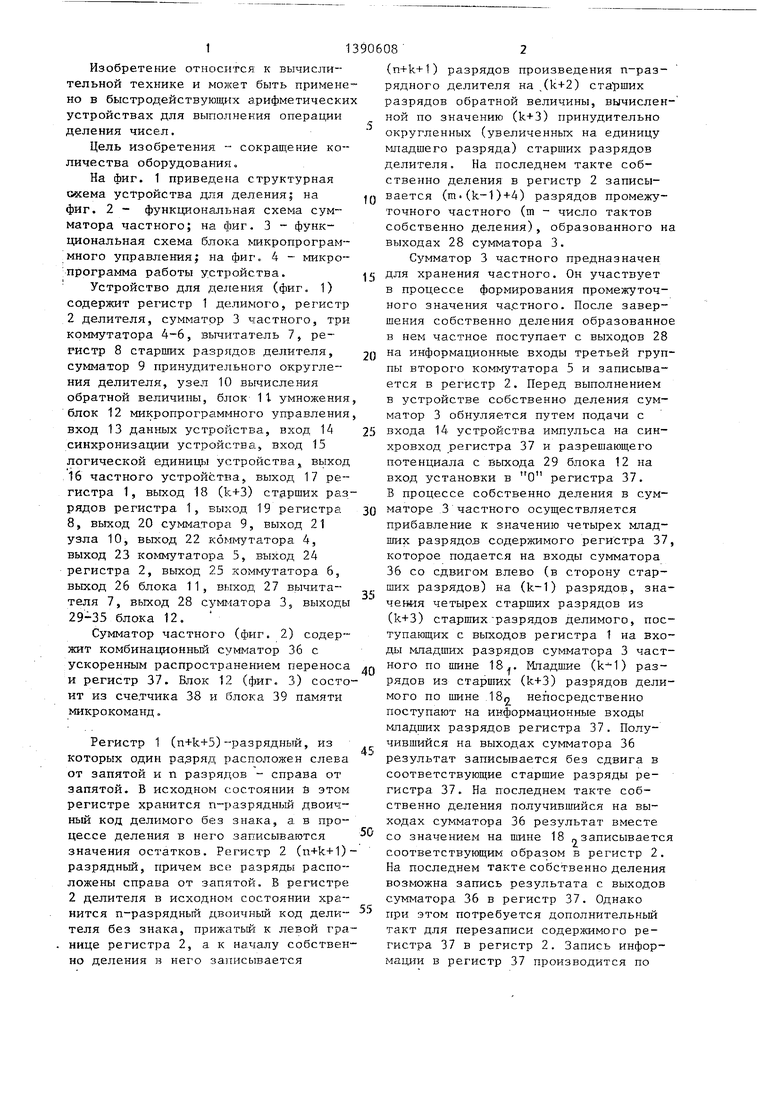

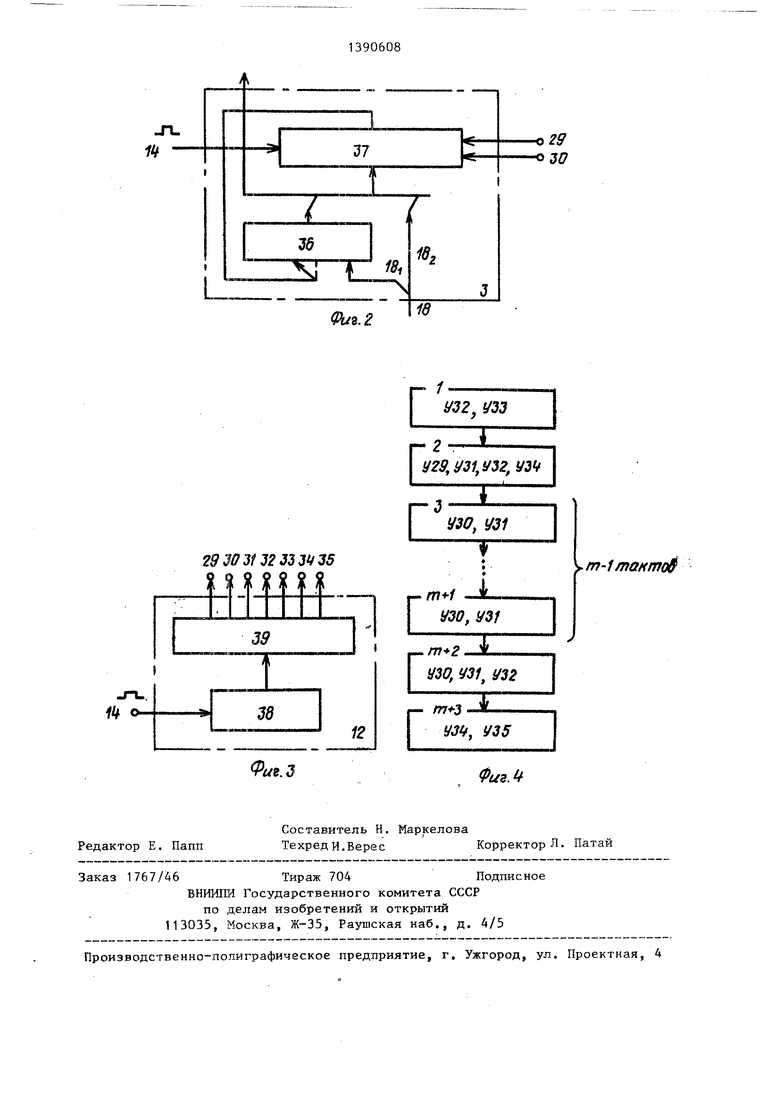

На фиг. 1 приведена структурная сжема устройства для деления; на фиг. 2 - функцконгшьная схема сумматора частного; HSI фиг. 3 - функциональная схема блока ш кpoпpoгpaм- много управления; на фиг. 4 - микро- программа работы устройства. Устройство для деления (фиг. 1) содержит регистр 1 делимого, регистр 2 делителя, сумматор 3 частного, три коммутатора 4-6, вьгаитатель 7, регистр 8 старших разрядов делителя, сумматор 9 принудительного округления делителя, узел 10 вычисления обратной величины, блок 11 умножения блок 12 микропрограммного управления вход 13 данных устройства, вход 14 синхронизации устройства, вход 15 логической единицы устройства, выход 16 частного устройства, выход 17 регистра 1, выход 18 (k+3) разрядов регистра 1, выход 19 регистра 8, выход 20 сумматора 9, выход 21 узла 10, выход 22 коммутатора 4, выход 23 коммутатора 5, выход 24 регистра 2, выход 25 коммутатора 6, выход 26 блока 11, выход 27 вычита- теля 7, выход 28 сум1-штора 3, выходы 29-35 блока 12.

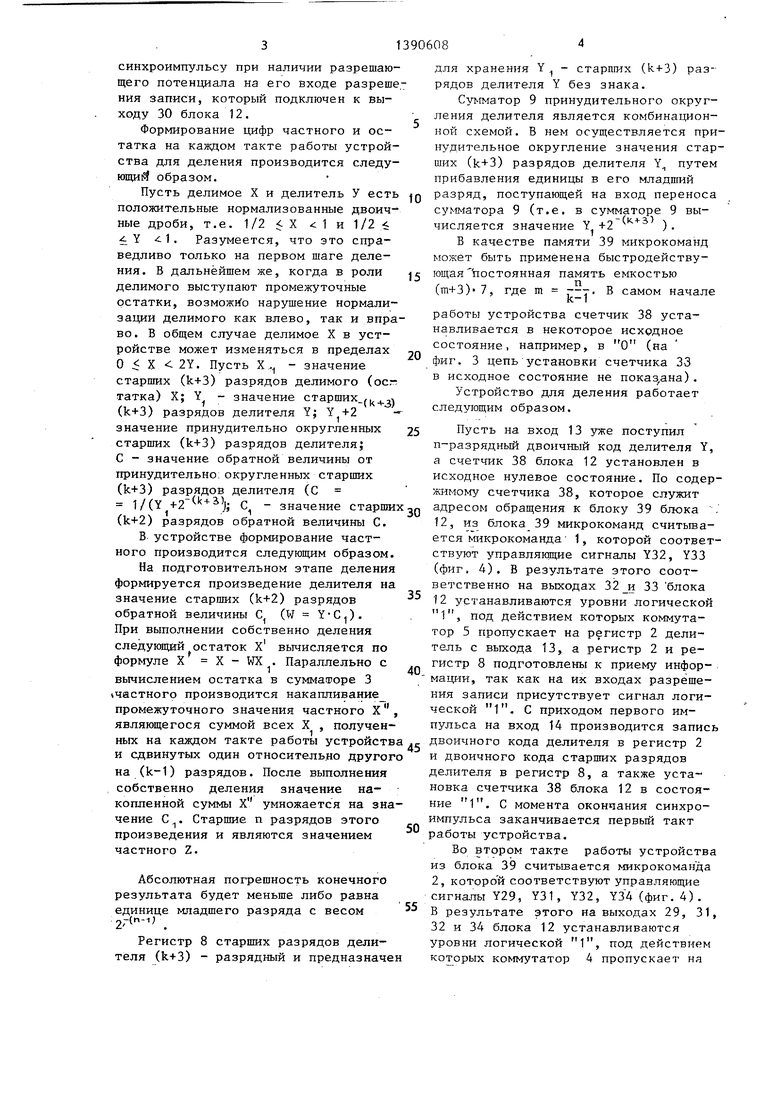

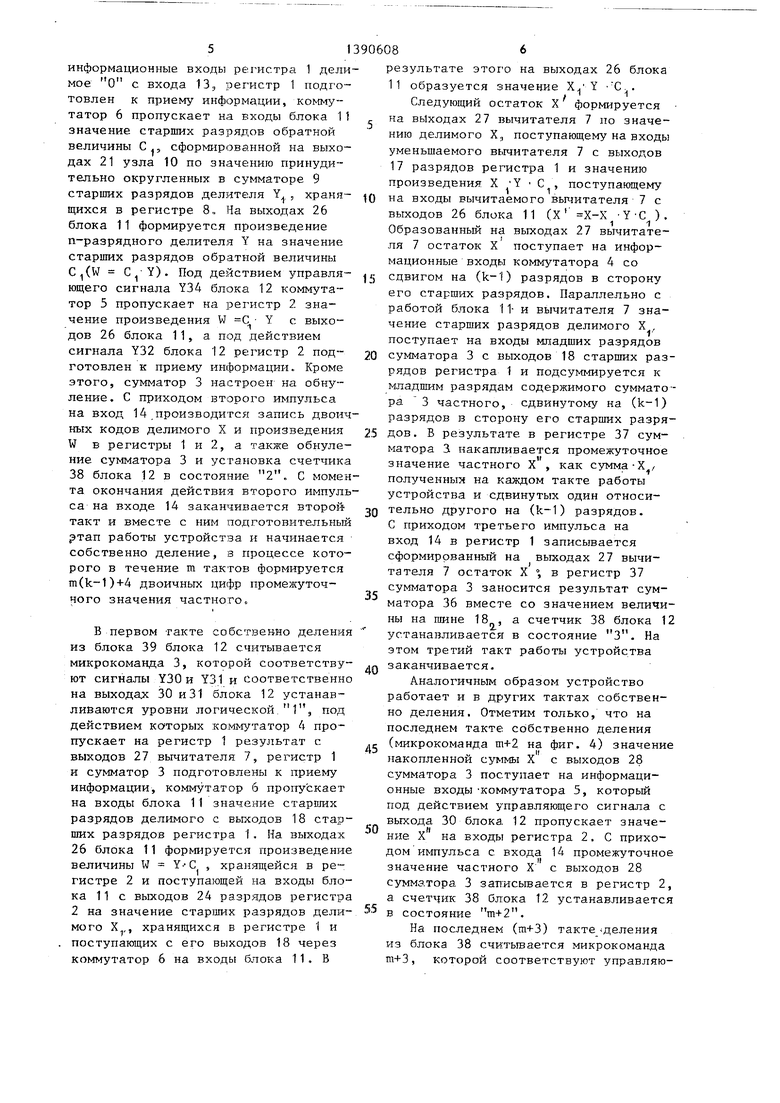

Сумматор частного (фиг. 2) содержит комбинационный сумматор 36 с ускоренным распространением переноса и регистр 37. Блок 12 (фиг. 3) состоит из сче.тчика 38 и блока 39 памяти микрокоманд,

Регистр 1 (n+k+5)-разрядный, из которых один разряд расположен слева от запятой и п разрядов - справа от запятой. В исходном состоянии S этом регистре хранится п-разрядный двоичный код делимого без знака, а в процессе деления в нет-о записываются значения остатков. Регистр 2 (n+k+1)- разрядный, причем все разрядь( расположены справа от запятой. В регистре 2 делителя в исходном состоянии хранится п-разрядный двоичный код дели- теля без знака, прижатый к левой границе регистра 2, а к началу собственно деления в него записывается

(n+k+1) разрядов произведения п-раз- рядного делителя на (k+2) старших разрядов обратной величины, вычислен- ной по значению (k+3) принудительно округленных (увеличенных на единицу младшего разряда) старших разрядов делителя. На последнем такте собственно деления в регистр 2 записыQ вается (m.(k-1)) разрядов промежуточного частного (т - число тактов собственно деления), образованного на выходах 28 сумматора 3.

Сумматор 3 частного предназначен

ij для хранения частного. Он участвует в процессе формирования промежуточного значения ча.стного. После завершения собственно деления образованное в нем частное поступает с выходов 28

0 на информационные входы третьей группы второго коммутатора 5 и записывается в регистр 2. Перед выполнением в устройстве собственно деления сумматор 3 обнуляется путем подачи с

5 входа 14 устройства импзшьса на син- хровход регистра 37 и разрешающего потенциала с вьгхода 29 блока 12 на вход установки в О регистра 37. В процессе собственно деления в сум0 маторе 3 частного осуществляется

прибавление к значению четырех младших разрядов содержимого регистра 37, которое подается на входы сумматора 36 со сдвигом влево (в сторону старших разрядов) на (k-1) разрядов, зна- чевия четырех старших разрядов из (k+3) старших-разрядов делимого, поступающих с выходов регистра 1 на входы младших разрядов сумматора 3 частQ ного по шине 18,. Младшие () разрядов из старших (k+3) разрядов делимого по шине .IB непосредственно

5

5

0

поступают на информационные входы младших разрядов регистра 37. Получившийся на выходах сумматора 36 результат записывается без сдвига в соответствующие старшие разряды регистра 37. На последнем такте собственно деления получившийся на выходах сумматора 36 результат вместе со значением на шине 18 „записываете соответствующим образом в регистр 2. На последнем такте собственно деления возможна запись результата с выходов сумматора 36 в регистр 37. Однако при этом потребуется дополнительный такт для перезаписи содержимого регистра 37 в регистр 2. Запись информации в регистр 37 производится по

синхроимпульсу при наличии разрешающего потенциала на его входе разрешения записи, который подключен к выходу 30 блока 12.

Формирование цифр частного и остатка на каждом такте работы устройства для деления производится следующий образом.

Пусть делимое X и делитель У есть положительные нормализованные двоичные дроби, т.е. 1/2 Х 1 и 1/2 Y 1. Разумеется, что это справедливо только на первом шаге деления. В дальнейшем же, когда в роли делимого выступают промежуточные остатки, возможно нарушение нормализации делимого как влево, так и вправо. В общем случае делимое X в устройстве может изменяться в пределах

20

работы устройства счетчик 38 устанавливается в некоторое исходное состояние, например, в О (на фиг. 3 цепь установки счетчика 33

О X 2Y. Пусть X.. - значение

старших (k+3) разрядов делимого (осг исходное состояние не показ ана) .

Устройство для деления работает следующим образом.

татка) X; Y - значение старших,|,, (k+3) разрядов делителя Yj Y +2 - значение принудительно округленных старших (k+3) разрядов делителя; С - значение обратной величины от принудительно; округленных старших (k+3) разрядов делителя (С 1/(Y С - значение старши (k+2) разрядов обратной величины С.

В устройстве формирование частного производится следующим образом.

На подготовительном этапе деления формируется произведение делителя на значение старших (k+2) разрядов обратной величины С (W Y-C). При выполнении собственно деления

следующий остаток X вычисляется по формуле X X - WX . Параллельно с

вычислением остатка в сумматоре 3 частного производится накаш1ивание промежуточного значения частного х, являющегося суммой всех X , полученных на каждом такте работы устройства и сдвинутых один относительно другого на (k-1) разрядов. После выполнения собственно деления значение на-

для хранения Y - старших (k+3) разрядов делителя Y без знака.

Сумматор 9 принудительного округления делителя является комбинационной схемой. В нем осуществляется принудительное округление значения старших (k+3) разрядов делителя Y путем прибавления единицы в его младший разряд, поступающей на вход переноса сумматора 9 (т.е. в сумматоре 9 вычисляется значение Y +2 ).

В качестве памяти 39 микрокоманд может быть применена быстродействующая постоянная память емкостью (т+3) 7, где m --т- В самом начале

К. I

работы устройства счетчик 38 устанавливается в некоторое исходное состояние, например, в О (на фиг. 3 цепь установки счетчика 33

исходное состояние не показ ана) .

5 п

5

0.

5

Устройство для деления работает следующим образом.

Пусть на вход 13 уже поступил п-разрядный двоичный код делителя Y, а счетчик 38 блока 12 установлен в исходное нулевое состояние. По содержимому счетчика 38, которое служит адресом обращения к блоку 39 блока . 12, из блока 39 микрокоманд считьша- ется микрокоманда 1, которой соответствуют управляющие сигналы Y32, Y33 (фиг. 4). В результате этого соответственно на выходах 32 и 33 блока 12 устанавливаются уровни логической 1, под действием которых коммутатор 5 пропускает на регистр 2 делитель с выхода 13, а регистр 2 и регистр 8 подготовлены к приему информации, так как на ик входах разрешения записи присутствует сигнал логической 1. С приходом первого импульса на вход 14 производится запись двоичного кода делителя в регистр 2 и двоичного кода старших разрядов делителя в регистр 8, а также установка счетчика 38 блока 12 в состоя

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1985 |

|

SU1357946A1 |

| Устройство для деления | 1990 |

|

SU1728862A1 |

| Устройство для деления | 1985 |

|

SU1322264A1 |

| Устройство для деления | 1988 |

|

SU1520510A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018933C1 |

| Устройство для деления | 1986 |

|

SU1357947A1 |

| Устройство для деления | 1991 |

|

SU1783523A1 |

| Устройство для деления | 1986 |

|

SU1429110A1 |

| Устройство для деления | 1989 |

|

SU1667060A1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

.Изобретение относится к вычислительной технике и может быть применено для быстрого деления чисел в любой позиционной системе счисления. Целью изобретения является сокращение количества оборудования, необходимого для реализации устройства. Для этого в устройстве входыумладших разрядов сумматора 3 частного соединены с вторым информационным входом коммутатора 6, а третий информационный вход коммутатора 5 соединен с выходами сумматора частного, что позволяет исключить второй блок умножения в устройстве, содерз ащем регистры 1, 2 делимого и делителя, коммутатор 4, вычитатель 7, регистр 8 старших разрядов делителя, сумматор 9 принудительного округления, узел 10 вычисления обратной величины, блок 11 умножения. 4 ил. (Л

копленной суммы Х умножается на зна- ние 1

импуль

чение С . Старшие п разрядов этого произведения и являются значением частного Z.

Абсолютная погрешность конечного результата будет меньше либо равна единице младшего разряда с весом 2Г(-.

Регистр 8 старших разрядов делителя (k+3) - разрядный и предназначен

ние 1

С момента окончания синхроимпульса заканчивается первый такт

работы устройства.

Во втором такте работы устройства из блока 39 считьшается микрокоманда 2, которой соответствуют управляющие сигналы Y29, Y31, Y32, У3 4(фиг.4).

В результате этого на выходах 29, 31, 32 и 34 блока 12 устанавливаются уровни логической 1, под действием которых коммутатор 4 пропускает на

51390608

информационные входы регистра 1 делимое О с входа 13,, регистр 1 подгоре11

товлен к информадии, коммутатор 6 пропускает на входы блока 11 значение старших разрядов обратной величины С,, сформированной на выходах 21 узла 10 по значению принудительно округленных в сумматоре 9 старших разрядов делителя Y , хран51- щихся в регистре 8. На выходах 26 блока 11 формируется произведение п-разрядного делителя Y на значение старших разрядов обратной величины C(W С Y). Под действием управляющего сигнала Y34 блока 12 коммутатор 5 пропускает на регистр 2 значение произведения W С Y с выходов 26 блока 11, а под действием сигнала Y32 блока 12 регистр 2 подготовлен к приему информации. Кроме этого, сумматор 3 настроен на обнуление, С приходом второго импульса на вход 14 .производится запись двоичных кодов делимого X и произведения W в регистры 1 и 2, а также обнуление сумматора 3 и установка счетчика 38 блока 12 в состояние 2. С момента окончания действия второго импульса на входе 14 заканчивается второй такт и вместе с ним подготовительный ртап работы устройства и начинается собственно деление, в процессе которого в течение m тактов формируется m(k-1)+4 двоичных цифр промежуточного значения частного.

В первом такте собственно деления из блока 39 блока 12 считывается микрокоманда 3, которой соответствуют сигналы Y30 и Y31 и соответственно на выходах 30 и 31 блока 12 устанавливаются уровни логической., под действием каторых коммутатор 4 пропускает на регистр 1 результат с выходов 27 вьгаитателя 7, регистр 1 и сумматор 3 подготовлены к приему информации, коммутатор 6 пропускает на входы блока 11 значение старших разрядов делимого с въгходов 18 старших разрядов регистра 1. На выходах 26 блока 11 формируется произведение величины W Y--С , хранящейся в регистре 2 и поступающей на входы блока 1 1 с выходов 24 разрядов регистра 2 на значение старших разрядов делимого Х,, хранящихся в регистре 1 и . поступающих с его выходов 18 через коммутатор 6 на входы блока 11, В

результате этого на выходах 26 блока 11 образуется значение X/ Y С;.

t ч

Следующий остаток X формируется

на выходах 27 вычитателя 7 по значению делимого Х,| поступающему на входы уменьшаемого вычитателя 7 с выходов 17 разрядов регистра 1 и значению произведения X Y С , поступающему

на входы вычитаемого вычитателя 7 с выходов 26 блока 11 (X Х-Х -Y-C ). Образованный на выходах 27 вычитателя 7 остаток X поступает на информационные входы коммутатора 4 со

сдвигом на (k-1) разрядов в сторону его старших разрядов. Параллельно с работой блока 11- и вычитателя 7 значение старших разрядов делимого X поступает на входы младших разрядов

сумматора 3 с выходов 18 старших разрядов регистра 1 и подсуммируется к младшим разрядам содержимого сумматора 3 частного, сдвинутому на (k-1) разрядов в сторону его старших разрядов. В результате в регистре 37 сумматора 3 накапливается промежуточное значение частного х, как сумма-Х / полученныз{ на каждом такте работы устройства и сдвинутых один относительно другого на (k-1) разрядов. С приходом третьего импульса на вход 14 в регистр 1 записывается сформированный на выходах 27 вычитателя 7 остаток X ° в регистр 37 сумматора 3 заносится результат сумматора 36 вместе со значением величины на шине 18 , а счетчик 38 блока 12 устанавливается в состояние 3. На этом третий такт работы устройства заканчивается.

Аналогичным образом устройство работает и в других тактах собственно деления. Отметим только, что на последнем такте собственно деления (микрокоманда т+2 на фиг. 4) значение накопленной суммы X с выходов 28 сумматора 3 поступает на информационные входы -коммутатора 5, который под действием управляющего сигнала с выхода 30 блока 12 пропускает значе

ние X на входы регистра 2. С приходом импульса с входа 14 промежуточное значение частного X с выходов 28 сумматора. 3 записьгоается в регистр 2, а счетчик 38 блока 12 устанавливается в состояние т+2.

На последнем (т+3) такте-деления из блока 38 считьгоается микрокоманда т+3, которой соответствуют управляю71390608

ие сигналы Y34 и Y35 и соответстенно на выходах 34 и 35 блока 12 станавливаются уровни логической 1. Под действием этих управляющих игналов коммутатор 6 пропускает на ходы блока 11 значение старших разядов обратной величины С , На выхоах 26 блока 11 формируется произвеение Х-С , старшие и разрядов кото- ю

ст вы ум та инф му пе ко го со со вх уп с ча ро вы уп уп то сум ты упр ре дел вы лен за ли вто ющи уп тор пр вы нак от с ц руд вхо вых цио ро ным тре мут бло вых жен ус дов

рого являются значением частного Z и поступают на выход 16 частного устройства. При этом уровень логической 1, установленный на седьмом выг ходе 35 блока 12, сигнализирует об окончании операции деления в устройстве.

Фо, рмула Изобретения

Устройство для деления , содержаще регистры делимого и делителя, сумматор частного, три коммутатора, вычя- татель, регистр старших разрядов делителя, сумматор принудительного окг ругления делителя, узел вычисления обратной величины, блок умножения и блок микропрограммного управления, причем вход данных устройства соединен с информационным входом регистра старших разрядов делителя и первыми информационными входами первого и второго коммутаторов, выходы которых соединены с информационными входами регистров делимого и делителя соответственно, синхровходы которых соединены с синхровходами сумматора частного блока микропрограммного управления, входом синхронизации устройства и регистра старших разрядов делителя, выход которого соединен с информационньм входом сумматора при- нудительного округления делителя, вход переноса которого является входом логической единицы устройства, выход сумматора принудительного округления делителя соединен с входом узла вычисления обратной величит ны, выход которого соединен с первым информационным входом третьего коммутатора, второй информационньй вход которого соединен с выходом

5

0

5

0

5

0

5

0

старших разрядов регистра делимого, выход которого соединен с входом уменьшаемого вычитателя, вход вычитаемого которого соединен с вторым информационным входом второго коммутатора и выходом блока умножения, первый и второй информационные входы которого соединены с выходами третьего коммутатора и регистра делителя соответственно, выход вычитателя соединен с вторым информационным входом первого коммутатора, первьй управляющий вход которого соединен с входом установки в О сумматора частного и первым выходом блока микропрограммного управления, второй выход которого соединен с вторым управлянщим входом первого и первым управляющим входом третьего коммутагс торов и входом разрешения записи сумматора частного, третий и /четверг тый выходы блока микропрограммного управления соединены с входами разрешения записи регистров делимого и делителя соответственно, пятьй выход блока микропрограммного управления соединен с входом разрешения : записи регистра старших разрядов де-- лителя и первым управляющим входом второго коммутатора, второй управляющий вход которого соединен с вторым управляющим входом третьего коммутатора и шестым выходом блока микропрограммного управления, седьмой выход которого является выходом признака окончания деления устройства, отличающееся тем, что, с целью сокращения количества оборудования, третий информационньш вход второго коммутатора соединен с выходом сумматора частного, информационный вход младших разрядов которого соединен с вторым информационным входом третьего коммутатора, третий управляющий вход второго коммутатора соединен с вторым выходом блока микропрограммного управления, выход п старших разрядов блока умножения является выходом частного устройства (п - разрядность операндов) .

| Патент США № 3234367, кл, 235-156, 1962 | |||

| Устройство для деления | 1985 |

|

SU1357946A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-04-23—Публикация

1986-03-19—Подача