sj

00 GO СЛ

кэ ы

Изобретение относится к вычислительной технике и может быть применено в быстродействующих арифметических устройствах для выполнения операции деления чисел.

Известно устройство для деления, формирующее в каждом такте цифр частного

(где 2 К т; . п - разрядность делимого

и делителя) и содержащее два регистра остатка, регистр делителя, сумматор частного, сумматор принудительного округления делителя, узел вычисления обратной величины, два сумматора, два блока умножения, вычитатель, элемент И-НЕ, два коммутатора и блок микропрограммного управления. Основным недостатком этого устройства является низкое быстродействие, вызванное большой длительностью такта формирования цифр частного и остатка.

Известно устройство для деления, формирующее в каждом такте цифр частного

(где 2 , п- разрядность делимого

,11--L г

и делителя) и содержащее два регистра остатка, регистр делителя, сумматор частного, сумматор принудительного округления делителя, узел вычисления обратной величины, два сумматора, два блока умножения, коммутатор, селектор, вычитатель, элемент НЕ и блок микропрограммного управления. Хотя быстродействие этого устройства несколько выше по сравнению с рассмотренным ранее, но и оно недостаточно высокое из-за относительно большой длительности такта, в случае, когда на входе данных устройства одновременно присутствуют п-раз- рядные двоичные коды делимого X и делителя Y и загружаются в первый регистр остатка и регистр делителя одновременно. Наиболее близким по технической сущности к изобретению является устройство для деления, формирующее в каждом такте

цифр частного (где 2 К j ту I n - разрядность делимого и делителя) и содержащее два регистра остатка, регистр делителя, регистр обратной величины, сумматор частного, сумматор принудительного округления, узел вычисления обратной величины, два сумматора, два блока умножения, коммутатор, селектор, вычитатель, элемент НЕ и блок микропрограммного управления, причем вход данных устройства соединен с информационным входом регистра делителя и с первым информационным входом коммутатора, выход которого соединен с информационным входом первого регистра остатка, выходы первого и второго регистров остатка соединены с первым и вторым

информационными входами первого сумматора соответственно, выход которого является выходом остатка устройства и соединен с входом уменьшаемого вычитателя, входы вычитаемого и заема которого соединены выходами первой и второй групп первого блока умножения соответственно, первый информационный вход первого блока умножения соединен с выходом

0 регистра, выходы разности и заема вычита- теля соединены с вторым информационным входом коммутатора и информационным входом второго регистра остатка соответственно, выходы старших разрядов первого и

5 второго регистров остатка соединены с первым и вторым информационными входами второго сумматора соответственно, выход младших разрядов которого соединен с первым информационным входом второго бло0 ка умножения, выход старшего разряда второго сумматора соединен с входом элемента НЕ, выход которого соединен с управляющимвходомселектора, информационный вход которого соединен с

5 выходом второго блока умножения, выход селектора соединен с информационным входом младших разрядов сумматора частного и с вторым информационным входом первого блока умножения, выход старших

0 разрядов делителя входа данных устройства соединен с информационным входом сумматора принудительного округления делителя, вход переноса которого соединен с входом логической единицы устройства, вы5 ход сумматора принудительного округления делителя соединен с информационным входом узла вычисления обратной величины, выход которого соединен с информационным входом регистра обратной величины,

0 выход которого соединен с вторым информационным входом второго блока умножения, вход синхронизации устройства соединен с синхровходами первого и второго регистров остатка, регистра делителя, ре5 гистра обратной величины, сумматора частного и блока микропрограммного управления, первый выход которого соединен с входом разрешения записи регистра делителя, регистра обратной величины, с пер0 вым управляющим входом коммутатора и входом установки в нуль второго регистра остатка и сумматора частного, выход которого является выходом частного устройства, второй выход блока микропрограммного уп5 равления соединен с вторым управляющим входом коммутатора и входами разрешения записи второго регистра остатка и сумматора частного, третий выход блока микропрог раммного управления соединен с входом разрешения записи nepeot о регистра оста г

ка, четвертый выход блока микропрограммного управления является выходом признака окончания деления устройства. Недостаток известного устройства - относительно низкое быстродействие, вызванное достаточно большой длительностью такта формирования к цифр частного.

Цель изобретения - повышение быстродействия устройства за счет сокращения длительности такта формирования к цифр частного, Оно достигается тем, что на длительности такта не влияет задержка селектора и устранена задержка вычитателя.

Поставленная цель достигается тем, что в устройство для деления, содержащее два регистра остатка, регистр делителя, регистр обратной величины, сумматор частного, сумматор принудительного округления делителя, узел вычисления обратной величины, два сумматора, блок умножения, коммутатор, селектор, элемент НЕ и блок микропрограммного управления, причем вход данных устройства через шину данных устройства соединён с информационным входом регистра делителя и с первым информационным входом коммутатора, выход которого соединен с информационным входом первого регистра остатка, выходы первого и второго регистров остатка соединены с первым и вторым информационными входами первого сумматора соответственно, выход которого является выходом остатка устР°йства, выходы старших разрядов первого и второго регистров остатка соединены с первым и вторым информационными входами второго сумматора соответственно, выход младших разрядов которого соединен с первым информационным входом блока умножения, выход старшего разряда сумматора соединен с управляющим входом селектора, информационный вход которого соединен с выходом блока умножения, выход селектора соединен с информационным входом младших разрядов сумматора частного, выход старших разрядов делителя через шину данных устройства соединен с информационным входом сумматора принудительного округления делителя, вход логической единицы устройства соединен с входом переноса сумматора принудительного округления делителя, выход которого соединен с информационным входом узла вычисления обратной величины, выход которого соединен с информационным входом регистра обратной величины, выход которого соединен с вторым информационным входом блока умножения, вход синхронизации устройства соединен с синхровходами первого и второго регистров остатка, регистра делителя, регистра

обратной величины, сумматора частного и блока микропрограммного управления, первый выход которого соединен с входом раз- решения записи регистра делителя, 5 регистра обратной величины, с первым управляющим входом коммутатора и входом установки в нуль второго регистра остатка и сумматора частного, выход которого является выходом частного устройства, второй вы0 ход блока микропрограммного управления соединен с вторым управляющим входом коммутатора и входами разрешения записи второго регистра остатка и сумматора частного, третий выход блока микропрограмм5 ного управления соединен с входом разрешения записи первого регистра остатка, четвертый выход блока микропрограммного управления является выходом признака окончания деления устройства,

0 введены управляемый формирователь частичных произведений и блок суммирования, причем выход регистра делителя соединен с первым информационным входом управляемого формирователя частичных произ5 ведений, выход блока деления усеченных чисел соединен с вторым информационным входом управляемого формирователя частичных произведений, управляющий вход которого соединен с выходом элемента НЕ,

0 выход первого сумматора соединен с первым информационным входом блока суммирования, второй информационный вход блока суммирования соединен с выходом управляемого формирователя частичных

5 произведений, выходы сумм и переносов блока суммирования соединены с вторым информационным входом коммутатора и информационным входом второго регистра остатка соответственно. Устройство для де0 ления содержит отличительные признаки, не обнаруженные ни в одном из известных устройств - наличие управляемого формирователя частичных произведений и блока суммирования с соответствующими связя5 ми. Эти признаки позволяют повысить быстродействие устройства-прототипа за счет сокращения длительности такта формирования к цифр частного. Таким образом, так как в заявляемом техническом решении

0 имеются отличительные признаки, обеспечивающие достижение поставленной цели и не обнаруженные ни в одном другом известном аналогичном техническом решении, то оно соответствует критерию существен5 ные отличия.

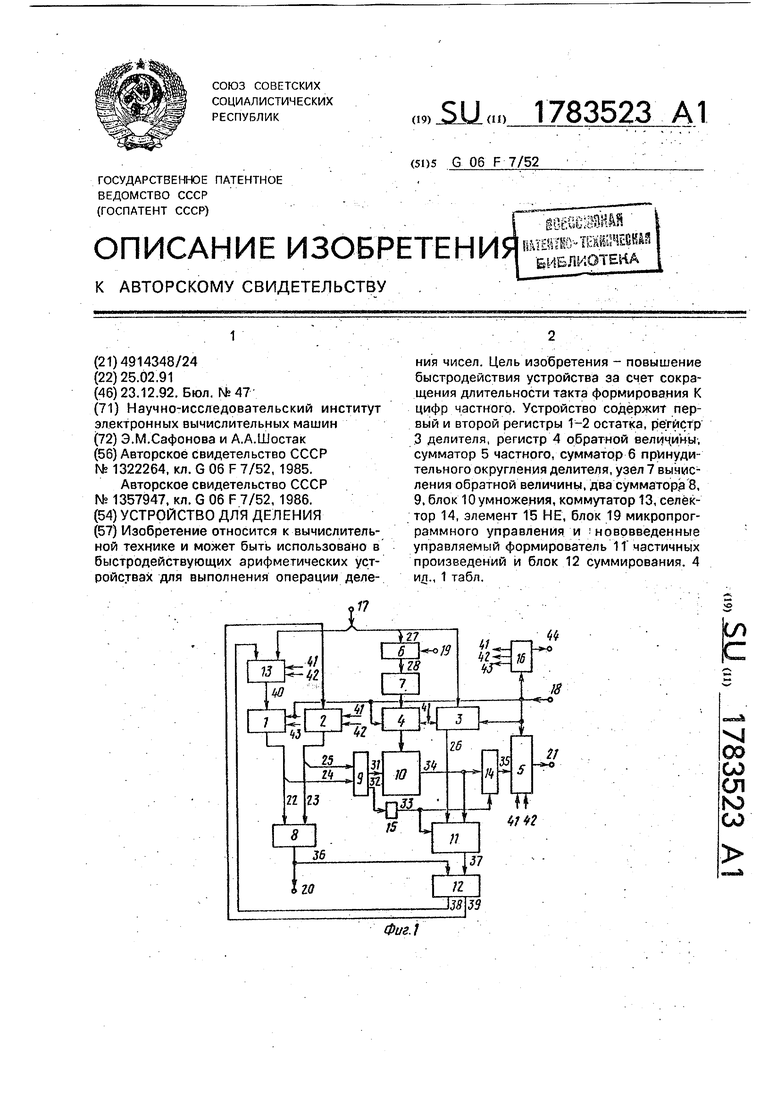

На фиг.1 приведена структурная схема устройства для деления; на фиг.2 - функциональная схема управляемого формирователя частичных произведений; на фиг.З - микропрограмма работы устройства; на

фиг.4 - функциональная схема блока микропрограммного управления.

Устройство для деления содержит (фиг.1) первый 1 и второй 2 регистры остатка, регистр 3 делителя, регистр 4 обратной величины, сумматор 5 частного, сумматор 6 принудительного округления делителя, узел 7 вычисления обратной величины, первый и второй сумматоры 8,9 соответственно, блок 10 умножения, управляемый формирователь 11 частичных произведений, блок 12 суммирования, коммутатор 13, селектор 14, элемент НЕ 15, блок 16 микропрограммного управления, вход 17 данных устройства, вход 18 синхронизации устройства, вход 19 логической единицы устройства, выходы 20 и 21 соответственно остатка и частного устройства, выходы 22 и 23 регистров 1 и 2, выходы 24, 25 старших разрядов регистров соответственно 1 и 2; выход 26 регистра 3, выход 27 старших разрядов делителя входа 17 данных устройства, выход 28 сумматора б, выход 29 узла 7 вычисления обратной величины, выход 30 регистра 4, выход 31 младших разрядов и выход 32 старшего разряда сумматора 9, выход 33 элемента НЕ 15, выход 34 блока 10 умножения, выход 35 селектора 14, выход 36 первого сумматора 8, выход 37 управляемого формирователя 11 частичных произведений, первый 38 и второй 39 выходы блока 12 суммирования, выход 40 коммутатора 13, выходы 41-44 с первого по четвертый блока 16 микропрограммного управления соответственно. Вход 17 данных через шину данных устройства соединен с информационным входом регистра 3 делителя и с первым информационным входом коммутатора 13, выход 40 которого соединен с информационным входом первого регистра 1 остатка, выходы 22, 23 первого 1 и второго 2 регистров остатка соединены с первым и вторым информационными входами первого сумматора 8 соответственно, выход 36 которого является выходом 20 остатка устройства и соединен с первым входом блока 12 суммирования, второй вход которого соединен с выходом 37 управляемого формирователя 11 частичных произведений, первый информационный вход управляемого формирователя 11 частичных произведений соединен с выходом 26 регистра 3 делителя, выход 38 сумм и выход 39 переносов блока 12 суммирования соединены с вторым информационным входом коммутатора 13 и информационным входом-второго регистра 2 остатка соответственно, выходы 24, 25 старших разрядов первого 1 и второго 2 регистров остатка соединены с первым и вторым информационными входами второго сумматора 9 соответственно, выход 31 младших разрядов которого соединен с первым информационным входом блока 10 умножения, выход 32 старшего разряда второго сумматора 9 соединен с входом элемента 15 НЕ, выход 33 которого соединен с управляющим входом селектора 14 и управляющим входом управляемого формирователя 11 частичных произведений, выход 34 блока 10 умножения

0 соединен с информационным входом селектора 14 и с вторым информационным входом управляемого формирователя 11 частичных произведений, выход 35 селектора 14 соединен с информационным входом

5 младших разрядов сумматора 5 частного, выход 27 старших разрядов делителя через шину данных устройства соединен с информационным чходом сумматора 6 принудительного округления делителя, вход 19

0 логической единицы устройства соединен с входом переноса сумматора 6 принудительного округления делителя, выход 28 которого соединен с входом узла 7 вычисления обратной величины, выход 29 которого сое5 динен с информационным входом регистра 4 обратной величины, выход 30 которого соединен с вторым информационным входом блока 10 умножения, вход 18синхрони- з ации устройства соединен с

0 синхровходами первого 1 и второго 2 регистров остатка, регистра 3 делителя, регистра 4 обратной величины, сумматора 5 частного и блока 16 микропрограммного управления, первый выход 41 которого соеди5 нен с входом разрешения записи регистра 3 делителя, регистра 4 обратной величины, с первым управляющим входом коммутатора 13 и входом установки в нуль второго регистра 2 и сумматора 5 частного, выход

0 которого является выходом 21 частного устройства, второй выход 42 блока 16 микропрограммного управления соединен с вторым управляющим входом коммутатора 13, входами разрешения записи второго ре5 гистра 2 остатка и сумматора 5 частного, третий выход 43 блока 16 микропрограммного управления соединен с входом разрешения записи первого регистра 1 остатка, четвертый выход 44 блока 16микропрограм0 Много управления является выходом признака окончания деления устройства. Рассмотрим функциональное значение и реализацию основных узлов и блоков предлагаемого устройства для деления. Первый

5 регистр 1 остатка (п+2)-разрядный,. из которых два разряда расположены слева от запятой, а остальные - справа от запятой. В исходном состоянии в разрядах справа от запятой этого регистра хранится п-разряд- ный двоичный код делимого без знака, а в

процессе деления в него с выхода 38 блока 12 записываются значения сумм очередных остатков. Второй регистр 2 остатка содержит (n-И) разрядов, из которых два располо- жены слева от запятой, а остальные - справа от запятой. В исходном состоянии этот регистр обнулен, а в процессе деления в него с выхода 39 блока 12 записываются значения переносов очередных остатков.

Регистр 3 делителя n-разрядный, причем все разряды расположены справа от запятой. В регистре 3 делителя в исходном состоянии и в процессе деления хранится n-разрядный двоичный код делителя без знака.

Регистр 4 обратной величины - (k-f-2)- разрядный, из которых один разряд расположен слева от запятой, а остальные - справа. Регистр 4 предназначен для хранения () старших разрядов обратной величины принудительно округленного усеченного делителя, поступающих с выхода 29 узла 7 вычисления обратной величины. Предполагается., что все регистры устройства реализованы на двухтактных синхронных DV триггерах, Запись информации в регистры производится по синхроимпульсу при наличии разрешающего потенциала на V- входах, Сумматор 5 частного предназначен для хранения частного. Он также участвует в операции деления в процессе формирования правильного частного, В первом такте деления сумматор 5 частного обнуляется путем подачи синхроимпульса с входа 18 синхронизации устройства на его синхровход и разрешающего потенциала с первого выхода 41 блока 16 микропрограммного управления на вход разрешения установки в нуль сумматора Б частного. Во всех остальных тактах работы устройства в сумматоре 5 частного накапливателя значение частного. Для этого к значению частного, сформированному на предыдущих тактах работы устройства и сдвинутому на разрядов влево (в сторону старших разрядов), прибавляется значение k цифр частного, сформиро- ванных на выходе 35 селектора 14 в текущем такте. Запись информации в сумматор 5 частного осуществляется по синхро- импульсу при наличии разрешающего потенциала на его входе разрешения записи, который подключен к второму выходу 42 блока 16 микропрограммного управления. После завершения деления образованное в сумматоре 5 частное поступает на выход 21 частного устройства. Предполагается, что сумматор 5 частного реализован также, как и в устройстве-прототипе, т.е. на комбинационном сумматоре и регистре.

Формирование k цифр частного в каждом такте работы устройства для деления производится путем умножения однорядного кода усеченного остатка, сформированно- 5 го на выходе 31 младших разрядов второго сумматора 9, на значение старших разрядов обратной величины усеченного делителя, хранимое в регистре 4 обратной величины и подаваемое с выходов ЗО регистра 4 обрат0 ной величины. Чтобы устранить возможность получения в устройстве цифр частного с избытком, значение старших разрядов делителя, поступающее с выхода 27 входа 17 устройства, увеличивается на единицу млад5 шего разряда в сумматоре 6 принудительного округления делителя. Пусть делимое X и делитель Y есть нормализованные двоичные дроби, т.е. 1/2 Х 1и1/2 У 1, Это справедливо только в первом такте де0 ления. В дальнейшем, когда в роли делимого выступают промежуточные остатки, возможно нарушение нормализации делимого как влево, так и вправо. В общем случае делимое X в предлагаемом устройстве

5 может изменяться в пределах О Х 2Y. „ Можно показать, что для получения на выходе 35 селектора 14 двоичных цифр частного с точностью до единицы их младшего разряда достаточно обрабатывать (k+4) старших

0 разрядов делимого X (один разряд - слева от запятой, а остальные - справа от запятой), (+3) старших разрядов делителя Y (все разряды расположены справа от запятой) и (k+2) старших разрядов обратной величины

5 принудительно округленного усеченного делителя (один разряд - слева от запятой, а остальные - справа от запятой). Сумматор 6 -(и+3)-разрядный комбинационного типа. В сумматоре 6 осуществляется принудитель0 ное округление делителя путем прибавления к значению (k+З) старших разрядов делител, поступающих на информационный вход сумматора 6 с выхода 27 через шину данных устройства с входа 17 данных,

5 единицы в младший разряд, поступающей на вход переноса сумматора 6 принудительного округления делителя через вход 19 логической единицы устройства. На выходе 28 сумматора 6 принудительного округления

0 делителя образуется +4}-разрядный результат (один разряд - слева от запятой, а остальные - справа от запятой), который далее поступает на информационный вход узла 7 вычисления обратной величины. Узел

5 7 вычисления обратной величины производит вычисление значения (k+2) старших разрядов обратной величины от принудительно округленного значения (k+З) старших разрядов делителя, поступающего на информационный вход узла вычисления обратной величины с выхода 28 сумматора 6 принудительного округления делителя. На выходе 29 узла 7 вычисления обратной величины формируется значение (k+2) старших разрядов обратной величины принудительно округленного усеченного делителя. Узел 7 может быть выполнен в виде комбинационной схемы, реализующей метод деления Стефанел- ли, или же совместно с сумматором б на ПЗУ по соответствующей таблице истинности. С помощью первого сумматора 8 комбинационного типа двухрядный код остатка, хранимый в первом 1 и втором 2 регистрах остатка, преобразуется в однорядный код. Второй сумматор 9 комбинационного типа осуществляет преобразование (k-t-5) старших разрядов двухрядного кода остатка, хранимого в регистрах 1 и 2 остатка, в однорядный код (два разряда - слева от запятой и (к+3)разряда - справа от запятой). На выходе 31 младших разрядов второго сумматора 9 образуется однорядный код (к+4) старших разрядов остатка (один разряд - слева от запятой, (к+3) разрядов - справа от запятой), а на выходе 32 старшего разряда второго сумматора 9 образуется старший дополнительный разряд остатка. В блоке 10 умножения производится умножение значения однорядного кода (к+4) старших разрядов остатка, поступающего на его первый информационный вход с выхода 31 младших разрядов второго сумматора 9 на значение (k+2) старших разрядов обратной величины принудительно округленного усеченного делителя, поступающее на его второй информационный вход с выхода 30 регистра 4 обратной величины. На выходе 34 блока 10 умножения формируется значение к цифр частного. Значение k-разрядного частного, полученного на выходе 35 селектора 14, может быть либо равно значению старших k разрядов частного, получаемого при делении n-разрядных чисел, либо меньше его на единицу младшего разряда с весом . Блок 10 умножения комбинационного типа и может быть разработан хорошо известными методами, например, в виде многослойной структуры с распространением переноса только в последнем слое. В управляемом формирователе 11 частичных произведений осуществляется формирование частичных произведений, получаемых при перемножении значения n-разрядного делителя, хранимого в регистре 3 делителя в прямом коде и поступающего на первый информационный вход управляемого формирователя частичных произведений с выхода 26 регистра 3 делителя и k-разрядного частного, сформированного на выходе 34 блока 10 умножения в прямом коде и поступающего на второй информационный вход управляемого формирователя частичных произведений.

При этом на выходе 37 управляемого формирователя 11 частичных произведений формируется ряд частичных произведений, соответствующих умножению множимого на отрицательный множитель в дополни0 тельном коде без представления множителя в дополнительном коде. В качестве множимого используется n-разрядный делитель. В качестве множител я используются к цифр частного, полученные на выходе 34 блока 10

5 умножения.

На управляющий вход управляемого формирователя 11 частичных произведений поступает сигнал с выхода 33 элемента НЕ 15.

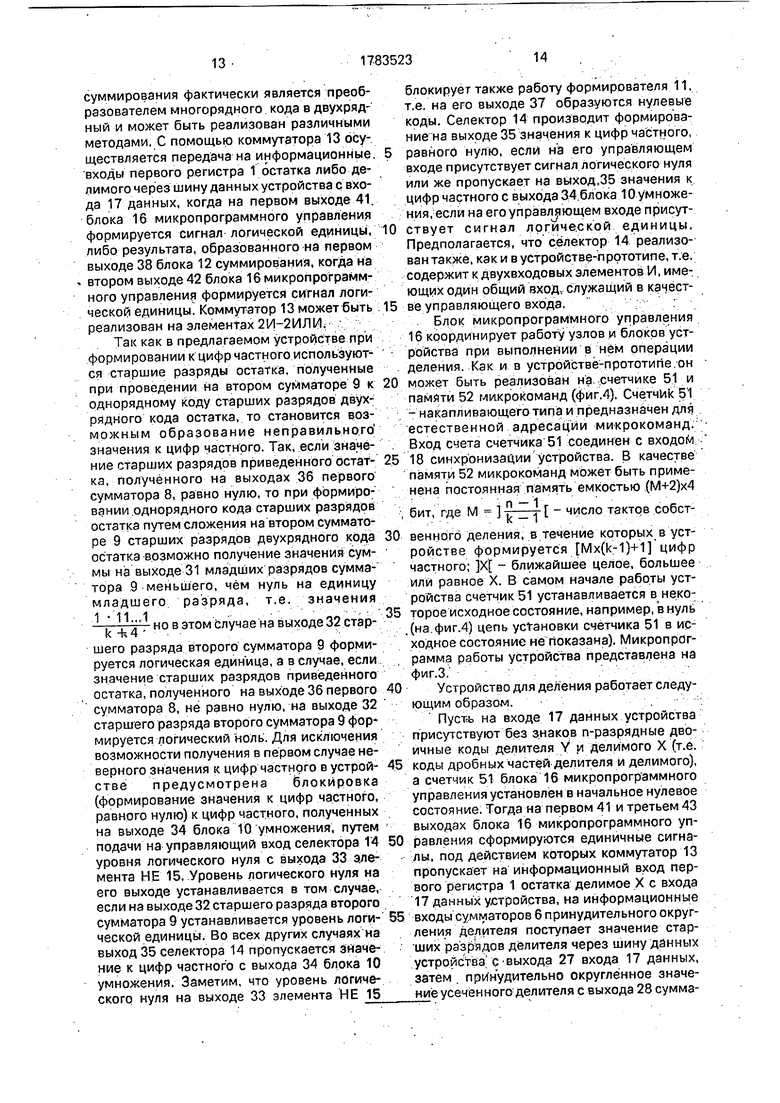

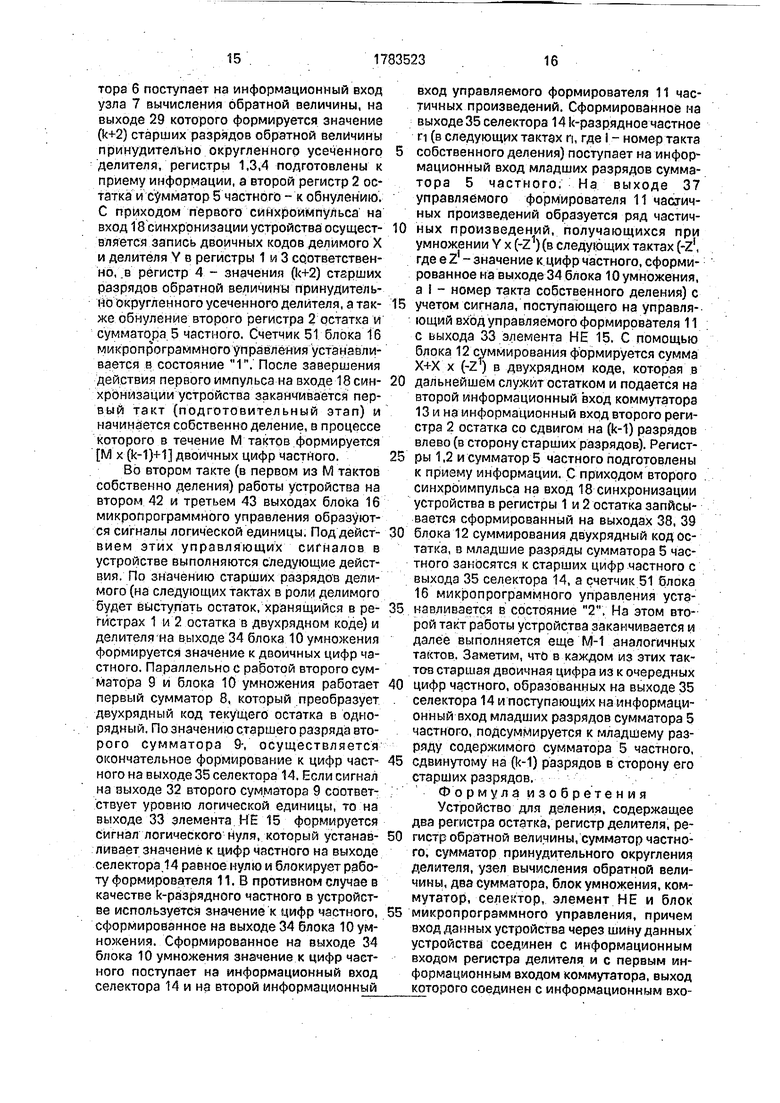

0 На фиг.2 показана функциональная схема управляемого формирователя 11 частичных произведений при k-4. На первый информационный вход формирователя 11с выхода 26 регистра 3 поступает значение

5 n-разрядного делителя, а на второй информационный вход с выхода 34 блока 10 умножения - значение k-разрядного частного в виде , Z2, Za, Z4. Для формирования частичных произведений применяется алго0 ритм умножения на два разряда множителя, начиная с младших разрядов, причем каждое частичное произведение соответствует умножению множимого на два разряда отрицательного множителя в дополнительном

5 коде. На выходе 37 управляемого формирователя 11 частичных произведений при k-4 образуется три частичных произведения. Управляемый формирователь 11 частичных произведений реализован на дешифрато0 pax 45-47 и коммутаторах 48-50.

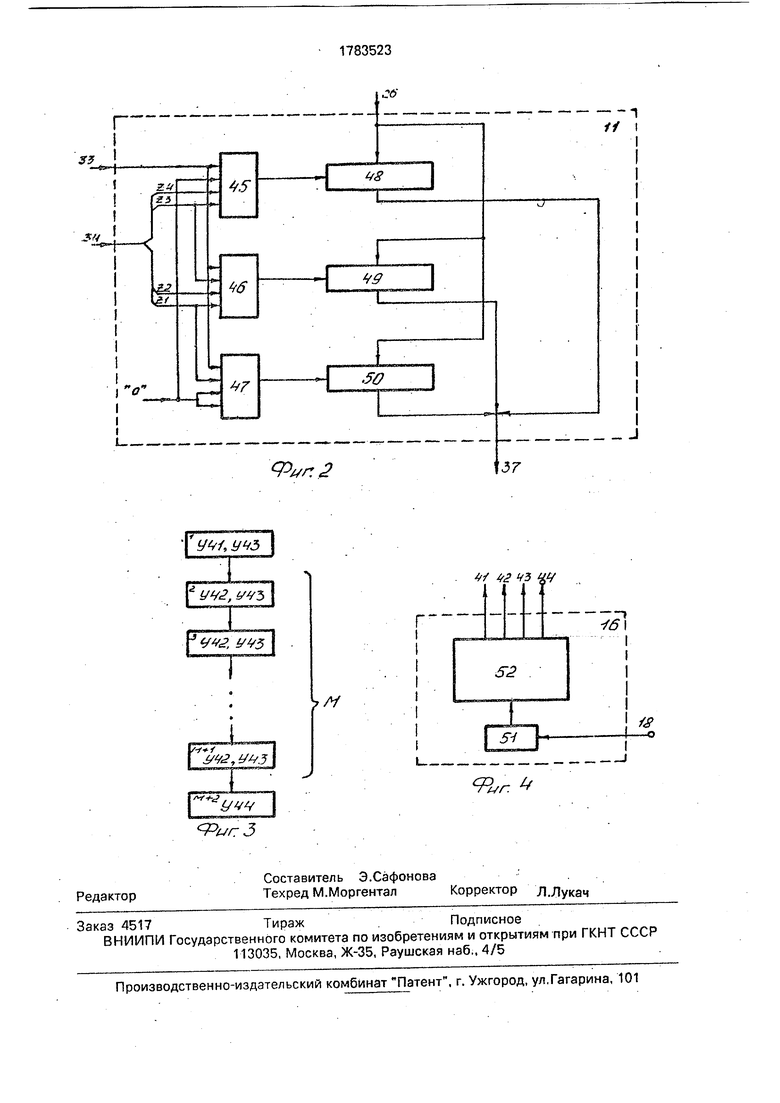

В таблице поясняется формирование частичного произведения на выходе одного из коммутаторов управляемого формирователя 11 в зависимости от расшифровки од5 ной двухразрядной группы разрядов множителя вместе со старшим разрядом соседней младшей группы при единичном или нулевом управляющем сигнале на выходе 33 элемента НЕ 15. С помощью блока 12

0 суммирования осуществляется сложение текущего остатка, сформированного на выходе 36 первого сумматора 8, с рядом частичных произведений, образованных на выходе 37 управляемого формирователя 11

5 частичных произведений и сдвинутых относительно друг друга определенным образом. Результат этого сложения является очередным остатком и получается на выходах сумм 38 и переносов 39 блока 12 суммирования в двухрядном коде. Блок 12

суммирования фактически является преобразователем многорядного кода в двухрядный и может быть реализован различными методами. С помощью коммутатора 13 осуществляется передача на информационные входы первого регистра 1 остатка либо делимого через шину данных устройства с входа 17 данных, когда на первом выходе 41. блока 16 микропрограммного управления формируется сигнал логической единицы, либо результата, образованного на первом выходе 38 блока 12 суммирования, когда на втором выходе 42 блока 16 микропрограммного управления формируется сигнал логической единицы. Коммутатор 13 может быть реализован на элементах 2Й-2ИЛИ.

Так как в предлагаемом устройстве при формировании к цифр частного используются старшие разряды остатка, полученные при проведении на втором сумматоре 9 к однорядному коду старших разрядов двухрядного кода остатка, то становится возможным образование неправильного значения к цифр частного. Так, если значение старших разрядов приведенного остатка, полученного на выходах 36 первого сумматора 8, равно нулю, то при формировании однорядного кода старших разрядов остатка путем сложения на втором сумматоре 9 старших разрядов двухрядного кода остатка возможно получение значения суммы на выходе 31 младших разрядов сумматора 9 меньшего, чем нуль на единицу младшего разряда, т.е. значения

1 11 1

-.-т А. но в этом случае на выходе 32 старшего разряда второго сумматора 9 формируется логическая единица, а в случае, если значение старших разрядов приведенного остатка, полученного на выходе 36 первого сумматора 8, не равно нулю, на выходе 32 старшего разряда второго сумматора 9 формируется логический ноль. Для исключения возможности получения в первом случае неверного значения к цифр частного в устройстве предусмотрена блокировка (формирование значения к цифр частного, равного нулю) к цифр частного, полученных на выходе 34 блока 10 умножения, путем подачи на управляющий вход селектора 14 уровня логического нуля с выхода 33 элемента НЕ 15, Уровень логического нуля на его выходе устанавливается в том случае, если на выходе 32 старшего разряда второго сумматора 9 устанавливается уровень логической единицы. Во всех других случаях на выход 35 селектора 14 пропускается значение к цифр частного с выхода 34 блока 10 умножения. Заметим, что уровень логического нуля на выходе 33 элемента НЕ 15

блокирует также работу формирователя 11, т.е. на его выходе 37 образуются нулевые коды. Селектор 14 производит формирование на выходе 35 значения к цифр частного,

5 равного нулю, если на его управляющем входе присутствует сигнал логического нуля или же пропускает на выход,35 значения к цифр частного с выхода 34 блока 10 умножения, если на его управляющем входе присут0 ствует сигнал логической единицы. Предполагается, что селектор 14 реализован также, как и в устройстве-л рототипе, т.е. содержит к двухвходовых элементов И, имеющих один общий вход, служащий в качест5 ве управляющего входа.

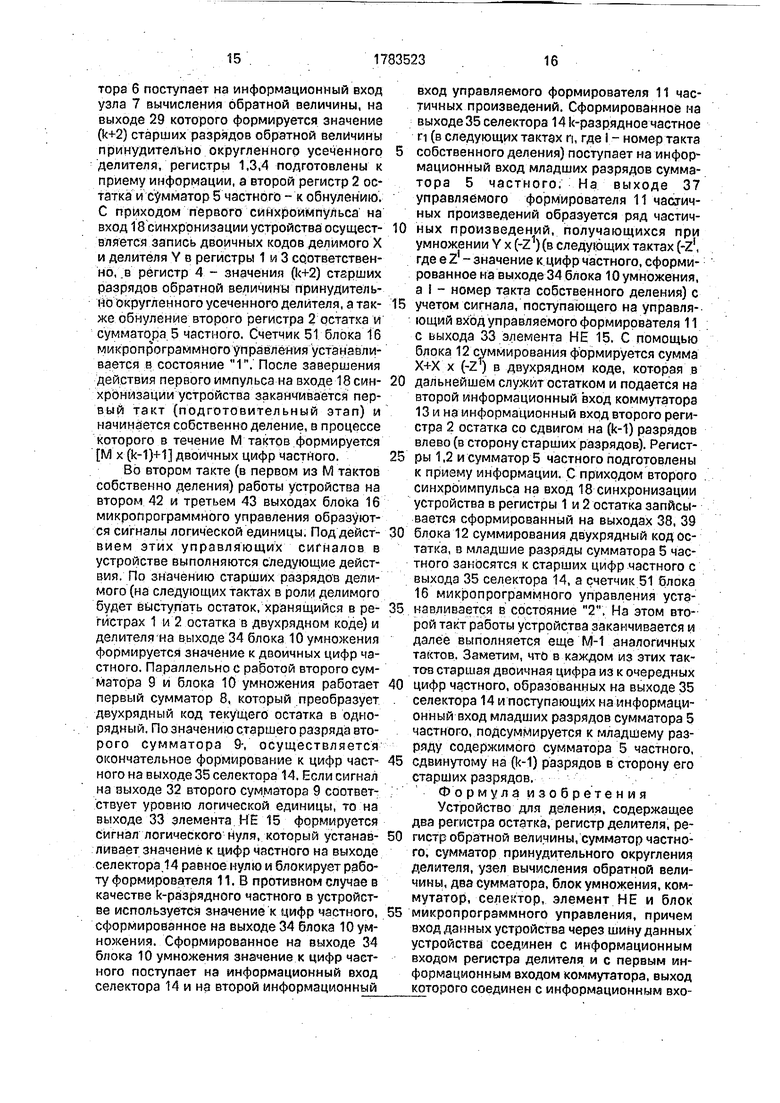

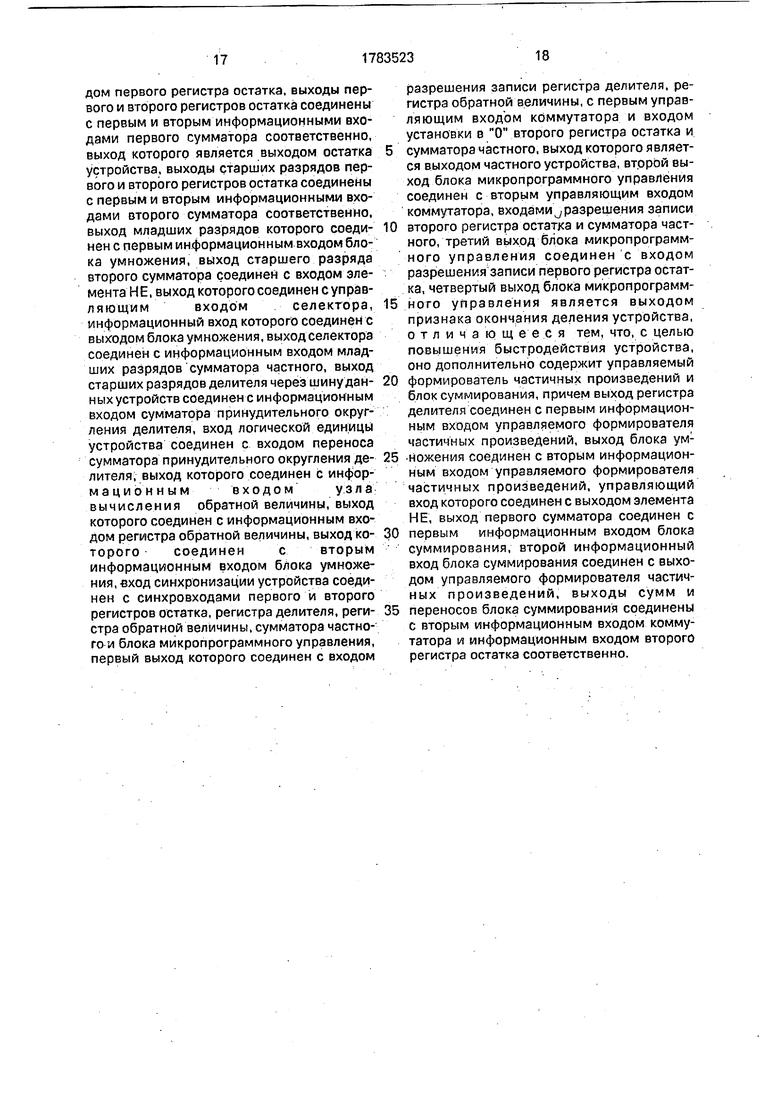

Блок микропрограммного управления 16 координирует работу узлов и блоков устройства при выполнении в нем операции деления. Как и в устройстве-прототипе он

0 может быть реализован на счетчике 51 и памяти 52 микрокоманд (фиг.4). Счетчик 51 - накапливающего типа и предназначен для естественной адресации микрокоманд. Вход счета счетчика 51 соединен с входом

5 18 синхронизации устройства. В качестве памяти 52 микрокоманд может быть применена постоянная память емкостью (М+2)х4

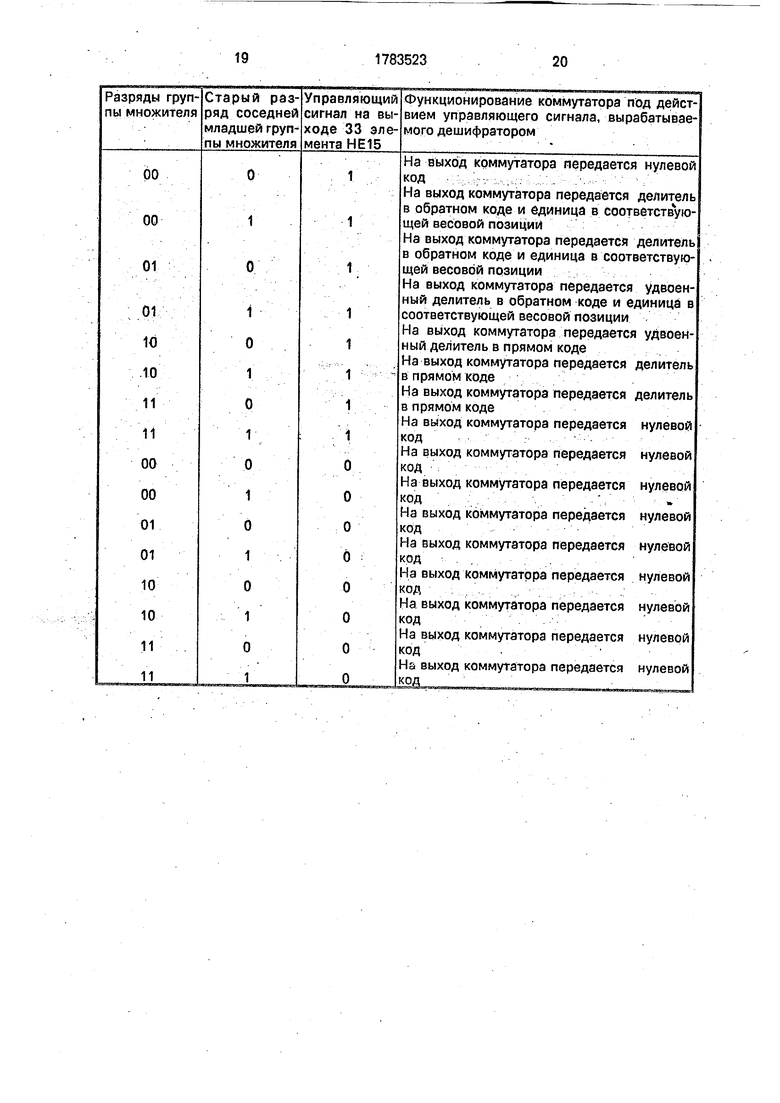

, бит, где М число тактов собст0 венного деления, в течение которых в устройстве формируется Mx(k-1)+1 цифр частного; Х - ближайшее целое, большее или равное X. В самом начале работы устройства счетчик 51 устанавливается в неко5 торое исходное состояние, например, в нуль .(на фиг.4) цепь установки счетчика 51 в исходное состояние не показана). Микропрограмма работы устройства представлена на фиг.З.

0 Устройство для деления работает следующим образом.

Пусть на входе 17 данных устройства присутствуют без знаков n-разрядные двоичные коды делителя Y и делимого X (т.е.

5 коды дробных частей делителя и делимого), а счетчик 51 блока 16 микропрограммного управления установлен в начальное нулевое состояние. Тогда на первом 41 и третьем 43 выходах блока 16 микропрограммного уп0 равленкя сформируются единичные сигналы, под действием которых коммутатор 13 пропускает на информационный вход первого регистра 1 остатка делимое X с входа 17 данных устройства, на информационные

5 входы сумматоров 6 принудительного округления делителя поступает значение старших разрядов делителя через шину данных устройства с выхода 27 входа 17 данных, затем принудительно округленное значение усеченного делителя с выхода 28 сумматора б поступает на информационный вход узла 7 вычисления обратной величины, на выходе 29 которого формируется значение (k+2) старших разрядов обратной величины принудительно округленного усеченного делителя, регистры 1,3,4 подготовлены к приему информации, а второй регистр 2 остатка и сумматор 5 частного - к обнулению. С приходом первого синхроимпульса на вход 18 синхронизации устройства осуществляется запись двоичных кодов делимого X и делителя Y в регистры 1 и 3 соответственно, в регистр 4 - значения (k+2) старших разрядов обратной величины принудительно округленного усеченного делителя, а также обнуление второго регистра 2 остатка и сумматора 5 частного. Счетчик 51 блока 16 микропрограммного управления устанавливается в состояние 1. После завершения действия первого импульса на входе 18 синхронизации устройства заканчивается первый такт (подготовительный этап) и начинается собственно деление, в процессе которого в течение М тактов формируется М х (k-1)+1 двоичных цифр частного.

Во втором такте (в первом из М тактов собственно деления) работы устройства на втором 42 и третьем 43 выходах блока 16 микропрограммного управления образуются сигналы логической единицы. Под действием этих управляющих сигналов в устройстве выполняются следующие действия. По значению старших разрядов делимого (на следующих тактах в роли делимого будет выступать остаток, хранящийся в регистрах 1 и 2 остатка в двухрядном коде) и делителя на выходе 34 блока 10 умножения формируется значение к двоичных цифр частного. Параллельно с работой второго сумматора 9 и блока 10 умножения работает первый сумматор 8, который преобразует двухрядный код текущего остатка в однорядный. По значению старшего разряда вто- рого сумматора 9% осуществляется окончательное формирование к цифр частного на выходе 35 селектора 14. Если сигнал на выходе 32 второго сумматора 9 соответствует уровню логической единицы, то на выходе 33 элемента НЕ 15 формируется сигнал логического нуля, который устанавливает значение к цифр частного на выходе селектора 14 равное кулю и блокирует работу формирователя 11. В противном случае в качестве k-разрядного частного в устройстве используется значение к цифр частного, сформированное на выходе 34 блока 10 умножения. Сформированное на выходе 34 блока 10 умножения значение к цифр частного поступает на информационный вход селектора 14 и на второй информационный

вход управляемого формирователя 11 частичных произведений. Сформированное на выходе 35 селектора 14 -разрядное частное п (в следующих тактах п, где i - номер такта

собственного деления) поступает на информационный вход младших разрядов сумматора Б частного. На выходе 37 управляемого формирователя 11 частичных произведений образуется ряд частич0 ных произведений, получающихся при умножении Y x (-Z1) (в следующих тактах (-Z1, где е Z - значение к цифр частного, сформированное на выходе 34 блока 10 умножения, а I - номер такта собственного деления) с

5 учетом сигнала, поступающего на управляющий вход управляемого формирователя 11 с выхода 33 элемента НЕ 15. С помощью блока 12 суммирования формируется сумма Х+Х х (-Z) в двухрядном коде, которая в

0 дальнейшем служит остатком и подается на второй информационный вход коммутатора 13 и на информационный вход второго регистра 2 остатка со сдвигом на (k-1) разрядов влево (в сторону старших разрядов). Регист5 ры 1,2 и сумматор 5 частного подготовлены к приему информации. С приходом второго синхроимпульса на вход 18 синхронизации устройства в регистры 1 и 2 остатка записывается сформированный на выходах 38, 39

0 блока 12 суммирования двухрядный код остатка, в младшие разряды сумматора 5 частного заносятся к старших цифр частного с выхода 35 селектора 14, а счетчик 51 блока 16 микропрограммного управления уста5 навливэется в состояние 2. На этом второй такт работы устройства заканчивается и далее выполняется еще М-1 аналогичных тактов. Заметим, чти в каждом из этих тактов старшая двоичная цифра из к очередных

0 цифр частного, образованных на выходе 35 селектора 14 и поступающих на информационный вход младших разрядов сумматора 5 частного, под суммируется к младшему разряду содержимого сумматора 5 частного,

5 сдвинутому на (k-1) разрядов в сторону его старших разрядов.

Формула изобретения Устройство для деления, содержащее два регистра остатка, регистр делителя, ре0 гистр обратной величины, сумматор частного, сумматор принудительного округления делителя, узел вычисления обратной величины, два сумматора, блок умножения, коммутатор, селектор, элемент НЕ и блок

5 микропрограммного управления, причем вход да иных устройства через шину данных устройства соединен с информационным входом регистра делителя и с первым информационным входом коммутатора, выход которого соединен с информационным входом первого регистра остатка, выходы первого и второго регистров остатка соединены с первым и вторым информационными входами первого сумматора соответственно, выход которого является выходом остатка устройства, выходы старших разрядов первого и второго регистров остатка соединены с первым и вторым информационными входами второго сумматора соответственно, выход младших разрядов которого соединен с первым информационным входом блока умножения, выход старшего разряда второго сумматора соединен с входом элемента НЕ, выход которого соединен с управляющимвходомселектора, информационный вход которого соединен с выходом блока умножения, выход селектора соединен с информационным входом младших разрядов сумматора частного, выход старших разрядов делителя через шину данных устройств соединен с информационным входом сумматора принудительного округления делителя, вход логической единицы устройства соединен с входом переноса сумматора принудительного округления делителя, выход которого соединен с инфор- мационным входомузла вычисления обратной величины, выход которого соединен с информационным входом регистра обратной величины, выход которого соединен с вторым информационным входом блока умножения, -вход синхронизации устройства соединен с синхровходами первого и второго регистров остатка, регистра делителя, регистра обратной величины, сумматора частного и блока микропрограммного управления, первый выход которого соединен с входом

разрешения записи регистра делителя, регистра обратной величины, с первым управляющим входом коммутатора и входом установки в О второго регистра остатка и 5 сумматора частного, выход которого является выходом частного устройства, второй выход блока микропрограммного управления соединен с вторым управляющим входом коммутатора, входами jразрешения записи

0 второго регистра остатка и сумматора частного, третий выход блока микропрограммного управления соединен с входом разрешения записи первого регистра остатка, четвертый выход блока микропрограмм5 ного управления является выходом признака окончания деления устройства, отличающееся тем, что, с целью повышения быстродействия устройства, оно дополнительно содержит управляемый

0 формирователь частичных произведений и блок суммирования, причем выход регистра делителя соединен с первым информационным входом управляемого формирователя частичных произведений, выход блока ум1

5 .ножения соединен с вторым информационным входом управляемого формирователя частичных произведений, управляющий вход которого соединен с выходом элемента НЕ, выход первого сумматора соединен с

0 первым информационным входом блока суммирования, второй информационный вход блока суммирования соединен с выходом управляемого формирователя частичных произведений, выходы сумм и

5 переносов блока суммирования соединены с вторым информационным входом коммутатора и информационным входом второго регистра остатка соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1990 |

|

SU1728862A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018933C1 |

| Устройство для деления | 1986 |

|

SU1357947A1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

| Устройство для деления | 1988 |

|

SU1520510A1 |

| Устройство для деления | 1985 |

|

SU1357946A1 |

| Устройство для деления | 1985 |

|

SU1322264A1 |

| Устройство для деления | 1986 |

|

SU1390608A1 |

| УСТРОЙСТВО ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 2012 |

|

RU2510072C1 |

Изобретение относится к вычислительной технике и может быть использовано в быстродействующих арифметических устройствах для выполнения операции деления чисел. Цель изобретения - повышение быстродействия устройства за счет сокращения длительности такта формирования К цифр частного. Устройство содержит первый и второй регистры 1-2 остатка, регистр 3 делителя, регистр 4 обратной величины, сумматор 5 частного, сумматор 6 принудительного округления делителя, узел 7 вычисления обратной величины, два сумматора 8, 9. блок 10 умножения, коммутатор 13, селектор 14, элемент 15 НЕ, блок 19 микропрограммного управления и нововведенные управляемый формирователь 11 частичных произведений и блок 12 суммирования. 4 ил., 1 табл.

5J

С 1+1 i

/ « V3 w

Г

Ls

Jо

| Устройство для деления | 1985 |

|

SU1322264A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления | 1986 |

|

SU1357947A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-12-23—Публикация

1991-02-25—Подача