113

Изобретение относится к вычислительной технике и может быть применено в быстродействующих арифметических устройствах для выполнения операции деления чисел.

Цель изобретения - повышение быстродействия устройства за счет сокращения времени формирования К дифр частного при делении на нем чисел большой разрядности.

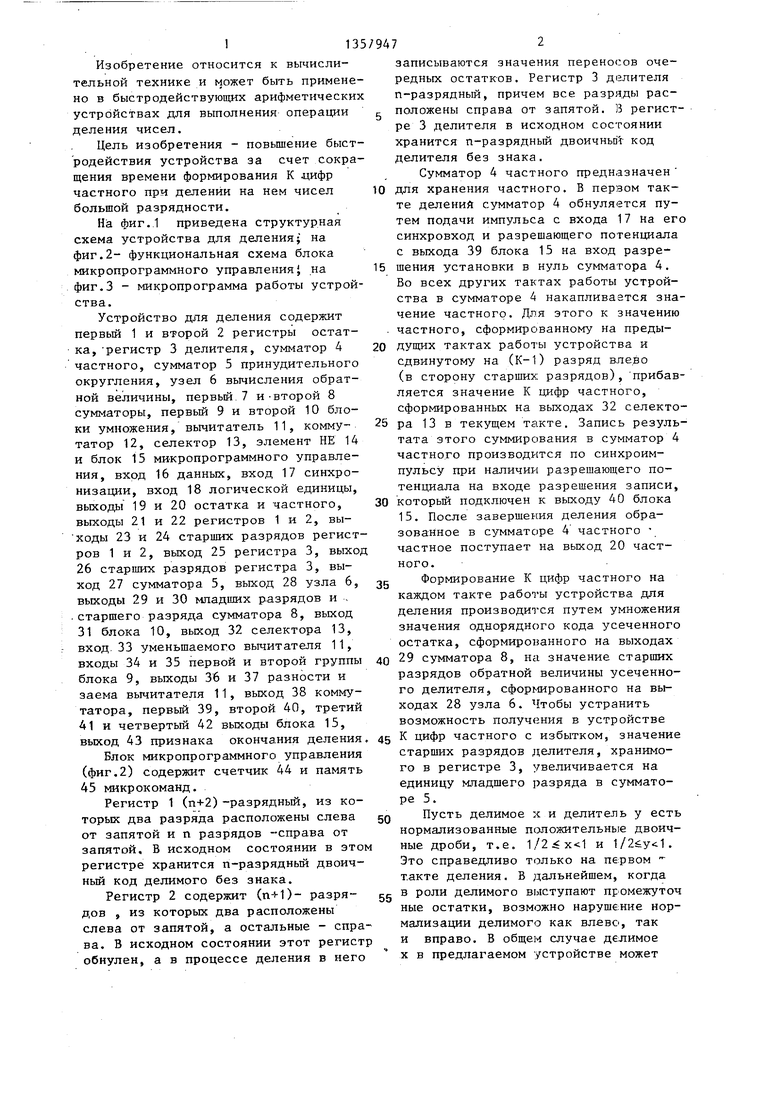

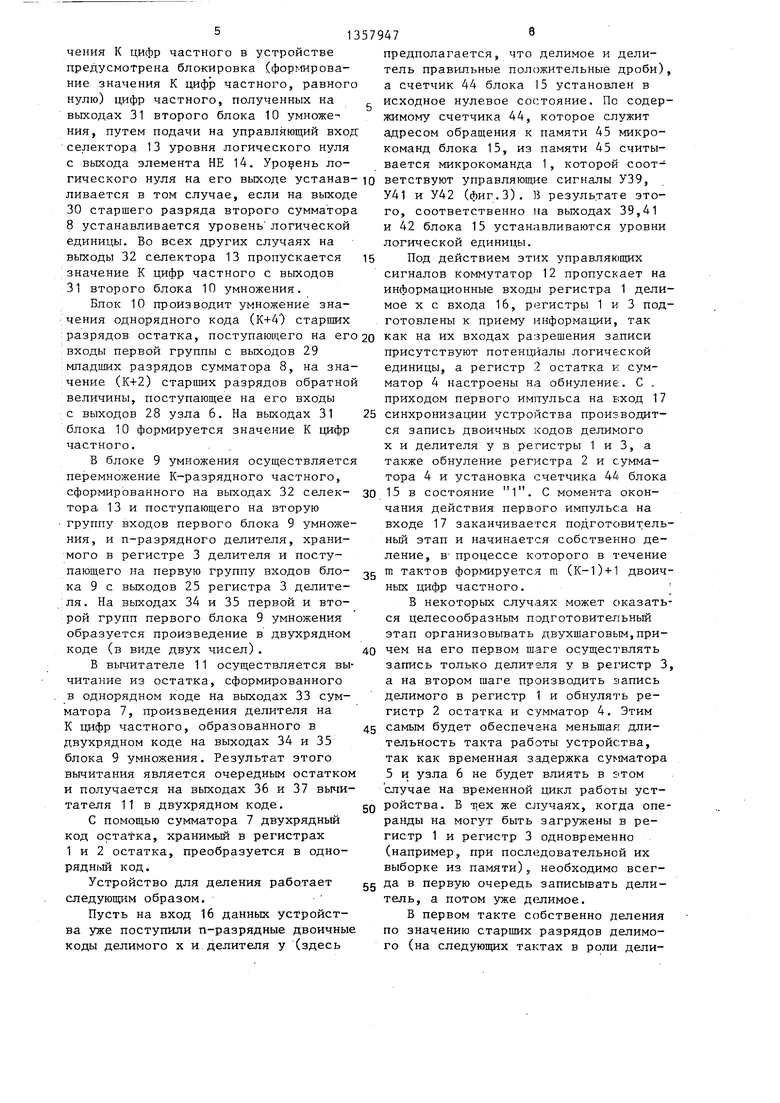

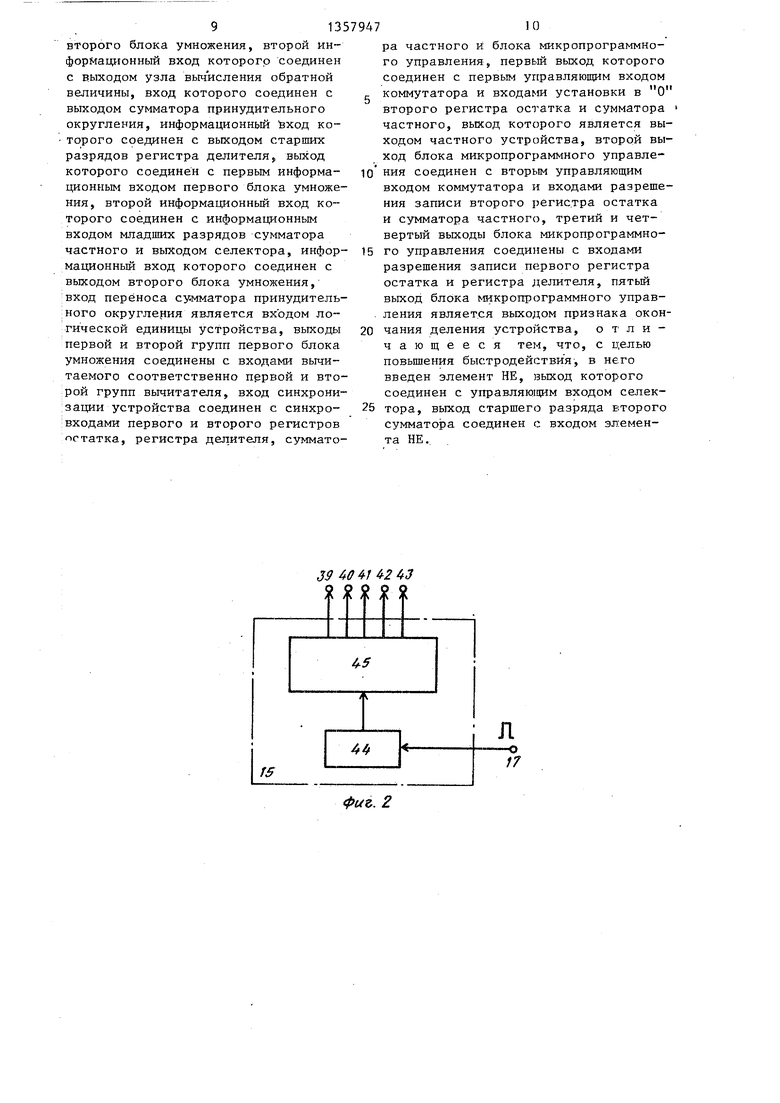

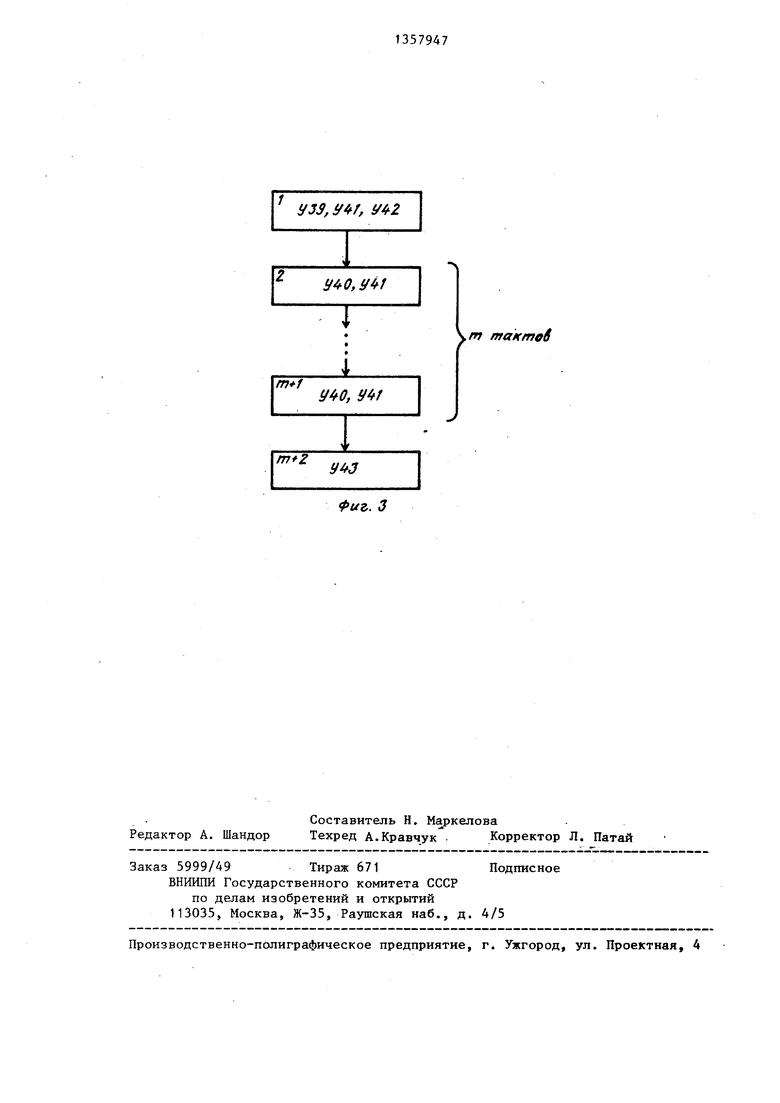

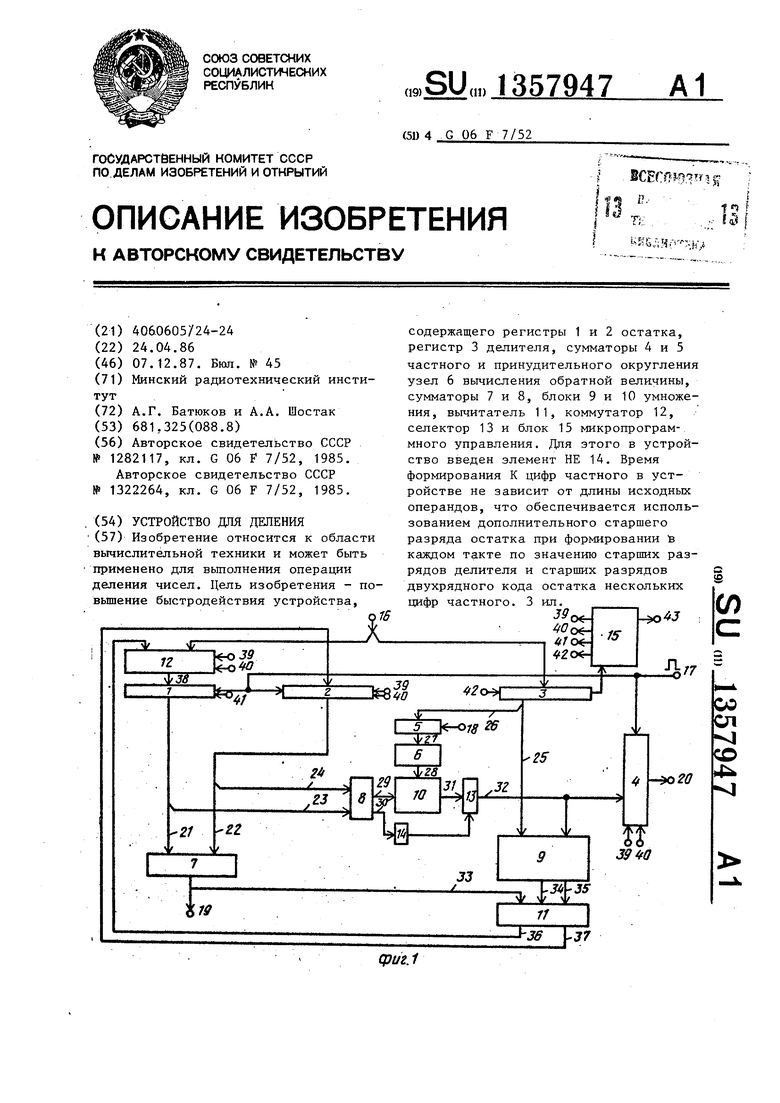

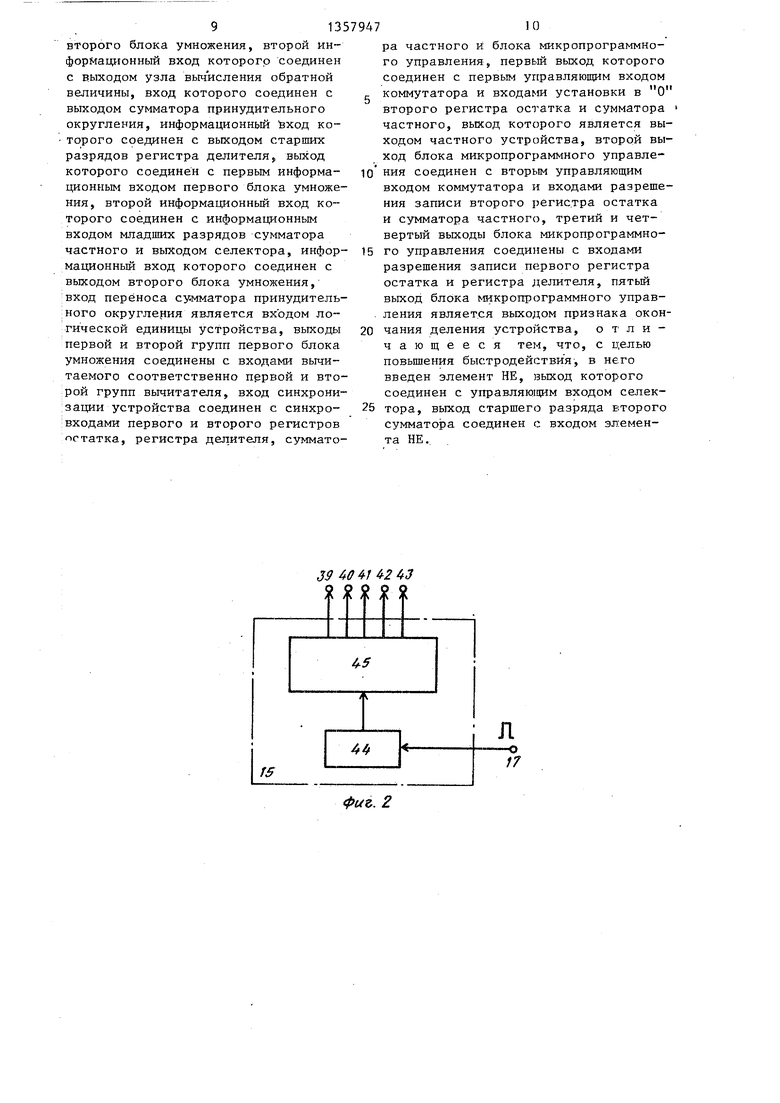

На фиг.1 приведена структурная схема устройства для деления} на фиг.2- функдиональная схема блока микропрограммного управленияJ на фиг.З - микропрограмма работы устройства.

Устройство для деления содержит первый 1 и второй 2 регистры остатка, регистр 3 делителя, сумматор 4 частного, сумматор 5 принудительного округления, узел 6 вычисления обратной величины, первый 7 и-второй 8 сумматоры, первый 9 и второй 10 блоки умножения, вычитатель 11, коммутатор 12, селектор 13, элемент НЕ 14 и блок 15 микропрограммного управле

ния, вход 16 данных, вход 17 синхронизации, вход 18 логической единицы, выходы 19 и 20 остатка и частного, выходы 21 и 22 регистров 1 и 2, вы- ходы 23 и 24 старших разрядов регистров 1 и 2, выход 25 регистра 3, выход 26 старших разрядов регистра 3, выход 27 сумматора 5, выход 28 узла 6, выходы 29 и 30 младших разрядов и . .старшего разряда сумматора 8, выход 31 блока 10, выход 32 селектора 13, вход. 33 уменьшаемого вычитателя 11, входы 34 и 35 первой и второй группы блока 9, выходы 36 и 37 разности и заема вычитателя 11, выход 38 коммутатора, первьй 39, второй 40, третий А1 и четвертый 42 выходы блока 15, выход 43 признака окончания деления

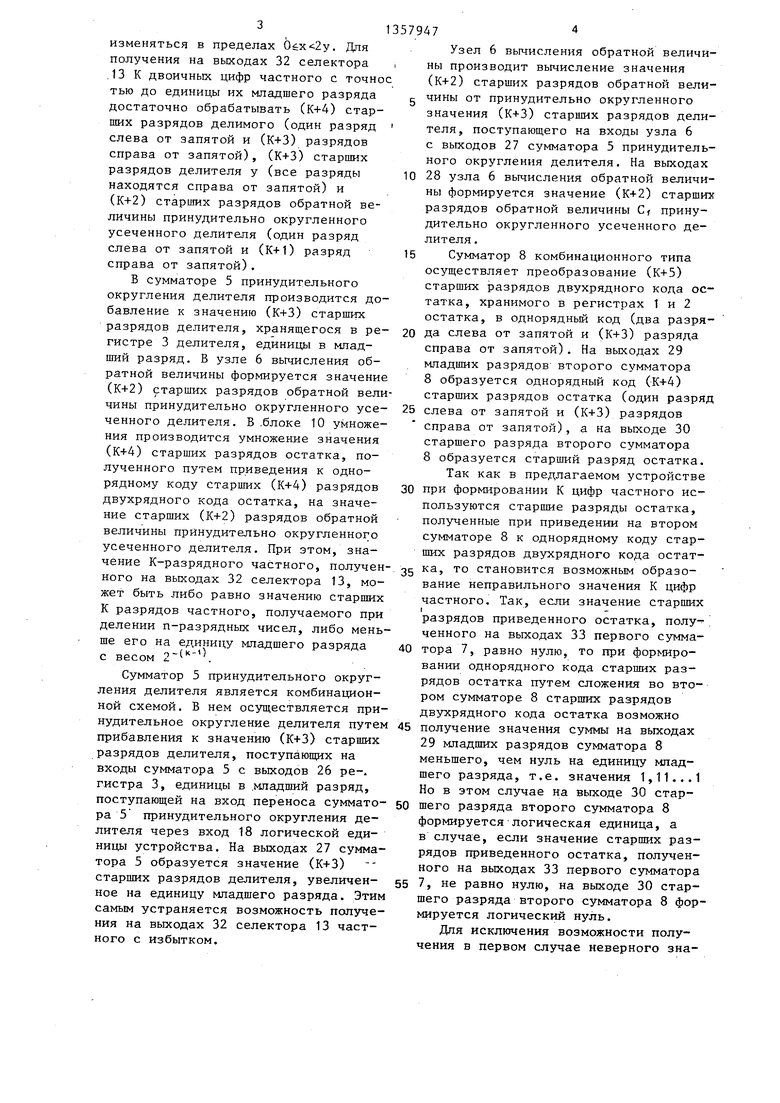

Блок микропрограммного управления (фиг.2) содержит счетчик 44 и память 45 микрокоманд.

Регистр 1 (п+2)-разрядный, из которых два разряда расположены слева от запятой и п разрядов -справа от запятой, В исходном состоянии в это регистре хранится п-разрядный двоичный код делимого без знака.

Регистр 2 содержит (п+1)- разрядов , из которых два расположены слева от запятой, а остальные - справа. В исходном состоянии этот регист обнулен, а в процессе деления в него

0

5

0

5

0

записываются значения переносов очередных остатков. Регистр 3 делителя п-разрядный, причем все разряды расположены справа от запятой. В регистре 3 делителя в исходном состоянии хранится п-разрядный двоичньй код делителя без знака.

Сумматор 4 частного предназначен для хранения частного. В первом такте делений сумматор 4 обнуляется путем подачи импульса с входа 17 на его синхровход и разрешающего потенциала с выхода 39 блока 15 на вход разрешения установки в нуль сумматора 4. Во всех других тактах работы устройства в сумматоре 4 накапливается значение частного. Для этого к значению частного, сформированному на предыдущих тактах работы устройства и сдвинутому на (К-О разряд влево (в сторону старших разрядов), прибавляется значение К цифр частного, сформированных на выходах 32 селектора 13 в текущем такте. Запись результата этого суммирования в сумматор 4 частного производится по синхроимпульсу при наличии разрешающего потенциала на входе разрешения записи, которьй подключен к выходу 40 блока 15. После завершения деления образованное в сумматоре 4 частного частное поступает на выход 20 частного.

Формирование К цифр частного на каждом такте работы устройства для деления производится путем умножения значения однорядного кода усеченного остатка, сформированного на выходах 29 сумматора 8, на значение старших разрядов обратной величины усеченного делителя, сформированного на выходах 28 узла 6. {тобы устранить возможность получения в устройстве 5 К цифр частного с избытком, значение старших разрядов делителя, хранимого в регистре 3, увеличивается на единицу младшего разряда в сумматоре 5.

Пусть делимое х и делитель у есть нормализованные положительные двоичные дроби, т.е. и . Это справедливо только на пе:рвом такте деления. В дальнейшем, когда в роли делимого выступают прюмежуточ ные остатки, возможно нарушение нормализации делимого как влево, так и вправо. В общем случае делимое X в предлагаемом устройстве может

5

0

0

5

изменяться в пределах , Для получения на выходах 32 селектора .13 К двоичных цифр частного с точное тью до единицы их младшего разряда достаточно обрабатывать (К+4) старших разрядов делимого (один разряд слева от запятой и (К+3) разрядов справа от запятой), (К+3) старгиих разрядов делителя у (все разряды находятся справа от запятой) и (К+2) старших разрядов обратной величины принудительно округленного усеченного делителя (один разряд слева от запятой и (К+1) разряд справа от запятой).

В сумматоре 5 принудительного округления делителя производится добавление к значению (К+3) старших разрядов делителя, хранящегося в ре- гистре 3 делителя, единицы в младший разряд. В узле 6 вьгчисления обратной величины формируется значение (К+2) старших разрядов обратной величины принудительно округленного усе- ченного делителя. В .блоке 10 умножения производится умножение значения (К+4) старших разрядов остатка, полученного путем приведения к однорядному коду старших (К+4) разрядов двухрядного кода остатка, на значение старших (К+2) разрядов обратной величины принудительно округленного усеченного делителя. При этом, значение К-разрядного частного, получен ного на выходах 32 селектора 13, может быть либо равно значению старших К разрядов частного, получаемого при делении п-разрядных чисел, либо меньше его на единицу младшего разряда с весом

Сумматор 5 принудительного округления делителя является комбинационной схемой. В нем осуществляется принудительное округление делителя путем прибавления к значению (К+3) старших разрядов делителя, поступающих на входы сумматора 5 с выходов 26 ре-, гистра 3, единицы в .младший разряд, поступающей на вход переноса суммато- ра 5 принудительного округления делителя через вход 18 логической единицы устройства. На выходах 27 сумматора 5 образуется значение (К+3) старших разрядов делителя, увеличен- ное на единицу младшего разряда. Этим самым устраняется возможность получения на выходах 32 селектора 13 частного с избытком.

Узел 6 вьгчисления обратной величины производит вычисление значения (К+2) старших разрядов обратной величины от принудительно округленного значения (К+3) старишх разрядов делителя, поступающего на входы узла 6 с выходов 27 сумматора 5 принудительного округления делителя. На выходах

28узла 6 вычисления обратной величины формируется значение (К+2) старши разрядов обратной величины Cf принудительно округленного усеченного делителя .

Сумматор 8 комбинационного типа осуществляет преобразование (К+5) старших разрядов двухрядного кода остатка, хранимого в регистрах 1 и 2 остатка, в однорядный код (два разряда слева от запятой и (К+3) разряда справа от запятой). На выходах 29 младших разрядов второго сумматора 8 образуется однорядный код (К+4) старших разрядов остатка (один разря слева от запятой и (К+3) разрядов справа от запятой), а на выходе 30 старшего разряда второго сумматора 8 образуется старший разряд остатка.

Так как в предлагаемом устройстве при формировании К цифр частного используются старшие разряды остатка, полученные при приведении на втором сумматоре 8 к однорядному коду старших разрядов двухрядного кода остатка, то становится возможным образование неправильного значения К цифр

частного. Так, если значение старших tразрядов приведенного остатка, полученного на выходах 33 первого сумматора 7, равно нулю, то при формировании однорядного кода старших разрядов остатка путем сложения во втором сумматоре 8 старших разрядов двухрядного кода остатка возможно получение значения суммы на выходах

29младших разрядов сумматора 8 меньшего, чем нуль на единицу младшего разряда, т.е. значения 1,11...1 Но в этом случае на выходе 30 старшего разряда второго сумматора 8 формируется логическая единица, а

в случае, если значение старших разрядов приведенного остатка, полученного на выходах 33 первого сумматора 7, не равно нулю, на выходе 30 старшего разряда второго сумматора 8 формируется логический нуль.

Для исключения возможности получения в первом случае неверного знаS135

чения К цифр частного в устройстве предусмотрена блокировка (формирование значения К цифр частного, равного нулю) цифр частного, полученных на выходах 31 второго блока 10 умноже

ния, путем подачи на управляющий вход

предполагается, что делимое и делитель правильные положительные дроби) а счетчик 44 блока 15 установлен в исходное нулевое состояние. По содержимому счетчика 44, которое служит адресом обращения к памяти 45 микрокоманд блока 15, из памяти 45 считывается микрокоманда 1, которой соотселектора 13 уровня логического нуля с выхода элемента НЕ 14. Уровень логического нуля на его выходе устанав- ю ветствуют управляющие сигналы У39, ливается в том случае, если на выходе У41 и У42 (фиг.З). Б результате это30старшего разряда второго сумматора 8 устанавливается уровень логической единицы. Во всех других случаях на выходы 32 селектора 13 пропускается 15 значение К цифр частного с выходов

31второго блока 10 умножения.

Блок 10 производит умножение значения однорядного кода (К+4 ) старших разрядов остатка, поступающего на его 20 как на их входах разрешения записи входы первой группы с выходов 29 присутствуют потенщ- алы логической младших разрядов сумматора 8, на зна- единицы, а регистр 2 остатка и сум- чение (К+2) старших разрядов обратной матор 4 настроены на обнуление. С . величины, поступающее на его входы приходом первого импульса на Е:ХОД 17 с выходов 28 узла 6. На выходах 31 25 синхронизации устройства проиэводит- блока 10 формируется значение К цифр ся запись двоичных кодов делимого частного.

В блоке 9 умножения осуществляется перемножение К-разрядного частного.

го, соответственно на выходах 39,41 и 42 блока 15 устанавливаются уровни логической единицы.

Под действием этих yпpaвляюшJix сигналов коммутатор 12 пропускает на информационные входы регистра 1 дели мое X с входа 16, регистры 1 и 3 подготовлены к приему информации, так

X и делителя у в регистры 1 и 3, а также обнуление регистра 2 и сумматора 4 и установка счетчика 44 блока

сформированного на выходах 32 селек- ЗО 15 в состояние 1. С момента окон- тора 13 и поступающего на вторую чания действия первого импульса на группу входов первого блока 9 умножевходе 17 заканчивается подготовител ный этап и начинается собственно де ление, в- процессе которого в течени

ния, и п-разрядного делителя, хранимого в регистре 3 делителя и поступающего на первую группу входов бло- 5 ™ тактов формируется га (К-1)+1 двоичка 9 с выходов 25 регистра 3 делителя. На выходах 34 и 35 первой и второй групп первого блока 9 умножения образуется произведение в двухрядном коде (в виде двух чисел).

В вычитателе 11 осуществляется вычитание из остатка, сформированного в однорядном коде на выходах 33 сумматора 7, произведения делителя на К цифр частного, образованного в двухрядном коде на выходах 34 и 35 блока 9 умножения. Результат этого вычитания является очередным остатком и получается на выходах 36 и 37 вычи- тателя 11 в двухрядном коде.

С помощью сумматора 7 двухрядный код остатка, хранимый в регистрах 1 и 2 остатка, преобразуется в однорядный код.

Устройство для деления рабо.тает следующим образом.

Пусть на вход 16 даиньк устройства уже поступили п-разрядные двоичные коды делимого х и делителя у (здесь

ных цифр частного.

В некоторых случаях может оказаться целесообразным подготовитехсьньй этап организовывать двухшаговым,при40 чем на его первом шаге осуществлять запись только делителя у в регистр 3, а на втором шаге производить запись делимого в регистр 1 и обнулять регистр 2 остатка и сумматор 4. Этим

45 самым будет обеспечена меньшая; длительность такта работы устройства, так как временная задержка сумматора 5 и узла 6 не будет влиять в EITOM случае на временной цикл работы уст5Q ройства. В т,ех же случаях, когда операнды на могут быть загружены в регистр 1 и регистр 3 одновременно (например, при последовательной их выборке из памяти), необходимо всег55 да в первую очередь записывать делитель, а потом уже дfшимoe.

В первом такте собственно деления по значению старших разрядов делимого (на следующих тактах в роли дели6

предполагается, что делимое и делитель правильные положительные дроби), а счетчик 44 блока 15 установлен в исходное нулевое состояние. По содержимому счетчика 44, которое служит адресом обращения к памяти 45 микрокоманд блока 15, из памяти 45 считывается микрокоманда 1, которой соответствуют управляющие сигналы У39, У41 и У42 (фиг.З). Б результате этокак на их входах разрешения записи присутствуют потенщ- алы логической единицы, а регистр 2 остатка и сум- матор 4 настроены на обнуление. С . приходом первого импульса на Е:ХОД 17 синхронизации устройства проиэводит- ся запись двоичных кодов делимого

го, соответственно на выходах 39,41 и 42 блока 15 устанавливаются уровни логической единицы.

Под действием этих yпpaвляюшJix сигналов коммутатор 12 пропускает на информационные входы регистра 1 делимое X с входа 16, регистры 1 и 3 подготовлены к приему информации, так

как на их входах разрешения записи присутствуют потенщ- алы логической единицы, а регистр 2 остатка и сум- матор 4 настроены на обнуление. С . приходом первого импульса на Е:ХОД 17 синхронизации устройства проиэводит- ся запись двоичных кодов делимого

X и делителя у в регистры 1 и 3, а также обнуление регистра 2 и сумматора 4 и установка счетчика 44 блока

15 в состояние 1. С момента окон- чания действия первого импульса на

входе 17 заканчивается подготовительный этап и начинается собственно деление, в- процессе которого в течение

ных цифр частного.

В некоторых случаях может оказаться целесообразным подготовитехсьньй этап организовывать двухшаговым,при40 чем на его первом шаге осуществлять запись только делителя у в регистр 3 а на втором шаге производить запись делимого в регистр 1 и обнулять регистр 2 остатка и сумматор 4. Этим

45 самым будет обеспечена меньшая; длительность такта работы устройства, так как временная задержка сумматора 5 и узла 6 не будет влиять в EITOM случае на временной цикл работы уст5Q ройства. В т,ех же случаях, когда операнды на могут быть загружены в регистр 1 и регистр 3 одновременно (например, при последовательной их выборке из памяти), необходимо всег55 да в первую очередь записывать делитель, а потом уже дfшимoe.

В первом такте собственно деления по значению старших разрядов делимого (на следующих тактах в роли дели

713

мого будет, выступать остаток, хранящийся в регистрах 1 и 2 в двухрядном коде) и делителя на выходах 31 блока 10 формируются четыре двоичных цифры частного.

Параллельно с работой блока 10 умножения и сумматора 8 работает сумматор 7, который преобразует двухрядный код текущего остатка в однорядный код. По значению сигнала на выходе 30 сумматора 8 осуществляется окончательное формирование К цифр частного. Если сигнал на выходе 30 сумматора 8 соответствует уровню логической единицы, то на выходе элемента НЕ 14 формируется сигнал логического нуля, который устанавливает значение К цифр частного на выходах 32 селекто- ра 13 равное нулю. В противном случае, в качестве К-разрядного частного в устройстве используется значение, К цифр частного, сформированных- на выходах 31 блока 10 умножения. Сформированное на выходах 32 селектора

13 К-разрядное частное Z| (на следующих тактах z;, где i - номер такта собственно деления) поступает на информационные входы младших разрядов сумматора 4 и на входы первого блока 9 умножения, на выходах 34 и 35 которого образуется в двухрядном коде произведение У-г,, а с помощью вычитателя 11 формируется разность X -yz в двухрядном коде, которая в дальнейшем служит остатком и подается на информационные входы коммутатора 12 и регистра 2 остатка со сдвигом на (К-1) разрядов влево (в сторону старших разрядов).

Одновременно с этим из памяти 45 ьшкрокоманд считывается микрокоманда 2 которой соответствуют управляющие сигналы У40 и У41 и соответственно на выходах 40 и 41 блока 15 устанавливаются уровни логической единицы. Под действием этих управляющих сигналов коммутатор 12 пропускает на инПосле выполнения последнего (т+1) такта на выходе 20 частного устройства образуется п-разрядное частное, на выходе 19 образуется п-разрядный остаток. Одновременно с этим из памяти 45 микрокоманд блока 15 считывается микрокоманда (т+2), которой соответствует управляющий сигнал У43 и соответственно на выходе 43 блока 15 устанавливается уровень логической 25 единицы, сигнализирующий об окончании операции деления.

Формула изобретения

30 Устройство для деления, содержащее два регистра остатка, регистр делителя, сумматор частного, сумматор принудительного округления, узел вычисления обратной величины, два сум2g матора, два блока умножения, коммутатор, селектор, вычитатель и блок микропрограммного управления, причем вход данных устройства соединен с информационным входом регистра делителя

40 и с первым информационным входом коммутатора, выход которого соединен с информационным входом первого регист- хра остатка, выходы первого и второго регистров остатка соединены с первым

45 и вторым.информационными входами соответственно первого сумматора, выход которого является выходом остатка устройства и соединен с входом уменьшаемого вычитателя, выходы разности формационные входы регистра 1 резуль- заема которого соединены с вторым тат с выхода 36 вычитателя 11, per, информационным входом коммутатора и гистры 1 и 2 и сумматор 4 подготовле- информационным входом второго регист- ны к приему информации. С приходом р остатка соответственно, выходы второго импульса на вход 17 в регист- старших разрядов первого и второго ры 1 и 2 записывается сформированный gg регистров остатка соединены соответ- на выходах 36 и 37 вычитателя 11 двух- ственно с первым и вторым информа- рядный код остатка, в мпадшие разряды ционными входами второго сумматора, сумматора 4 частного заносится К выход младших разрядов которого сов- старших цифр частного, а счетчик 44 динен с первым информационным входом

0

блока 15 устанавливается в состояние 2.

Аналогичным образом устройство работает и в других тактах. В каждом такте старшая двоичная цифра из К очередных цифр частного, образованных на выходах 32 селектора 13 и посту-, пающих на информационные входы младших разрядов сумматора 4 частного, подсуммируется к младшему двоичному разряду содержимого сумматора 4 частного, сдвинутому на (К-1) разрядов в сторону его старших разрядов.

После выполнения последнего (т+1) такта на выходе 20 частного устройства образуется п-разрядное частное, на выходе 19 образуется п-разрядный остаток. Одновременно с этим из памяти 45 микрокоманд блока 15 считывается микрокоманда (т+2), которой соответствует управляющий сигнал У43 и соответственно на выходе 43 блока 15 устанавливается уровень логической 5 единицы, сигнализирующий об окончании операции деления.

5

0

Формула изобретения

30 Устройство для деления, содержащее два регистра остатка, регистр делителя, сумматор частного, сумматор принудительного округления, узел вычисления обратной величины, два сум2g матора, два блока умножения, коммутатор, селектор, вычитатель и блок микропрограммного управления, причем вход данных устройства соединен с информационным входом регистра делителя

40 и с первым информационным входом коммутатора, выход которого соединен с информационным входом первого регист- хра остатка, выходы первого и второго регистров остатка соединены с первым

45 и вторым.информационными входами соответственно первого сумматора, выход которого является выходом остатка устройства и соединен с входом умень9135

второго блока умножения, второй информационный вход которого соединен с выходом узла вычисления обратной величины, вход которого соединен с выходом сумматора принудительного округления, информационный Ьход которого соединен с выходом старших разрядов регистра делителя,, выход которого соединен с первым информа- ционным входом первого блока умножения, второй информационный вход которого соединен с информационным входом младишх разрядов сумматора частного и выходом селектора, инфор- мационньш вход которого соединен с выходом второго блока умножения, вход переноса су-мматора принудитель- :ного округления является входом логической единицы устройства, выходы первой и второй групп первого блока умножения соединены с входами вычитаемого соответственно первой и вто- рой групп вычитателя, вход синхрони- :зации устройства соединен с синхро- : входами первого и второго регистров остатка, регистра делителя, суммато39 40 4/ 42 4 J

3 о о

1 М 1

Г5

фиг. 2

0

ра частного и блока микропрограммного управления, первый выход которого соединен с первым управляющим входом коммутатора и входами установки в О второго регистра остатка и сумматора частного, выход которого является выходом частного устройства, второй выход блока микропрограммного управления соединен с вторым управляющим входом коммутатора и входами разрешения записи второго регистра остатка и сумматора частного, третий и четвертый выходы блока микропрограммного управления соединены с входами разрешения записи первого регистра остатка и регистра делителя, пятый выход блока микропрограммного управления является выходом признака окончания деления устройства, отличающееся тем, что, с целью повышения быстродействия, в него введен элемент НЕ, выход которого соединен с управляющим входом селектора, выход старшего разряда второго сумматора соединен с входом элемента НЕ,

ff

Л -О

17

yj,y«/,

,

t t

i.

,

Фиг. 3

Редактор A. Шандор

Составитель Н. Маркелова

Техред А.Кравчук Корректор Л. Патай

Заказ 5999/49 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

m тактоб

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1990 |

|

SU1728862A1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

| Устройство для деления | 1991 |

|

SU1783523A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018933C1 |

| Устройство для деления чисел | 1988 |

|

SU1580353A1 |

| Устройство для деления чисел | 1990 |

|

SU1735844A1 |

| Устройство для деления чисел | 1986 |

|

SU1417010A1 |

| Устройство для деления | 1985 |

|

SU1322264A1 |

| Устройство для деления | 1988 |

|

SU1541598A1 |

| Устройство для деления | 1989 |

|

SU1667060A1 |

Изобретение относится к области вычислительной техники и может быть применено для вьтолнения операции деления чисел. Цель изобретения - посодержащего регистры 1 и 2 остатка, регистр 3 делителя, сумматоры 4 и 5 частного и принудительного округления узел 6 вычисления обратной величины, сумматоры 7 и 8, блоки 9 и 10 умножения, вычитатель 11, коммутатор 12, селектор 13 и блок 15 микропрограммного управления. Для этого в устройство введен элемент НЕ 14. Время формирования К цифр частного в устройстве не зависит от длины исходных операндов, что обеспечивается использованием дополнительного старшего разряда остатка при формировании Ь каждом такте по значению старших разрядов делителя и старших разрядов двухрядного кода остатка нескольких цифр частного. 3 ил. & (Л

| Устройство для деления | 1985 |

|

SU1282117A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления | 1985 |

|

SU1322264A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-07—Публикация

1986-04-24—Подача