Разбертка

0ПГУ

Разбертка

Синхронизации 7

Фиг. 1

Подсбет 26

х|

го

00 00 00

о

ю

Изобретение относится к автоматике и вычислительной технике, в частности предназначено для использования в устройствах отображения информации на экране электронно-лучевой трубки (ЭЛТ) и является усовершенствованием основного изобретения по авт. св. № 1259330.

Цель изобретения - повышение быстродействия устройства.

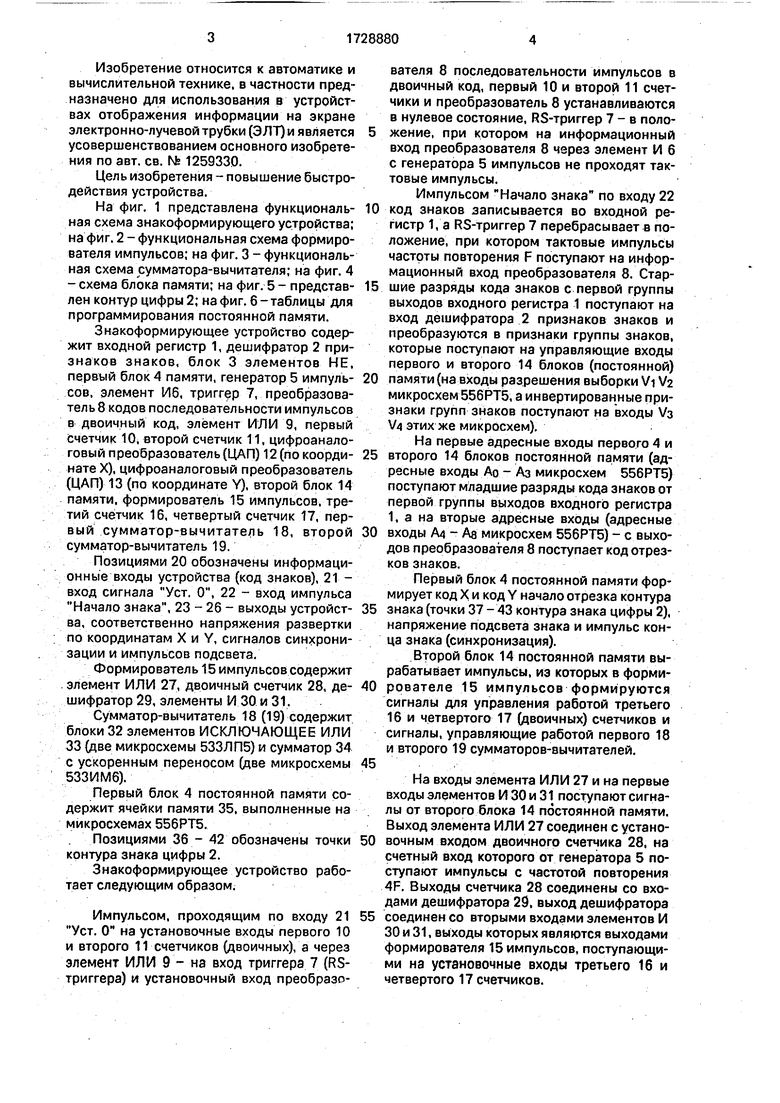

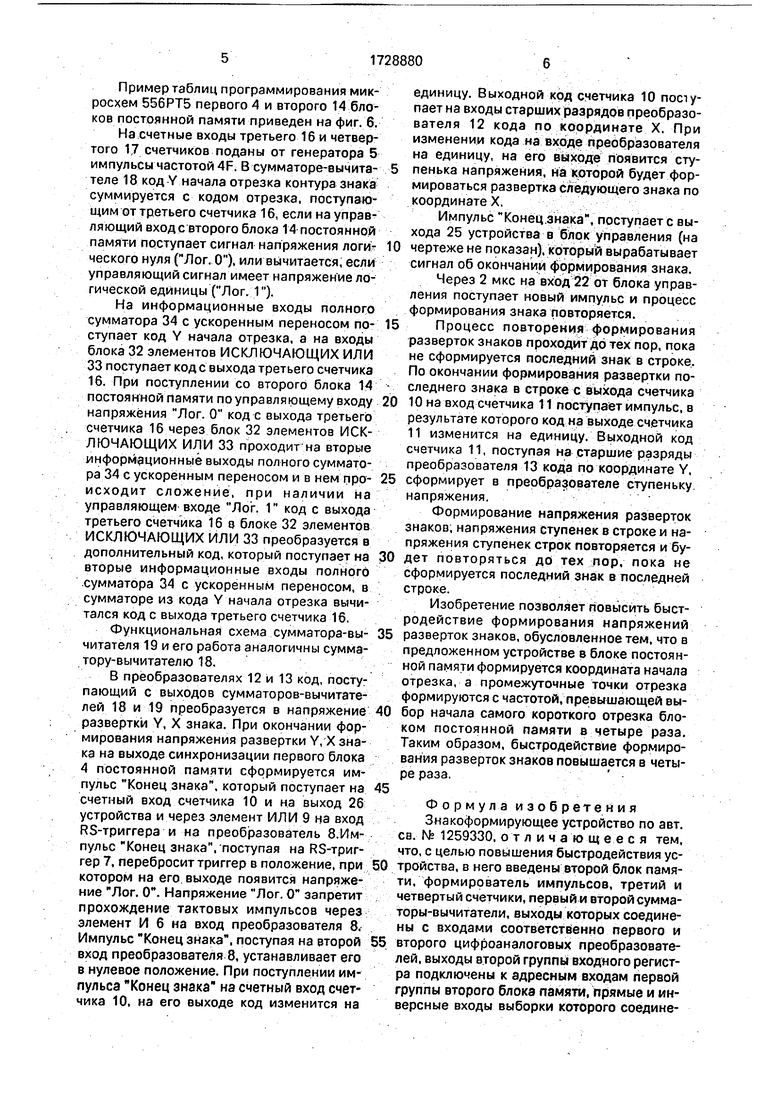

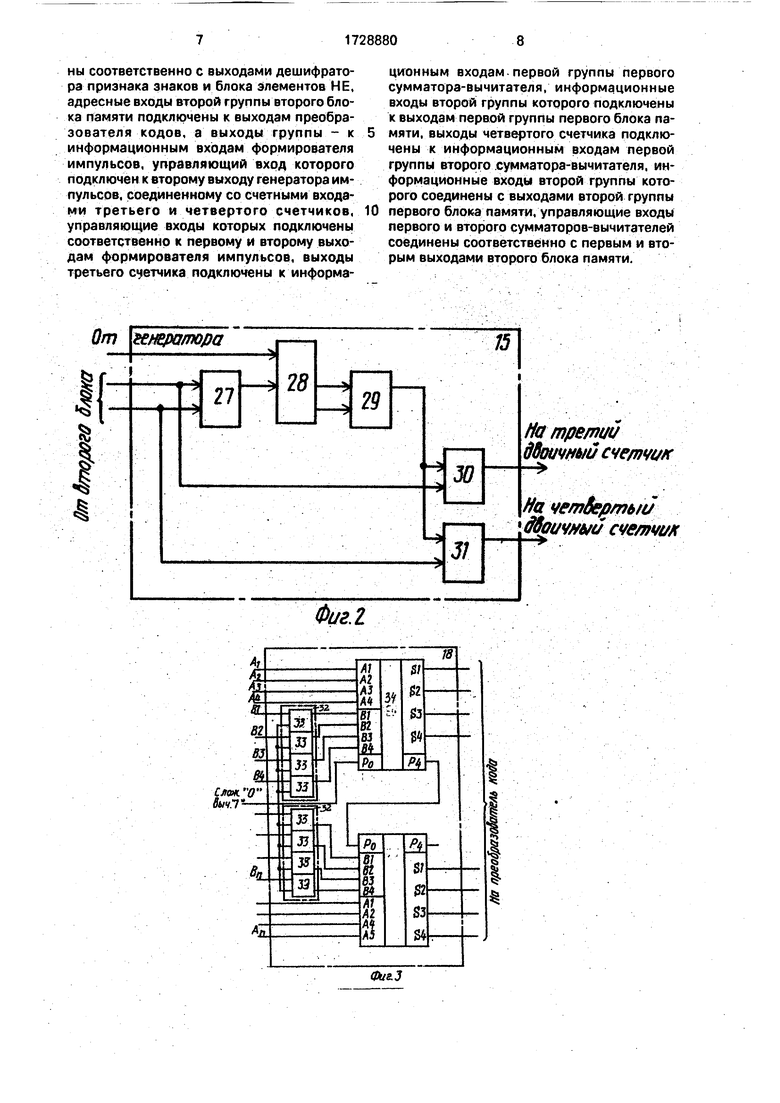

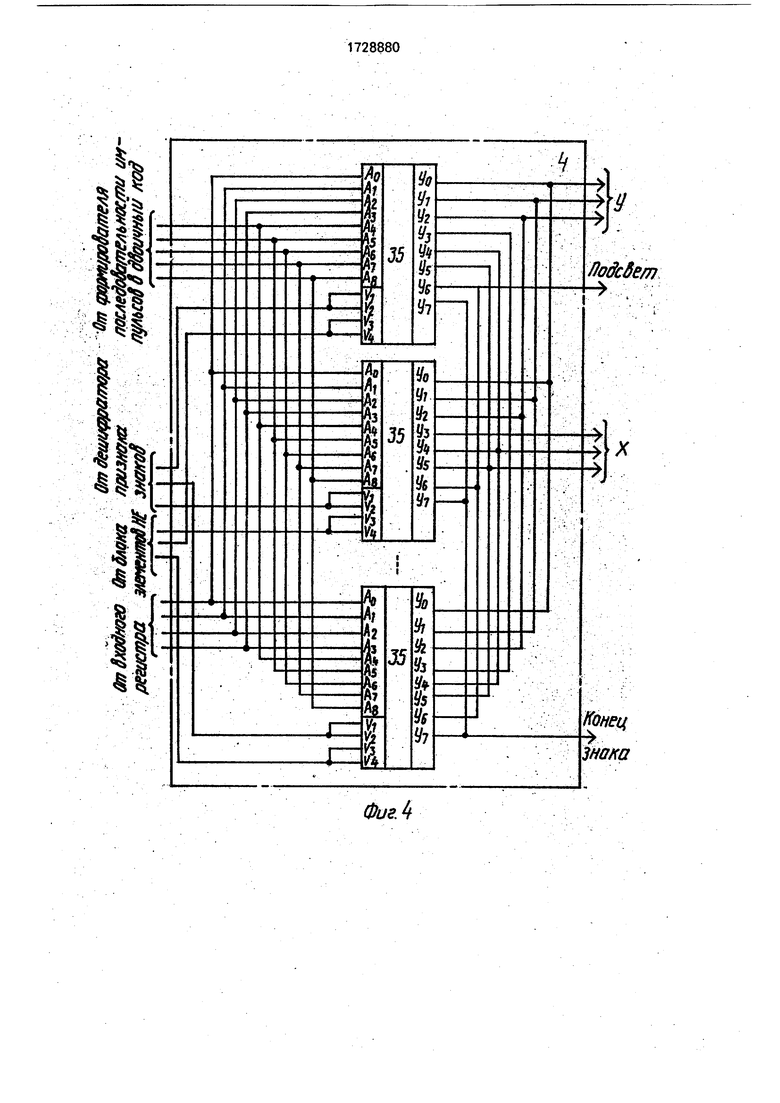

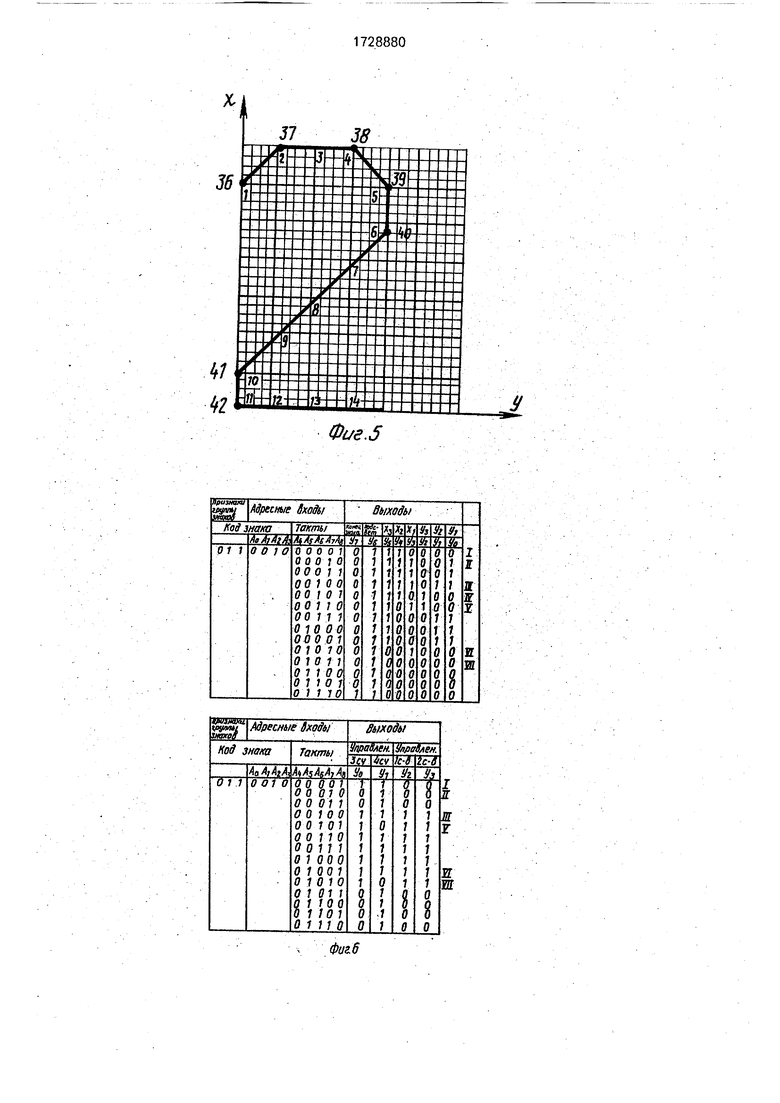

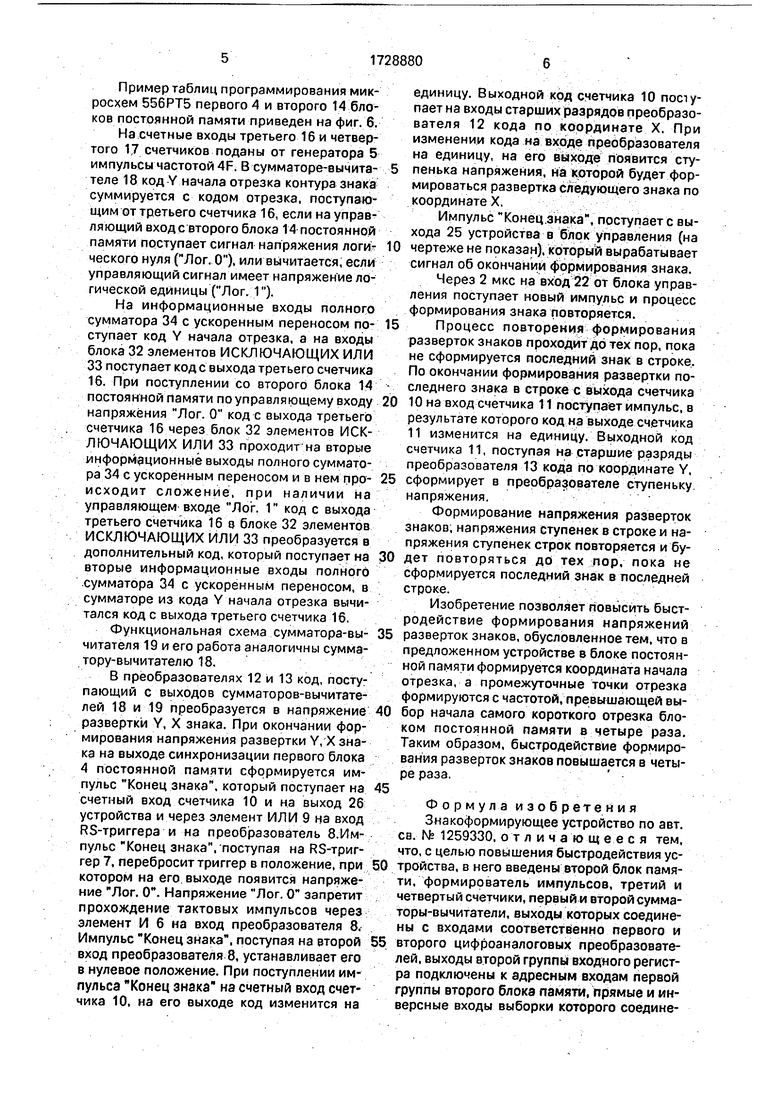

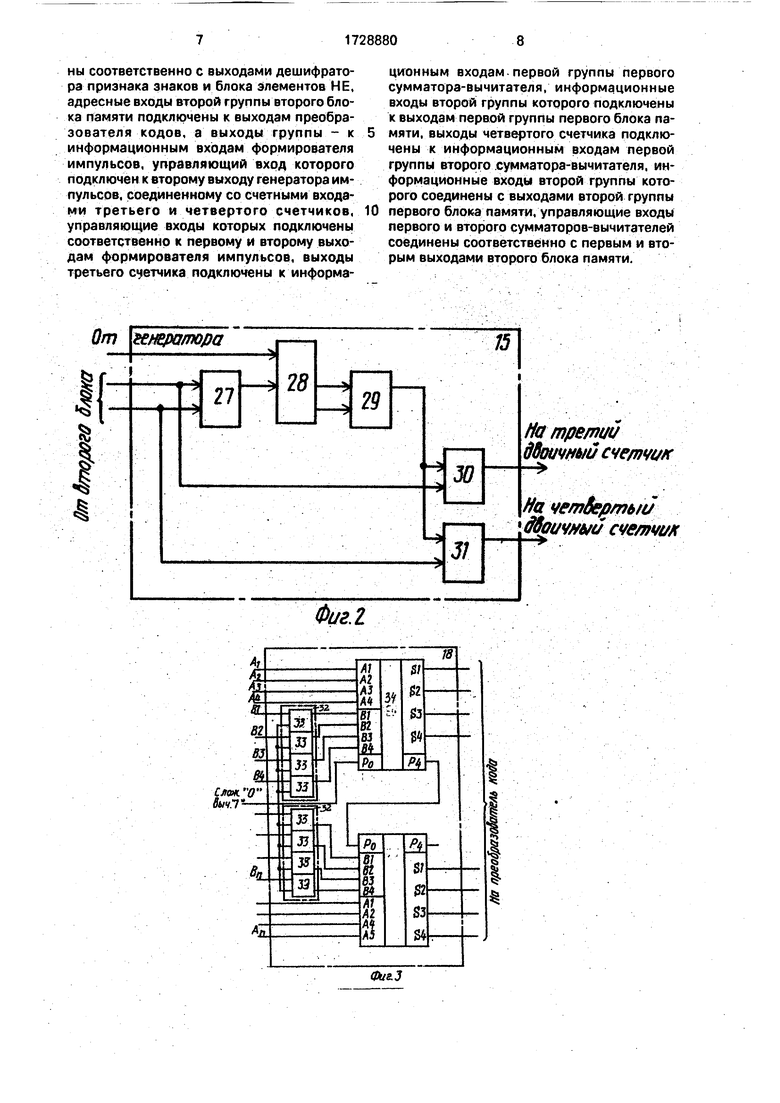

На фиг. 1 представлена функциональная схема знакоформирующего устройства; на фиг. 2 - функциональная схема формирователя импульсов; на фиг. 3 - функциональная схема сумматора-вычитателя; на фиг. 4 - схема блока памяти; на фиг. 5 - представлен контур цифры 2; на фиг. 6 - таблицы для программирования постоянной памяти.

Знакоформирующее устройство содержит входной регистр 1, дешифратор 2 признаков знаков, блок 3 элементов НЕ, первый блок А памяти, генератор 5 импульсов, элемент Иб, триггер 7, преобразователь 8 кодов последовательности импульсов в двоичный код, элемент ИЛИ 9, первый счетчик 10, второй счетчик 11, цифроанало- говый преобразователь (ЦАП) 1.2 (по координате X), цифроаналоговый преобразователь (ЦАП) 13 (по координате Y), второй блок 14 памяти, формирователь 15 импульсов, третий счётчик 16, четвертый счетчик 17, первый сумматор-вычитатель 18, второй сумматор-вычитатель 19.

Позициями 20 обозначены информационные входы устройства (код знаков), 21 - вход сигнала Уст. О, 22 - вход импульса Начало знака, 23 - 26 - выходы устройства, соответственно напряжения развертки по координатам X и Y, сигналов синхронизации и импульсов подсвета.

Формирователь 15 импульсов содержит . элемент ИЛИ 27, двоичный счетчик 28, дешифратор 29, элементы И 30 и 31.

Сумматор-вычитатель 18 (19) содержит блоки 32 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 33 (две микросхемы 533ЛП5) и сумматор 34 с ускоренным переносом (две микросхемы 533ИМ6).

Первый блок 4 постоянной памяти содержит ячейки памяти 35, выполненные на микросхемах 556РТ5.

Позициями 36 - 42 обозначены точки контура знака цифры 2.

Знакоформирующее устройство работает следующим образом.

Импульсом, проходящим по входу 21 Уст. О на установочные входы первого 10 и второго 11 счетчиков (двоичных), а через элемент ИЛИ 9 - на вход триггера 7 (RS- триггера) и установочный вход преобразователя 8 последовательности импульсов в двоичный код, первый 10 и второй 11 счетчики и преобразователь 8 устанавливаются в нулевое состояние, RS-триггер 7 - в положение, при котором на информационный вход преобразователя 8 через элемент И б с генератора 5 импульсов не проходят тактовые импульсы.

Импульсом Начало знака по входу 22

0 код знаков записывается во входной регистр 1, а RS-триггер 7 перебрасывает в положение, при котором тактовые импульсы частоты повторения F поступают на информационный вход преобразователя 8. Стар5 шие разряды кода знаков с первой группы выходов входного регистра 1 поступают на вход дешифратора 2 признаков знаков и преобразуются в признаки группы знаков, которые поступают на управляющие входы первого и второго 14 блоков (постоянной)

0 памяти (на входы разрешения выборки Vi V2 микросхем 556РТ5, а инвертированные признаки групп знаков поступают на входы Уз V4 этих же микросхем).

На первые адресные входы первого 4 и

5 второго 14 блоков постоянной памяти (адресные входы АО - Аз микросхем 556РТ5) поступают младшие разряды кода знаков от первой группы выходов входного регистра 1, а на вторые адресные входы (адресные

0 входы А4 - Аа микросхем 556РТ5) - с выходов преобразователя 8 поступает код отрезков знаков.

Первый блок 4 постоянной памяти формирует код X и код Y начало отрезка контура

5 знака (точки 37 - 43 контура знака цифры 2), напряжение подсвета знака и импульс конца знака (синхронизация).

Второй блок 14 постоянной памяти вырабатывает импульсы, из которых в форми0 рователе 15 импульсов формируются сигналы для управления работой третьего 16 и четвертого 17 (двоичных) счетчиков и сигналы, управляющие работой первого 18 и второго 19 сумматоров-вычитателей.

5

На входы элемента ИЛИ 27 и на первые входы элементов И 30 и 31 поступают сигналы от второго блока 14 постоянной памяти. Выход элемента ИЛИ 27 соединен с устано0 вочным входом двоичного счетчика 28, на счетный вход которого от генератора 5 поступают импульсы с частотой повторения 4F. Выходы счетчика 28 соединены со входами дешифратора 29. выход дешифратора

5 соединен со вторыми входами элементов И 30 и 31, выходы которых являются выходами формирователя 15 импульсов, поступающими на установочные входы третьего 16 и четвертого 17 счетчиков.

Пример таблиц программирования микросхем 556РТ5 первого А и второго 14 блоков постоянной памяти приведен на фиг. 6.

Несчетные входы третьего 1.6 и четвертого 1,7 счетчиков поданы от генератора 5 импульсы частотой 4F. В сумматоре-вычита- теле 18 код V начала отрезка контура знака суммируется с кодом отрезка, поступающим от третьего счетчика 16, если на управляющий вход с второго блока 14 постоянной памяти поступает сигнал напряжения логи ческого нуля (Лог. О), или вычитается, если управляющий сигнал имеет напряжение логической единицы (Лог. 1).

На информационные входы полного сумматора 34 с ускоренным переносом поступает код Y начала отрезка, а на входы блока 32 элементов ИСКЛЮЧАЮЩИХ ИЛИ 33 поступает код с выхода третьего счетчика 16. При поступлении со второго блока 14 постоянной памяти поуправляющему входу напряжения Лог. О код с выхода третьего счетчика 16 через блок 32 элементов ИСКЛЮЧАЮЩИХ ИЛИ 33 проходит на вторые информационные выходы полного сумматора 34 с ускоренным переносом и в нем происходит сложение, при наличии на управляющем входе Лог. 1 код с выхода третьего счетчика 16 в блоке 32 элементов ИСКЛЮЧАЮЩИХ ИЛИ 33 преобразуется в дополнительный код, который поступает на вторые информационные входы полного .сумматора 34 с ускоренным переносом, в сумматоре из кода Y начала отрезка вычитался код с выхода третьего счетчика 16,

Функциональная схема сумматора-вы- читателя 19 и его работа аналогичны сумма- тору-вычитателю 18.

В преобразователях 12 и 13 код, поступающий с выходов сумматоров-вычитате- лей 18 и 19 преобразуется в напряжение развертки Y, X знака. При окончании формирования напряжения развертки Y, X знака на выходе синхронизации первого блока 4 постоянной памяти сформируется импульс Конец знака, который поступает на счетный вход счетчика 10 и на выход 26 устройства и через элемент ИЛИ 9 на вход RS-триггера и на преобразователь 8.Им- пульс Конец знака, поступая на RS-триг- гер 7, перебросит триггер в положение, при котором на его выходе появится напряжение Лог. 0й. Напряжение Лог. О запретит прохождение тактовых импульсов через элемент И 6 на вход преобразователя 8. Импульс Конец знака, поступая на второй вход преобразователя 8, устанавливает его в нулевое положение. При поступлении импульса Конец знака на счетный вход счетчика 10, на его выходе код изменится на

единицу. Выходной код счетчика 10 поступает на входы старших разрядов преобразо- вателя 12 кода по координате X. При изменении кода на входе преобразователя на единицу, на его выходе появится сту- 5 пенька напряжения, на которой будет формироваться развертка следующего знака по координате X.

Импульс Конёц.знака, поступаете выхода 25 устройства в блок управления (на

0 чертеже не показан), который вырабатывает сигнал об окончаний формирования знака. Через 2 мкс на вход 22 от блока управления поступает новый импульс и процесс формирования знака повторяется.

5 Процесс повторения формирования

разверток знаков проходит до тех пор, пока

не сформируется последний знак в строке.

По окончании формирования развертки по следнего знака в строке с выхода счетчика

0 10 на вход счетчика 11 поступает импульс, в результате которого код на выходе счетчика 11 изменится на единицу. Выходной код счетчика 11, поступая на старшие разряды преобразователя 13 кода по координате Y,

5 сформирует в преобразователе ступеньку, напряжения.

Формирование напряжения разверток знаков, напряжения ступенек в строке и напряжения ступенек строк повторяется и бу0 дет повторяться до тех пор, пока не сформируется последний знак в последней строке.

Изобретение позволяет повысить быстродействие формирования напряжений

5 разверток знаков, обусловленное тем, что в предложенном устройстве в блоке постоянной памяти формируется координата начала отрезка, а промежуточные точки отрезка формируются с частотой, превышающей вы0 бор начала самого короткого отрезка блоком постоянной памяти в четыре раза. Таким образом, быстродействие формирования разверток знаков повышается в четыре раза.

5

Формула изобретения Знакоформирующее устройство по авт. св. № 1259330, о т л и чающее с я тем, что, с целью повышения быстродействия ус0 тройства, в него введены второй блок памяти, формирователь импульсов, третий и четвертый счетчики, первый и второй сумма- торы-вычитатели, выходы которых соединены с входами соответственно первого и

5 второго цифроаналоговых преобразователей, выходы второй группы входного регистра подключены к адресным входам первой группы второго блока памяти, прямые и инверсные входы выборки которого соединены соответственно с выходами дешифратора признака знаков и блока элементов НЕ, адресные входы второй группы второго блока памяти подключены к выходам преобразователя кодов, а выходы группы - к информационным входам формирователя импульсов, управляющий вход которого подключен к второму выходу генератора импульсов, соединенному со счетными входами третьего и четвертого счетчиков, управляющие входы которых подключены соответственно к первому и второму выходам формирователя импульсов, выходы третьего счетчика подключены к информа0

ционным входам.первой группы первого сумматора-вычитателя, информационные входы второй группы которого подключены к выходам первой группы первого блока памяти, выходы четвертого счетчика подключены к информационным входам первой группы второго .сумматора-вычитателя, информационные входы второй группы которого соединены с выходами второй группы первого блока памяти, управляющие входы первого и второго сумматоров-вычитателей соединены соответственно с первым и вторым выходами второго блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Знакоформирующее устройство | 1984 |

|

SU1259330A1 |

| Устройство для двухкоординатного управления рабочим органом | 1990 |

|

SU1815620A1 |

| Вычислительное устройство | 1986 |

|

SU1325468A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1987 |

|

SU1564685A1 |

| Устройство для отображения символов на экране электронно-лучевой трубки | 1990 |

|

SU1837359A1 |

| Устройство для отображения векторных диаграмм на экране электронно-лучевой трубки | 1988 |

|

SU1541663A1 |

| Устройство для отображения векторов на экране электронно-лучевой трубки | 1988 |

|

SU1635171A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Устройство для формирования отрезка наклонной линии на экране электронно-лучевой трубки | 1987 |

|

SU1425767A1 |

| Устройство для формирования векторов на газоразрядной индикаторной панели | 1988 |

|

SU1642509A1 |

Изобретение относится к области автоматики v вычислительной техники, в частности предназначено для использования в устройствах отображения информации на экране электронно-лучевой трубки. Цель изобретения - повышение быстродействия, которое достигается тем, что в знакоформи- рующее устройство введены второй блок 14 памяти, формирователь 15 импульсов, третий 16 и четвертый 17 счетчики, первый 18 и второй 19 сумматоры-вычитатели. Код координат X, Y начала отрезка контура знака формируется в блоке 1 памяти. Код отрезков контура знака формируется счетчиками 16 и 17. В сумматорах-вычислителях 18 и 19 происходит сложение кода начала отрезка с ко- дом отрезка или вычитание из кода начала отрезка кода отрезка. 6 ил.

От ЪенЕратора

27

28

«I

Фиг.2

15

29

Не третий дбоичный сче/пчик

- . :

J/

Начетбергпыи tijot/ww счетчм

ФиеЛ

Фиг.5

| Знакоформирующее устройство | 1984 |

|

SU1259330A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

Авторы

Даты

1992-04-23—Публикация

1990-07-23—Подача