Изобретение относится к вычислительной технике и может быть использовано в системах обработки данных, работающих в реальном масштабе времени, для вычисления расстояния между точками, заданными в полярных координатах.

Цель изобретения - расширение функциональных возможностей за счет обеспечения возможности вычисления расстояния между точками, заданными в полярных координатах.

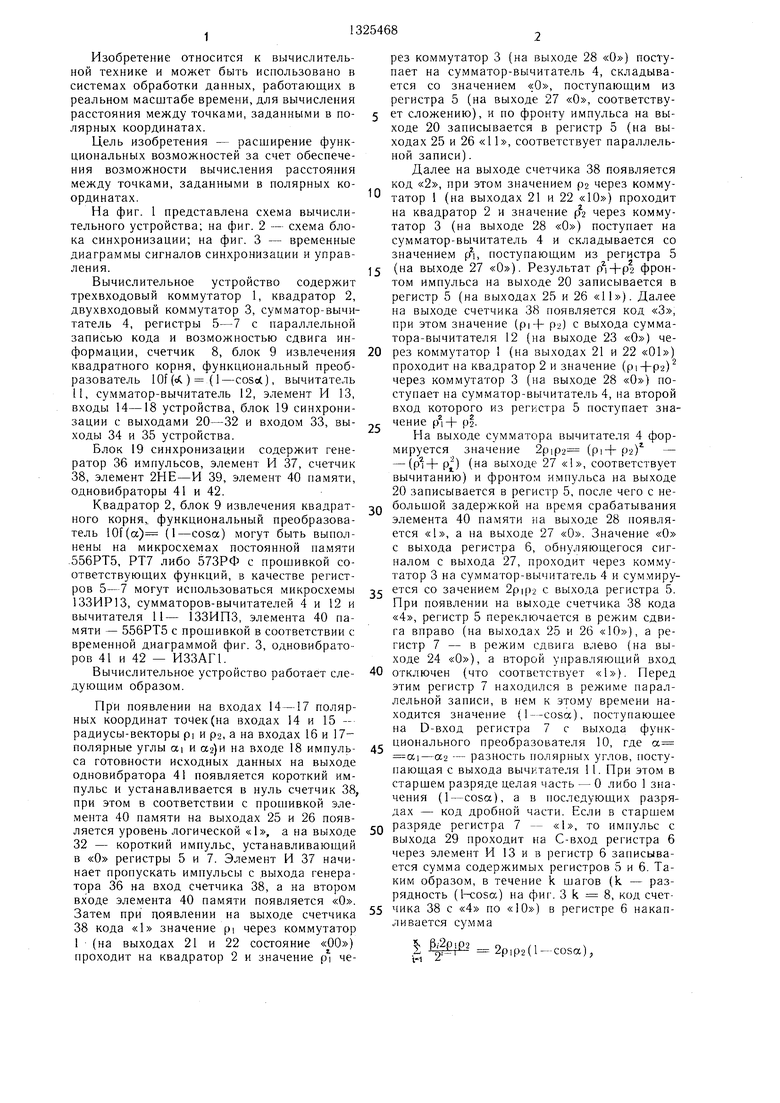

На фиг. 1 представлена схема вычислительного устройства; на фиг. 2 - схема блока синхронизации; на фиг. 3 - временные диаграммы сигналов синхронизации и управления.

Вычислительное устройство содержит трехвходовый коммутатор 1, квадратор 2, двухвходовый коммутатор 3, сумматор-вычи- татель 4, регистры 5-7 с параллельной записью кода и возможностью сдвига информации, счетчик 8, блок 9 извлечения квадратного корня, функциональный преобразователь I0f(t)(l-cosoc), вычитатель 11, сумматор-вычитатель 12, элемент И 13, входы 14-18 устройства, блок 19 синхронизации с выходами 20-32 и входом 33, выходы 34 и 35 устройства.

Блок 19 синхронизации содержит генератор 36 импульсов, элемент И 37, счетчик 38, элемент 2НЕ-И 39, элемент 40 памяти, одновибраторы 41 и 42.

Квадратор 2, блок 9 извлечения квадратного корня,, функциональный преобразователь 10f(a) (1-cosa) могут быть выполнены на микросхемах постоянной памяти ,556РТ5, РТ7 либо 573РФ с прошивкой соответствующих функций, в качестве регистров 5-7 могут использоваться микросхемы 133ИР13, сумматоров-вычитателей 4 и 12 и вычитателя 11- 133ИПЗ, элемента 40 памяти - 556РТ5 с прошивкой в соответствии с временной диаграммой фиг. 3, одновибрато- ров 41 и 42 - ИЗЗАГ1.

Вычислительное устройство работает следующим образом.

При появлении на входах 14-17 полярных координат точек(на входах 14 и 15 - радиусы-векторы pi и р2, а на входах 16 и 17- полярные углы а. и а2)и на входе 18 импульса готовности исходных данных на выходе одновибратора 41 появляется короткий импульс и устанавливается в нуль счетчик 38 при этом в соответствии с прошивкой эле- мепта 40 памяти на выходах 25 и 26 появляется уровень логической «1, а на выходе 32 - короткий имиульс, устанавливающий в «О регистры 5 и 7. Элемент И 37 начинает пропускать импульсы с выхода генератора 36 на вход счетчика 38, а на втором входе элемента 40 памяти появляется «О. Затем при появлении на выходе счетчика 38 кода «1 значение pi через коммутатор 1 (на выходах 21 и 22 состояние «00) проходит на квадратор 2 и значение р че0

5

0

5

рез коммутатор 3 (на выходе 28 «О) поступает на су.мматор-вычитатель 4, складывается со значением «О, поступающим из регистра 5 (на выходе 27 «О, соответствует сложению), и по фронту импульса на выходе 20 записывается в регистр 5 (на выходах 25 и 26 «11, соответствует параллельной записи).

Далее на выходе счетчика 38 появляется код «2, при этом значением р2 через коммутатор 1 (на выходах 21 и 22 «10) проходит на квадратор 2 и значение р через коммутатор 3 (на выходе 28 «О) поступает на сумматор-вычитатель 4 и складывается со значением , поступающим из регистра 5 (на выходе 27 «О). Результат p i-+-pl фронтом импульса на выходе 20 записывается в регистр 5 (на выходах 25 и 26 «11). Далее на выходе счетчика 38 появляется код «3, при этом значение (pi-f рг) с выхода сумма- тора-вычитателя 12 (на выходе 23 «О) через коммутатор 1 (на выходах 21 и 22 «01) проходит на квадратор 2 и значение () через коммутатор 3 (на выходе 28 «О) поступает на сумматор-вычитатель 4, на второй вход которого из регистра 5 поступает значение р2На выходе сумматора вычитателя 4 формируется значение 2pip2 (pi-b р2) - - ( р) (на выходе 27 «1, соответствует вычитанию) и фронтом импульса на выходе 20 записывается в регистр 5, после чего с нел большой задержкой на время срабатывания элемента 40 памяти на выходе 28 появляется «1, а на выходе 27 «О. Значение «О с выхода регистра 6, обнуляющегося сигналом с выхода 27, проходит через коммутатор 3 на сумматор-вычитатель 4 и суммиру ется со зачением 2pip2 с выхода регистра 5. При появлении на выходе счетчика 38 кода «4, регистр 5 переключается в режим сдвига вправо (на выходах 25 и 26 «10), а регистр 7 - в режим сдвига влево (на выходе 24 «О), а второй управляющий вход отключен (что соответствует «1). Перед этим регистр 7 находился в режиме параллельной записи, в нем к этому времени находится значение (l--cosa), поступающее на D-вход регистра 7 с выхода функционального преобразователя 10, где а а.-«2 - разность полярных углов, поступающая с выхода вычктателя 11. При этом в старшем разряде целая часть - О либо 1 значения (1-cosa), а в последующих разрядах - код дробной части. Если в старшем разряде регистра 7 - «Ь, то импульс с выхода 29 проходит на С-вход регистра 6 через элемент И 13 и в регистр 6 записывается сумма содержимых регистров 5 и 6. Таким образом, в течение k шагов (k - разрядность (1-coso;) на фиг. 3 k 8, код счетчика 38 с «4 по «10) в регистре 6 накапливается су.мма

2Р Р2 2p,p2(l -cosa),

0

5

0

5

где Pi - значение i-го разряда двоичного

кода (1-cosa).

Значения 2pip2/2 формируются сдвигом информации в регистре 5 вправо, на DR-BXO- де (вход информации «Сдвиг вправо) постоянно установлен «О (для ТТЛ-логики цепь «Общий).

При появлении на выходе счетчика 38 кода «11 на выходах 24 и 26 появляется «1 и регистры 5 и 7 .переключаются в режим параллельной записи. Одновременно на выходе 32 появляется короткий импульс, формируемый одновибратором 41, и регистры 5 и 7 обнуляются.

Далее, по фронту сигнала с выхода 20 в регистр 5 переписывается значение 2pip2X Х(1-cosa), поступающее с выхода регистра 6 через коммутатор 3 (на выходе 28 «1) и сумматор-вычитатель 4 (регистр 5 обнулен, на выходе 27 «О). При появлении на выходе счетчика 38 кода «12 значение (р1-р2) с выхода сумматора-вычитателя 12 (на выходе 23 «1.) через коммутатор 1 (на выходах 21 и 22 «01) поступает на кадра- тор 2, с выхода которого значение (pi-р) через коммутатор 3 (на выходе 28 «О) поступает на первый вход сумматора-вычитателя 4, на второй вход которого из регистра 5 поступает значение 2pip2 (1-cosa). При этом на выходе сумматора-вычитателя 4 формируется значение S pt - -2pip2cosa (pi-р2)+2pip2 X (1-cosa) и фронтом сигнала с выхода 20 записывается в регистр 5.

При появлении на выходе счетчика 38 кода «13 на выходе 25 появляется «О, блокирует прохождение импульсов через элемент И 37 и разрещает прохождение сигнала с входа 33, соединенного с выходом старщего разряда регистра 5, на второй вход элемента 40 памяти через элемент 2НЕ-И 39. Если в старшем разряде регистра 5- «О, то на втором входе элемента 40 памяти и на выходе 26 будет «1, регистр 5 будет в режиме «Сдвиг влево, одновременно на выходе 30 при каждом очередном сдвиге будет появляться импульс, поступающий на С-вход счетчика 8.

При появлении в старщем разряде ре- гистра 5 (вход 33)- «1 на втором входе элемента 40 памяти и на выходе 26, в соответствии с прошивкой элемента 40 памяти, появляется «О, после чего значения в регистре 5 и счетчике 8 не изменяются (на выходах 25 и 26 «00, на выходе 30 отсутст- вуют импульсы). Одновременно на выходе 31 появляется сигнал «Готовность результата. При этом в (п-f 1) старших разрядах регистра 5 будет приближенное (с точностью до n + l значащих цифр) значение S « 2, где 1 Ei; п - разрядность аргументов pi; 1 - значение кода на выходах счетчика 8 (количество сдвигов информации в регистре 5); Pi - значение млад

шего разряда кода; fa разрядов кода. Так как

значение старших

0

5

0

5

0

5

0

0

5

S -2 - 2

. 2. 12 2 в блоке 9 извлечения квадратного корня по значению S и значению fi («О или «1) табличным путем определяется значение корня, являющееся мантиссой результата, и поступает на выход 35, при этом на выходах старщих разрядов счетчика 8 (выход 34) присутствует порядок результата. Причем при S О в старщем разряде регистра 5 единица все равно появляется, т. к. ня DL-входе - «Ь (для 133 серии допускается: вход отключен).

При неоДходимости вычисления функции Z аргументы подаются на входы 14 и 15, а на входах 16 и 17 фиксируются коды с разностью, соответствующей л/2.

Предлагаемое устройство позволяет без значительного увеличения аппаратных средств производить вычисление расстояния между точками, заданными в полярных координатах, что позволяет эффективно его использовать для обработки больших массивов информации в системах, работающих в реальном масштабе времени.

Формула изобретения

Вычислительное устройство, содержащее три регистра, два сумматора-вычитателя, блок синхронизации, элемент И, первый вход которого соединен с выходом первого регистра, первый выход блока синхронизации соединен с входами сброса первого и второго регистров, отличающееся тем, что, с целью расщирения функциональных возможностей за счет обеспечения возможностей вычисления расстояния между точками, заданными в полярных координатах, в него введены вычитатель, квадратор, счетчик, блок извлечения квадратного корня, два коммутатора, функциональный преобразователь, причем входы задания первого и второго модулей векторов устройства соединены с первым и вторым информационными входами первых сумматора-вычитателя и коммутатора, выход первого сумматора-вычитателя соединен с третьим информационным входом первого коммутатора, выход которого соединен с информационным входом квадратора, выход которого соединен с первым информационным входом второго коммутатора, выход которого соединен с первым информационным входом второго сумматора-вычитателя. выход которого соединен с информационными входами второго и третьего регистров, выход второго регистра соединен с вторым информационным входом третьего коммутатора, второй выход блока синхронизации соединен с син- хровходами первого и второго регистров, третий выход блока синхронизации соединен

с управляющим входом первого сумматора- вычитателя, четвертый и пятый выходы блока синхронизации соединены с первым и вторым управляющими входами первого коммутатора, щестой и,седьмой выходы блока синхронизации соединены с управляющим входом второго коммутатора и вторым входом элемента И соответственно, восьмой выход блока синхронизации соединен с управляющим входом второго сумматора-вычитателя и входом сброса третьего регистра, выход элемента И соединен с синхровходом третьего регистра, девятый выход блока синхронизации соединен с входом установки в «О первого регистра, десятый выход блока синхронизации соединен с входом установки в «1 второго регистра, одиннадцатый выход блока синхронизации соединен с входом сбро- .са счетчика и входом установки в «О второго регистра, двенадцатый выход блока синхронизации соединен со счетный входом счетчика, тринадцатый выход блока синхро0

5

низации является выходом признака готовности результата устройства, входы задания первого и второго полярных углов устройства соединены с первым и вторым информационными входами вычитателя, выход которого соединен с информационным входом функционального преобразователя, выход которого соединен с информационным входом первого регистра, выход младщего разряда счетчика соединен с входом строби- рования блока извлечения квадратного корня, выход старшего разряда второго регистра соединен с входом управления режимом блока синхронизации, выход младщих разрядов второго регистра соединен с вторым информационным входом второго сумматора- вычитателя и информационным входом блока извлечения квадратного корня, выход стар- щих разрядов счетчика является выходом порядка результата устройства, выход блока извлечения квадратног о корня является выходом мантиссы результата устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функции @ | 1984 |

|

SU1166102A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1988 |

|

SU1624699A1 |

| Устройство для определения среднеквадратического значения | 1983 |

|

SU1130877A1 |

| Квадратор | 1987 |

|

SU1501049A1 |

| Устройство для вычисления функций | 1990 |

|

SU1709304A1 |

| Многомерный статистический анализатор сглаженной эффективной мощности нагрузки | 1991 |

|

SU1836692A3 |

| Устройство для анализа характеристик спектра | 1983 |

|

SU1142844A1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

| Устройство для вычисления функции arctg y/x | 2017 |

|

RU2642385C1 |

| Сглаживающее устройство | 1984 |

|

SU1265797A1 |

Изобретение относится к вычислительной технике. Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения возможности вычисления расстояния между точками заданными в полярных координатах. Вычислительное устройство содержит коммутаторы 1 и 3, квадратор 2, три регистра 5-7, два сумматора-вычитателя 4 и 12, вычитатель 11, функциональный преобразователь 10f(o) (l-созл), где с. - W 15 разность полярных углов точек, блок 9 извлечения квадратного корня, счетчик 8, схему И 13, блок 19 синхронизации. Вычисление производится в соответствии с формулой ,2+9|-29i9i- cos(oc, - лг. ), где S- расстояние между точками; Pi , Pi - радиусы-векторы точек; tk, , i - полярные углы точек, в следующей последовательности: вычисляется (y,-f9l). затем 2р,9г (р, +pi) -(р-, +Р ). затем производится умножение (2pip2)(l-cosa) посредством сдвига информации в регистрах 5 и 7 и накопления частичных сумм в регистре 6. Далее вычисляется S (pi-р2) + +2pip2(l-cosa) p2-2pip2cosa. Полученное значение сдвигается в регистре 5 до появления логической единицы в старшем разряде, количество сдвигов фиксируется счетчиком 8 и определяет порядок результата, а по старшим разрядам кода S блоком 9 извлечения корня определяется мантисса результата. 1 з.п. ф-лы, 3 ил. 3 (Л 16 77 00 ьо ел 4i О5 00 г

9иг.г

32

.5

| Устройство для вычисления квадратного корня из суммы квадратов двух чисел | 1982 |

|

SU1027719A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU1024914A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-23—Публикация

1986-03-25—Подача