3154

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники, а также в измерительной технике и в преобразователях иастотьь

1Гель изобретения - расширение функциональных возможностей умножителя за счет введения в выходнок сигнал постоянной частртной подставки с -возможностью ее изменения,

На фиг.1 изображена электрическая структурная схема предлагаемого умножителя; на фиг.2 - блок управления.

Умножитель содержит генератор 1 тактовых импульсов, первый элемент И 2. 3 управления, делитель 4 частоты, первый задатчик 5 кода, сумматор 6, счетчик 7 импульсов, мультиплексор 8, делитель 9 кодов, демуль- типлексор 10, регистр 11 хранения, делитель 12 с переменным коэффициентом деления, второй-задатчик 13 кода, третий задатчик 14 кода и второй элемент И 15,

Генератор 1 тактовых импульсов через первый элемент И 2 соединен с тактовым входом делителя 12 с переменным коэффициентом деления, выход которого соединен с выходной тиной 16, а информационные входы соединены с выходами регистра 11 хранения.

Первый вход блока 3 управления соединен со входной шиной 17, второй вход - с выходом генератора 1 тактовых импульсов, с тактовым вхоцом делителя 9 кодов и со входом делителя 4 частоты, выход которого соединен с первым входом второго элемента И 15, выход которого соединен со счетным входом счетчика 7 импульсов, информационные входы которого соединены с выходами первого задатчика 5 кода, выходы - с первой группой входов мультиплексора 8, выходы которого соеди- нены с первой группой входов делителя 9 кодов, вторая группа входов которого соединена с выходами второго задатчика 13 кода, выходы - со входами демультиплексоря 10, первая группа выходов которого соединена с информационными входами регистра 11 хранения, вторая группа выходов - с первой группой входов сумматора 6, вторая группа входов которого соединена с выходами третьего задатчика 14 кодов, выходы - со второй группой входов мультиплексора 8. Первый и второй выходы блока 3 управления соединены со

0

5

0

5

д50

5

0

50

5

вторыми входами соответственно перво- го 2 и второго 15 элементов И, третий выход соединен - установочным входом счетчика 7 импульсов, четвертый выход - со входом управления мультип.пек сора 8, пятый выход - со входом запуска делителя 9 кодов, шестой выход - со входом зшравления де- мультиплексора 10 и седьмой выход - с входом записи регистра 11 хранения.

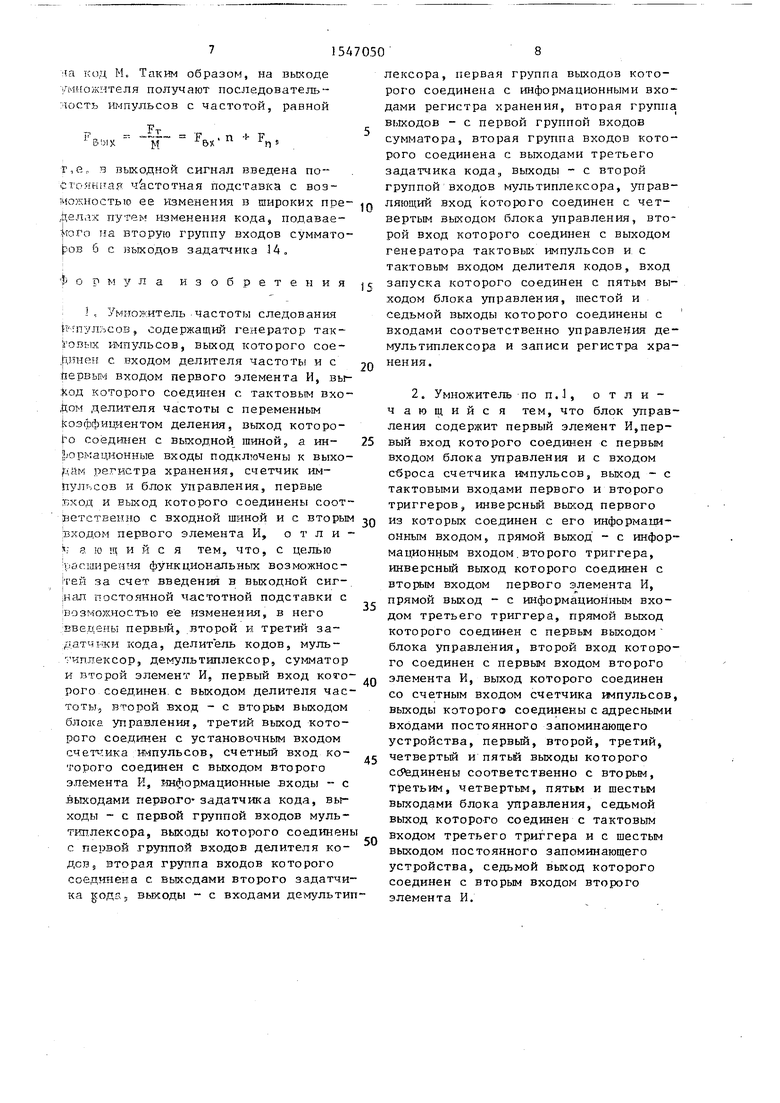

Блок 3 управления содержит первый элемент И 18, первый вход которого соединен с первым входом блока 3 управления и со входом сброса счетчика 19 импульсов, выход - с тактовыми входами первого 20 и второго 21 триггеров, инверсный выход первого из которых соединен с его информационным входом, прямой выход - с информационным входом второго триггера 2 , инверсный выход которого соединен со вторым входом первого элемента И 18, прямой выход - с информационньм входом третьего триггера 22, прямой вы-| ход которого соединен с первым выходом блока 3 управления, второй вход которого соединен с первым входом второго элемента И 23, выход которого соединен со счетным входом счетчика 39 импульсов, выходы которого соединены с адресными входами постоянного запоминающего устройства 24, первый, второй, третий, четвертый и пятый выходы которого соединены соответственно с вторым, третьим, четвертым, пятым и шестым выходами блока 3 управления, седьмой выход которого соединен с тактовым входом третьего триггера 22 и с шестым выходом постоянного запоминающего устройства 24, седьмой выход которого соединен со вторым входом второго элемента И 23.

Умножитель работает следующим образом .

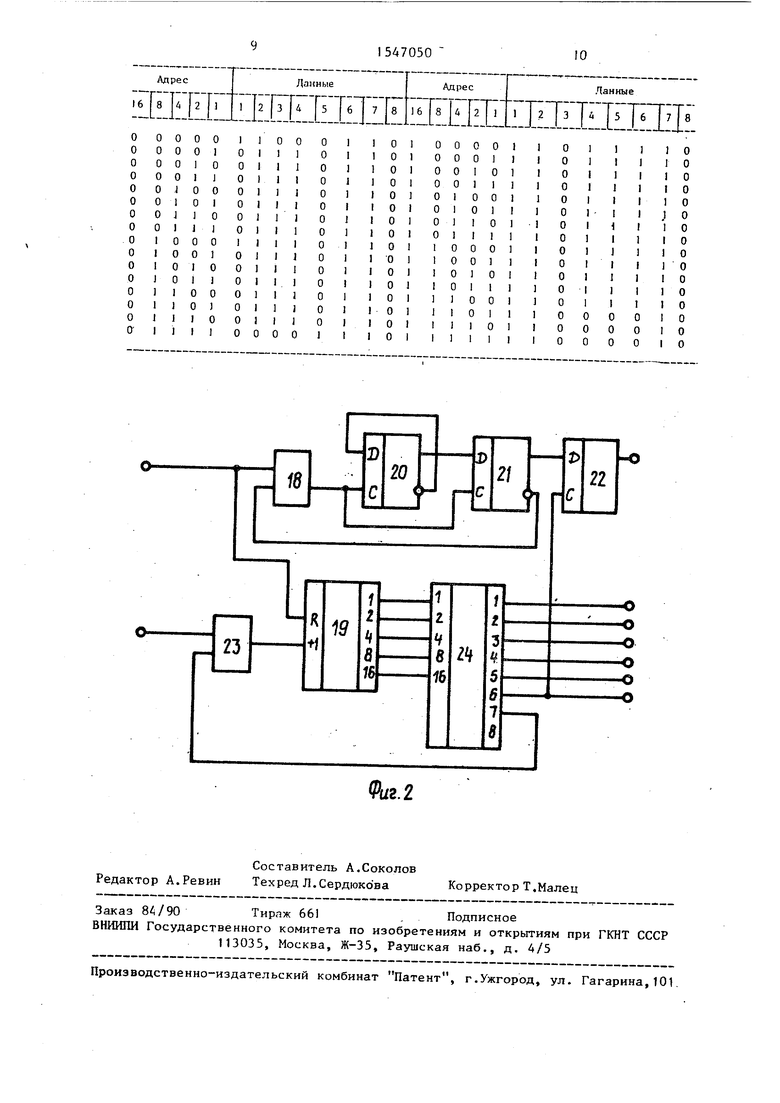

В исходном состоянии на первом выходе блока 3 установлен низкий уровень (на структурной схеме цепи начальной установки условно не показан) , в результате чего элемент И 2 закрыт по второму входу, импульсы тактовой частоты с выхода генератора 1 на тактовый вход делителя 12 не поступают, счетчик 19 обнулен и на выходе запоминающего устройства 24 установлен код, соответствующий нулевому адресу, приведенному на таблице. По приходу второго импульса на шину 17 триггер 21 переключается в единичное состояние и сигнал низкого уровня с инверсного выхода триггера 21 запрещает прохождение входного сигнала на тактовые входы триггеров 20 и 21 . По приходу тридцать второго импульса тактовой частоты положительный перепад сигнала на шестом выходе запоминающего устройства 24 переключает триггер 22 в единичное состояние. . Этим сигналов на первом выходе блока 3 открывается по второму входу элемент И 2 и импульсы тактовой частоты с выхода генератора 1 поступают на вход делителя 12, в результате чего на шине появляется сигнал с частотой FBb,x. Задержка после включения необг- ходима для предотвращения появления ложной частоты на выходе умножителя в первый момент после включения питания.

Таким образом, после первых двух импульсов входной частоты и тридцати двух импульсов тактовой частоты.в регистре 11 хранится верное число, опт ределяющее выходную частоту деления, а следовательно, верной будет и частота на выходе умножителя.

Карта программирования запоминающего устройства 24 приведена в таблице.

Рассмотрим работу умножителя посл прихода 1-го импульса входной частот на шину 17. На вход делителя 4 частоты с коэффициентом деления, равным п, поступают импульсы с выхода генератора J. С приходом первого импульса тактовой частоты после фронта 1-го импульса входной частоты на втором выходе блока 3 появляется низкий уровень, закрывающей элемент И 15. Импульсы делителя 4 частоты на счетный вход счетчика 7 не поступают, в результате чего в счетчике хранится число, равное Fr

-тактовая частота на выходе

генератора 1 ;

-входная частота на шине 17; п - коэффициент деления делителя

4 частоты.

В этот же момент на четвертом выходе блока 3 появляется высокий уроо N где FT

F8

вень, что соответствует подключению мультиплексором 8 выводов счетчика 7 к первой группе входов делителя 9 кодов. Положительный перепад сигнала на пятом выходе блока 3 запускает дели0

5

0

тель 9 кодов, который тактируется импульсами генератора 1 и осуществляет деление двоичного кода числа 1, по даваемого с выходов задатчика 13 кода на вторую группу входов делителя 9 кодов, на число N, т.е. через четырнадцать тактов на выходе делителя 9 имеет код, равный N 1/N.

Демультиплексор 10 сигналом с шестого выхода блока 3 включен так, что выходы делителя 9 подключены к первой группе входов сумматора 6, на вторую группу входов которого подается код числа а с выходов задатчика 14, причем

а - Fn/Fr.

Таким образом, на выходах сумматора 6 получают код, равный

1/N + а.

По приходу последнего тактового импульса первого цикла деления муль5 типлексор 8 переключается так, что выходы сумматора 6 оказываются подключенными к первой группе входов делителя 9. В этот же момент на третьем выходе блока 3 появляется низкий уроQ вень, по которому происходит запись кода с выходом задатчика 5 в счетчик 7. Эта предварительная запись необходима для учета в измерении периода входной частоты того времени, когда счетчик 7 остановлен. По приходу следующего тактового импульса на втором выходе блока 3 появляется высокий уровень и счетные импульсы через элемент И 15 начинают поступать на счет- ный вход счетчика 7. Б этот же момент начинается второй цикл деления, по окончании которого на.-выходах делителя 9 получается код, равный

1 J

Fex-n

5

0

М - ми..., «... М т,ш--г-ппТ

5

ТГ

а

т; tFT

FB nrF

В момент прихода последнего такто- вого импульса второго цикла деления низкий уровень на шестом выходе блока 3 переключает демультиплексор 10 так, что выходы делителя 9 оказываются подключенными к информационным входам регистра П, запись в который происходит по приходу следующего тактового импульса положительным перепадом сигнала на седьмом выходе бло- .ка 3. Делитель 12 делит частоту FT

ч t ciu M. Таким образом, на выходе чшолчтеля получают последователь- гость импульсов с частотой, равной

т- „II.

D JX f.t

F&x n + Fn

Г,р, т чыходной сигнал введена по- Сто- ti ap частотная подставка с воз- ОАностыо ее изменения в широких пое- йел, путем изменения кода, подаваемого на вторую группу входов сумматоров б с выходов задатчикз ЗА.

Ц/ о Р м у л a изобретения

1 . Укпо т итель частоты следования Г пульсов, содержащий генератор так- 1овых импульсов, выход которого сое- Й ТНРЧ с входом делителя частоты и с йервькч входом первого элемента И, вьг- Код которого соединен с тактовым входом делителя частоты с переменным (соэйсЬициентом деления, выход КОТОРОГО соединен с выходной шиной, а информационные входы подключены к выхо- регистра хранения, счетчик им- пултсов и блок управления, первые тзхоц и вькод которого соединены соответствехтно с входной шчной и с вторым зо из которых соединен с его информаш35

40

входом первого элемента И, о т л и - ю и и и с я тем, что, с целью плгыиреччя функциональнь х возможностей за счет введения в выходной сигнал постоянной частотной подставки с возможностью ее изменения, в него Евепены первый, второй и третий за- атчтхи кода, делитель кодов, мультиплексор, декулътиплексор, сумматор и второй элемент И, первый вход которого соединен с выходом делителя частоты, второй вход - с вторым выходом блока управления, третий выход которого соединен с установочным входом счетчика импульсов, счетный вход КОТОРОГО соединен с выходом второго элемента К, информационные -входы - с выходами первого- задатчика кода, выходы - с первой группой входов мультиплексора, выходы которого соединены г первой группой входов делителя ко- ДС13, вторая группа входов которого соединена с выходами второго задатчика кодг; выходы - с входами демультип45

онным входом, прямой выход - с информационным входом второго триггера, инверсный выход которого соединен с вторым входом первого элемента И, прямой выход - с информационным входом третьего триггера, прямой выход которого соединен с первьм выходом блока управления, второй вход которого соединен с первым входом второго элемента И, выход которого соединен со счетным входом счетчика импульсов, выходы которого соединены с адресными входами постоянного запоминающего устройства, первый, второй, третий, четвертьй и пятьй выходы которого соединены соответственно с вторым, третьим, четвертым, пятьм и шестым выходами блока управления, седьмой выход которого соединен с тактовым входом третьего триггера и с шестым выходом постоянного запоминающего устройства, седьмой выход которого соединен с вторым входом второго элемента И.

0

5

лексора, первая группа выходов которого соединена с информационными входами регистра хранения, вторая группа выходов - с первой группой входов сумматора, вторая группа входов которого соединена с выходами третьего задатчика кода, выходы - с второй группой входов мультиплексора, управляющий вход которого соединен с четвертым выходом блока управления, второй вход которого соединен с выходом генератора тактовых импульсов и с тактовым входом делителя кодов, вход запуска которого соединен с пятым выходом блока управления, шестой и седьмой выходы которого соединены с входами соответственно управления де- мультиплексора и записи регистра хранен ия.

2. Умножитель поп.1, о т л и - чающийс я тем, что блок управления содержит первый элемент И,первый вход которого соединен с первым входом блока управления и с входом сброса счетчика импульсов, выход - с тактовыми вхоцами первого и второго триггеров, инверсный выход первого

5

0

5

онным входом, прямой выход - с информационным входом второго триггера, инверсный выход которого соединен с вторым входом первого элемента И, прямой выход - с информационным входом третьего триггера, прямой выход которого соединен с первьм выходом блока управления, второй вход которого соединен с первым входом второго элемента И, выход которого соединен со счетным входом счетчика импульсов, выходы которого соединены с адресными входами постоянного запоминающего устройства, первый, второй, третий, четвертьй и пятьй выходы которого соединены соответственно с вторым, третьим, четвертым, пятьм и шестым выходами блока управления, седьмой выход которого соединен с тактовым входом третьего триггера и с шестым выходом постоянного запоминающего устройства, седьмой выход которого соединен с вторым входом второго элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следования импульсов | 1989 |

|

SU1728964A2 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Устройство для контроля и диагностики радиоэлектронной аппаратуры | 1986 |

|

SU1432463A1 |

| Устройство для автоматического копирования линии сварного соединения | 1985 |

|

SU1318356A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2040050C1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| Устройство для индикации | 1990 |

|

SU1795513A1 |

| Устройство для многоканальной записи аналоговых процессов | 1985 |

|

SU1304070A1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| Логический пробник | 1987 |

|

SU1525636A1 |

Изобретение может использоваться в устройствах автоматики и вычислительной технике, а также в измерительной технике и в преобразователях частоты. Цель изобретения - расширение функциональных возможностей за счет введения в выходной сигнал постоянной частотной подставки с возможностью изменения последней - достигается введением делителя 9 кодов, мультиплексора 8, демультиплексора 10, сумматора 6, элемента И 15 и задатчиков 5, 13 и 14 кода с организацией новых функциональных связей. Устройство также содержит генератор 1 тактовых импульсов, элемент И 2, блок 3 управления, делитель 4 частоты, счетчик 7 импульсов, регистр 11 хранения, делитель 12 с переменным коэффициентом деления, входную и выходную шины 17 и 16. 1 з.п. ф-лы, 2 ил., 1 табл.

| Умножитель частоты | 1985 |

|

SU1305822A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Умножитель частоты следования импульсов | 1984 |

|

SU1256181A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровой умножитель частоты следования периодических импульсов | 1983 |

|

SU1164858A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-02-28—Публикация

1988-05-16—Подача