Изобретение относится к электросвязи, может найти применение в системах пере-- дачи данных и является усовершенствованием изобретения по авт. св. № 1462507.

Целью изобретения является повышение помехозащищенности.

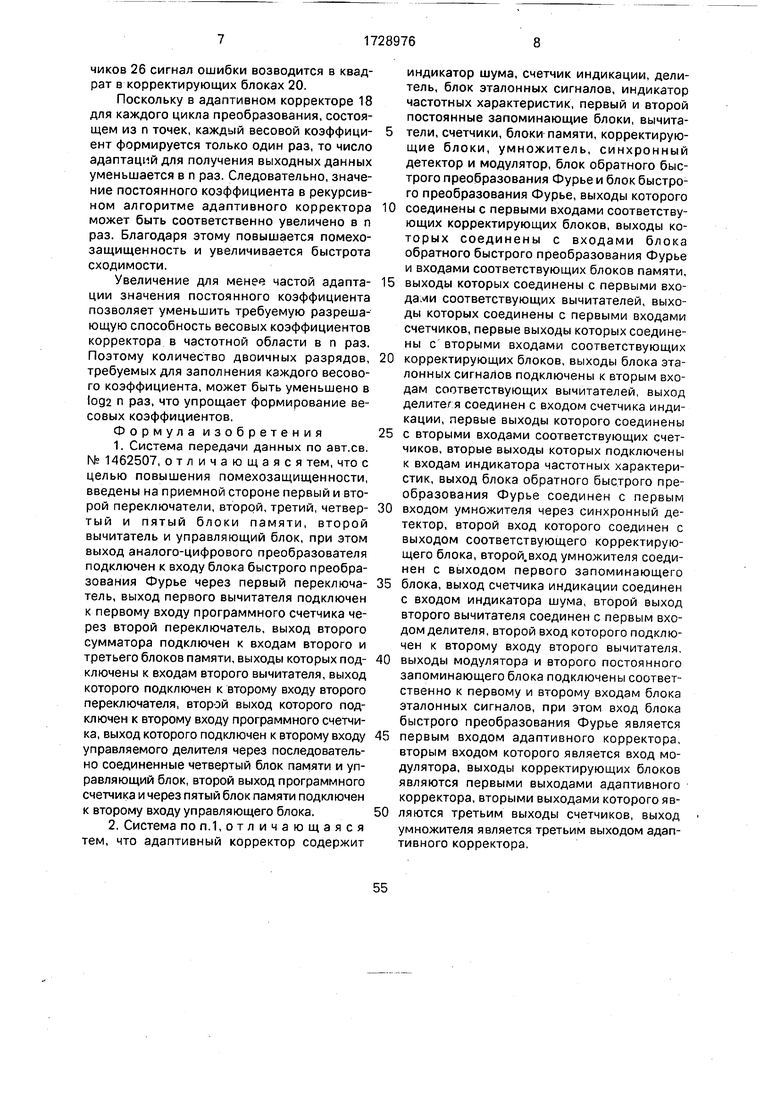

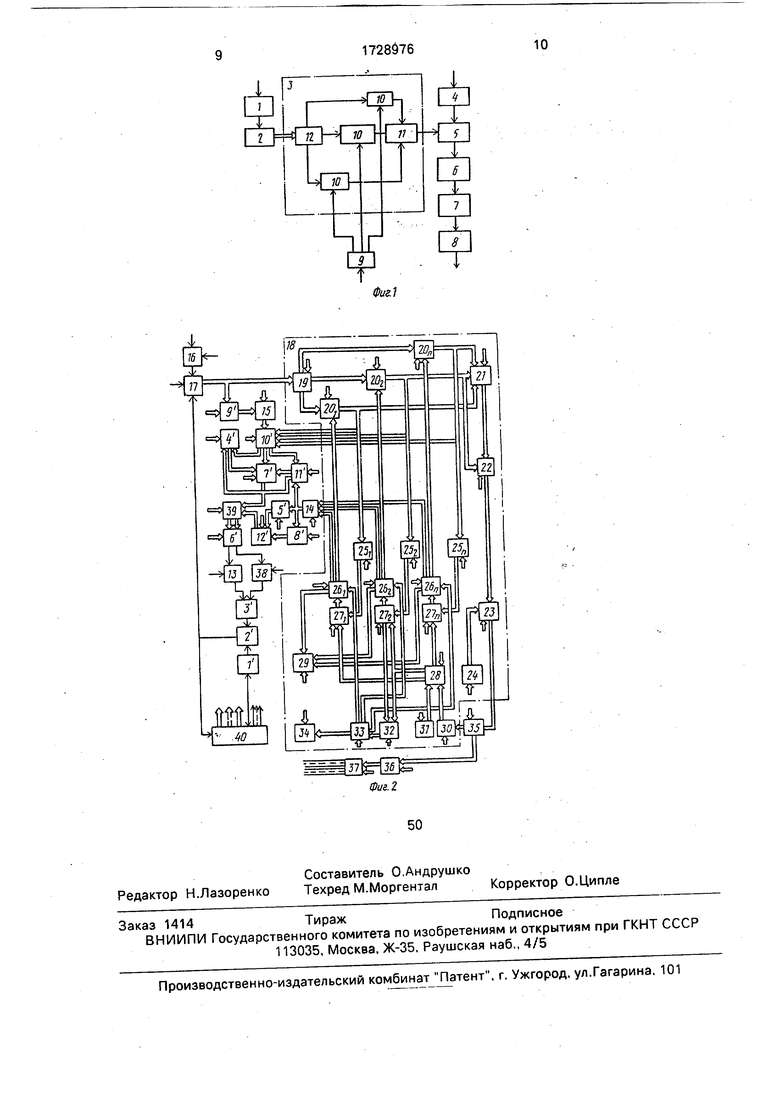

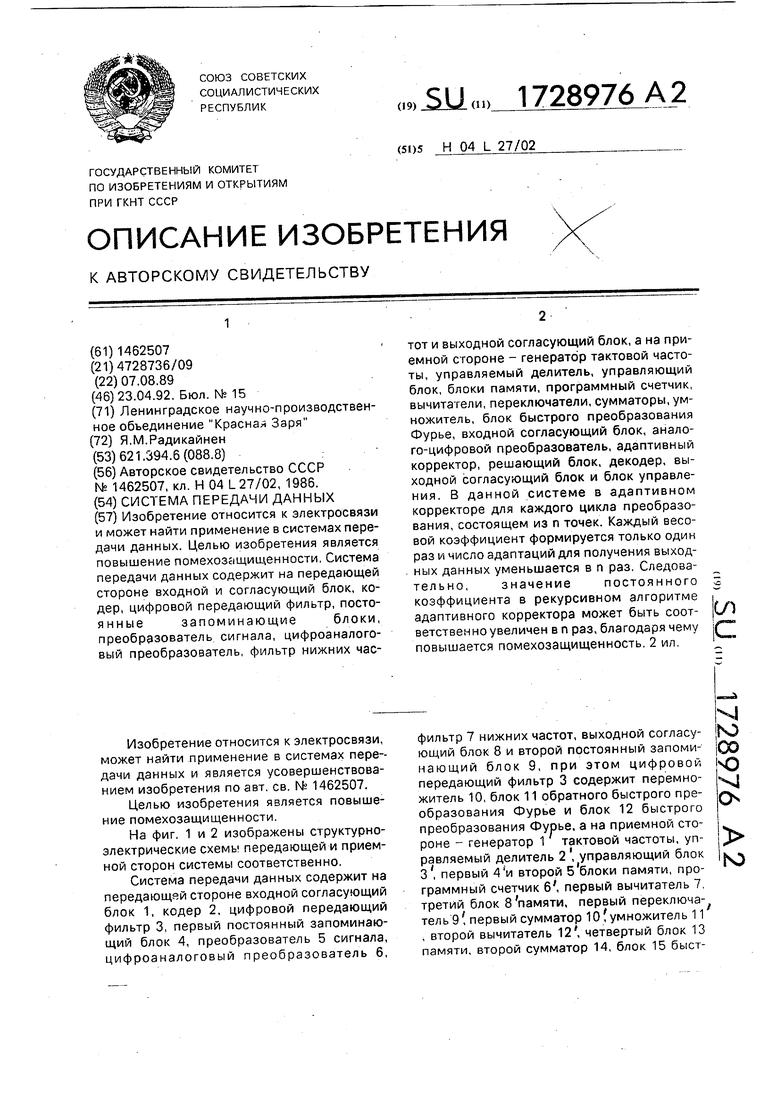

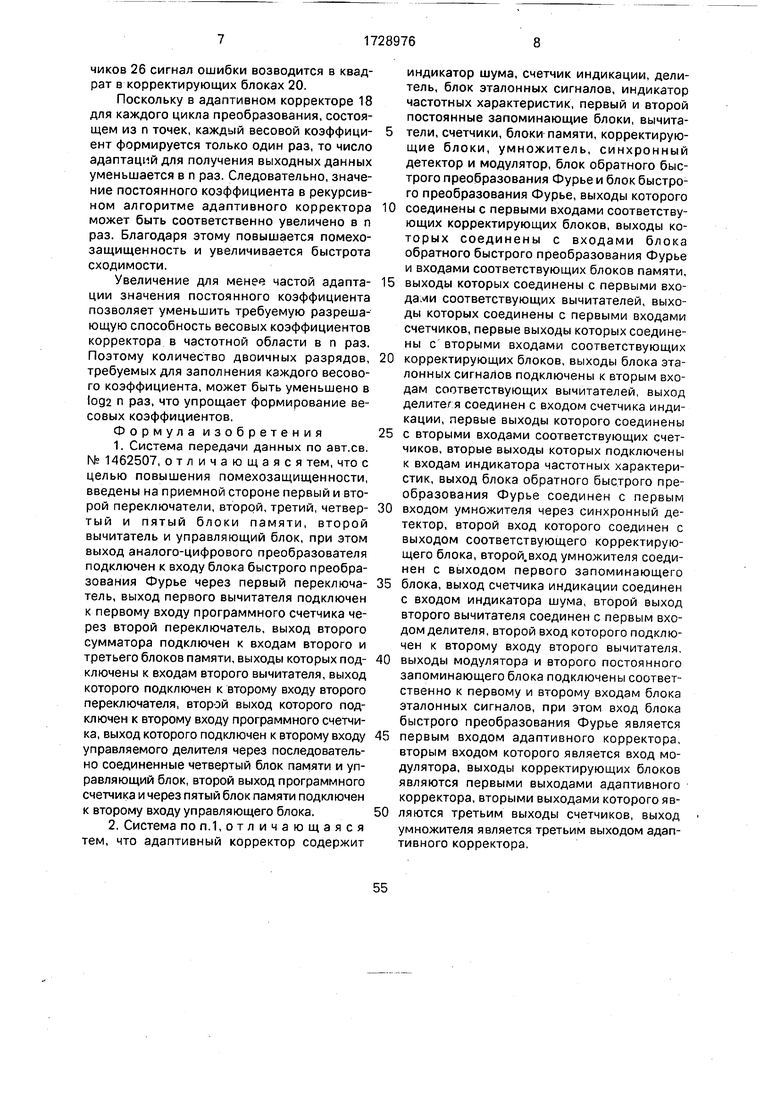

На фиг. 1 и 2 изображены структурно- электрические схемы передающей и приемной сторон системы соответственно.

Система передачи данных содержит на передающей стороне входной согласующий блок 1, кодер 2, цифровой передающий фильтр 3, первый постоянный запоминающий блок 4, преобразователь 5 сигнала, цифроаналоговый преобразователь 6,

фильтр 7 нижних частот, выходной согласующий блок 8 и второй постоянный запоминающий блок 9, при этом цифровой передающий фильтр 3 содержит перемножитель 10, блок 11 обратного быстрого преобразования Фурье и блок 12 быстрого преобразования Фурье, а на приемной стороне - генератор 1 тактовой частоты, управляемый делитель 2 , управляющий блок 3, первый 4 и второй 5 блоки памяти, программный счетчик 6, первый вычитатель 7, третий блок 8 памяти, первый переключатель 9, первый сумматор 10(умножитель 11 , второй вычитатель 12, четвертый блок 13 памяти, второй сумматор 14, блок 15 быстч

ю

00

ю XI о

N5

рого преобразования Фурье, входной согласующий блок 16, аналого-цифровой преобразователь 17 и адаптивный корректор 18, содержащим блок 19 быстрого преобразования Фурье, корректирующие блоки 20, блок 21 обратного быстрого преобразования Фурье, синхронный детектор 22, умно- житель 23, первый постоянный запоминающий блок 24, блоки 25 памяти, счетчики 26, вычитатели 27, блок 28 эталонных сигналов, индикатор частотных характеристик 29, модулятор 30, второй запоминающий блок 31, делитель 32, счетчик 33 индикации и индикатор 34 шума, а также решающий блок 35, декодер 36, выходной согласующий блок 37, пятый блок 38 памяти, второй переключатель 39 и блок 40 управления.

Входной согласующий блок 16 приемной стороны системы передачи данных служит для поддержания постоянным уровня входного сигнала. Кроме того, во входной согласующий блок 16 входит преобразователь Гильберта. Аналого-цифровой преобразователь 17 состоит из двух частей соответственно для синфазной и квадратурной составляющей сигнала. Синфазная и квадратурная составляющие сигнала в устройстве обрабатываются поочередно. Частота дискретизаци / приемника принимается равной Рдр. Пр 2 FT. Отсчет сигнала с выхода адаптивного корректора 18 поступает через синхронный детектор 22 и умножитель 23 в решающий блок 35, в котором производится оценка принимаемых информационных символов ап min Vxn - ai/, здесь min 1b (x) - функция, обратная функции minf(x), т.е. принимающая значение аргумента х, минимизирующего Ь(х).

Адаптивный корректор 18 служит для борьбы с линейными искажениями, Он работает в частотной области с использованием.блока 19 на 32 и 64 точки. Также выполнен блок 21. Между блоками 19 и 21 включаются корректирующие блоки 20i,...,20n, представляющие в простейшем случае умножители либо сумматоры. Сигнал от решающего блока 35 поступает через модулятор 30 на блок 28 эталонного сигнала, который может быть выполнен идентично с блоками 19(21).

Эталонный сигнал с выхода блока 28 и задержанный с помощью блоков 25i,...,25n памяти сигнал с выходов корректирующих

блоков 20т20п сравниваются в вычитателях 27i27П, и сигнал ошибки с соответствующим знаковым разрядом подается с помощью счетчиков 26i,...26n на регулировку корректирующих блоков 20i,...20n. Перед

й

началом коррекции счетчики устанавливаются в номинальное положение (в десятичном исчислении).

Здесь может быть осуществлена также

5 индикация частотных характеристик с помощью индикатора 29 частотных характеристик, С помощью делителя 32 и счетчика 33 индикации может меняться скорость регулировки коррекции в зависимости от вели10 чины отношения сигнал/шум. Когда не ставится задача отображения характеристик и отношения сигнал/шум, делитель 32 и счетчики 33 индикации не требуются. Для тактовой синхронизации с единич15 ного интервала снимается 2 выборки.

С помощью 2-, 4- или 8-точечного блока 15 для тактовой синхронизации преобразуются сигналы первых выборок, затем вторых выборок, соответствующих единичным

20 интервалом. Разность сумм определенных частот с выхода блока 15 первых и вторых выборок подается через второй переключатель 39, программный счетчик б , блоки 13 и 38 памяти на управляющий блок 3, Сумми- 25 рование сигнала указанных частот с выхода блока 15 осуществляется в первом сумматоре 10. Здесь могут суммироваться сигналы двух частот спектра.

В определенных случаях достаточно

30 сигнала одной частоты спектра, т.е, без суммирования. Таким образом, здесь применяются те частоты, которые в наибольшей степени содержат информацию о тактовой частоте. Все это обеспечивает быстрое

35 вхождение в связь и без настроечной комбинации сигнала, что весьма важно при срывах связи от различного рода помех и при коммутациях. Для увеличения точности синхронизации можно ввести поправку, опре40 деляющуюся влиянием искажений характеристики канала связи, во второй вы- читатель 12 после вхождения в связь, Тогда сигналы с выходов соответствующих счетчиков суммируются с помощью первого сум45 матора 10. Полученная сумма умножается с помощью умножителя 11 на сумму от второго сумматора 14. Результат подается на первый вычитатель 7 и первый блок 4 памяти. Далее, как описано выше. В большин50 стве случаев нет необходимости осуществлять суммирование первым сумматором 10 при каждом цикле блока 15. Поэтому между вторым вычитателем 12 и вторым сумматором 14 может быть включен второй

55 блок 5 памяти. В зависимости от требований ошибка тактового сигнала может быть выделена от синфазной составляющей сигнала, от квадратурной составляющей сигнала или от обеих составляющих.

После вхождения в связь сигнал на первый сумматор 10 может подаваться с выходов корректирующих блоков 20, а с выхода блока 15 сигнал не подается.

Сперва преобразуются первый выборки с помощью блока 19, сигналы которого с выходов корректирующих блоков 20 подаются на первый сумматор 10 . Затем преобразуются вторые выборки.

Если не подать несущую частоту на вход блока 21, то для получения неискаженного демодулированного сигнала с выхода блока 21 требуется усложнить схему блока 21. Поэтому во многих случаях целесообразно подавать также несущую частоту на вход блока 21, Тогда на выходе блока 21 необходимо включить синхронный детектор 22, второй вход которого соединен с соответствующим входом блока 21. В состав блока 22 входит тактовый генератор несущей частоты со схемой выделения ошибки выполненной традиционно.

Кроме того, чтобы иметь сигнал с несущей частотой на выходе блока 28 эталонных сигналов по аналогии с сигналом на выходах корректирующих блоков 20 перед блоком 28 эталонных сигналов включается модулятор 30.

Перед запуском устройства в работу со второго постоянного запоминающего блока 31 подается соответствующий сигнал на блок эталонных сигналов 28, приводящий счетчики 26 корректора в положение для предварительного наилучшего устранения искажений в канале связи в зависимости от количества переприемных участков в нем. Это дополнительно ускорит вхождение в связь, что имеет большое значение в том случае, когда ошибка синхронизации снимается счетчиком 26.

Второй запоминающий блок 31 может быть установлен после блока эталонных сигналов 28, однако в этом случае сигналы во второй запоминающий блок 31 должны быть записаны в частотной области. Блоки 13 и 38 памяти, включенные на выходе программного счетчика 6, позволяют более точно выбрать необходимый момент подачи сигнала на управляющий блок 3.

Путем включения на выходе второго сумматора 14, третьего блока 8 памяти и второго вычитателя 12, выход которого соединен с входом второго переключателя 39 имеем возможность в каналах связи с малыми шумами обходиться без блоков 11, 7, 4, 14, 15, 9 и этим существенно сократить количество вычислительных операций. Тогда сигнал ошибки для схемы синхронизации снимается с выходов счетчиков 26. Причем этот сигнал может сниматься с одного счетчика (например, со счетчика соответствующей несущей частоты) либо с нескольких. или со всех счетчиков 26, в зависимости от требования точности и качества канала связи.

Сигналы после данного цикла преобразования Фурье со счетчиков 26 суммируются во втором сумматоре 14 и поступают в третий блок 8 памяти. А сигналы счетчиков

0 26 после следующего цикла, просуммировав во втором сумматоре 14, вычитаются во втором вычитателе 12 с числа, записанного в третий блок памяти 8, и ошибка в той или иной полярности поступает на второй пере5 ключатель 39 и т.д. Когда нет ошибки синхронизации на выходах счетчиков 26 сигнал близок к 0. При появлении ошибки синхронизации сигнал на выходе счетчиков 26 отклоняется от 0 в ту или другую сторону и эта

0 ошибка выявляется на выходе второго вычитателя (элемента сравнения) 12 . Далее ошибка через второй переключатель 39, программируемый счетчик 6 и соответствующие блоки 13 и 38 памяти поступает на

5 управляющий блок 3.

В простейшем случае со счетчика 26 достаточно подать сигнал со знакового разряда непосредственно на блоки памяти 13 и 38, т.е. при отклонении ошибки в одну сто0 рону подается сигнал на вычитание импульса в управляемом делителе, а при отклонении ошибки в другую сторону подается сигнал на добавление импульса.

Когда корректирующие блоки представ5 ляют собой умножители, то перед началом коррекции счетчики 26 устанавливаются Б номинальное положение (в десятичном исчислении единицы), а в процессе коррекции к этой единице будет вносится сигнал ошиб0 ки с тем или другим знаком.

В процессе коррекции в счетчиках 26 в соответствии с искажениями значение будет отклоняться от номинального в ту или другую сторону. С этим числом со счетчиков

5 26 умножается в корректирующем блоке 20 числа, приходящие с выхода блока 19, чем минимизируется ошибка.

Устройство может работать как по абсолютному критерию ошибки п, так и по квад0 ратичному критерию ошибки п2. В первом случае значение ошибки в корректирующем блоке 20 непосредственно умножается на подаваемый на его вход корректируемый сигнал. Во втором случае в корректирую5 идем блоке 20 предварительно значения ошибки возводятся в квадрат, а затем умножаются на подаваемый на корректирующий блок 20 сигнал, т.е. осуществляется коррекция. Среднеквадратичный критерий ошибки означает, что усредненный с помощью счетчиков 26 сигнал ошибки возводится в квадрат в корректирующих блоках 20.

Поскольку в адаптивном корректоре 18 для каждого цикла преобразования, состоящем из п точек, каждый весовой коэффициент формируется только один раз, то число адаптации для получения выходных данных уменьшается в п раз. Следовательно, значение постоянного коэффициента в рекурсивном алгоритме адаптивного корректора может быть соответственно увеличено в п раз. Благодаря этому повышается помехозащищенность и увеличивается быстрота сходимости.

Увеличение для менее частой адаптации значения постоянного коэффициента позволяет уменьшить требуемую разрешающую способность весовых коэффициентов корректора в частотной области в п раз. Поэтому количество двоичных разрядов, требуемых для заполнения каждого весового коэффициента, может быть уменьшено в loga n раз, что упрощает формирование весовых коэффициентов.

Формула изобретения

1.Система передачи данных по авт.се. № 1462507, отличающаяся тем, что с целью повышения помехозащищенности, введены на приемной стороне первый и второй переключатели, второй, третий, четвертый и пятый блоки памяти, второй вычитатель и управляющий блок, при этом выход аналого-цифрового преобразователя подключен к входу блока быстрого преобразования Фурье через первый переключатель, выход первого вычитателя подключен к первому входу программного счетчика через второй переключатель, выход второго сумматора подключен к входам второго и третьего блоков памяти, выходы которых подключены к входам второго вычитателя, выход которого подключен к второму входу второго переключателя, второй выход которого подключен к второму входу программного счетчика, выход которого подключен к второму входу управляемого делителя через последовательно соединенные четвертый блок памяти и управляющий блок, второй выход программного счетчика и через пятый блок памяти подключен к второму входу управляющего блока.

2.Система по п.1,отличающаяся тем, что адаптивный корректор содержит

индикатор шума, счетчик индикации, делитель, блок эталонных сигналов, индикатор частотных характеристик, первый и второй постоянные запоминающие блоки, вычита- тели, счетчики, блоки памяти, корректирующие блоки, умножитель, синхронный детектор и модулятор, блок обратного быстрого преобразования Фурье и блок быстрого преобразования Фурье, выходы которого

соединены с первыми входами соответствующих корректирующих блоков, выходы которых соединены с входами блока обратного быстрого преобразования Фурье и входами соответствующих блоков памяти,

выходы которых соединены с первыми входами соответствующих вычитателей, выходы которых соединены с первыми входами счетчиков, первые выходы которых соединены с вторыми входами соответствующих

корректирующих блоков, выходы блока эталонных сигналов подключены к вторым входам соответствующих вычитателей, выход делитегя соединен с входом счетчика индикации, первые выходы которого соединены

с вторыми входами соответствующих счетчиков, вторые выходы которых подключены к входам индикатора частотных характеристик, выход блока обратного быстрого преобразования Фурье соединен с первым

входом умножителя через синхронный детектор, второй вход которого соединен с выходом соответствующего корректирующего блока, второй.вход умножителя соединен с выходом первого запоминающего

блока, выход счетчика индикации соединен с входом индикатора шума, второй выход второго вычитателя соединен с первым входом делителя, второй вход которого подключен к второму входу второго вычитателя,

выходы модулятора и второго постоянного запоминающего блока подключены соответственно к первому и второму входам блока эталонных сигналов, при этом вход блока быстрого преобразования Фурье является

первым входом адаптивного корректора, вторым входом которого является вход модулятора, выходы корректирующих блоков являются первыми выходами адаптивного корректора, вторыми выходами которого являются третьим выходы счетчиков, выход умножителя является третьим выходом адаптивного корректора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система передачи данных | 1986 |

|

SU1462507A1 |

| СИСТЕМА ПЕРЕДАЧИ ДАННЫХ | 1991 |

|

RU2019049C1 |

| УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ | 1991 |

|

RU2033697C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ТАКТОВОЙ И НЕСУЩЕЙ ЧАСТОТ | 1991 |

|

RU2096917C1 |

| УСТРОЙСТВО ДЛЯ НАСТРОЙКИ КОРРЕКТОРА МЕЖСИМВОЛЬНОЙ ИНТЕРФЕРЕНЦИИ | 1991 |

|

RU2034404C1 |

| УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ | 1988 |

|

RU2033696C1 |

| Устройство для передачи и приема информации | 1987 |

|

SU1449989A1 |

| УСТРОЙСТВО ОЦЕНКИ И КОРРЕКЦИИ ПАРАМЕТРОВ КАНАЛА ДЛЯ ПРИЕМА COFDM-СИГНАЛОВ | 2008 |

|

RU2407198C2 |

| Устройство для распознавания контуров изображений | 1983 |

|

SU1156103A1 |

| Адаптивный фильтр | 1983 |

|

SU1116537A1 |

Изобретение относится к электросвязи и может найти применение в системах передачи данных. Целью изобретения является повышение помехозащищенности, Система передачи данных содержит на передающей стороне входной и согласующий блок, кодер, цифровой передающий фильтр, посто- янные запоминающие блоки, преобразователь сигнала, цифроаналого- вый преобразователь, фильтр нижних частот и выходной согласующий блок, а на приемной стороне - генератор тактовой частоты, управляемый делитель, управляющий блок, блоки памяти, программный счетчик, вычитатели, переключатели, сумматоры, умножитель, блок быстрого преобразования Фурье, входной согласующий блок, аналого-цифровой преобразователь, адаптивный корректор, решающий блок, декодер, выходной согласующий блок и блок управления. В данной системе в адаптивном корректоре для каждого цикла преобразования, состоящем из п точек. Каждый весовой коэффициент формируется только один раз и число адаптации для получения выходных данных уменьшается в п раз. Следовательно, значение постоянного коэффициента в рекурсивном алгоритме адаптивного корректора может быть соответственно увеличен вп раз, благодаря чему повышается помехозащищенность. 2 ил. (Л С

| Система передачи данных | 1986 |

|

SU1462507A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-04-23—Публикация

1989-08-07—Подача