Изобретение относится к микроэлектронике и может быть использовано при построении адресных формирователей ТТЛ-типа.

Известен адресный формирователь, представляющий собой два последовательно соединенных сложных инвертора на основе стандартных вентилей типа ТТЛ.

Недостатком такого адресного формирователя является большое время задержки до прямого выхода, так как необходимо, чтобы последовательно переключились два ТТЛ вентиля.

Этот недостаток устраняется при подключении входа второго инвертора к внутренней точке первого инвертора. Для этого используется дополнительный транзистор связи, база-эмиттерный переход которого подключен параллельно база-эмиттерному переходу фазорасщепительного транзистора, а коллектор подключен к входу второго инвертора. Недостаток известного адресного формирователя связан с возможным разбросом сопротивления контакта к эмиттеру. При этом возникает перехват тока в один из транзисторов, имеющий низкое сопротивление контакта к эмиттеру. Это приводит к тому, что транзистор, имеющий высокое сопротивление эмиттера, не входит в насыщение, напряжение на его коллекторе повышается и это может привести к нарушению работы адресного формирователя.

Целью изобретения является повышение надежности адресного формирователя.

Поставленная цель достигается тем, что в адресный формирователь, содержащий первый инвертор, состоящий из четырех транзисторов, двух резисторов и первого диода, анод которого соединен с эмиттером первого транзистора, база которого соединена с первым выводом первого резистора и коллектором второго транзистора, а коллектор соединен с вторым выводом первого резистора и подключен к шине питания первого инвертора, к шине нулевого потенциала которого подключен эмиттер третьего транзистора, коллектор которого соединен с катодом первого диода и является инверсным выходом формирователя, а база соединена с эмиттерами второго и четвертого транзисторов и с первым выводом второго резистора, второй вывод которого соединен с эмиттером третьего транзистора, база второго транзистора является входом формирователя и соединена с базой четвертого транзистора, второй инвертор, выход которого является прямым выходом формирователя, а вход соединен с коллектором четвертого транзистора первого инвертора, введены в первый инвертор третий резистор, второй и третий диоды, аноды которых соединены с первым выводом третьего резистора, второй вывод которого соединен с коллектором первого транзистора, база которого соединена с катодом второго диода, катод третьего диода соединен с входом второго инвертора.

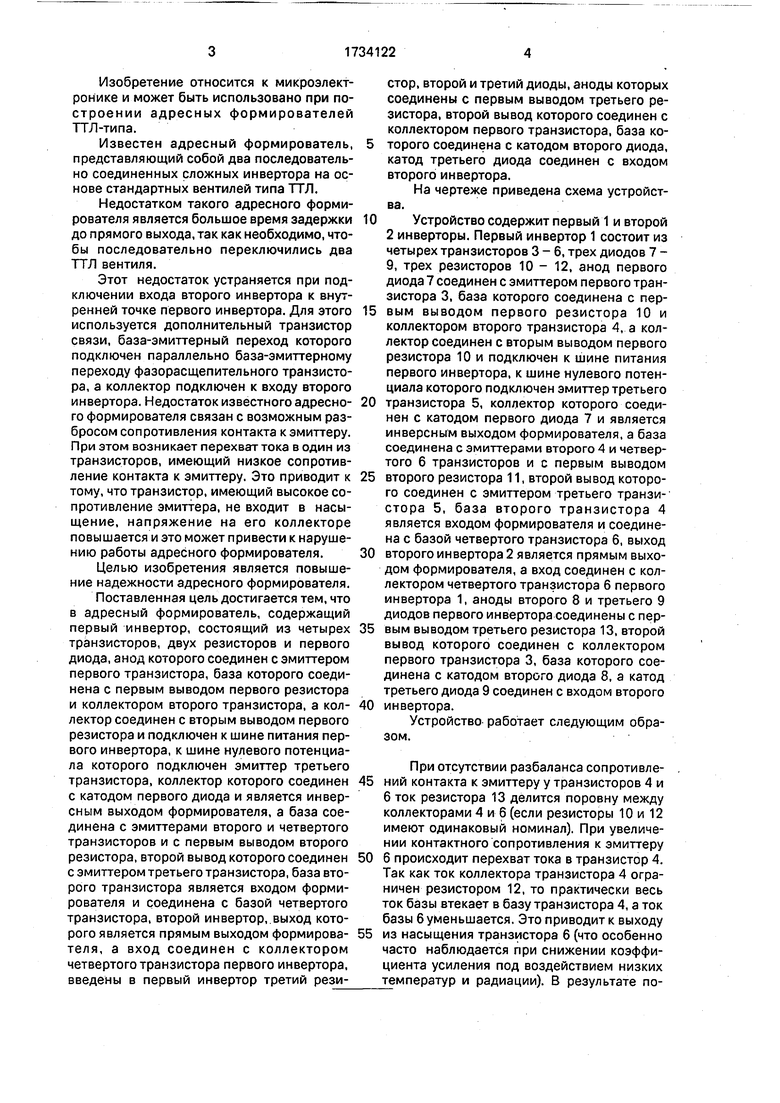

На чертеже приведена схема устройства.

Устройство содержит первый 1 и второй 2 инверторы. Первый инвертор 1 состоит из четырех транзисторов 3-6, трех диодов 7 - 9, трех резисторов 10 - 12, анод первого диода 7 соединен с эмиттером первого транзистора 3, база которого соединена с первым выводом первого резистора 10 и коллектором второго транзистора 4, а коллектор соединен с вторым выводом первого резистора 10 и подключен к шине питания первого инвертора, к шине нулевого потенциала которого подключен эмиттер третьего

транзистора 5, коллектор которого соединен с катодом первого диода 7 и является инверсным выходом формирователя, а база соединена с эмиттерами второго 4 и четвертого 6 транзисторов и с первым выводом

второго резистора 11, второй вывод которого соединен с эмиттером третьего транзистора 5, база второго транзистора 4 является входом формирователя и соединена с базой четвертого транзистора 6, выход

второго инвертора 2 является прямым выходом формирователя, а вход соединен с коллектором четвертого транзистора 6 первого инвертора 1, аноды второго 8 и третьего 9 диодов первого инвертора соединены с первым выводом третьего резистора 13, второй вывод которого соединен с коллектором первого транзистора 3, база которого соединена с катодом второго диода 8, а катод третьего диода 9 соединен с входом второго

инвертора.

Устройство работает следующим образом.

При отсутствии разбаланса сопротивле- ний контакта к эмиттеру у транзисторов 4 и 6 ток резистора 13 делится поровну между коллекторами 4 и 6 (если резисторы 10 и 12 имеют одинаковый номинал). При увеличении контактного сопротивления к эмиттеру 6 происходит перехват тока в транзистор 4. Так как ток коллектора транзистора 4 ограничен резистором 12, то практически весь ток базы втекает в базу транзистора 4, а ток базы 6 уменьшается. Это приводит к выходу из насыщения транзистора 6 (что особенно часто наблюдается при снижении коэффициента усиления под воздействием низких температур и радиации). В результате потенциал на коллекторе 6 увеличивается, диод 9 закрывается и весь ток резистора 13 начинает втекать в транзистор 4, что приводит к некоторому увеличению тока базы 6 при одновременном уменьшении тока коллектора 6. Таким образом, транзистор 6 снова стремится войти в насыщение. Резисторы 10 и 12 необходимо выбрать как можно большего номинала (их номинал определяется необходимым уровнем лог. 1 на выходе адресного формирователя для конкретной схемотехнической реализации дешифратора), а резистор 13 необходимо выбрать как можно меньшего номинала (он ограничивается требованиями по току потребления и степени насыщения выходных транзисторов).

Таким образом, введение диодов 8 и 9, катоды которых подключены к коллекторам транзисторов 4 и 6, а аноды которых соединены с резистором 13, второй конец которого соединен с источником питания, позволяет увеличить надежность и выход годных в процессе производства за счет предотвращения выхода из насыщения транзисторов 4 и 6 при наличии разбаланса сопротивлений в эмиттере одного из этих транзисторов.

Формула изобретения Адресный формирователь, содержащий два инвертора, первый из которых состоит

из четырех транзисторов, двух резисторов и первого диода, анод которого соединен с эмиттером первого транзистора, база которого соединена с первым выводом первого резистора и коллектором второго транзистора, а коллектор соединен с вторым выводом первого резистора и подключен к шине питания, эмиттер третьего транзистора подключен к шине нулевого потенциала, а коллектор соединен с катодом первого диода и является инверсным выходом адресного формирователя, база третьего транзистора соединена с эмиттерами второго и четвертого транзисторов и с первым выводом второго резистора, второй вывод которого соединен с эмиттером третьего транзистора, база второго транзистора является входом адресного формирователя и соединена с базой четвертого транзистора, выход второго инвертора является прямым выходом адресного формирователя, а вход соединен с коллектором четвертого транзистора первого инвертора, отличающийся тем. что, с целью повышения надежности, первый инвертор содержит третий резистор, второй и третий диоды, аноды которых соединены с первым выводом третьего резистора, второй вывод которого соединен с коллектором первого транзистора, база которого соединена с катодом второго диода, катод третьего диода соединен с входом второго инвертора.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫХОДНАЯ СХЕМА С ТРЕМЯ СОСТОЯНИЯМИ | 1992 |

|

RU2072629C1 |

| Усилитель-инвертор | 1987 |

|

SU1429310A1 |

| ПЕРЕДАТЧИК МУЛЬТИПЛЕКСНОЙ МАНЧЕСТЕРСКОЙ ЛИНИИ СВЯЗИ | 2002 |

|

RU2229769C2 |

| ТТЛ-вентиль | 1985 |

|

SU1324105A1 |

| ТРАНЗИСТОРНЫЙ КЛЮЧ | 2005 |

|

RU2287219C1 |

| Устройство для управления преобразователем постоянного напряжения в постоянное | 1986 |

|

SU1394362A1 |

| Элемент транзисторно-транзисторной ложки (его варианты) | 1985 |

|

SU1274149A1 |

| ТТЛ-инвертор | 1984 |

|

SU1269252A1 |

| ТТЛ-вентиль | 1985 |

|

SU1324104A1 |

| Устройство управления записью-считыванием информации для полупроводникового запоминающего устройства | 1986 |

|

SU1367040A1 |

Изобретение относится к микроэлектронике и может быть использовано при построении адресных формирователей ТТЛ- типа. Целью изобретения является повышение надежности адресного формирователя. Поставленная цель достигается тем, что формирователь содержит третий резистор 13, второй диод 8, третий диод 9 с соответствующими связями. При наличии разбаланса контактных сопротивлений транзистор, имеющий завышенное сопротивление эмиттера, удерживается в насыщении за счет уменьшения его тока коллектора. Это обеспечивается за счет перераспределения тока, протекающего через третий резистор 13. В результате функционирование формирователя не нарушается. 1 ил. ч Ё СО ю N

| Валиев К.А., Орликовский А.А | |||

| Полупроводниковые интегральные схемы памяти на биполярных транзисторных структурах | |||

| - М.: Сов.радио, 1979, с | |||

| Прибор для измерения угла наклона | 1921 |

|

SU253A1 |

| Патент США N° 3962589, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

Авторы

Даты

1992-05-15—Публикация

1990-03-16—Подача