Изобретение относится к импульсной технике и может быть использовано при построении выходных каскадов различных цифровых ИС,

Целью изобретения является повышение быстродействия путем снижения межкаскадных задержек распространения сигнал 1.

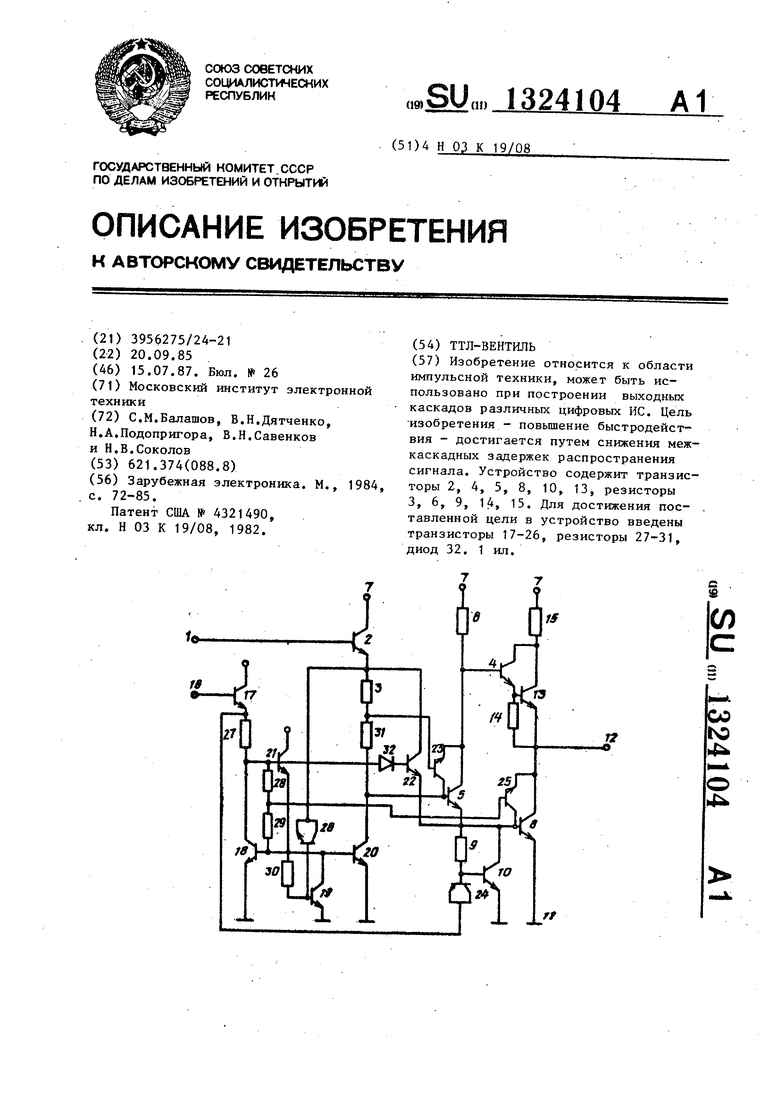

На чертеже представлена принципиальная электрическая схема ТТЛ-вентиля.

ТТЛ-вентипь содержит первую входную шину 1, первьй транзистор 2,эмиттер которого соединен с первым выводом Первого резистора 3, база второго f5 тером пятнадцатого транзистора 25,

транзистора 4 соединена коллектором третьего транзистора 5 и через второй резистор 6 с шиной 7 питания, эмиттер третьего транзистора 5 соединен с базой четвертого транзистора 8 и через третий резистор 9 с базой пятого транзистора 10, эмиттер которого соединен с общей шиной 11 и эмиттером четвертого транзистора 8, коллектор которого соединен с выходной шиной 12, эмиттером шестого транзистора 13 и первым выводом четвертого резистора 14, второй вывод которого соединен с базой шестого транзистора 13 и

эмиттером второго транзистора 4, кол- 30 зисторов соединены с шиной 7 питания,

эмиттеры восьмого - десятого транзисторов 18-20 соединены с общей шиной 11.

Устройство работает следующим об35 разом.

Б состоянии 1 на шине 1 (О на шине 16) выходной 8 и фазорасщепи- тельньш 5 транзисторы открыты, но не входят в насыщение за счет фиксации

40 потенциалов их коллекторов транзисторами 25 и 23.

Выходной 8 и фазорасщепительный 5 транзисторы находятся в режиме, близком к нормальному активному - с

мальми токами базы, которые много меньше токов, задаваемых на их входы и протекающих через шунтирующие элементы из их базовой цепи в коллекторную. В первом элементе ускорения

50 -транзистор 21 открыт, находится в нормальном активном режиме и потребляет некоторьй 1инимальный ток, много меньший тока эмиттера фазорасщепи- тельного транзистора. Это достигается

55 соответствующим выбором номинала резистора 23 и минимизацией площади транзистора 21. В аналогичном режиме работает и транзистор 27 третьего

лекторы которых соединены через пятый резистор 15 с шиной 7 питания, . вторую входную шину 16, седьмой - шестнадцатый транзисторы 17-26, шестой десятый резисторы 27-31, диод 32, первая входная шина 1 соединена, с базой первого транзистора 2, вторая входная шина 16 соединена с базой седьмого транзистора 17, эмиттер которого через шестой резистор 27 соединен с коллектором восьмого транзистора 18, база которого через де- вятьй резистор 30 соединена с базой девятого транзистора 19, коллектор которого соединен с базами восьмого 18 и десятого 20 транзисторов и с эмиттером одиннадцатого транзистора 21, база которого соединена с коллектором восьмого транзистора 18, эмиттер двенадцатого транзистора соединен с эмиттером третьего транзистора 5, база KOTopopq соединена с коллектором тринадцатого транзистора 23, коллектором- десятого транзистора 20 и через последовательно соединенные десятый 31 и первЬй 3 резисторы с эмиттером первого транзистора 2 и с коллектором двенадцатого транзистора 22, общая точка соединения первого 3 и десятого 31 резисторов соединена с базой тринадцатого транзистора 23, эмиттер которого соединен с коллектором третьего транзистора 5,

эмиттер которого соединен с коллектором пятого транзистора 10, эмиттер седьмого транзистора 17 соединен с эмиттером и коллектором четырнадца-

того транзистора 24, база которого через третий резистор 9 соединена с коллектором пятнадцатого транзистора 25 и базой четвертого транзистора 8, коллектор которого соединен с эмитбаза которого соединена с первыми выводами седьмого 28 и восьмого 29 резисторов, вторые выводы которых соединены соответственно с коллектором восьмого транзистора 18, анодом диода 32 и базой восьмого транзисто-. ра 18, катод диода 32 соединен с базой двенадцатого транзистора 22, база девятого транзистора 19 соедине-

на с базой шестнадцатого транзистора 26, эмиттер и коллектор которого соединены с эмиттером первого транзистора 2, коллекторы первого 2, седьмого 17 и одиннадцатого 21 тран

элемента ускорения. Во входном каскаде вход токового зеркала подключен к инверсному входу 20. В соответствии с уровнем О на данном входе в рассматриваемом состоянии в токовом зер- капе тбк имеет минимальное значение (больше нуля, поскольку токовое зеркало полностью не выключается), минимальная часть тока ответвляется в выходной транзистор 15 токового зеркала, больЬая часть тока поступает в базу фазорасщепительного транзистора 5.

В состоянии о на шине 1 (1 на шине 16) фазорасщепительный 5 и выходной 8 транзисторы заперты. Высокий потенциал коллектора запертого фазорасщепительного транзистора 5 задает через выходной эмиттерный повторитель выходной уровень 1.

Выходной, ток токового зеркала увеличивает при этом логический перепад на базе фазорасщепительного транзистора 5 за счет падения напряжения на резисторе 31,

В динамическом режиме при переключении из состояния 1 в О на шине

1 (соответственно из О в 1 на шиТаким образом, предлагаемое устройство имеет более высокое, быстро-, действие по сравнению с прототипом при одинаковой потребляемой мощности благодаря повышению эффективности цепочек ускорения за счет их более раннего запуска от входного каскада. Использование в цепочках ускорения 20 разисторов вместо фиксирующих диодов изменяет режим работы ускоряющих транзисторов - задает минимальный v статический ток потребления и увеличивает быстродействие цепочки ускоре- .ния. Входной каскад на токовом зеркале, формирующий сигналы запуска цепочек ускорения, позволяет также реализовать опорные смещения для элементов ограничения насыщения. Это делает

не 16) запираются фазорасщепительный 5 и выходной 8 транзисторы. Для уско-30 перспективным использование ТТЛ-вен- рения их выключения при управлении тиля в качестве выходного каскада, по базе требуется увеличение токов, для которого главным требованием яв- . вытекающих из их баз. Для выключения ляется эффективное переключение зна- фазорасщепительного транзистора 5 такой ток обеспечивается за счёт 35 включения токового зеркала входного каскада. Отрицательный фронт импульса, передаваемый через емкостный элемент на транзисторе 26 на базу транзистора 19, создает дпя него запирающий 40 импульс. Соответственно, импульсно увеличивается ток, втекающий в базу выходного транзистора 20 токового зеркйла из эмиттера транзистора 21. Положительный фронт, передаваемый 45 эмиттерным повторителем на транзисторе 17 через емкостной элемент 24 на базу транзистора 10, .формирует в нем импульс тока, вытекающего из базы выходного, транзистора 30 и втекающе- 50 транзистора, коллектор которого сое- го в коллектор транзистора 19. динен с выходной шиной, эмиттером При переключении из состояния О

чительной внешней нагрузки. Формула изобретения

ТТЛ-вентиль содержит первую входную шину, первый транзистор, эмиттер которого соединен с первым выводом первого резистора, база второго транзистора соединена с коллектором третьего транзистора и через второй резистор с шиной питания, эмиттер третьего транзистора соединен с базой четвертого транзистора и через третий резистор с базой пятого транзистора, эмиттер которого соединен с общей шиной и эмиттером четвертого

шестого транзистора и первым вьшодом четвертого резистора, второй вьшод которого соединен с базой шестого

в 1 на шине 1 (из 1 в О на шине

шестого транзистора и первым вьшодом четвертого резистора, второй вьшод которого соединен с базой шестого

16) фазорасщепительный 5 и выходной

8 транзисторы включаются. Для ускоре-55транзистора и эмиттером второго

кия их включения требуется увеличе-транзистора, коллекторы которых соение тока, втекакяцего в их базы. Длядинены через резистор с шиной питафазорасщепительного транзистора 5ния, отличающийся тем.

увеличение втекающего тока обеспечивается за счет выключения токового зеркала входного каскада. Для выходного транзистора 8 втекающий ток увеличивается за счет импульсного включения транзистора 22. При положительном фронте запускающего импульса на коллекторе транзистора 22 ток через его емкость коллектор - база почти полностью втекает в его ба.зу и усиливается им.

Таким образом, предлагаемое устройство имеет более высокое, быстро-, действие по сравнению с прототипом при одинаковой потребляемой мощности благодаря повышению эффективности цепочек ускорения за счет их более раннего запуска от входного каскада. Использование в цепочках ускорения разисторов вместо фиксирующих диодов изменяет режим работы ускоряющих транзисторов - задает минимальный v статический ток потребления и увеличивает быстродействие цепочки ускоре- ния. Входной каскад на токовом зеркале, формирующий сигналы запуска цепочек ускорения, позволяет также реализовать опорные смещения для элементов ограничения насыщения. Это делает

перспективным использование ТТЛ-вен- тиля в качестве выходного каскада, для которого главным требованием яв- ляется эффективное переключение зна- транзистора, коллектор которого сое- динен с выходной шиной, эмиттером

перспективным использование ТТЛ-вен- тиля в качестве выходного каскада, для которого главным требованием яв- ляется эффективное переключение зна- транзистора, коллектор которого сое- динен с выходной шиной, эмиттером

чительной внешней нагрузки. Формула изобретения

ТТЛ-вентиль содержит первую входную шину, первый транзистор, эмиттер которого соединен с первым выводом первого резистора, база второго транзистора соединена с коллектором третьего транзистора и через второй резистор с шиной питания, эмиттер третьего транзистора соединен с базой четвертого транзистора и через третий резистор с базой пятого транзистора, эмиттер которого соединен с общей шиной и эмиттером четвертого

перспективным использование ТТЛ-вен- тиля в качестве выходного каскада, для которого главным требованием яв- ляется эффективное переключение зна- транзистора, коллектор которого сое- динен с выходной шиной, эмиттером

шестого транзистора и первым вьшодом четвертого резистора, второй вьшод которого соединен с базой шестого

что, с целью повьшения (Зыстродейст- вйя, в него введены вторая входная шина, седьмой, восьмой, девятый, десятый, одиннадцатый, двенадцатый, тринадцатый, четырнадцатый, пятнад- цатУй и шестнадцатый транзисторы, шестой, седьмой, восьмой, девятый и десятый резисторы, диод, первая входная шина соединена с базой первго транзистора, вторая входная шина соединена с базой седьмого транзистора, эмиттер которого через шестой реэистор соединен с кол/1ектором восмого транзистора, база которого че- рс.з девятый резистор соединена с ба ЗОЙ девятого транзистора, коллектор которого соединен с базами восьмог и десятого транзисторов и с эмиттером одиннадцатого транзистора, база KOTopfjro соединена с коллектором восьмого транзистора, эмиттер двенадцатого транзистора соединен с эмиттером третьего транзистора, баз которого соединена с коллектором тринадцатого транзистора, коллектор десятого транзистора и через последовательно соединенные десятый и певый резисторы с эмиттером первого транзистора и с коллектором двенадц

того транзистора, общая точка соеди

Редактор Л.Веселовская Заказ 2972/56

Составитель А.Кабанов

Техред Л.Олийнык Корректор М.Демчик

Тираж 901Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

нения первого и десятого резисторов соединена.с базой тринадцатого транзистора, эмиттер которого соединен с коллектором третьего транзистора, эмиттер которого соединен с коллектором пятого транзистора, эмиттер седьмого транзистора соединен с эмиттером и коллектором четырнадцатого транзистора, база которого через третий резистор соединена с коллектором пятнадцатого транзистора и базой четвертого транзистора, коллектор которого соединен с эмиттером пятнадцатого транзистора, база которого соединена с первыми выводами седьмого и восьмого резисторов, вторые вьшоды которых соединены соответственно с коллектором восьмого транзистора, анодом диода и базой восьмого транзистора, катод диода соединен с базой двенадцатого транзистора, база девятого транзистора соединена с базой шестнадцатого транзистора, эмиттер и коллектор которого соединены с эмиттером первого транзистора, коллекторы первого, седьмого и одиннадцатого транзисторов соединены с шиной питания, эмиттеры восьмого, девятого и десятого транзисторов

| название | год | авторы | номер документа |

|---|---|---|---|

| ТТЛ-инвертор | 1984 |

|

SU1269252A1 |

| ТТЛ-вентиль | 1985 |

|

SU1324103A1 |

| ТТЛ-вентиль | 1985 |

|

SU1324105A1 |

| Транзисторный ключ | 1985 |

|

SU1283957A1 |

| Инверторная схема с минимальной асимметрией | 1985 |

|

SU1311016A1 |

| Формирователь импульсов управления | 1985 |

|

SU1290501A1 |

| Одноразрядный сумматор | 1988 |

|

SU1599854A1 |

| Устройство для формирования импульсов | 1990 |

|

SU1775850A1 |

| Усилитель-инвертор | 1987 |

|

SU1429310A1 |

| Входное устройство схемы сравнения токов | 1988 |

|

SU1554128A1 |

Изобретение относится к области импульсной техники, может быть использовано при построении выходных каскадов различных цифровых НС. Цель изобретения - повышение быстродействия - достигается путем снижения межкаскадных задержек распространения сигнала. Устройство содержит транзисторы 2, 4, 5, 8, 10, 13, резисторы 3, 6, 9, 14, 15. Для достижения поставленной цели в устройство введены транзисторы 17-26, резисторы 27-31, диод 32. 1 ил. СЛ С со ю //

| Зарубежная электроника | |||

| М., 1984, с | |||

| Термосно-паровая кухня | 1921 |

|

SU72A1 |

| Патент США № 4321490, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-07-15—Публикация

1985-09-20—Подача