Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления.

Цель изобретения упрощение устройства путем исключения одного элемента памяти на магнитном сердечнике, а также двух диодов и одного конденсатора за счет реализации в устройстве схемными мерами условий для формирования с помощью конденсатора кратковременной электрической несимметричности, исключающей возможность переключения триггерной ячейки импульсами, формируемыми на входе и выходе обмотки считывания элемента памяти при восстановлении состояния сердечника.

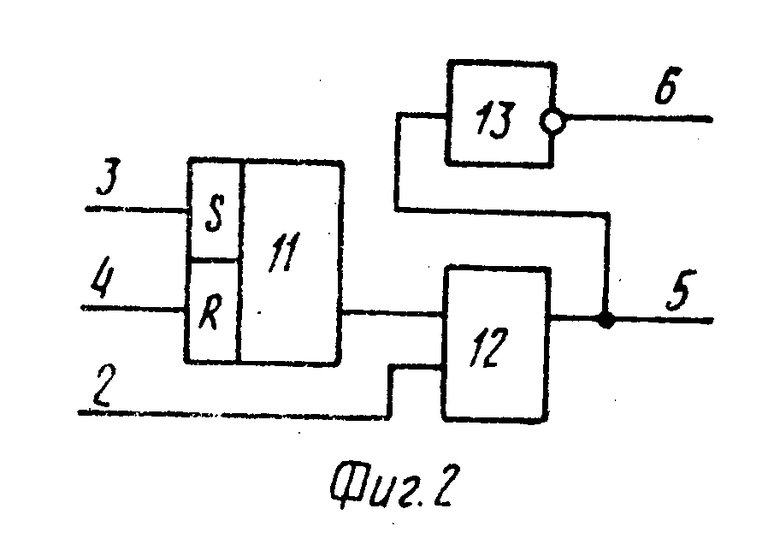

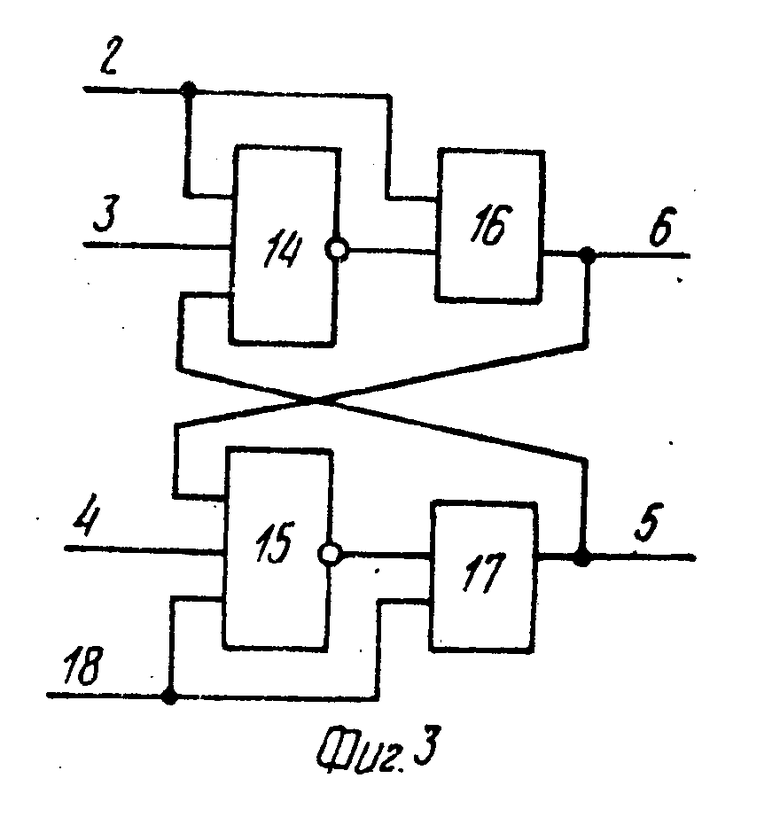

На фиг. 1 приведена схема триггерного устройства; на фиг. 2 схема триггерной ячейки, обеспечивающей работу устройства в счетном режиме; на фиг. 3 схема триггерной ячейки, обеспечивающей работу устройства в режиме с установочными входами.

Триггерное устройство содержит триггерную ячейку 1, имеющую один управляющий вход 2, входы установки 3 и сброса 4 с прямым 5 и инверсным 6 выходами, элемент 7 памяти на магнитном сердечнике с ППГ и обмотками записи и считывания, конденсатор 8, первый 9 и второй 10 резисторы. Входы установки 3 и сброса 4 триггерной ячейки 1 соединены с одним из выводов соответственно первого 9 и второго 10 резисторов. Вход обмотки записи элемента 7 памяти соединен с прямым выходом 5 триггерной ячейки 1, вход 4 сброса которой соединен с одним из выводов конденсатора 8. Вход и выход обмотки считывания элемента 7 памяти соединены с другими выводами соответственно второго 10 и первого 9 резисторов, а ее средняя точка с общей шиной. Выход обмотки записи элемента 7 памяти соединен с инверсным выходом 6 триггерной ячейки 1, вход 3 установки которой подключен к другому выводу конденсатора 8.

Триггерная ячейка 1 (см. фиг. 2) содержит RS-триггер 11, S- и R-входы которого соединены соответственно с входами установки 3 и сброса 4 триггерной ячейки 1 и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 12, первый и второй входы которого соединены соответственно с прямым выходом RS-триггера 11 и управляющим входом 2 триггерной ячейки 1, а выход соединен с прямым выходом 5 триггерной ячейки 1 и через инвертор 13 с ее инверсным выходом 6. Управляющий вход 2 триггерной ячейки 1 является счетным входом устройства.

Триггерная ячейка 1 (см. фиг. 3) содержит первый 14 и второй 15 элементы ИЛИ-НЕ, первые входы которых соединены соответственно с входами установки 3 и сброса 4 триггерной ячейки 1. Второй вход элемента ИЛИ-НЕ 14 соединен с первым управляющим входом 2 триггерной ячейки 1. Вторые входы первого 14 и второго 15 элементов ИЛИ-НЕ соединены с первыми входами соответственно первого 16 и второго 17 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входы которых соединены с выходами соответственно первого 14 и второго 15 элементов ИЛИ-НЕ, а выходы соединены с третьими входами соответственно второго 15 и первого 14 элементов ИЛИ-НЕ и соответственно с инверсным 6 и прямым 5 выходами триггерной ячейки 1. Второй вход элемента ИЛИ-НЕ 15 соединен со вторым управляющим входом 18 триггерной ячейки 1. Первый 2 и второй 18 управляющие входы триггерной ячейки 1 являются соответственно входами сброса и установки устройства.

Триггерное устройство работает следующим образом.

В исходном состоянии RS-триггер 11 триггерной ячейки 1 находится в состоянии логического "0", на входе 2 присутствует уровень логического "0". Поэтому на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12 и на прямом выходе 5 триггерной ячейки 1 присутствует уровень логического "0", а на выходе инвертора 13 и на инверсном выходе 6 триггерной ячейки 1 уровень логической "1". Через обмотку записи элемента 7 памяти протекает ток в направлении от инверсного выхода 6 к прямому выходу 5 триггерной ячейки 1. Перемагничивание сердечника элемента 7 памяти закончилось, импульсы на обмотке считывания отсутствуют, входы установки 3 и сброса 4 триггерной ячейки 1 привязаны к общей шине через соответственно первый 9 и второй 10 резисторы. Конденсатор 8 разряжен. Сердечник элемента 7 памяти находится в состоянии логического "0".

Если RS-триггер 11 изменит свое состояние под действием внешних помех, то изменятся уровни напряжения на выходах 5 и 6 триггерной ячейки 1. Через обмотку записи элемента 7 памяти потечет ток в направлении с выхода 5 на выход 6. Сердечник элемента 7 памяти начнет перемагничиваться. На входе обмотки считывания элемента 7 памяти сформируется импульс положительной полярности, а на выходе обмотки считывания импульс отрицательной полярности. Конденсатор 8 начнет заряжаться через резисторы 9 и 10. Уровень напряжения на входе 3 установки триггерной ячейки 1 начнет понижаться, стремясь к амплитуде импульса на выходе обмотки считывания элемента 7 памяти. Однако отрицательный уровень напряжения на входе 3 установки триггерной ячейки 1 будет ограничен диодом входной защитной цепи RS-триггера 11 по S-входу, катод которого подключен к S-входу, а анод к общей шине.

Уровень напряжения на входе 4 сброса триггерной ячейки 1 повышается по мере заряда конденсатора 8. При достижении напряжением на входе 4 сброса уровня порога срабатывания RS-триггера 11 по R-входу RS-триггер 11 возвращается в исходное состояние. Уровни напряжения на выходах 5, 6 триггерной ячейки 1 изменяются на противоположные. Через обмотку записи элемента 7 памяти начинает протекать ток в направлении от выхода 6 к выходу 5 триггерной ячейки 1, восстанавливая состояние сердечника элемента 7 памяти. При этом на входе обмотки считывания формируется импульс отрицательной полярности, а на ее выходе импульс положительной полярности. При этом уровни напряжения на входах установки 3 и сброса 4 триггерной ячейки 1 в начальный момент не изменятся. Затем за счет перезаряда конденсатора 8 напряжение на входе 4 сброса начнет уменьшаться. К моменту восстановления состояния сердечника элемента 7 памяти напряжение на конденсаторе 8 упадет практически до нуля. После восстановления состояния сердечника импульсы на входе и выходе обмотки считывания заканчиваются. Устройство приходит в исходное состояние. Аналогичным образом обеспечивается восстановление состояния логической "1" после переключения RS-триггера 11 под действием помех в состояние логического "0".

Если на вход 2 триггерного устройства, находящегося в исходном состоянии, поступит уровень логической "1", то изменятся уровни напряжения на выходах 5 и 6 триггерной ячейки 1. Через обмотку записи элемента 7 памяти протекает ток в направлении от выхода 5 к выходу 6, перемагничивая сердечник в состояние логической "1". При этом на входе обмотки считывания элемента 7 памяти формируется импульс положительной полярности, а на ее выходе импульс отрицательной полярности. Конденсатор 8 заряжается до амплитуды импульса положительной полярности, при этом на входе 4 сброса триггерной ячейки 1 присутствует высокий уровень напряжения, подтверждающий исходное состояние RS-триггера 11.

После перемагничивания сердечника элемента 7 памяти в состояние логической "1" импульсы на обмотке считывания заканчиваются. Конденсатор 8 разряжается через обмотку считывания и резисторы 9 и 10. После разряда конденсатора 8 на входе 2 восстанавливается уровень логического "0". При этом изменяются уровни напряжения на выходах 5 и 6 триггерной ячейки 1. Ток в обмотке записи элемента 7 памяти изменяет направление. При этом сердечник элемента 7 памяти начинает перемагничиваться, формируя импульс положительной полярности на выходе обмотки считывания и импульс отрицательной полярности на ее входе. Конденсатор 8 заряжается через резисторы 9 и 10 до порога срабатывания RS-триггера 11 по S-входу. После переключения RS-триггера 11 в состояние логической "1" начинается восстановление состояния сердечника элемента 7 памяти и конденсатора 8. После восстановления состояния указанных элементов процесс переключения триггерного устройства в состояние логической "1" заканчивается.

Переключение триггерного устройства в состояние логического "0" происходит аналогичным образом.

Триггерное устройство работает следующим образом.

В исходном состоянии на входах установки 18 и сброса 2 устройства присутствует уровень логического "0". Сердечник элемента 7 памяти находится в состоянии логического "0". Уровень логического "0" с выхода и входа обмотки считывания элемента 7 памяти через резисторы 9 и 10 поступает на входы соответственно установки 3 и сброса 4 триггерной ячейки 1, а следовательно, и на первые входы элементов ИЛИ-НЕ 14 и 15 соответственно. Конденсатор 8 разряжен. На выходах элемента ИЛИ-НЕ 14 и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 16, а следовательно, и на третьем входе элемента ИЛИ-НЕ 15 присутствует уровень логической "1". На выходах элемента ИЛИ-НЕ 15, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 17, а следовательно, и на третьем входе элемента ИЛИ-НЕ 14 присутствует уровень логического "0". На прямом выходе 5 триггерной ячейки 1 присутствует уровень логического "0", а на инверсном выходе 6 уровень логической "1". Через обмотку записи элемента 7 памяти протекает ток в направлении от выхода 6 к выходу 5 триггерной ячейки 1, подтверждая нулевое состояние сердечника элемента памяти 7.

При поступлении импульса положительной полярности на вход 18 установки элемент ИЛИ-НЕ 15 остается в состоянии логического "0", элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 17 устанавливается в состояние логической "1", элемент ИЛИ-НЕ 14 и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 16 в состояние логического "0". При этом на прямом выходе 5 триггерной ячейки 1 устанавливается уровень логической "1", а на инверсном выходе 6 уровень логического "0". Через обмотку записи элемента 7 памяти начинает протекать ток в направлении от выхода 5 к выходу 6 триггерной ячейки 1, перемагничивая сердечник элемента 7 памяти в состояние логической "1". На входе обмотки считывания формируется импульс положительной полярности, а на выходе обмотки считывания импульс отрицательной полярности. После заряда конденсатора 8 через резисторы 9 и 10 на входе 4 сброса триггерной ячейки 1 формируется высокий уровень напряжения, который не влияет на состояние триггерной ячейки 1.

После перемагничивания сердечника элемента 7 памяти в состояние логической "1" импульсы на входе и выходе обмотки считывания заканчиваются. Конденсатор 8 разряжается через обмотки считывания и резисторы 9 и 10. После разряда конденсатора 8 импульс на входе 18 установки заканчивается, элемент ИЛИ-НЕ 15 переходит в состояние логической "1", элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 17 остается в состоянии логической "1". На этом процесс переключения триггерного устройства в состояние логической "1" заканчивается.

Переключение триггерного устройства в состояние логического "0" при поступлении импульса положительной полярности на вход 2 сброса происходит аналогичным образом.

Таким образом, предлагаемое триггерное устройство нормально функционирует, как в счетном режиме при использовании триггерной ячейки, представленной на фиг. 2, так и в режиме с установочными входами при использовании триггерной ячейки, представленной на фиг. 3. При этом достигнуто упрощение триггерного устройства путем исключения одного элемента памяти на магнитном сердечнике, двух диодов и одного конденсатора. По числу дискретных элементов без учета триггерной ячейки устройство упрощено в два раза. Указанное упрощение достигнуто за счет формирования в устройстве с помощью конденсатора кратковременной несимметричности, исключающей возможность переключения триггерной ячейки импульсами элемента памяти, формируемыми при восстановлении состояния сердечника. При этом используется нелинейность входного сопротивления интегральных микросхем, связанная с наличием диода, катодом подключенного к входу микросхемы, а анодом к общей шине.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2001 |

|

RU2207716C2 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1990 |

|

SU1780487A1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1990 |

|

SU1753919A1 |

| Триггерное устройство (его варианты) | 1981 |

|

SU970650A1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2250556C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2250554C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2002 |

|

RU2248662C2 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2248664C1 |

| Триггерное устройство | 1979 |

|

SU813709A1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2237967C1 |

Изобретение относится к импульсной технике и позволяет упростить устройство. Триггерное устройство содержит триггерную ячейку 1, имеющую по крайней мере один управляющий вход 2, входы установки 3 и сброса 4 которой соединены с одними из выходов соответственно первого 9 и второго 10 резисторов, и элемент памяти 7 на магнитном сердечнике с ППГ и обмотками записи и считывания. Вход обмотки записи соединен с прямым выходом 5 триггерной ячейки 1, вход 4 сброса которой соединен с одним из выводов конденсаторов 8. Вход и выход обмотки считывания соединен с другими выводами соответственно второго 10 и первого 9 резисторов, а ее средняя точка - с общей шиной. Выход обмотки записи соединен с инверсным выходом 6 триггерной ячейки 1, вход 3 установки которой подключен к другому выводу конденсатора 8. 1 з.п. ф-лы, 3 ил.

| Триггерное устройство | 1979 |

|

SU813709A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Триггерное устройство (его варианты) | 1981 |

|

SU970650A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1997-09-10—Публикация

1990-04-02—Подача