Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления.

Известно триггерное устройство [см. авт. св. СССР N 970650 от 03.04.81, кл. H 03 K 3/286, Триггерное устройство (второй вариант), Г.И.Шишкин, опублик. 30.10.82 в БИ N 40], содержащее RS-триггер, элемент "исключающее ИЛИ", первый и второй элементы памяти на магнитных сердечниках, первый и второй диоды, первый и второй конденсаторы, первый и второй резисторы. Входы обмоток считывания первого и второго элементов памяти на магнитных сердечниках соединены с первой шиной питания, а выходы обмоток считывания через соответственно первый и второй диоды, включенные в прямом направлении относительно источника питания, соединены соответственно с входами установки и сброса триггера, которые соединены с первой шиной питания через соответственно первый и второй конденсаторы и с второй шиной питания через соответственно первый и второй резисторы. Выходы обмоток записи первого и второго элементов памяти на магнитных сердечниках соединены между собой. Вход обмотки записи первого элемента памяти на магнитном сердечнике соединен с прямым выходом элемента "исключающее ИЛИ", первый вход которого соединен с входом устройства, а второй вход соединен с прямым выходом триггера. Инверсный выход элемента "исключающее ИЛИ" соединен с входом обмотки записи второго элемента памяти на магнитном сердечнике.

Недостатками данного устройства являются его сложность, связанная с необходимостью использования двух элементов памяти на магнитных сердечниках, обладающих большими габаритами, и большое потребление мощности, связанное с протеканием большого тока через обмотку записи элементов памяти на магнитных сердечниках вследствие малого количества ее витков, поскольку большая часть суммарного количества витков использована в обмотке считывания, и с необходимостью формирования на обмотке считывания сигнала, амплитуда которого должна быть достаточно близка к напряжению питания.

Наиболее близкой к заявляемой по технической сущности является энергонезависимая ячейка памяти (см. авт. св. СССР N 845287 от 02.07.79, кл. H 03 K 19/16, Энергонезависимая ячейка памяти, Н.М.Лукманов, опублик. 07.07.81 в БИ N 25), содержащая сердечник с прямоугольной петлей гистерезиса (ППГ) и обмоткой, триггер, логические элементы И-НЕ и резистор. Средняя точка обмотки сердечника подключена через резистор к источнику питания. Конец обмотки подключен к выходу первого элемента И-НЕ, начало - к выходу второго элемента И-НЕ и к одному из входов третьего элемента И-НЕ, второй вход которого подключен к шине разрешения, а выход - к единичному входу (S-входу) триггера, нулевой вход (R-вход) которого подключен к шине сброса, счетный вход - к информационной шине, а прямой и инверсный выходы - к входам первого и второго элементов И-НЕ соответственно, вторые входы которых подключены к шине перемагничивания.

Недостатками данной ячейки памяти являются большое потребление мощности, связанное с необходимостью пропускания через обмотку сердечника большого тока, поскольку перемагничивание сердечника производится током, протекающим только через половину витков обмотки, а напряжение на обмотке должно быть равным уровню логической "1", т.е. достаточно близким к напряжению питания, и низкая помехоустойчивость, связанная с тем, что входные информационные сигналы поступают на счетный вход триггера, обладающего малой инерционностью.

Цель изобретения - уменьшение потребляемой мощности и повышение помехоустойчивости.

Поставленная цель достигается тем, что в энергонезависимую ячейку памяти, содержащую сердечник с прямоугольной петлей гисторезиса и обмоткой, конец которой подключен к выходу первого логического элемента, который выполнен в виде элемента И-НЕ, один из входов которого соединен с шиной перемагничивания, триггер, R-вход которого подключен к шине сброса, инверсный выход - к одному из входов второго логического элемента, резистор, один вывод которого подключен к шине питания, и информационную шину, введены дополнительный резистор, транзистор и диод, второй логический элемент выполнен в виде элемента "исключающее ИЛИ", а триггер - в виде асинхронного RS-триггера на элементах И-НЕ, при этом другой вход второго логического элемента соединен с информационной шиной, выход - с другим входом элемента И-НЕ и через дополнительный резистор - с началом обмотки сердечника, катодом диода и базой транзистора, коллектор которого соединен с другим выводом резистора и S-входом триггера, эмиттер - с анодом диода и концом обмотки сердечника.

Указанная совокупность признаков позволяет уменьшить потребляемую мощность за счет уменьшения величины тока в обмотке путем использования для перемагничивания сердечника всего количества витков обмотки при напряжении на обмотке, равном падению напряжения на диоде, и повысить помехоустойчивость путем использования инерционности сердечника для селекции информационных (счетных) импульсов по длительности.

Известно техническое решение [см. авт. св. СССР N 970650 от 03.04.81, кл. H 03 K 3/286, Триггерное устройство (первый вариант), Г.И.Шишкин, опублик. 30.10.82 в БИ N 40], в котором обнаружены следующие отличительные от прототипа существенные признаки: триггер выполнен в виде асинхронного RS-триггера, (второй) логический элемент выполнен в виде элемента "исключающее ИЛИ", при этом другой вход (второго) логического элемента соединен с информационной шиной. Свойства заявляемого и известного решений, обусловленные наличием этих признаков совпадают: обеспечивается счетный режим работы устройства путем перемагничивания сердечника при поступлении счетного импульса в состояние, противоположное состоянию триггера, что позволяет совместно с другими признаками использовать инерционность сердечника для повышения помехоустойчивости устройства.

Не обнаружены известные технические решения, содержащие остальные отличительные от прототипа существенные признаки. Это позволяет сделать вывод о соответствии заявляемого технического решения критерию "существенные отличия".

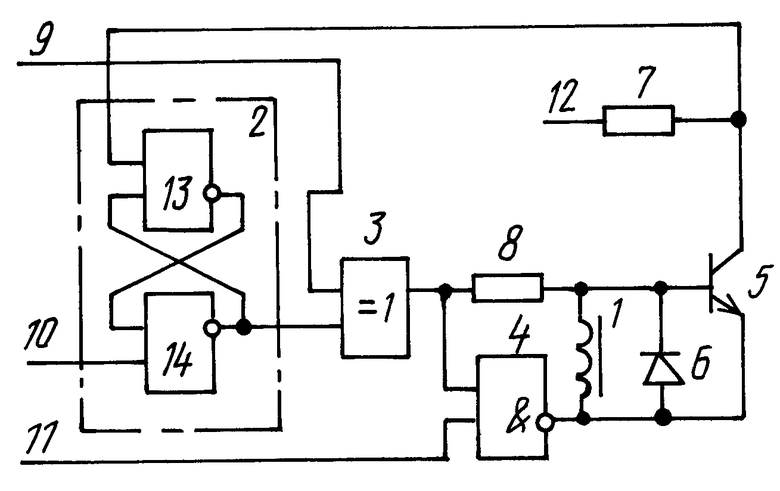

На чертеже приведена схема энергонезависимой ячейки памяти.

Энергонезависимая ячейка памяти содержит сердечник 1 с ППГ и обмоткой, асинхронный RS-триггер 2, элемент 3 "исключающее ИЛИ", элемент 4 И-НЕ, транзистор 5, диод 6, резистор 7, дополнительный резистор 8, информационную шину 9, шину 10 сброса, шину 11 перемагничивания, шину 12 питания. RS-триггер 2 выполнен на элементах 13 и 14 И-НЕ по известной схеме (см. кн.:Букреев И.Н., Мансуров Б.М., Горячев В.И. Микроэлектронные схемы цифровых устройств. - М.: Сов.Радио, 1975, с.57, рис.2.3а).

R-вход триггера 2 подключен к шине 10 сброса, инверсный выход - к одному из входов элемента 3 "исключающее ИЛИ", другой вход которого соединен с информационной шиной 9. Один из входов элемента 4 И-НЕ соединен с шиной 11 перемагничивания, другой вход - с выходом элемента 3 "исключающее ИЛИ" и через дополнительный резистор 8 - с началом обмотки сердечника 1, катодом диода 6 и базой транзистора 5, эмиттер которого соединен с анодом диода 6, концом обмотки сердечника 1 и выходом элемента 4 И-НЕ, а коллектор - с S-входом триггера 2 и через резистор 7 с шиной 12 питания.

RS-триггер 2 выполнен на элементах 13 и 14 И-НЕ. Один из входов элемента 13 И-НЕ соединен с S-входом триггера 2, один из входов элемента 14 И-НЕ соединен с R-входом триггера 2, а выход - с инверсным выходом триггера 2.

Элемент 3 "исключающее ИЛИ" выполнен на микросхеме 564ЛП2, элементы 4, 13 и 14 И-НЕ - на микросхеме 564ЛА7, в качестве транзистора 5 использован транзистор 2Т312Б, в качестве диода 6 - диод 2Д510А, в качестве резисторов 7 и 8 - резисторы С2 - 33Н - 0,125 - 10 кОм ± 5%. В качестве сердечника 1 использован сердечник ленточный кольцевой М2,5 - 3/2,5 - 45 де4.804.004ТУ. Число витков обмотки 300.

В силу дуальности схемы RS-триггер 2 может быть выполнен на элементах 13 и 14 ИЛИ-НЕ. Тогда в качестве логического элемента 4 нужно использовать элемент ИЛИ-НЕ, использовать транзистор 5 типа p-n-p, изменить полярность включения диода 6 и подключить резистор 7 не к шине питания 12 (шине питания с положительным потенциалом), а к общей шине (шине питания с отрицательным потенциалом). Полярность сигналов на входах 9, 10, 11 также изменится на противоположную.

Логические элементы 3, 4, 13, 14 могут быть выполнены на КМОП микросхемах других серий, например серий К176, К561. В качестве транзистора 5 могут использоваться транзисторы матрицы 1НТ251 и другие, в качестве диода 6 - диоды 2Д522Б и другие, в качестве резисторов 7 и 8 - резисторы типа С2-23 и другие. В качестве сердечника 1 может использоваться сердечник зМЧ - 3/2,5 - 60 де4.804.005ТУ.

Энергонезависимая ячейка памяти работает следующим образом. В исходном состоянии на шинах 9, 10 и 11 присутствует уровень логического "0". Триггер 2 принудительно удерживается в состоянии логического "0", на его инверсном выходе, а следовательно, и на выходе элемента 3 "исключающее ИЛИ" присутствует уровень логической "1". На выходе элемента 4 И-НЕ также присутствует уровень логической "1". Поэтому ток через обмотку сердечника 1 не протекает. Транзистор 5 закрыт, на S-входе триггера 2 присутствует уровень логической "1", поступающий с шины 12 через резистор 7.

Допустим, что сердечник 1 находится в состоянии логического "0". За состояние логического "0" сердечника 1 принято состояние, в которое он перемагничивается током, втекающим в обмотку со стороны начала (*). При этом ячейка памяти находится в состоянии логического "0".

Для переключения ячейки памяти в состояние логической "1" необходимо подать уровень логической "1" на шину 11. При этом на выходе элемента 4 И-НЕ установится уровень логического "0". Через обмотку сердечника 1 начнет протекать ток в направлении с выхода элемента 3 "исключающее ИЛИ" через резистор 8 на выход элемента 4 И-НЕ, ограничиваемый резистором 8. При этом подтверждается состояние логического "0" сердечника 1. Поскольку перемагничивание сердечника 1 не производится, падение напряжения на нем недостаточно для открывания транзистора 5. Если же сердечник 1 был частично перемагничен помехами в состояние логической "1", то на обмотке сердечника 1 формируется импульс положительной полярности, открывающий транзистор 5. При этом на S-входе триггера 2 формируется уровень логического "0", однако уровень напряжения на его инверсном выходе не изменяется вследствие наличия уровня логического "0" на R-входе.

После восстановления состояния логического "0" сердечника 1 транзистор 5 закрывается, на S-входе триггера 2 восстанавливается уровень логической "1". Затем на шину 10 поступает уровень логической "1", разрешающий переключение триггера 2 в состояние логической "1".

С задержкой относительно момента поступления уровня логической "1" на шину 10 поступает уровень логической "1" на шину 9. При этом на выходе элемента 3 "исключающее ИЛИ" устанавливается уровень логического "0", а на выходе элемента 4 И-НЕ - уровень логической "1". При этом сердечник 1 начинает перемагничиваться в состояние логической "1" током, втекающим в обмотку с выхода элемента 4 И-НЕ. Величина тока, а следовательно, и скорость перемагничивания ограничиваются резистором 8 и диодом 6.

После перемагничивания сердечника 1 в состояние логической "1" энергонезависимая ячейка находится в состоянии логической "1". На шины 9, 10 и 11 поступает уровень логического "0". Триггер 2 принудительно удерживается в состоянии логического "0". На выходах элементов 3 и 4 (исключающее ИЛИ и И-НЕ соответственно) и на S-входе триггера 2 присутствует уровень логической "1".

Для переключения ячейки памяти в состояние логического "0" необходимо подать уровень логической "1" на шину 11. При этом на выходе элемента 4 И-НЕ установится уровень логического "0". Через обмотку сердечника 1 начнет протекать ток в направлении с выхода 3 "исключающее ИЛИ". Сердечник 1 начнет перемагничиваться в состояние логического "0", на обмотке сердечника 1 сформируется импульс положительной полярности, амплитуда которого ограничена прямосмещенным переходом транзистора 5, который открывается и формирует уровень логического "0" на S-входе триггера 2.

С некоторой задержкой поступает уровень логической "1" на шину 10, разрешая переключение триггера 2 в состояние логической "1" сигналом по S-входу. На инверсном выходе триггера 2 устанавливается уровень логического "0". На выходе элемента 3 "исключающее ИЛИ" устанавливается уровень логического "0", а на выходе элемента 4 И-НЕ - уровень логической "1". Транзистор 5 закрывается. Сердечник 1 начинает восстанавливать состояние логической "1".

После переключения триггера 2 в состояние логической "1" можно подавать уровень логической "1" на шину 9. При этом на выходе элемента 3 "исключающее ИЛИ" устанавливается уровень логической "1", а на выходе элемента 4 И-НЕ - уровень логического "0". При этом сердечник 1 начинает перемагничиваться в состояние логического "0". Транзистор 5 открыт и подтверждает состояние логической "1" триггера 2. После перемагничивания сердечника 1 в состояние логического "0" транзистор 5 закрывается. Ячейка памяти находится в состоянии логического "0". На шины 9, 10 и 11 поступает уровень логического "0". Ячейка памяти устанавливается в исходное состояние.

Для опроса состояния ячейки памяти необходимо подать уровень логической "1" последовательно на шины 11 и 10, не подавая уровень логической "1" на шину 9.

В режиме хранения информации состояние ячейки памяти записано в сердечник 1 с ППГ. RS-триггер 2 принудительно удерживается в состоянии логического "0". Обмотка сердечника 1 обесточена. На шинах 9, 10 и 11 присутствует уровень логического "0". В указанных условиях присутствие напряжения питания на элементах ячейки памяти не является необходимым. Питание необходимо только во время присутствия уровня логической "1" на шинах 9, 10 и 11.

Таким образом, описание работы подтверждает нормальное функционирование энергонезависимой ячейки в счетном режиме. В режиме хранения информации ячейка памяти допускает выключение напряжения питания. Ячейка памяти позволяет производить опрос состояния сердечника 1 без разрушения.

В заявляемой ячейке памяти достигается уменьшение потребляемой мощности за счет уменьшения необходимой величины тока в обмотке путем использования всех витков в одной обмотке и уменьшения амплитуды импульса на обмотке при перемагничивании сердечника. Поэтому после перемагничивания сердечника увеличения тока в обмотке практически не происходит.

Одновременно достигается повышение помехоустойчивости за счет использования инерционности перемагничивания сердечника для селекции входных импульсов по длительности. Критическая длительность счетных импульсов задается задержкой в поступлении сигнала на шину 10 относительно шины 11. При этом ячейка памяти чувствительна к помехам по шине 9 только в состоянии логического "0".

Одновременно в заявляемой ячейке памяти достигается упрощение схемы в связи с отсутствием необходимости в счетном триггере и в связи с уменьшением числа входных шин с 4 до 3.

В институте изготовлен лабораторный макет энергонезависимой ячейки памяти, испытания которого подтвердили осуществимость и практическую ценность заявляемого объекта. Максимальный ток, потребляемый макетом в режиме считывания и перезаписи, равен 2 мА, а помехоустойчивость 100 мкс.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1992 |

|

RU2030094C1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 2002 |

|

RU2230427C2 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1990 |

|

SU1811353A1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1991 |

|

RU2036547C1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1999 |

|

RU2215337C2 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1991 |

|

RU2034397C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2001 |

|

RU2207716C2 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1990 |

|

SU1734563A1 |

| Энергонезависимая ячейка памяти | 1979 |

|

SU845287A1 |

| ПОМЕХОУСТОЙЧИВЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1991 |

|

RU2038692C1 |

Энергонезависимая ячейка памяти, содержащая сердечник с прямоугольной петлей гистерезиса и обмоткой, первый вывод которой подключен к выходу первого логического элемента, который выполнен в виде элемента И - НЕ, один из входов которого соединен с шиной перемагничивания, триггер, R-вход которого подключен к шине сброса, инверсный выход - к одному из входов второго логического элемента, резистор, один вывод которого подключен к шине питания, и информационную шину, отличающаяся тем, что, с целью уменьшения потребляемой мощности и повышения помехоустойчивости, введены дополнительный резистор, транзистор и диод, второй логический элемент выполнен в виде элемента "исключающее ИЛИ", а триггер - в виде асинхронного RS-триггера на элементах И - НЕ, при этом другой вход второго логического элемента соединен с информационной шиной, выход - с другим входом элемента И - НЕ и через дополнительный резистор - с вторым выводом обмотки сердечника, катодом диода и базой транзистора, коллектор которого соединен с другим выводом резистора и S-входом триггера, эмиттер - с анодом диода и первым выводом обмотки сердечника.

Энергонезависимая ячейка памяти, содержащая сердечник с прямоугольной петлей гистерезиса и обмоткой, первый вывод которой подключен к выходу первого логического элемента, который выполнен в виде элемента И - НЕ, один из входов которого соединен с шиной перемагничивания, триггер, R-вход которого подключен к шине сброса, инверсный выход - к одному из входов второго логического элемента, резистор, один вывод которого подключен к шине питания, и информационную шину, отличающаяся тем, что, с целью уменьшения потребляемой мощности и повышения помехоустойчивости, введены дополнительный резистор, транзистор и диод, второй логический элемент выполнен в виде элемента "Исключающее ИЛИ", а триггер - в виде асинхронного RS-триггера на элементах И - НЕ, при этом другой вход второго логического элемента соединен с информационной шиной, выход - с другим входом элемента И - НЕ и через дополнительный резистор - со вторым выводом обмотки сердечника, катодом диода и базой транзистора, коллектор которого соединен с другим выводом резистора и S-входом триггера, эмиттер - с анодом диода и первым выводом обмотки сердечника.

| Триггерное устройство (его варианты) | 1981 |

|

SU970650A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Энергонезависимая ячейка памяти | 1979 |

|

SU845287A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1998-09-27—Публикация

1990-12-06—Подача