Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления.

Известно триггерное устройство (см. авторское свидетельство СССР №1753919 от 05.10.90, МКИ: Н 03 К 3/037 “Триггерное устройство”, авторы Л.Б. Егоров, Г.И. Шишкин, опубл. 10.09.97, бюл. №25), содержащее первый и второй элементы памяти на магнитных сердечниках, выходы обмоток считывания которых соединены с общей шиной, входы обмоток записи соединены соответственно с прямым и инверсным выходами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого подключены к входной шине и выходу RS-триггера соответственно, входы установки и сброса которого соединены через соответственно первый и второй резисторы с входами обмоток считывания первого и второго элементов памяти соответственно. Первый вход блока управления соединен с входной шиной, второй и третий входы блока управления соединены соответственно с прямым и инверсным выходами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а первый и второй выходы блока управления соответственно через третий и четвертый резисторы соединены с выходами обмоток записи соответственно первого и второго элементов памяти.

Недостатком данного триггерного устройства является сравнительно большой ток потребления от источника питания.

Известно триггерное устройство (см. патент РФ №2106742 от 16.08.95, МКИ: Н 03 К 3/286 “Триггерное устройство”, авторы Е.И. Рыжаков, Г.И. Шишкин, опубл. 10.03.98, бюл. №7), которое является наиболее близким по технической сущности к заявляемому объекту и выбрано в качестве прототипа, содержащее RS-триггер, входы установки и сброса которого соединены с первыми выводами первого и второго резисторов соответственно и через соответственно первый и второй конденсаторы - с общей шиной, а прямой и инверсный выходы соединены с первыми входами соответственно первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входы которых подключены к входной шине триггерного устройства, а выходы соединены с входами обмоток записи соответственно первого и второго элементов памяти на магнитных сердечниках, входы обмоток считывания которых соединены с общей шиной, первый и второй элементы И-НЕ, третий и четвертый элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, третий, четвертый, пятый и шестой резисторы. RS- триггер выполнен на элементах И-НЕ. Выходы первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с первыми входами соответственно третьего и четвертого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы которых через соответственно третий и четвертый резисторы соединены с выходами обмоток записи соответственно первого и второго элементов памяти, выходы обмоток считывания которых через соответственно пятый и шестой резисторы соединены с первыми входами соответственно первого и второго элементов И-НЕ, выходы которых соединены со вторыми выводами соответственно второго и первого резисторов и со вторыми входами соответственно четвертого и третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ. Вторые входы первого и второго элементов И-НЕ объединены и подключены к входной шине триггерного устройства.

Недостатком прототипа является сравнительно большой ток потребления от источника питания.

Задачей, решаемой заявляемым изобретением, является уменьшение тока потребления от источника питания.

Указанный технический результат достигается тем, что в триггерном устройстве, содержащем RS-триггер, входы сброса и установки которого соединены с общей шиной через первый и второй конденсаторы соответственно и с первыми выводами первого и второго резисторов соответственно, первый и второй элементы И-НЕ, первые входы которых объединены и соединены с входной шиной, третий и четвертый резисторы, первый и второй элементы памяти на магнитных сердечниках с прямоугольной петлей гистерезиса, новым является введение первого и второго двухканальных демультиплексоров, первого и второго элементов ИЛИ-НЕ, первый и второй элементы памяти на магнитных сердечниках с прямоугольной петлей гистерезиса содержат по одной обмотке, средние точки которых через третий и четвертый резисторы соединены с первыми входами первого и второго элементов ИЛИ-НЕ соответственно и с выходами первого и второго элементов И-НЕ соответственно, вторые входы которых соединены с прямым и инверсным выходами RS-триггера соответственно, выходы первого и второго элементов ИЛИ-НЕ соединены с входами обмоток первого и второго элементов памяти соответственно, первый информационный вход первого демультиплексора соединен со вторым информационным входом второго демультиплексора, со вторым входом второго элемента ИЛИ-НЕ и с выходом обмотки первого элемента памяти, выход обмотки второго элемента памяти соединен со вторым входом первого элемента ИЛИ-НЕ, со вторым информационным входом первого демультиплексора и с первым информационным входом второго демультиплексора, управляющие входы первого и второго демультиплексоров объединены и соединены с входной шиной, выходы первого и второго демультиплексоров соединены со вторыми выводами соответственно первого и второго резисторов, RS-триггер выполнен на элементах ИЛИ-НЕ.

Указанная совокупность существенных признаков позволяет уменьшить ток потребления триггерного устройства от источника питания за счет возможности уменьшения тока подмагничивания сердечников путем увеличения количества витков в обмотках записи элементов памяти.

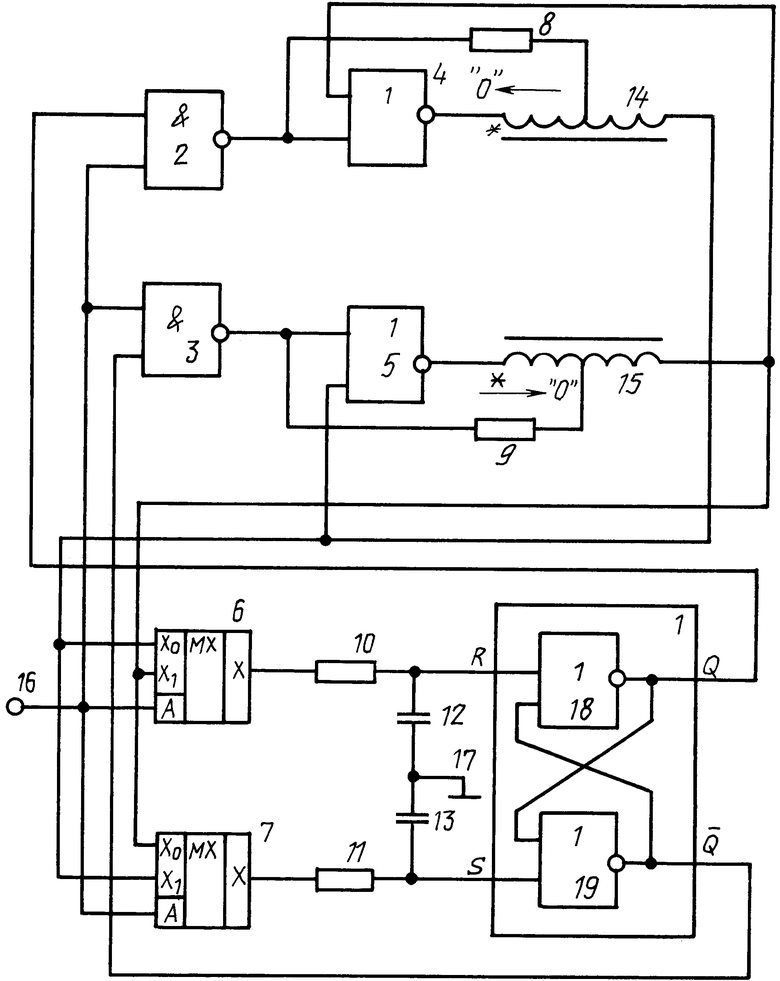

На чертеже приведена принципиальная электрическая схема триггерного устройства.

Триггерное устройство содержит RS-триггер 1, элементы 2 и 3 И-НЕ, элементы 4 и 5 ИЛИ-НЕ, двухканальные демультиплексоры 6 и 7, резисторы 8, 9, 10 и 11, конденсаторы 12 и 13, элементы 14 и 15 памяти на магнитных сердечниках с прямоугольной петлей гистерезиса (ППГ) с одной обмоткой, имеющей отвод от средней точки, входную шину 16 и общую шину 17. Первые входы элементов 2 и 3 И-НЕ объединены и соединены с входной шиной 16 и с управляющими входами демультиплексоров 6 и 7. Вторые входы элементов 2 и 3 соединены соответственно с прямым и инверсным выходами RS-триггера 1. Вход сброса RS-триггера 1 через резистор 10 соединен с выходом демультиплексора 6 и через конденсатор 12 - с общей шиной 17. Вход установки RS-триггера 1 через резистор 11 соединен с выходом демультиплексора 7 и через конденсатор 13 - с общей шиной 13. Выход элемента 2 И-НЕ соединен с первым входом элемента 4 ИЛИ-НЕ и через резистор 8 - со средней точкой обмотки элемента 14 памяти. Выход элемента 3 И-НЕ соединен с первым входом элемента 5 ИЛИ-НЕ и через резистор 9 - со средней точкой обмотки элемента 15 памяти. Второй вход элемента 4 ИЛИ-НЕ соединен с выходом обмотки элемента 15 памяти, со вторым информационным входом демультиплексора 6 и с первым информационным входом демультиплексора 7. Второй вход элемента 5 ИЛИ-НЕ соединен с выходом обмотки элемента 14 памяти, с первым информационным входом демультиплексора 6 и со вторым информационным входом демультиплексора 7. Выходы элементов 4 и 5 ИЛИ-НЕ соединены со входами обмоток элементов 14 и 15 памяти соответственно. RS-триггер 1 содержит элементы 18 и 19 ИЛИ-НЕ, при этом первые входы элементов 18 и 19 являются соответственно входами сброса и установки RS-триггера 1, выходы элементов 18 и 19 являются соответственно прямым и инверсным выходами RS-триггера, вторые входы элементов 18 и 19 соединены соответственно с выходами элементов 19 и 18.

Триггерное устройство работает следующим образом.

При включении питания (цепи питания логических элементов 2, 3, 4, 5, 6, 7, 18 и 19 для упрощения на чертеже не показаны) триггерное устройство установится в состояние, соответствующее состоянию элементов 14, 15 памяти, которое они приобрели в предыдущем цикле работы. Рассмотрим случай, когда элементы памяти 14 и 15 были намагничены в состояние “лог.0”, что соответствует направлению протекания тока в обмотке элемента 14 памяти от средней точки к ее входу, а в обмотке элемента 15 памяти - от входа к средней точке (входы обмоток на чертеже обозначены знаком (*)). Если после включения питания RS-триггер установился в нулевое состояние, при котором на его прямом выходе (Q)-сигнал “лог.0”, а на инверсном выходе  - сигнал “лог.1”, на выходах элементов 2 и 3 И-НЕ установятся сигналы “лог.1” и “лог.0” соответственно. На выходе элемента 4 - сигнал “лог.0”, поэтому ток через обмотку элемента 14 памяти потечет от ее средней точки ко входу, подтверждая направление намагниченности сердечника элемента 14 памяти, при этом на выходе обмотки элемента 14 памяти может возникнуть короткий импульс помехи положительной полярности относительно общей шины 17, связанный с непрямоугольностью петли гистерезиса сердечника элемента 14 памяти, который не окажет влияния на процесс восстановления схемы, поскольку осуществит только небольшую задержку включения элемента 5 в состояние с “лог.1” на выходе, а на S-входе RS-триггера 1 указанный импульс будет подавлен интегрирующей цепью, составленной из резистора 11 и конденсатора 13. После появления на выходе элемента 5 сигнала “лог.1” через обмотку элемента 15 памяти потечет ток в направлении от входа обмотки к ее средней точке, подтверждая направление намагниченности сердечника элемента 15 памяти, при этом на выходе обмотки элемента 15 памяти может возникнуть короткий импульс помехи. Амплитуда импульса помехи может достигать значения, близкого к величине напряжения питания схемы (Е); это объясняется тем, что значения сопротивлений резисторов 8 и 9 выбираются с таким расчетом, чтобы при перемагничивании сердечников в полуобмотках элементов 14 и 15 памяти возникал импульс напряжения с амплитудой, примерно равной Е/2, число витков в полуобмотках элементов 14 и 15 памяти примерно одинаково (под полуобмотками в данном случае понимаются части обмотки соответствующего элемента памяти от ее входа до средней точки и от средней точки до выхода). Указанный импульс помехи имеет отрицательную полярность относительно напряжения на выходе элемента 5, поэтому вызывает кратковременное появление сигнала “лог.0” относительно общей шины 17 на выходе обмотки элемента 15 памяти. Этот импульс помехи также не окажет влияния на процесс восстановления схемы, поскольку, с одной стороны, не влияет на состояние элемента 4 (на втором входе элемента 4 ИЛИ-НЕ - сигнал “лог.1”), с другой стороны, подавляется интегрирующей цепью, составленной из резистора 10 и конденсатора 12. После окончания переходных процессов на выходах обмоток элементов 14 и 15 памяти установятся сигналы соответственно “лог.0” и “лог.1”, на R-входе RS-триггера 1- сигнал “лог.1” (конденсатор 12 заряжен до напряжения, близкого к Е), на S-входе - сигнал “лог.0” (конденсатор 13 разряжен). Таким образом, триггерное устройство будет находиться в устойчивом состоянии “лог.0”.

- сигнал “лог.1”, на выходах элементов 2 и 3 И-НЕ установятся сигналы “лог.1” и “лог.0” соответственно. На выходе элемента 4 - сигнал “лог.0”, поэтому ток через обмотку элемента 14 памяти потечет от ее средней точки ко входу, подтверждая направление намагниченности сердечника элемента 14 памяти, при этом на выходе обмотки элемента 14 памяти может возникнуть короткий импульс помехи положительной полярности относительно общей шины 17, связанный с непрямоугольностью петли гистерезиса сердечника элемента 14 памяти, который не окажет влияния на процесс восстановления схемы, поскольку осуществит только небольшую задержку включения элемента 5 в состояние с “лог.1” на выходе, а на S-входе RS-триггера 1 указанный импульс будет подавлен интегрирующей цепью, составленной из резистора 11 и конденсатора 13. После появления на выходе элемента 5 сигнала “лог.1” через обмотку элемента 15 памяти потечет ток в направлении от входа обмотки к ее средней точке, подтверждая направление намагниченности сердечника элемента 15 памяти, при этом на выходе обмотки элемента 15 памяти может возникнуть короткий импульс помехи. Амплитуда импульса помехи может достигать значения, близкого к величине напряжения питания схемы (Е); это объясняется тем, что значения сопротивлений резисторов 8 и 9 выбираются с таким расчетом, чтобы при перемагничивании сердечников в полуобмотках элементов 14 и 15 памяти возникал импульс напряжения с амплитудой, примерно равной Е/2, число витков в полуобмотках элементов 14 и 15 памяти примерно одинаково (под полуобмотками в данном случае понимаются части обмотки соответствующего элемента памяти от ее входа до средней точки и от средней точки до выхода). Указанный импульс помехи имеет отрицательную полярность относительно напряжения на выходе элемента 5, поэтому вызывает кратковременное появление сигнала “лог.0” относительно общей шины 17 на выходе обмотки элемента 15 памяти. Этот импульс помехи также не окажет влияния на процесс восстановления схемы, поскольку, с одной стороны, не влияет на состояние элемента 4 (на втором входе элемента 4 ИЛИ-НЕ - сигнал “лог.1”), с другой стороны, подавляется интегрирующей цепью, составленной из резистора 10 и конденсатора 12. После окончания переходных процессов на выходах обмоток элементов 14 и 15 памяти установятся сигналы соответственно “лог.0” и “лог.1”, на R-входе RS-триггера 1- сигнал “лог.1” (конденсатор 12 заряжен до напряжения, близкого к Е), на S-входе - сигнал “лог.0” (конденсатор 13 разряжен). Таким образом, триггерное устройство будет находиться в устойчивом состоянии “лог.0”.

Если после включения питания RS-триггер установился в единичное состояние, при котором на его прямом (Q) выходе - сигнал “лог.1”, а на инверсном  выходе - сигнал “лог.0”, на выходах элементов 2 и 3 установятся сигналы соответственно “лог.0” и “лог.1”. В обмотках элементов 14 и 15 памяти потекут токи, направление которых не совпадает с направлением намагниченности сердечников элементов 14 и 15 памяти, при этом на выходе обмотки элемента 15 памяти появится сигнал “лог.1” относительно общей шины 17, который через демультиплексор 6 и резистор 10 будет заряжать конденсатор 12 до напряжения “лог.1”. Поскольку длительность импульса, возникающего на выходе обмотки элемента 15 памяти, выбирается больше, чем постоянная времени интегрирующей цепи (резистор 10, конденсатор 12), то с задержкой на R-входе RS-триггера 1 также появится сигнал “лог.1”. Сигнал “лог.1” с выхода обмотки элемента 15 памяти вызывает сигнал “лог.0” на выходе элемента 4 ИЛИ-НЕ, поэтому вход и средняя точка обмотки элемента 14 памяти находятся под одинаковыми потенциалами, на выходе обмотки элемента 14 памяти также напряжение, близкое к нулевому, конденсатор 13 поддерживается в разряженном состоянии, на S-входе RS-триггера - сигнал “лог.0”. Под действием указанных сигналов RS-триггер 1 переключится в состояние “лог.0”, на его выходе Q установится сигнал “лог.0”, на выходе

выходе - сигнал “лог.0”, на выходах элементов 2 и 3 установятся сигналы соответственно “лог.0” и “лог.1”. В обмотках элементов 14 и 15 памяти потекут токи, направление которых не совпадает с направлением намагниченности сердечников элементов 14 и 15 памяти, при этом на выходе обмотки элемента 15 памяти появится сигнал “лог.1” относительно общей шины 17, который через демультиплексор 6 и резистор 10 будет заряжать конденсатор 12 до напряжения “лог.1”. Поскольку длительность импульса, возникающего на выходе обмотки элемента 15 памяти, выбирается больше, чем постоянная времени интегрирующей цепи (резистор 10, конденсатор 12), то с задержкой на R-входе RS-триггера 1 также появится сигнал “лог.1”. Сигнал “лог.1” с выхода обмотки элемента 15 памяти вызывает сигнал “лог.0” на выходе элемента 4 ИЛИ-НЕ, поэтому вход и средняя точка обмотки элемента 14 памяти находятся под одинаковыми потенциалами, на выходе обмотки элемента 14 памяти также напряжение, близкое к нулевому, конденсатор 13 поддерживается в разряженном состоянии, на S-входе RS-триггера - сигнал “лог.0”. Под действием указанных сигналов RS-триггер 1 переключится в состояние “лог.0”, на его выходе Q установится сигнал “лог.0”, на выходе  - сигнал “лог.1”, изменятся на противоположные сигналы на выходах элементов 2 и 3, изменятся направления намагниченности в обмотках элементов 14 и 15 памяти. Короткие импульсы помех, возникающие на выходах обмоток элементов 14 и 15 памяти в процессе восстановления состояния сердечников, как было показано выше, не окажут влияние на работу схемы, поскольку будут подавлены интегрирующими RC-цепями (резисторы 10 и 11, конденсаторы 12 и 13). В результате, триггерное устройство также установится в устойчивое состояние “лог.0”. Аналогичным образом происходит восстановление состояния RS-триггера 1 в соответствии с состояниями намагниченности элементов 14 и 15 памяти в случае, когда в элементы 14 и 15 памяти в предыдущем цикле работы триггерного устройства было записано состояние “лог. 1”.

- сигнал “лог.1”, изменятся на противоположные сигналы на выходах элементов 2 и 3, изменятся направления намагниченности в обмотках элементов 14 и 15 памяти. Короткие импульсы помех, возникающие на выходах обмоток элементов 14 и 15 памяти в процессе восстановления состояния сердечников, как было показано выше, не окажут влияние на работу схемы, поскольку будут подавлены интегрирующими RC-цепями (резисторы 10 и 11, конденсаторы 12 и 13). В результате, триггерное устройство также установится в устойчивое состояние “лог.0”. Аналогичным образом происходит восстановление состояния RS-триггера 1 в соответствии с состояниями намагниченности элементов 14 и 15 памяти в случае, когда в элементы 14 и 15 памяти в предыдущем цикле работы триггерного устройства было записано состояние “лог. 1”.

Для переключения триггерного устройства на входную шину 16 подается тактовый сигнал с уровнем “лог.0”. При этом на выходах элементов 2 и 3 И-НЕ появляются сигналы “лог.1”, на выходах элементов 4 и 5 ИЛИ-НЕ - сигналы “лог.0”, демультиплексоры 6 и 7 переходят в режим трансляции на выход сигналов, подаваемых на их первые информационные входы. Рассмотрим процесс переключения триггерного устройства, находящегося в состоянии “лог.0”, то есть на Q-выходе - сигнал “лог.0”, на  -выходе - сигнал “лог.1”. Направление тока в обмотке элемента 14 памяти сохраняется прежним, поэтому на выходе обмотки элемента 14 памяти сохранится сигнал “лог.0”, который теперь через демультиплексор 6 и резистор 10 будет разряжать конденсатор 12 в нулевое состояние. Направление тока в обмотке элемента 15 изменится на противоположное, поэтому на выходе обмотки элемента 15 памяти появится импульс напряжения с амплитудой, близкой к величине Е, относительно общей шины 17, который, передаваясь через демультиплексор 7 и резистор 11, будет заряжать конденсатор 13 до уровня “лог.1”. Под воздействием указанных сигналов RS-триггер с некоторой задержкой переключится в состояние “лог.1” (на Q-выходе - сигнал “лог.1”, на

-выходе - сигнал “лог.1”. Направление тока в обмотке элемента 14 памяти сохраняется прежним, поэтому на выходе обмотки элемента 14 памяти сохранится сигнал “лог.0”, который теперь через демультиплексор 6 и резистор 10 будет разряжать конденсатор 12 в нулевое состояние. Направление тока в обмотке элемента 15 изменится на противоположное, поэтому на выходе обмотки элемента 15 памяти появится импульс напряжения с амплитудой, близкой к величине Е, относительно общей шины 17, который, передаваясь через демультиплексор 7 и резистор 11, будет заряжать конденсатор 13 до уровня “лог.1”. Под воздействием указанных сигналов RS-триггер с некоторой задержкой переключится в состояние “лог.1” (на Q-выходе - сигнал “лог.1”, на  -выходе - сигнал “лог.0”, при этом сигналы на выходах элементов 2 и 3 не изменятся, не изменятся и токи в обмотках элементов 14 и 15 памяти. После перемагничивания сердечника элемента 15 памяти импульс напряжения положительной полярности на выходе его обмотки закончится, конденсатор 13 разрядится в нулевое состояние, с соответствующей задержкой на S-входе установится сигнал “лог.0”, RS-триггер при этом останется в состоянии “лог.1”. В таком состоянии схема останется до окончания тактового сигнала на входе 16; после окончания тактового сигнала элементы 2 и 3 снова переходят в режим инверсии сигналов, поступающих с выходов RS-триггера 1, демультиплексоры 6 и 7 снова будут транслировать на выходы сигналы, поступающие на их вторые информационные входы. На выходе элемента 2 И-НЕ появляется сигнал “лог.0”, на выходе элемента 4 ИЛИ-НЕ - сигнал “лог.1”, ток в обмотке элемента 14 памяти изменится на противоположный, при этом на выходе обмотки элемента 14 появится импульс напряжения отрицательной полярности относительно уровня Е, с амплитудой, близкой к величине Е, то есть импульс “лог.0”. Указанный импульс напряжения не изменит режим намагничивания элемента 15, поскольку в это время сохраняется работа элемента 5 в режиме инвертора. Проходя через демультиплексор 7, импульс с выхода обмотки элемента 14 памяти сохраняет разряженное состояние конденсатора 13, то есть сохраняется сигнал “лог.0” на S-входе RS-триггера 1. На выходе элемента 3 И-НЕ сохранится сигнал “лог.1”, который присутствовал во время действия тактового сигнала, поэтому направление тока через обмотку элемента 15 памяти сохранится. На выходе обмотки элемента 15 памяти присутствует нулевой уровень сигнала, который поддерживает разряженное состояние конденсатора 12. Нулевые сигналы на R- и S-входах RS-триггера 1 не изменят его состояния. После перемагничивания сердечника элемента 14 памяти импульс “лог.0” на выходе обмотки элемента 14 памяти заканчивается, там устанавливается сигнал “лог.1”, при этом состояние элемента 5 не изменится, поскольку на его втором входе - сигнал “лог.1”; конденсатор 13 начинает заряжаться до уровня “лог.1”, на S-входе с задержкой установится сигнал “лог.1”, подтверждающий единичное состояние RS-триггера 1. На этом процесс переключения триггерного устройства в состояние “лог.1” заканчивается. Аналогично происходит переключение триггерного устройства из состояния “лог.1” в состояние “лог.0”.

-выходе - сигнал “лог.0”, при этом сигналы на выходах элементов 2 и 3 не изменятся, не изменятся и токи в обмотках элементов 14 и 15 памяти. После перемагничивания сердечника элемента 15 памяти импульс напряжения положительной полярности на выходе его обмотки закончится, конденсатор 13 разрядится в нулевое состояние, с соответствующей задержкой на S-входе установится сигнал “лог.0”, RS-триггер при этом останется в состоянии “лог.1”. В таком состоянии схема останется до окончания тактового сигнала на входе 16; после окончания тактового сигнала элементы 2 и 3 снова переходят в режим инверсии сигналов, поступающих с выходов RS-триггера 1, демультиплексоры 6 и 7 снова будут транслировать на выходы сигналы, поступающие на их вторые информационные входы. На выходе элемента 2 И-НЕ появляется сигнал “лог.0”, на выходе элемента 4 ИЛИ-НЕ - сигнал “лог.1”, ток в обмотке элемента 14 памяти изменится на противоположный, при этом на выходе обмотки элемента 14 появится импульс напряжения отрицательной полярности относительно уровня Е, с амплитудой, близкой к величине Е, то есть импульс “лог.0”. Указанный импульс напряжения не изменит режим намагничивания элемента 15, поскольку в это время сохраняется работа элемента 5 в режиме инвертора. Проходя через демультиплексор 7, импульс с выхода обмотки элемента 14 памяти сохраняет разряженное состояние конденсатора 13, то есть сохраняется сигнал “лог.0” на S-входе RS-триггера 1. На выходе элемента 3 И-НЕ сохранится сигнал “лог.1”, который присутствовал во время действия тактового сигнала, поэтому направление тока через обмотку элемента 15 памяти сохранится. На выходе обмотки элемента 15 памяти присутствует нулевой уровень сигнала, который поддерживает разряженное состояние конденсатора 12. Нулевые сигналы на R- и S-входах RS-триггера 1 не изменят его состояния. После перемагничивания сердечника элемента 14 памяти импульс “лог.0” на выходе обмотки элемента 14 памяти заканчивается, там устанавливается сигнал “лог.1”, при этом состояние элемента 5 не изменится, поскольку на его втором входе - сигнал “лог.1”; конденсатор 13 начинает заряжаться до уровня “лог.1”, на S-входе с задержкой установится сигнал “лог.1”, подтверждающий единичное состояние RS-триггера 1. На этом процесс переключения триггерного устройства в состояние “лог.1” заканчивается. Аналогично происходит переключение триггерного устройства из состояния “лог.1” в состояние “лог.0”.

Восстановление состояния триггерного устройства, если произойдет его сбой под действием помехи в режиме хранения информации, осуществляется в соответствии с состояниями элементов 14 и 15 памяти аналогично тому, как происходит его восстановление при включении напряжения питания. Например, если триггерное устройство находится в состоянии “лог.0” (на Q-выходе RS-триггера - сигнал “лог.0”, сердечники элементов 14 и 15 памяти намагничены в состояние “лог.0”, как показано стрелками на чертеже), и помеха переключит RS-триггер 1 в состояние “лог.1” (UQ=1,  ), то на выходе обмотки элемента 15 памяти появится сигнал “лог.1”, подтверждающий заряженное состояние конденсатора 12; сигнал “лог.1” с выхода обмотки элемента 15 памяти создаст сигнал “лог.0” на выходе элемента 4, поэтому обмотка элемента 14 памяти обесточена и на ее выходе - сигнал “лог.0”, обеспечивающий при переключении работу элемента 5 в режиме инвертора. Кроме того, сигнал “лог.0” с выхода обмотки элемента 14 памяти подтверждает разряженное состояние конденсатора 13. Под действием сигналов на R- и S-входах RS-триггер 1 переключится в состояние “лог.0”, направление токов в обмотках элементов 14 и 15 памяти восстановится в первоначальное состояние, на этом процесс восстановления триггерного устройства заканчивается.

), то на выходе обмотки элемента 15 памяти появится сигнал “лог.1”, подтверждающий заряженное состояние конденсатора 12; сигнал “лог.1” с выхода обмотки элемента 15 памяти создаст сигнал “лог.0” на выходе элемента 4, поэтому обмотка элемента 14 памяти обесточена и на ее выходе - сигнал “лог.0”, обеспечивающий при переключении работу элемента 5 в режиме инвертора. Кроме того, сигнал “лог.0” с выхода обмотки элемента 14 памяти подтверждает разряженное состояние конденсатора 13. Под действием сигналов на R- и S-входах RS-триггер 1 переключится в состояние “лог.0”, направление токов в обмотках элементов 14 и 15 памяти восстановится в первоначальное состояние, на этом процесс восстановления триггерного устройства заканчивается.

Из описания работы триггерного устройства видно, что его нормальная работа обеспечивается при равенстве числа витков в полуобмотках элементов 14 и 15 памяти, при этом одна полуобмотка (между входом и средней точкой обмотки) по аналогии с прототипом выполняет роль обмотки записи, а обе включенные последовательно полуобмотки выполняют роль обмотки считывания. В схеме прототипа для ее нормального функционирования обмотка считывания должна содержать примерно в 2 раза больше витков, чем обмотка записи, следовательно, в заявляемом устройстве, с учетом совмещения обмоток записи и считывания, каждый элемент памяти может содержать на одну треть меньшее количество витков, или при выбранных размерах сердечников имеется возможность увеличения в 1.5 раза количества витков в обмотках записи и считывания (в каждой из полуобмоток элементов 14 и 15 памяти), а значит, уменьшения примерно в 1.5 раза тока намагничивания сердечников элементов памяти, за счет увеличения сопротивления ограничительных резисторов 8 и 9. В результате, уменьшается ток потребления триггерного устройства от источника питания в статическом и динамическом режимах его работы.

Таким образом, как следует из описания работы, заявляемое триггерное устройство имеет меньший ток потребления от источника питания.

Испытания лабораторного макета триггерного устройства подтвердили осуществимость и практическую ценность заявляемого устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2248663C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2250555C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2250554C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2250557C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2002 |

|

RU2248662C2 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1983 |

|

SU1145890A1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1999 |

|

RU2215337C2 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2250556C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2248664C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1995 |

|

RU2106742C1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления. Технический результат заключается в уменьшении тока потребления от источника питания. Устройство содержит RS-триггер (1), элементы (Э) И-НЕ (2) и (3), (Э) ИЛИ-НЕ (4) и (5), двухканальные демультиплексоры (6) и (7), резисторы (8)-(11), конденсаторы (12) и (13), (Э) (14) и (15) памяти на магнитных сердечниках с прямоугольной петлей гистерезиса с одной обмоткой, имеющей отвод от средней точки, входную шину (16) и общую шину (17). 1 ил.

Триггерное устройство, содержащее RS-триггер, входы сброса и установки которого соединены с общей шиной через первый и второй конденсаторы соответственно и с первыми выводами первого и второго резисторов соответственно, первый и второй элементы И-НЕ, первые входы которых объединены и соединены с входной шиной, третий и четвертый резисторы, первый и второй элементы памяти на магнитных сердечниках с прямоугольной петлей гистерезиса, отличающееся тем, что введены первый и второй двухканальные демультиплексоры, первый и второй элементы ИЛИ-НЕ, первый и второй элементы памяти на магнитных сердечниках с прямоугольной петлей гистерезиса содержат по одной обмотке, средние точки которых через третий и четвертый резисторы соединены с первыми входами первого и второго элементов ИЛИ-НЕ соответственно и с выходами первого и второго элементов И-НЕ соответственно, вторые входы которых соединены с прямым и инверсным выходами RS-триггера соответственно, выходы первого и второго элементов ИЛИ-НЕ соединены с входами обмоток первого и второго элементов памяти соответственно, первый информационный вход первого демультиплексора соединен со вторым информационным входом второго демультиплексора, со вторым входом второго элемента ИЛИ-НЕ и с выходом обмотки первого элемента памяти, выход обмотки второго элемента памяти соединен со вторым входом первого элемента ИЛИ-НЕ, со вторым информационным входом первого демультиплексора и с первым информационным входом второго демультиплексора, управляющие входы первого и второго демультиплексоров объединены и соединены с входной шиной, выходы первого и второго демультиплексоров соединены со вторыми выводами соответственно первого и второго резисторов, RS-триггер выполнен на элементах ИЛИ-НЕ.

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1995 |

|

RU2106742C1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1991 |

|

RU2036547C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1990 |

|

SU1753919A1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1980 |

|

SU852131A1 |

| КАРКАСНЫЙ АРБОЛИТ | 2000 |

|

RU2243188C2 |

Авторы

Даты

2004-10-10—Публикация

2003-06-09—Подача