Изобретение относится к цифровым вычислительным машинам, в частности к устройствам для выполнения математических операций в двоичном представлении, и может быть использовано в любой отрасли народного хозяйства, где необходима реализация вычислительного процесса в реальном масштабе времени, например для исследования быстроизменяющихся процессов,- протекающих в сложных динамических объектах.

Известно устройство для вычисления гиперболических функций. Устройство характеризуется тем, что оно

содержит п блоков вычисления итерации и блок синхронизации. Каждый блок вычисления итерации содержит входные регистры и сумматоры-вычита- тели„ Блок синхронизации содержит триггер, генератор импульсов, элемент И, счетчик и элемент ИЛИ-НЕ.

Недостатком этого устройства является низкое быстродействие из-за последовательного принципа его работы.

Наиболее близким к предлагаемому является матричный вычислитель гиперболических функций, содержащий сумматоры-матрицы, вычитателъ, для

1

СЈ

сд

00 Јъ

лл

Формирователей начальных значений, сумматор.

Недостатком известного устройства является низкая точность вычислений, обусловленная реализацией в нем приближенного способа представления аргумента.

Цель изобретения - повышение точности вычисления функций

В устройство, содержащее два комбинационных сумматора, дополнительно введены п-1 коммутатор, 2п-4 группы блоков частичной суммы, первые управляющие входы коммутаторов являются входом первого разряда кодовой комбинации, вторые управляющие входы 1,2,.с о,(п-1)-го коммутаторов являются входами соответственно 1,2,о„о,(п-1)-го разряда кодовой комбинации, на информационные входы 1,2,0о о,(п-1)-го коммутаторов поданы двоичные константы, соответственно равные 1/2, 2/3,.., , выход

первого коммутатора соединен с входами разрядной дискреты блоков частичной суммы первой группы, содержащей из (п-2)-х элементов, входы частичной суммы 1,2, с.., (п-2)-гоблоков частичной суммы первой группы являются соответственно входами 3,,«.. ,п-го - разряда кодовой комбинации, на информационные входы k-x блоков частичной суммы 1 и (1 + п - 2)-й группы подаkмы константы, равные , + , у, ,где

п - число разрядов входного аргумента , изменяется от 1 до n-2, k - от 1 до п-1-1, управляющие-входы k-x блоков частичной суммы 1 и (1 + п - 2)-й групп являются входами k-ro разряда кодовой комбинации, выходы 2,3,с о.,(п-1)-го коммутаторов соединены соответственно с входами частичной суммы 1,2,0.,(п-2)-го блоков частичной суммы (п-1)-и группы, вхо ды разрядной дискреты данных блоков являются входом второго разряда кодовой комбинации, выход первого бло- ka частичной суммы S-й группы, S изменяется от 1 до п-3, подан на вход (5+3)-й разрядной дискреты первого комбинационного сумматора со сдвигом на S+2 разряда вправо и одновременно соединен с входами раз- рядной дискреты блоков частичной суммы (S + п - 1)-й группы, выход j-ro блока частичной суммы S-й группы соединен с входом частичной суммы/

0

5

0

(j-1)-ro блока частичной суммы (S+ +1)-й группы, изменяется от 2 до n-S-1, выход первого блока частичной суммы п-2-и группы подан на вход (п+1)-й разрядной дискреты первого сумматора со сдвигом на п разрядов, выход первого блока частичной суммы (S + п - 2)-и группы подан на вход (S + 3)-й разрядной дискреты второго сумматора со сдвигом на S+2 разряда вправо и одновременно соединен с входами разрядной дискреты блоков частичной суммы (8+1)-й группы, выход j-ro блока частичной суммы (S + jt- n - 2)-и группы соединен с входом частичной суммы (j-l)-ro блока частичной суммы (S + п - 1)-й группы, выход первого блока частичной суммы (2п-4)-й группы подан на вход (п+1)-й разрядной дискреты второго сумматора со сдвигом на п разрядов вправо, на входы первой разрядной дискреты первого и второй разрядной дискреты втоe рого комбинационных сумматоров подан код нуля, входы второй, третьей разрядных дискрет первого комбинационного сумматора являются входами соответственно 1,2-го разрядов кодовой комбинации со сдвигом соответственно на 1,2 разряда, на вход первой разрядной дискреты второго комбинационного сумматора подан код единицы, блок частичной суммы содержит коммутатор с одним управляющим входом, умно5 житель, сумматор, управляющий вход коммутатора с одним управляющим входом является управляющим входом блока частичной суммы, информационный вход соединен с входом разрядной дискреты

0 блока частичной суммы, выход коммутатора с одним управляющим входом соединен с первым входом умножителя, второй вход которого является информационным входом блока частичной суммы,

5 выход умножителя соединен с первым входом сумматора, второй вход которого является входом частичной суммы блока частичной суммы, вход сумматора является выходом блока частичной суммы

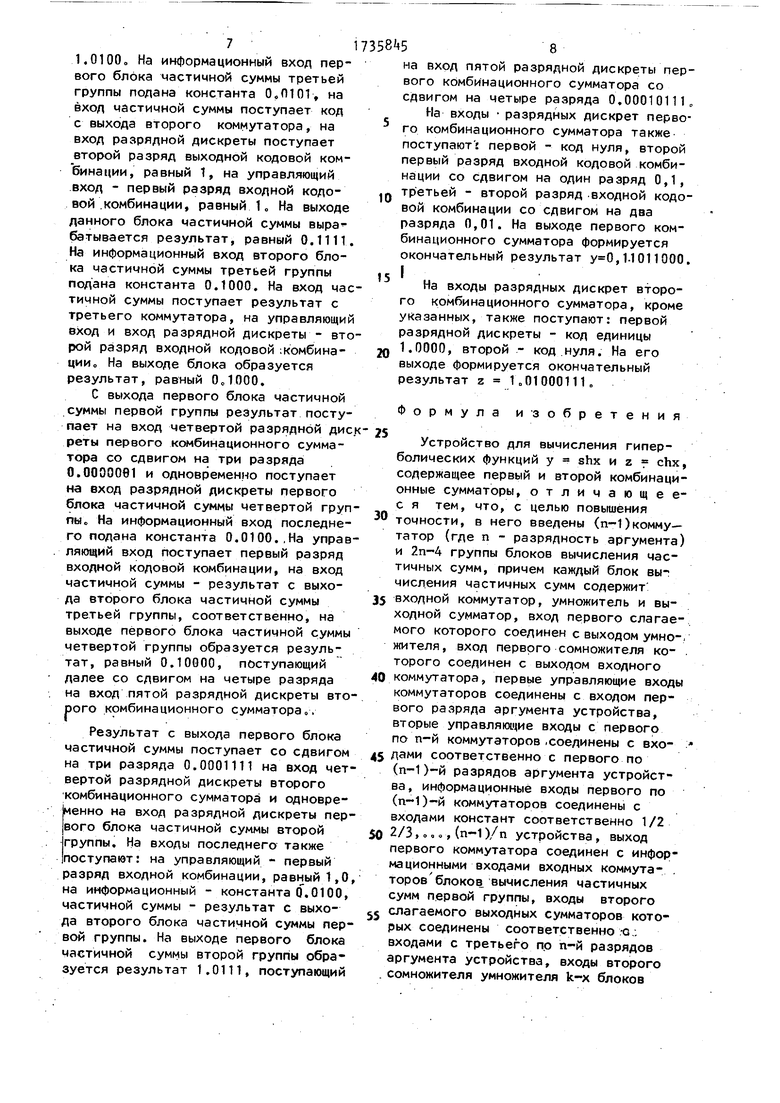

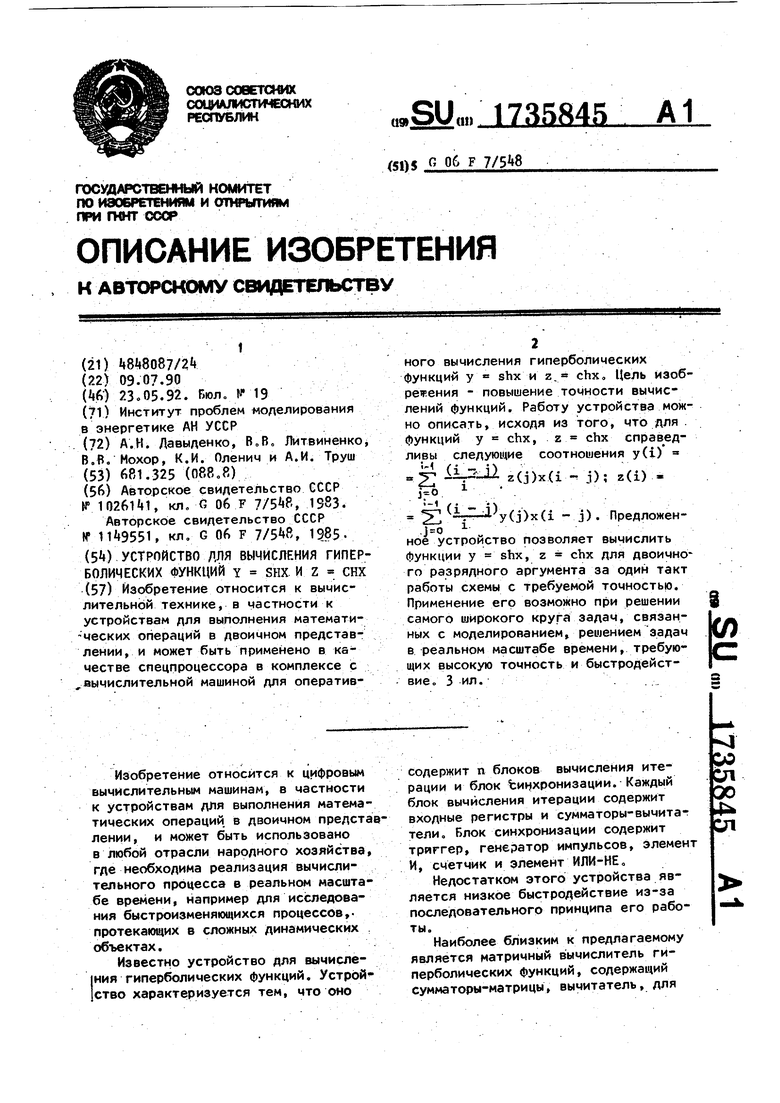

0 На фиг.1 показана блок-схема устройства для вычисления гиперболических функций у shx, z chx; на фиг.2 - блок-схема блока частичной . суммы; на фиг.З - схема коммутатора. Устройство (фиг„1) содержит коммутаторы 1(1), 1(2),„о0,1(1), (), блоки 2(1.1), 2(1.2),...,2(т.1) вычисления частичной суммы (), комбинационные сумматоры 3(1), 3(2).

0

5

51

Блок вычисления частичной суммы (фиг.2) содержит коммутатор с одним управляющим входом, умножитель 5 сумматор 6„ Все элементы схем (фиг.1 и 2) могут быть реализованы на любых известных стандартных логических элементах.

Коммутатор может быть, например, реализован по схеме, где показаны двухвходовые схемы И 7(1), 7(2),..., 7(j)() (фиг,ЗК

Работа устройства описывается исходя из того, что для функций у shx и z « chx справедливы соотношения

y(i)

z(j)x(i-j);

z(i)

(1 - Л)

y(j)x(i-j)

при у(0)0, z(0)1, ,2,...,n, 7 где x(i) - разряды аргумента;

y(i) и z(i) - разряды результата

Проведем анализ точности вычисле - ий на известном примере (х 0,8А1) ля функции у shx у(1) z(0)x(1)1; у(2) z(0)x(2) + 1/2z(1)x(1)1; у(3) z(0)x(3) + 2/3z(1)x(2) +

+ 1/3z(2)x(1)0,16666667; y(4) z(0)x(4) + 3/4z(1)x(3) + + 1/2z(2)x(2) + 1/4z(3)x(1)

-1.5;

y(5) z(0)x(5) + 4/5z(1)x(4) +

+ 3/5z(2)x(3) + 2/5z(3)x(2) + + 1,5z(4)x(1) « 1,508333;

у(6) 0,7083333;

у(7) 1,5835817;

у(8) 1,6263393;,

у - 0,941511.

Для функции z chx:

z(1) у(0)х(1)0;

z(2) - у(0)х(2) + 1/2у(1)х(1) 0,5;

z(3) - у(0)х(3) + 2/Зу(1)х(2) + + 1/Зу(2)х(1) 1;

z(4) у(0)х(4) + 3/МОх(3)

f 1/2y(2)x(2) + 1/4у(3)х(1)

0,541666;

z(5) « у(0)х(5) + 4/5у(1)х(4) + + 3/5у(2)х(3)+2/5у(3)х(2) + + 1/5у(4)х(1) 1,166666;

z(6) - 2,2513889;

z(7) 1,341666;

z(8) - 1,2291915;

z - 1,3727738.

«

Точное значение функции у 0,91«3702 , z - 1,, Относительная погрешность известного устройства равна

йУ(,р - 0,65-10- ;

10

uznp 0,3-Ю-,

предлагаемого

йу - 0,23 10-

&Z - 0,16-10-г ,

I

Точность вычислений в предлагаемом устройстве в два раза выше. Рассмотрим работу устройства на

примере расчета функций у shx, z chxo Ограничимся четырьмя разрядами (). Нантиса аргумента 0,1101 полается поразрядно на соответствующие.шины входной кодовой комбинации 1,2,3,0 Первый разряд, равный 1, поступает на первые управляющие входы 1,2,3-го коммутаторов, на вторые управляющие входы которых поступают соответственно 1,2,3-й разряды кодовой комбинации,

равные 1,1,0. Первый, второй коммутаторы открываются, а третий остается в закрытом состоянии, на их выходах соответственно устанавливаются коды OJOOO, 0.1010, 0,0000.

С выхода первого коммутатора код 0.1000 поступает на вход третьей разрядной дискреты второго комбинационного сумматора со сдвигом на два разряда П,0010 и одновременно подается на входы разрядной дискреты блоков частичной суммы первой группы. На информационный вход первого блока частичной суммы подана двоичная константа 0.0101, на вход частичной

суммы поступает третий разряд входной кодовой комбинации, равный О, на управляющий вход - первый разряд кодовой комбинации, равный 1. На выходе первого блока частичной суммы

первой группы устанавливается код 0.0010. На информационный вход второго блока частичной суммы первой группы подана константа 0.10CG.

На вход частичной суммы поступает

четвертый разряд входной кодовой комбинации, равный 1, на управляющий вход - второй разряд равный 1. На выходе второго блока частичной суммы первой группы образуется результат

71

1.0100 На информационный вход первого блока частичной суммы третьей группы подана константа О.Л101, на вход частичной суммы поступает код с выхода второго коммутатора, на вход разрядной дискреты поступает второй разряд выходной кодовой комбинации, равный 1, на управляющий вход - первый разряд входной кодовой комбинации, равный 1. На выходе данного блока частичной суммы вырабатывается результат, равный 0.1111. На информационный вход второго блока частичной суммы третьей группы подана константа 0.1000. На вход частичной суммы поступает результат с третьего коммутатора, на управляющий вход и вход разрядной дискреты - второй разряд входной кодовой .комбинации о На выходе блока образуется результат, равный 0„1000.

С выхода первого блока частичной суммы первой группы результат поступает на вход четвертой разрядной дис реты первого комбинационного сумматора со сдвигом на три разряда 0.0000061 и одновременно поступает на вход разрядной дискреты первого блока частичной суммы четвертой группы На информационный вход последнего подана константа 0.0100.,На управляющий вход поступает первый разряд входной кодовой комбинации, на вход частичной суммы - результат с выхода второго блока частичной суммы третьей группы, соответственно, на выходе первого блока частичной суммы четвертой группы образуется результат, равный 0.10000, поступающий далее со сдвигом на четыре разряда на вход пятой разрядной дискреты второго комбинационного сумматора,.

I

Результат с выхода первого блока частичной суммы поступает со сдвигом на три разряда 0.0001111 на вход четвертой разрядной дискреты второго комбинационного сумматора и одновременно на вход разрядной дискреты первого блока частичной суммы второй группы. На входы последнего также поступают: на управляющий - первый разряд входной комбинации, равный 1,0 на информационный - константа 6.0100, частичной суммы - результат с выхода второго блока частичной суммы первой группы. На выходе первого блока частичной суммы второй группы образуется результат 1.0111, поступающий

5

8

на вход пятой разрядной дискреты первого комбинационного сумматора со сдвигом на четыре разряда 0.00010111„ На входы разрядных дискрет первого комбинационного сумматора также поступают : первой - код нуля, второй первый разряд входной кодовой комбинации со сдвигом на один разряд 0,1, третьей - второй разряд входной кодовой комбинации со сдвигом на два разряда 0,01. На выходе первого комбинационного сумматора формируется окончательный результат ,1-1011000.

I

На входы разрядных дискрет второго комбинационного сумматора, кроме указанных, также поступают: первой разрядной дискреты - код единицы 1.0000, второй - код нуля. На его выходе формируется окончательный результат z 1.01000111.

Формула изобретения

Устройство для вычисления гиперболических функций у shx и z f chx, содержащее первый и второй комбинационные сумматоры, отличающее- с я тем, что, с целью повышения

точности, в него введены (п-1)коммутатор (где п - разрядность аргумента) и 2п-4 группы блоков вычисления частичных сумм, причем каждый блок вычисления частичных сумм содержит

входной коммутатор, умножитель и выходной сумматор, вход первого слагаемого которого соединен с выходом умно-, жителя, вход первого сомножителя которого соединен с выходом входного

коммутатора, первые управляющие входы коммутаторов соединены с входом первого разряда аргумента устройства, вторые управляющие входы с первого

по n-й коммутаторов .соединены с вхо- дами соответственно с первого по (п-1)-й разрядов аргумента устройства, информационные входы первого по (п-1)-й коммутаторов соединены с входами констант соответственно 1/2 2/3, о.,(п-1 )/п устройства, выход первого коммутатора соединен с информационными входами входных коммутаторов блоков вычисления частичных сумм первой группы, входы второго слагаемого выходных сумматоров которых соединены соответственно -с. входами с третьего по n-й разрядов аргумента устройства, входы второго сомножителя умножителя k-x блоков

вычисления частичных сумм 1-х и (1+ +П-2)-х групп соединены с входами

констант ГЛТТ устройства (1 1,2,

„„,,n-2; k 1,2, „,,„, п-1-1), управляющие входы входных коммутаторов k-x блоков вычисления частичных сумм 1-й и ()-й групп соединены с входами k-x разрядов аргумента устройства, выходы с второго по (п-1)-й коммутаторов соединены с входами второго слагаемого выходного сумматора соответственно с первого по (п-2)-й блоков вычисления частичных сумм

выходного сумматора первого блока вычисления частичных сумм (8+п-2)-й группы соединен с входом (S+3)-ro слагаемого второго комбинационного 5 сумматора со сдвигом на S+2 разряда вправо и информационными входами входных коммутаторов блоков вычисления частичных сумм (8+1)-й группы, выход выходного сумматора j-ro блока вычисления частичных сумм (8+п-2)-й группы соединен с входом второго слагаемого выходного сумматора (j-l)-ro блока вычисления частичных сумм (S+ +п-1)-й группы, выход выходного сум10

(п-1)-й группы, информационные входы 15 матора первого блока вычисления частичных сумм (2п-4)-й группы соединен

20

входных коммутаторов которых соединены с входом второго разряда аргумента устройства, выход выходного сумматора S-ro блока вычисления частичных сумм.соединен с входом (5+3)-го слагаемого первого комбинационного сумматора со сдвигом на S+2 разряда вправо (S 1,2,..,,п-3) и соединен с информационными входами входных коммута- ,5 ва, влиды в.ири. и ipcibe. и wwi авторов блоков вычисления частичных мых первого комбинационного суммато- сумм (S+n-1)-группы, выход выходного сумматора j-ro блока вычисления частичных сумм S-й группы соединен с входом второго слагаемого выходного сумматора (j-1)-ro блока вычисления частичных сумм (З-И)-й группы, (j 2,3,.,.,п-8-1), выход выходного сумматора первого боока вычисления частичных сумм (п-2)-й группы соедис входом (n-l)-ro слагаемого второго комбинационного сумматора со сдвигом на п разрядов вправо, входы первого слагаемого первого комбинационного сумматора и второго слагаемого второго комбинационного сумматора соединены с входом логического нуля устройства, входы второго и третьего слагаера соединены с входами соответственно первого и второго разрядов аргу- мента устройства со сдвигом соответственно на-один и два разряда вправо, 30 вход первого слагаемого второго комбинационного сумматора соединен с входом логической единицы устройства, выходы первого и второго комбинационных сумматоров соединены с выходами

нен с входом (п-И)-го слагаемого пер- 35 соответственно гиперболического сину- вого комбинационного сумматора со « и гиперболического косинуса устрой- сдвигом на п разрядов вправо, выход

выходного сумматора первого блока вычисления частичных сумм (8+п-2)-й группы соединен с входом (S+3)-ro слагаемого второго комбинационного сумматора со сдвигом на S+2 разряда вправо и информационными входами входных коммутаторов блоков вычисления частичных сумм (8+1)-й группы, выход выходного сумматора j-ro блока вычисления частичных сумм (8+п-2)-й группы соединен с входом второго слагаемого выходного сумматора (j-l)-ro блока вычисления частичных сумм (S+ +п-1)-й группы, выход выходного сум

матора первого блока вычисления частичных сумм (2п-4)-й группы соединен

ва, влиды в.ири. и ipcibe. и wwi авмых первого комбинационного суммато-

с входом (n-l)-ro слагаемого второго комбинационного сумматора со сдвигом на п разрядов вправо, входы первого слагаемого первого комбинационного сумматора и второго слагаемого второго комбинационного сумматора соединены с входом логического нуля устройства, входы второго и третьего слагаева, влиды в.ири. и ipcibe. и wwi авмых первого комбинационного суммато-

ра соединены с входами соответственно первого и второго разрядов аргу- мента устройства со сдвигом соответственно на-один и два разряда вправо, вход первого слагаемого второго комбинационного сумматора соединен с входом логической единицы устройства, выходы первого и второго комбинационГ

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций синуса и косинуса | 1991 |

|

SU1827673A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1315971A1 |

| Устройство для умножения | 1991 |

|

SU1807481A1 |

| Вычислительное устройство | 1988 |

|

SU1532917A1 |

| Цифровой нерекурсивный фильтр | 1989 |

|

SU1665502A1 |

| Устройство для вычисления суммы произведений | 1981 |

|

SU978144A1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| Матричное устройство для решения уравнений в частных производных | 1985 |

|

SU1302276A1 |

| Устройство для умножения | 1981 |

|

SU1018115A1 |

| Устройство для умножения | 1989 |

|

SU1672441A1 |

Изобретение относится к вычислительной технике, в частности к устройствам для выполнения математи-ческих операций в двоичном представлении, и может быть применено в качестве спецпроцессора в комплексе с .вычислительной машиной для оперативного вычисления гиперболических функций у shx и z. chx. Цель изобретения - повышение точности вычислений функций. Работу устройства можно описать, исходя из того, что для функций у chx, z chx справедливы следующие соотношения y(i) . .. j 0 1 ное устройство позволяет вычислить Функции у shx, z chx для двоичного разрядного аргумента за один такт работы схемы с требуемой точностью. Применение его возможно при решении самого широкого круга задач, связанных с моделированием, решением задач в реальном масштабе времени, требующих высокую точность и быстродействие. 3 ил. z(j)x(i - j); z(i) y(j)x(i - j). Предложен9 IB

Вхоо константы о

&хоо частичном

СУММЫ1.

ьхоа разрядной о иск-

УпраЬляюиииы MDg о-

-оЬыхо§

I

фмг. 2

в

ы

7 х о

А

|

фиг. 3

| Ступенчатый шкив для приводных ремней с натяжным роликом | 1928 |

|

SU10261A1 |

| G Об F , 1983 | |||

| Авторское свидетельство СССР Г , кл | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1992-05-23—Публикация

1990-07-09—Подача