1

Изобретение относится к вычислительной технике и- предназначено для вычисления по известньм кодам первой и второй прямоугольных координат измеряемой величины кодов ее полярных координат.

Цель изобретения - повышение быст родействия цифрового преобразователя координат.

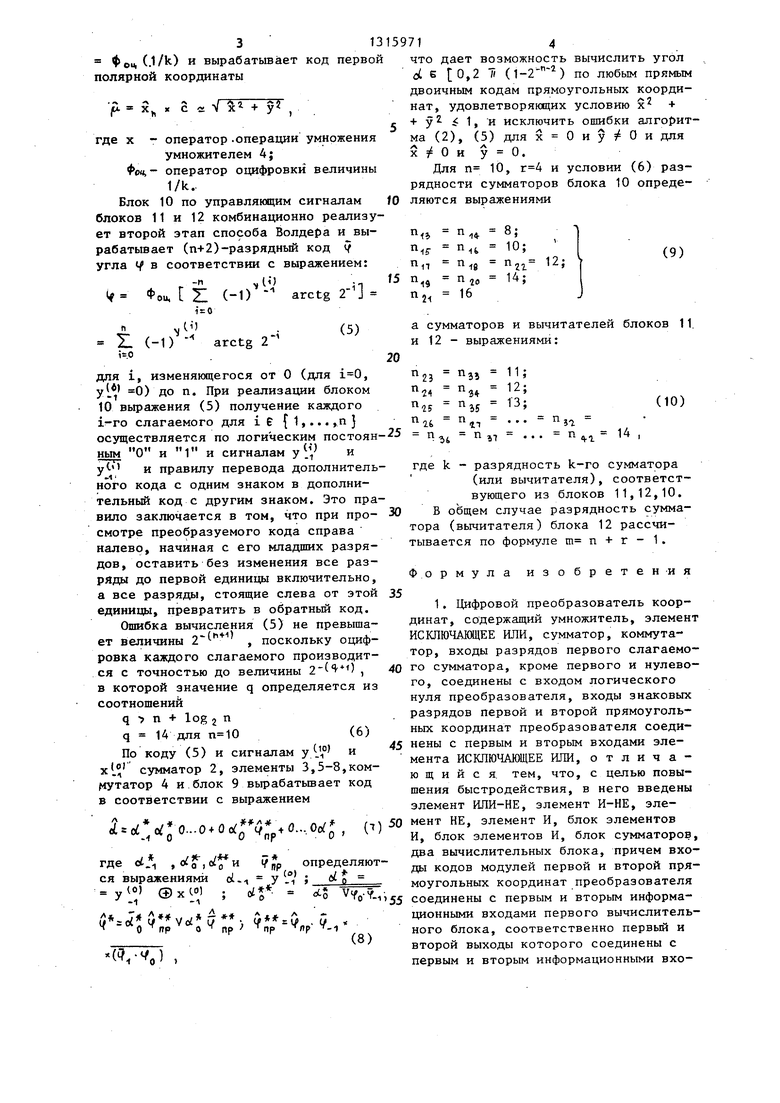

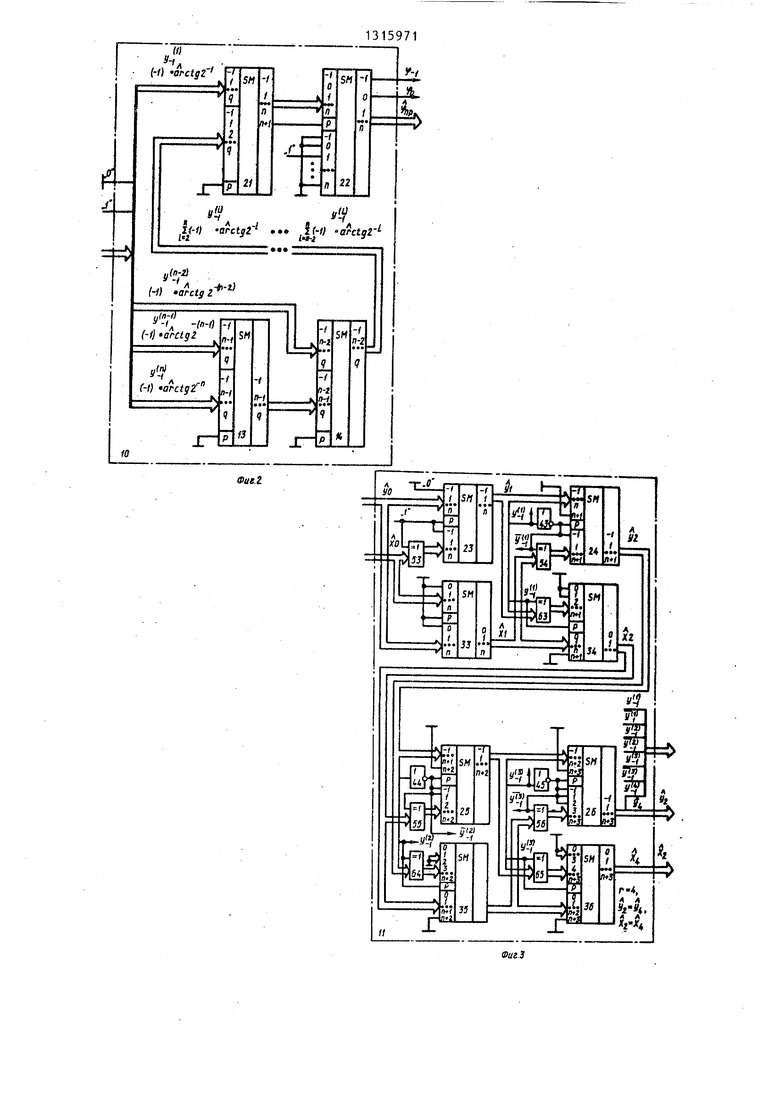

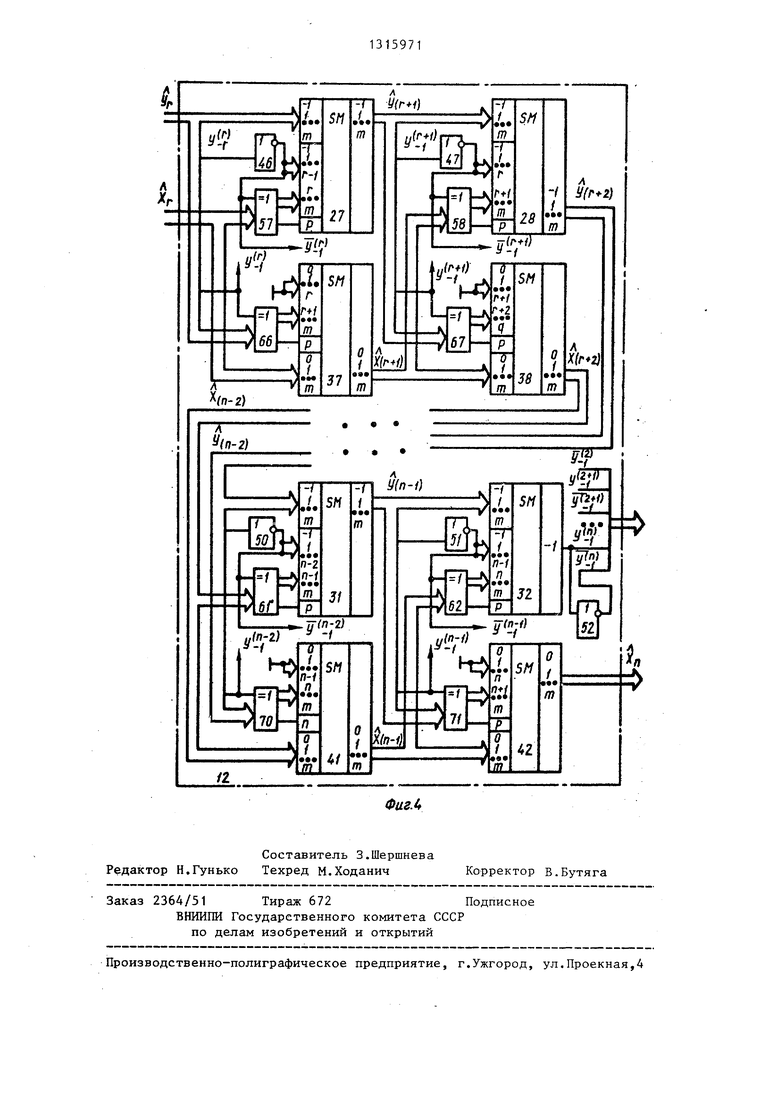

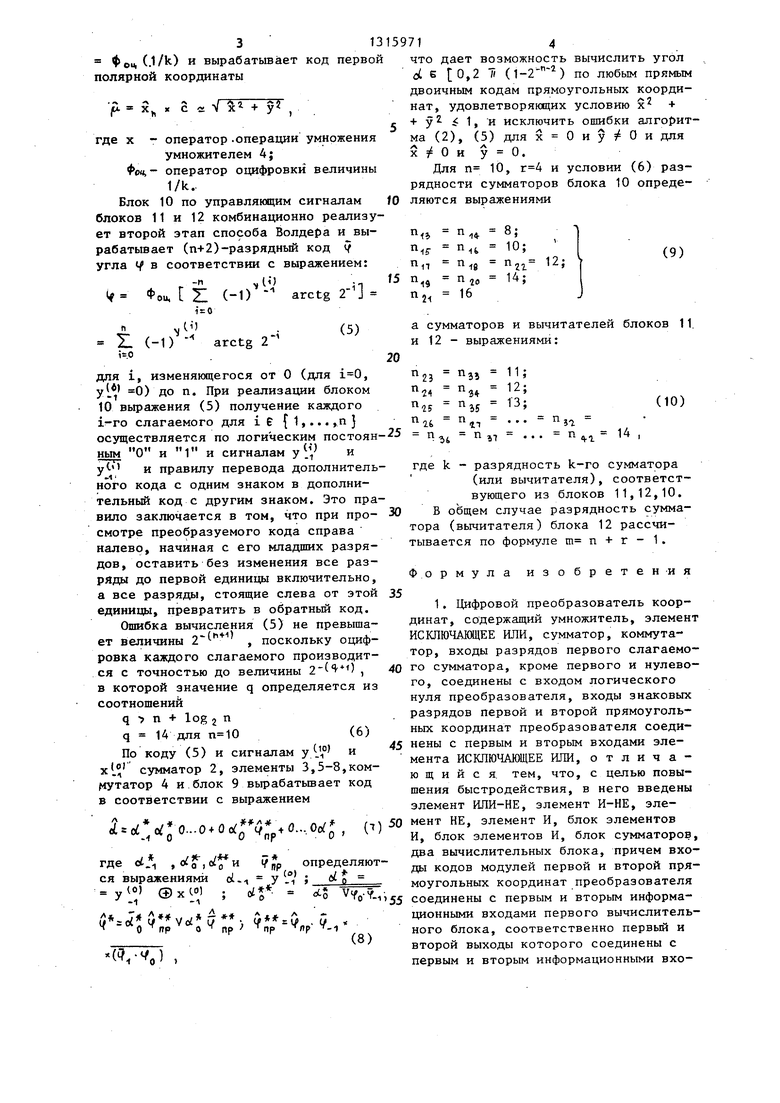

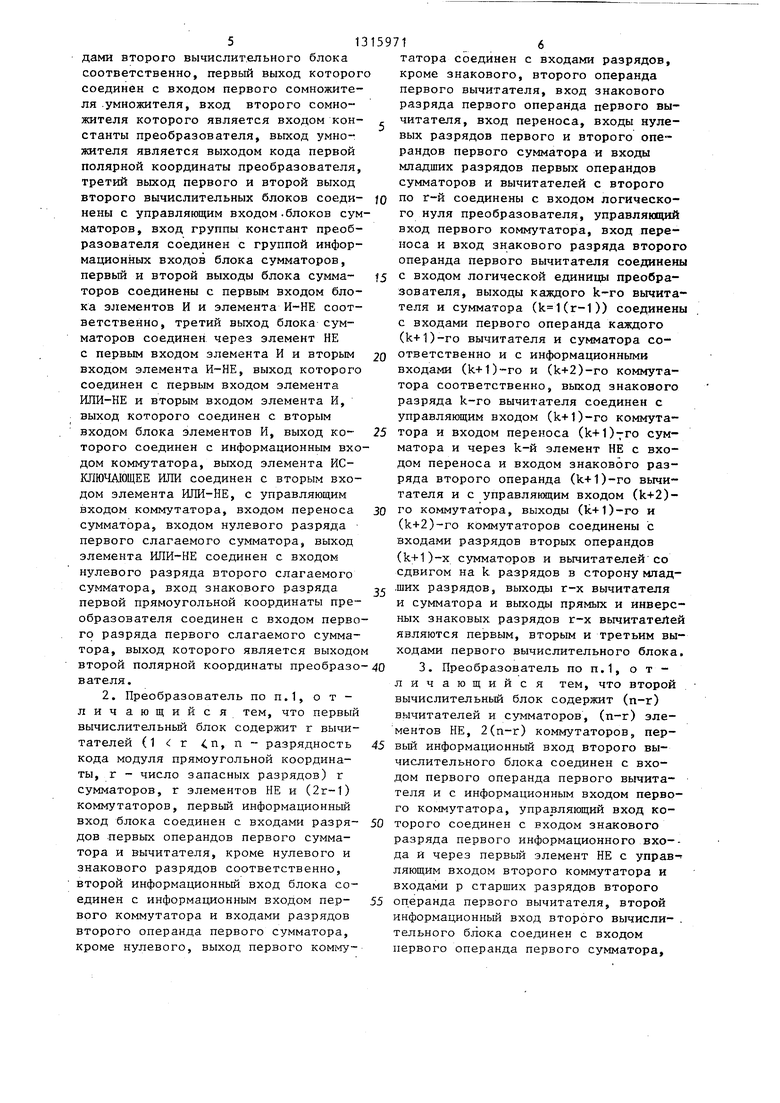

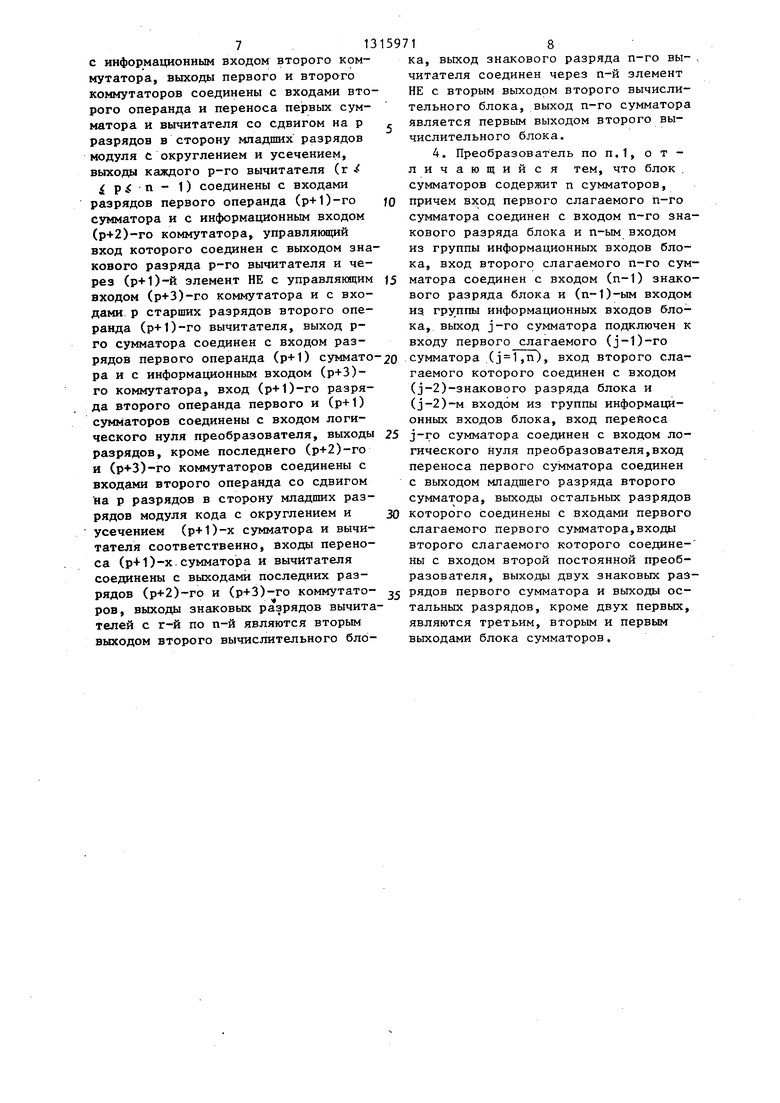

На фиг.1-4 приведена функциональная схема предлагаемого цифрового преобразователя координат (ЦПК),выполненная для и , при заданной точности вычислений.

Преобразователь (фиг.1) содержит умножитель 1, сумматор 2, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 3, коммутатор 4,элемент НЕ 5, элемент ИЛИ-НЕ 6, элемент И-НЕ 7, элемент И 8, блок 9 элементов И, блок 10 сумматоров, и вычисли тельньй блок, образованньй блоком 11 для комбинационной реализации г первых итераций методом Волдера на первом этапе без усечения разрядной сет ки и блоком 12 для комбинационной реализации (п-г) последних итераций методом Волдера на первом этапе с усечением разрядной сетки и с округлением.

Блок 10 сумматоров содержит сумматоров с первого 13 по десятый 22 (фиг. 2).

Вычислительный блок, образованный блоком 11 (фиг. 3) и блоком 12 (фиг. 4), содержит десять вычитате- лей с первого 23 по десятый 32, десять сумматоров с первого 33 по десятый 42, десять инверторов с первого 43 по десятьй 52 и девятнадцать коммутаторов с первого 53 по девятнадцатый 71.

Предлагаемый ЦПК является комбинационным устройством, вычисляющим по (п+1)-разрядным кодам у (-1) У.

П .

х1 2- . у. и X (-1) -V 1, X.,

(где у . и X - разрядные цифры знаковых разрядов кодов у и х первой и второй прямоугольных координат соответственно п-разрядный код

A i2-V;

д

и (п+2)-разрядный код oi , где у. и х.-- разрядная цифра i-ro разряда кода

13159712

X и /С соответственно. Связь между кодом 0 и углом d характеризуется Бьфажениями

г- ,- ,

(1)

.S-.,,-Liu.,,4,,}-.

п л г-

vi;

где d, - может рассматриваться как разрядная цифра знакового разряда дополнительного кода d или как разрядная цифра с весом 2 старшего разряда кода oL d-o - разрядная цифра старшего разряда с весом 2° кода ; d - код приведенного углао р

20

2 пр

С учетом изложенного работу предлагаемого ЦПК можно описать следующим образом.

В установившемся режиме вычисли- 25 тельные блоки 11 и 12 по п-разрядным

кодам Уд (у) и Xg (х) реализуют комбинационно соотношения первого этапа вычислений по способу Волдера:

i(.V

л

X .

л X .

U(-1}

л

У

(2)

35

X:

+ 2- (у.) Л О

для i изменянмцегося от О до (п-1) с начальными условиями у (у), х-

40 (и). При этом выражения (2) выполняются в дополнительном коде для i 0,1,2,3 точно блоком 11, а для i 4,...9 приближенно (с усечением и округлением) блоком 12. В результате

45 блоки 11 и 12 вырабатьшают управляюу , -1 - 1

,(п1 -г,

. W.4 -(

50

х ; . k . 1 х + у

(3)

где k - постоянная преобразования и определяется формулой

55 k (1+2-2 -)

(4)

где П - .символ произведения.

Умножитель производит комбинационное умножение кода Хр на код с

Фоц (.1/l) и вырабатьшает код первой полярной координаты

X с « V Х + у J

оператор.операции умножения

умножителем 4j

оператор оцифровки величины 1/k..

Блок 10 по управляющим сигналам блоков 11 и 12 комбинационно реализует второй этап способа Волдера и вырабатывает (п+2)-разрядный код Q угла (/ в соответствии с выражением:

(i) .- 2-1

Фои, t Z (-1) arctg

n ,C1)

I. (-1) i.0

arctg 2

(5)

для i, изменяющегося от О (для , У 0) до n. При реализации блоком 10 выражения (5) получение каждого i-ro слагаемого для i е {1,...,п } осуществляется по логическим постоян ным О и 1 и сигналам у

уС«

л 1

у ® X (.) ,

;0:jv $

1 S .Y.,

А , , л ч ( . (I пр пр лр -1

(8)

и I и сигналам у :, и и правилу перевода дополнительного кода с одним знаком в дополнительный код с другим знаком. Это правило заключается в том, что при про- смотре преобразуемого кода справа налево, начиная с его младших разрядов, оставить без изменения все разряды до первой единицы включительно, а все разряды, стоящие слева от этой единицы, превратить в обратный код.

Ошибка вычисления (5) не превышает величины 2 , поскольку оцифровка каждого слагаемого производится с точностью до величины ) , в которой значение q определяется из соотношений

q п + log 2 п

q 14 для (6)

По коду (5) и сигналам у 1,° и х Д сумматор 2, элементы 3,5-8,ком- (утатор 4 и блок 9 вьфабатьшает код в соответствии с выражением

ct O...O.,p.O.... , (7)

где oi., ,, ( определяются выражениями о1., у .° ; ai

«(О .J 1 0 I

что дает возможность вычислить угол at Б 0,2 Ji ( ) по любым прямым двоичным кодам прямоугольных координат, удовлетворяющих условию х + 1, и исключить ошибки алгоритма (2), (5) для х для X О и у 0.

Для п 10, и условии (6) разрядности сумматоров блока 10 опреде ляются выражениями

n п

n

14- 1& 18

П 20

16

8;

10; П2 12; 14;

(9)

а сумматоров и вычитателей блоков 11. и 12 - выражениями:

20

n

25

23 24 4s ife

n

3i

11;

n,, 12;

n

3+ 45

ГЗ;

(10)

n

п

ъ.

п

п JT

4-1 п 14

45

,,55

3035

40

50

где k - разрядность k-ro сумматора (или вычитателя), соответствующего из блоков 11,12,10. В общем случае разрядность сумматора (вычитателя) блока 12 рассчитывается по формуле т п + г - 1.

Формула изобретен И я

1. Цифровой преобразователь координат, содержащий умножитель, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, сумматор, коммутатор, входы разрядов первого слагаемого сумматора, кроме первого и нулевого, соединены с входом логического нуля преобразователя, входы знаковых разрядов первой и второй прямоугольных координат преобразователя соединены с первым и вторым входами элемента ИСКПЮЧАЩЕЕ ИЛИ, отличающийся, тем, что, с целью повышения быстродействия, в него введены элемент ИЛИ-НЕ, элемент И-НЕ, элемент НЕ, элемент И, блок элементов И, блок элементов И, блок сумматоров, два вычислительных блока, причем входы кодов модулей первой и второй прямоугольных координат преобразователя соединены с первым и вторым информационными входами первого вычислительного блока, соответственно первый и второй выходы которого соединены с первым и вторым информационными входами второго вычислит.ельного блока соответственно, первый выход которог соединен с входом первого сомножителя .умножителя, вход второго сомножителя которого является входом кон- станты преобразователя, выход умножителя является выходом кода первой полярной координаты преобразователя, третий выход первого и второй выход второго вычислительных блоков соеди- нены с управляющим входом-блоков сумматоров, вход группы констант преобразователя соединен с группой информационных входов блока сумматоров, первый и второй выходы блока сумма- торов соединены с первым входом блока элементов И и элемента И-НЕ соответственно, третий выход блока сумматоров соединен через элемент НЕ) с первым входом элемента И и вторым входом элемента И-НЕ, выход которого соединен с первым входом элемента ИЛИ-НЕ и вторым входом элемента И, выход которого соединен с вторым входом блока элементов И, выход ко- торого соединен с информационным входом коммутатора, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с вторым входом элемента ИЛИ-НЕ, с управляющим входом коммутатора, входом переноса сумматора, входом нулевого разряда первого слагаемого сумматора, выход элемента ИЛИ-НЕ соединен с входом нулевого разряда второго слагаемого сумматора, вход знакового разряда первой прямоугольной координаты преобразователя соединен с входом первого разряда первого слагаемого сумматора, выход которого является выходо второй полярной координаты преобразо вателя,

2. Преобразователь по п.1, о т - личающийся тем, что первый вычислительный блок содержит г вычи- тателей (1 г п, п - разрядность кода модуля прямоугольной координаты, г - число запасных разрядов) г сумматоров, г элементов НЕ и (2г-1) коммутаторов, первый информационный вход блока соединен с входами разря- дов первых операндов первого сумматора и вычитателя, кроме нулевого и знакового разрядов соответственно, второй информационный вход блока соединен с информационным входом пер- вого коммутатора и входами разрядов второго операнда первого сумматора, кроме нулевого, выход первого коммутатора соединен с входами разрядов, кроме знакового, второго операнда первого вычитателя, вход знакового разряда первого операнда первого вычитателя, вход переноса, входы нулевых разрядов первого и второго операндов первого сумматора и входы младших разрядов первых операндов сумматоров и вычитателей с второго по г-й соединены с входом логического нуля преобразователя, управляющий вход первого коммутатора, вход переноса и вход знакового разряда второг операнда первого вычитателя соединен с входом логической единицы преобразователя, выходы каждого k-ro вычитателя и сумматора ((r-1)) соединен с входами первого операнда каждого (k+1)-ro вычитателя и сумматора соответственно и с информационными входами (k+1)-ro и (k+2)-ro коммутатора соответственно, выход знакового разряда k-ro вычитателя соединен с управляющим входом (k+1)-ro коммутатора и входом переноса ( сумматора и через k-й элемент НЕ с входом переноса и входом знакового разряда второго операнда (k+1)-ro вычитателя и с управляющим входом ()- го коммутатора, выходы (k+l)-ro и (k+2)-ro коммутаторов соединены с входами разрядов вторых операндов

(k+1)-x сумматоров и вычитателей со сдвигом на k разрядов в сторону млад- ,ших разрядов, выходы г-х вычитателя и сумматора и выходы прямых и инверсных знаковых разрядов г-х вьтитатеЛе являются первым, вторым и третьим выходами первого вычислительного блока

3. Преобразователь по п.1, о т - личающийся тем, что второй вычислительный блок содержит (п-г) вычитателей и сумматоров, (п-г) элементов НЕ, 2(п-г) коммутаторов, пер- вьй информационный вход второго вычислительного блока соединен с входом первого операнда первого вычитателя и с информационным входом первого коммутатора, управляющий вход которого соединен с входом знакового разряда первого информационного вхо- да и через первьш элемент НЕ с управляющим входом второго коммутатора и входами р старших разрядов второго операнда первого вычитателя, второй информационный вход второго вычисли- тельного блока соединен с входом первого операнда первого сумматора.

713

с информационным входом второго коммутатора, выходы первого и второго коммутаторов соединены с входами второго операнда и переноса первых сумматора и вычитателя со сдвигом на р разрядов в сторону младших разрядов модуля с округлением и усечением, выходы каждого р-го вычитателя (г

р п - 1) соединены с входами разрядов первого операнда (р+1)-го сумматора и с информационным входом (р+2)-го коммутатора, управлянмций вход которого соединен с выходом знакового разряда р-го вычитателя и через (р+1)-й элемент НЕ с управляющим входом (р+3)-го коммутатора и с входами р старших разрядов второго операнда (р+1)-го вычитателя, выход р- го сумматора соединен с входом разрядов первого операнда (р+1) сумматора и с информационньм входом (р+3)- го коммутатора, вход (р+1)-го разряда второго операнда первого и (р+1) сумматоров соединены с входом логического нуля преобразователя, выходы разрядов, кроме последнего (р+2)-го и (р+3)-го коммутаторов соединены с входами второго операнда со сдвигом на р разрядов в сторону младших разрядов модуля кода с округлением и усечением (р+1)-х сумматора и вычитателя соответственно, входы переноса (р-И)-х, суммато)ра и вычитателя соединены с выходами последних разрядов (р+2)-го и (р+3)-го коммутаторов, выходы знаковых разрядов вычита- телей с г-й по п-й являются вторым выходом второго вычислительного бло18

ка, выход знакового разряда п-го вы- . читателя соединен через п-й элемент НЕ с вторым выходом второго вычислительного блока, выход п-го сумматора является первым выходом второго вычислительного блока.

4, Преобразователь по п.1, отличающийся тем, что блок сумматоров содержит п сумматоров,

причем вход первого слагаемого п-го сумматора соединен с входом п-го знакового разряда блока и п-ым входом из группы информационных входов блока, вход второго слагаемого п-го сумматора соединен с входом (п-1) знакового разряда блока и (п-1)-ым входом из группы информационных входов блока, выход j-ro сумматора подключен к входу первого слагаемого (j-l)-ro

сумматора (,п), вход второго слагаемого которого соединен с входом (j-2)-3HaKOBoro разряда блока и (j-2)-м входом из группы информационных входов блока, вход перейоса

j-ro сумматора соединен с входом логического нуля преобразователя,вход переноса первого сумматора соединен с выходом младшего разряда второго сумматора, выходы остальных разрядов

которого соединены с входами первого слагаемого первого сумматора,входы второго слагаемого которого соедине- ны с входом второй постоянной преобразователя, выходы двух знаковых разрядов первого сумматора и выходы остальных разрядов, кроме двух Первых, являются третьим, вторым и первым выходами блока сумматоров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой преобразователь тригонометрических функций | 1986 |

|

SU1327094A1 |

| Устройство для умножения с накоплением | 1986 |

|

SU1310810A1 |

| Вычислительное устройство | 1985 |

|

SU1278840A1 |

| Матричный преобразователь координат | 1988 |

|

SU1559343A1 |

| Устройство для поворота вектора | 1983 |

|

SU1144104A1 |

| Конвейерное вычислительное устройство | 1987 |

|

SU1432512A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Конвейерное устройство для деления | 1985 |

|

SU1297037A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1290307A1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

Изобретение относится к вычислительной технике и предназначено для вычисления по известным кодам первой и второй прямоугольных координат измеряемой величины кодов первой и второй ее полярных координат. Цель изобy- f. ретения - повышение быстродействия цифрового преобразователя координат. Преобразователь содержит умножитель 1, сумматор 2, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 3 и коммутатор 4. Новым в преобразователе является то, что он содержит элемент НЕ 5, элемент ИЛИ-НЕ 6, элемент И 8, блок элементов И 9,блок сумматоров 10 и два вычислительных блока 11, 12, причем блок сумматоров состоит из п сумматоров, первый вы- числит,ельной блок содержит г вычита- телей, г сумматоров, г элементов НЕ и 2г-1 коммутаторов, второй вычислительный блок содержит п-г вычитате- лей .и сумматоров, п-г элементов НЕ, 2(п-г-1) коммутаторов 1 ; г п. 4 ил. 2., о « (Л с Со СП со X. ь

| Цифровой преобразователь координат | 1981 |

|

SU960834A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Синусно-косинусный преобразователь | 1981 |

|

SU1005040A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-06-07—Публикация

1985-07-16—Подача