Изобретение относится к цифровой вычислительной технике и может быть использовано при построении специализированных вычислительных устройств.

Известно устройство для вычисления суммы произведений, содержащее регистры множимого и множителя,сумматор и матрицу модулей, выход которой соединен с входом сумматора, а входы подключены к выходам регистров Г1 .

Недостатком этого устройства является большое количество оборудования и,- кроме того, данное устройство предназначено для вычисления суммы произведений только положительных чисел.

Известно устройство для вычисления суммы произведений, содержащее четыре сумматора, регистрдл суммы и разности/ блоки вычисления произведений, блоки формирования и хранения признаков,два многовходовых сумматора, регистры задержки. Это устройство работает в избыточной двоичной системе счисления и выдает результаты вычисления последовательным кодом, |Начиная с старшего разряда, непосредственно в процессе вычисления.

что обеспечивает его высокое быстродействие 2.

Однако техническая реализация устройства требует больших аппаратурных затрат.

Наиболее близким к предлагаемому является устройство для вычисления суммы произведений, содержащее первый

10 и второй сумматоры, входы которых являются входами соответственно первого и второго множимых устройства, а выходы подключены к входам соответственно регистра суммы и регистра раз15ности, первый и второй регистры множителей, входы которых являются входами соответственно первого.и второго множителей устройства, а выходы подключены к управляющим входам бло20ка коммутаторов, информационные входы которого подключены к выходам регистров суммы и разности, а выходы к первой группе входов многовходового сумматора, второй вход которого под25ключен к старшему разряду регистра хранения результата, а выход - к входу младшего разряда регистра хранения результата. Это устройство работает в избыточной двоичной системе

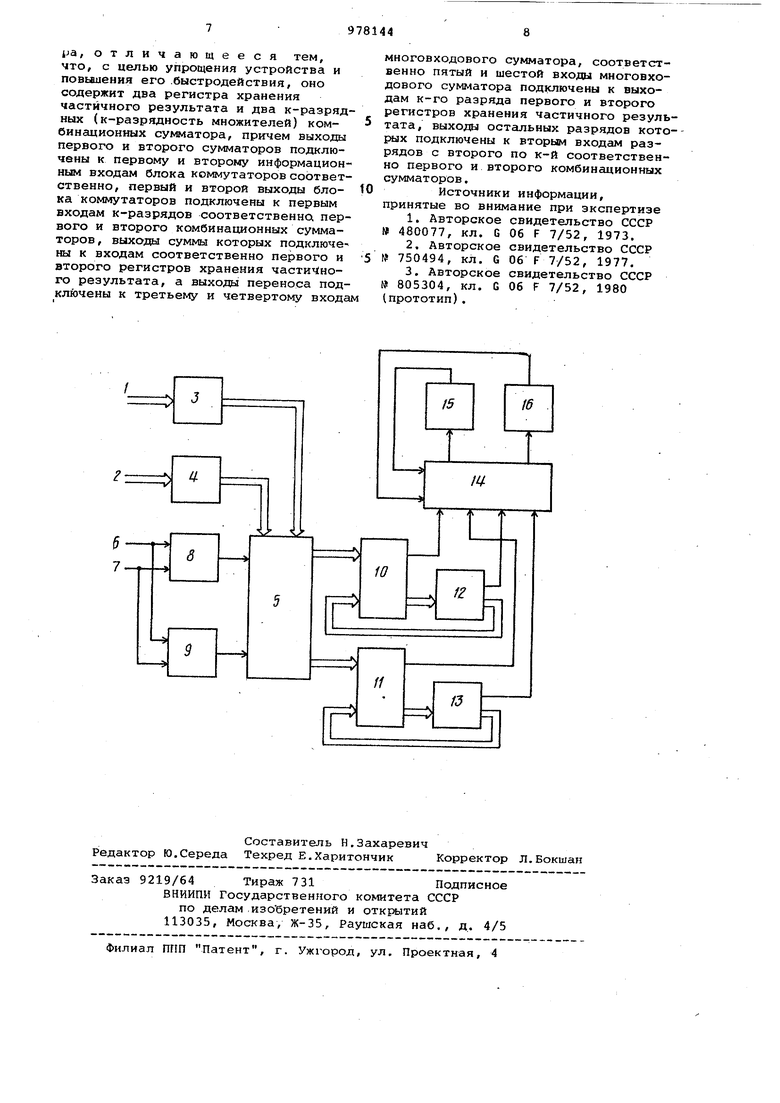

30 счисления и выдает результаты вычисления последовательным кодом, начин со старшего разряда f3J. Недостатком данного устройства я ляется большое количество оборудова ния и недостаточное быстродействие. Цель изобретения - упрощение уст ройства и повышение его быстродейст вия. Указанная цель достигается тем, что устройство для вычисления суммы произведений, содержащее первый и „второй .сумматоры, первый и второй входы которых подключены соответ;ственно к шинам первого и второго мно жимых устройства, блок коммутаторов .первый и второй регистры множителей входы которых подключены к шинам соответственно первого и второго множителей, устройства, а выходы под ключены соответственно к первому и второму управляющим входам блока коммутаторов, два регистра сдвига и многовходовой сумматор, первый и второй входы которого соответственно соединены с выходами старшего разряда первого и второго регистров dдвйгa, входь младшего разряда которых подключены к выходам многовходового сумматора, содержит два регистра хранения частичного результата и два к-разрядных (к-разрядность мно жителей) комбинационных сумматора, причем выходы первого и второго сумматоров подключены к первому и второ му информационным входам блока коммутатроов соответственно, первый и второй выходы блока коммутаторов подключены к первым входам к разрядов соответственно первого и второго комбинационных сумматоров, выходы суммы которых подключены к входам соответственно первого и второго регистров хранения частичного результата, а выходы переноса подключены к третьему и четвертому входам много входового сумматора, соответственно пятый и шестой входы многовходового сумматора подключены к выходам к-го разряда первого и второго регистров хранения частичного результата, выходы остальных разрядов которых подключены к вторым входам разрядов с второго по к-ый соответственно первого и второго комбинационных сумматоров. На чертеже представлена структурная схема предлагаемого устройства для вычисления суммы произведений. Устройство содержит шины 1 и 2 первого и второго множителей, первый и второй регистры 3 и 4 множителей, блок 5 коммутаторов, шины 6 и 7 первого и второго множимых, первый и второй сумматоры 8 и 9, первый и вто рой к-разрядные комбинационные сумматоры 10 и 11, первый и второй регистры 12 и 13 хранения частичного результата, многовходовой сумматор 14, первый и второй регистры 15 и 16 сдвига . Шины 1 и 2 первого и второго множителей устройства подключены к входам регистров 3 и 4 множителей, выходы которых подключены к управляющим входам блока 5, коммутаторов.Шины б и 7 первого и второго множи1«их устройства подключены к входам сумматоров 8 и 9, выходы которых соедит нены с информационными входами блока 5 коммутаторов. Первая и вторая группы, выходов блока 5 коммутаторов соединены с первыми входами разрядов соответственно первого и второго / к-разрядных комбинационных сумматоров 10 и 11, выходы суммы которых подключены к входам разрядов соответственно первого и второго регистров 12 и 13 хранения частич.ного результата, а выходы переноса подключены к третьему и четвертому- входам многовхбдового сумматора 14, первый и второй входы которого соединены с выходами старшего разряда первого и второго регистров 15 и 16 сдвига соответственно,- входы младшего разряда которых подключены к соответствующим выходам многовходового сумматора 14, .пятый и шестой входы которого подключены к выходам к-го разряда первого и второго регистров 12 и 13 хранения частичного результата, выходы остальных разрядов которых подключены к вторым входс1М разрядов с второго по к-ый соответственно первого и второго комбинационных сумматоров 10 и 11. Вычисление суммы лроизвед ений в каждом цикле производится по следующей формуле Z АС + ВО, где А и Б - множимые, выраженные цифрами 1,0 и 1 избыточной двоичной системы; С и D - множители, выраженные цифрами Т и 1 (цифра Т означает О в двоичной системе). Так как каждый разряд множителей может принимать только значения I или 1, то текущая -сумма произведений Z может быть получена путем формирования суммы или разности множимых + 8и R A-B Значения множителей параллельным кодом подаются по шинам 1 и 2 .первого и второго множителей устройства и заносятся в регистры 3 и 4 множителей. Значения первого и второго множимых подаются поразрядно, начиная с старшего разряда,по шинам 6 и 7 первого и второго множимых устройства в сумматоры 8 и 9, которые работают в избыточной двоичной системе счисления. B сумматоре8 образуется сумма S множи a X,aв сумматоре 9 образуется раз- ность R множимых. В каждом такте работы устройства на информационные входы блока 5 коммутаторов подаются текущие значения суммы S и разности R{ множимых.I

В соответствии со значениями J--ro U - 1,2,. ..,k), разряда мно ситёлей Cj и DJ .поступающих с выходов j-ro

разряда регистров множителей 3 и 4 на управляющие входы блока 5 коммутаторов, на положительный и отрицательный выходы J-ro коммутатора вьщаетсц суАвиа Sj или разность Rj i-ro разря-. да множимых А и В.

Принцип работы j-ro коммутатора .блока 5 поясняет таблица.

.L.:n........r.i-...

т 7 s S

Так как значения суммы и разности множимых подаются на информационные . входы блока 5 KON yTaTopoB по положительным ( R) и отрицательньм (S и R) шинам, то отрицательные значения и разности множимых получаем путем взаимной перестановки положительных и отрицательных шии на входах коммутаторов.

Полученные на выходах коммутаторов блока 5 значения Z соответствуют сумме произведений i-ro разряда множимых А и В на к разрядов множителей Си D, т.е. Zj + BiD. Получен№лР1 частичный результат суммы произведений подается на первые входы разрядов, к-разрядных комбинационных сумматоров 10 и 11, на вторые входы которых подается значение частичного результата без двух старших разрядов к-го и (k+1)-ro, полученное в предыдущем 11-1)-м такте с выходов (k-l) младших разрядов регистЕ ов 12 и 13 хранения частичного результата. При этом в комбинационном сумматоре 10 суммируются только положительные значения частичного результата, а в комбинационном сумматоре 11 - только отрицательные.

Значения полученного результата с выходов сумм комбинационных cyNwaторов записываются в регистры 12 и 13, а значения старшего {k+l)-ro разряда полученного результата с вЫ-, ходов, переноса этих сумматоров подаются на третий и четвертый входаа многовходового сумматора 14, на пятый и шестой входы которого одновременно поступают значения к-го разряда результата предыдущего U-l)-ro такта работы устройства с выходов к-го разряда регистров 12 и 13 хранения частичного результата..На первую пару входов многовходового сумматора,

который работает в избыточной двоичной системе счисления,с выходов старшего разряда регистров 15 и 16 сдвига подается значение 1-го разряда суМмы произведений, накопленное в регистрах

0 15 и 16 в предыдущих циклах вычисления.

Полученное в рассматриваемом цикле значение суммы произведений подается последовательным кодом, начиная со старшего разряда, с выходов многовходового сумматора 14 на входы младшего разряда регистров 15 и 16 сдвига, в которых от цикла к циклу накапливается результат вычисления.

Q Введение комбинационных сумматоров позволяет упростить предлагаемое устройство, так как по аппаратурным затратам они в совокупности с многовходовым сумматором (в данндм

5 случае на шесть входов) требуют меньших аппаратурных затрат, чем многовходовой сумматор в известном устройстве на к входов, причем выигрыш в оборудовании пропорционален к, т.е.

Q количеству разрядов множителей.

Кроме того, задержка прохождения ин- формации в многовходовом сумматоре на к входов больше, чем в известном устройстве, т.е.имеет место увеличение быстродействия.

5

Результат вычисления может выводиться из регистров 15 и 16 в каждом дикЛе параллельным или последовательным кодом. При последовательном выводе результата в каждом цикле (или.

после N циклов) вычисления, он может {выдаваться с выходов многовходового сумматора 14 во время цикла вычисления.

45

Формула изобретения

Устройство для вычисления суммы произведений, содержащее первый и второй сумматоры, первый и второй входы которого подключены соответственно к шинам первого и второго множимых устройства, блок коммутаторов, первый и второй регистры множителей, входы которых подключены к шинам соответственно первого и второго множителей устройства, а выходы подключены соответственно к первому и второму управляющим входам блока коммутаторов, два регистра сдвига и многовходовой сумматор, первый и второй входы которого соответственно соединены с выходами старшего разряда первого и второго регистров сдвига, входы младшего разряда которых подключены к выходам многовходового сумматоtja, отличающееся тем, что, с целью упрощения устройства и повыаения его .быстродействия, оно содержит два регистра хранения частичного результата и два к-разрядных (к-разрядность множителей) комбинационных сумматора, причем выходы первого и второго сумматоров подключены к первому и второму информационным входам блока коммутаторов соответственно, первый и второй выходы блока коммутаторов подключены к первым входам к-разрядов соответственна первого и второго комбинационных сумматоров , выходы суммы которых подключен ны к входам соответственно первого и второго регистров хранения частичного результата, а выходы переноса подключены к третьему и четвертому входа многовходового сумматора, соответственно пятый и шестой входы многовходового сумматора подключены к выходам к-го разряда первого и второго регистров хранения частичного результата, выходы остальных разрядов которых подключены к вторым входам разрядов с второго по к-й соответственно первого и второго комбинационных сумматоров. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 480077, кл. G 06 F 7/52, 1973. 2.Авторское свидетельство СССР № 750494, кл. G Об F 7/52, 1977. 3.Авторское свидетельство СССР № 805304, кл. G 06 F 7/52, 1980 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления сумм произведений | 1982 |

|

SU1020818A1 |

| Устройство для вычисления сумм произведений | 1978 |

|

SU805304A1 |

| Устройство для умножения | 1981 |

|

SU1024906A1 |

| Вычислительное устройство | 1981 |

|

SU997030A1 |

| Устройство для умножения | 1981 |

|

SU999043A1 |

| Устройство для умножения | 1982 |

|

SU1059566A1 |

| Накапливающий перемножитель | 1981 |

|

SU987618A1 |

| Устройство для умножения | 1991 |

|

SU1807481A1 |

| Устройство для вычисления матрицы направляющих косинусов | 1983 |

|

SU1233142A1 |

| Устройство для умножения | 1981 |

|

SU1018115A1 |

Авторы

Даты

1982-11-30—Публикация

1981-06-05—Подача