Изобретение относится к цифровым вычислительным машинам, в частности к устройствам для выполнения математических операций в двоичном представлении, и может быть использовано в любой отрасли народного хозяйства, где необходима реализация вычислительного процесса в реальном масштабе времени, например, для исследования быстроизменяющихся процессов, протекающих в сложных динамических объектах

Цель изобретения - повышение точности вычисления функций,

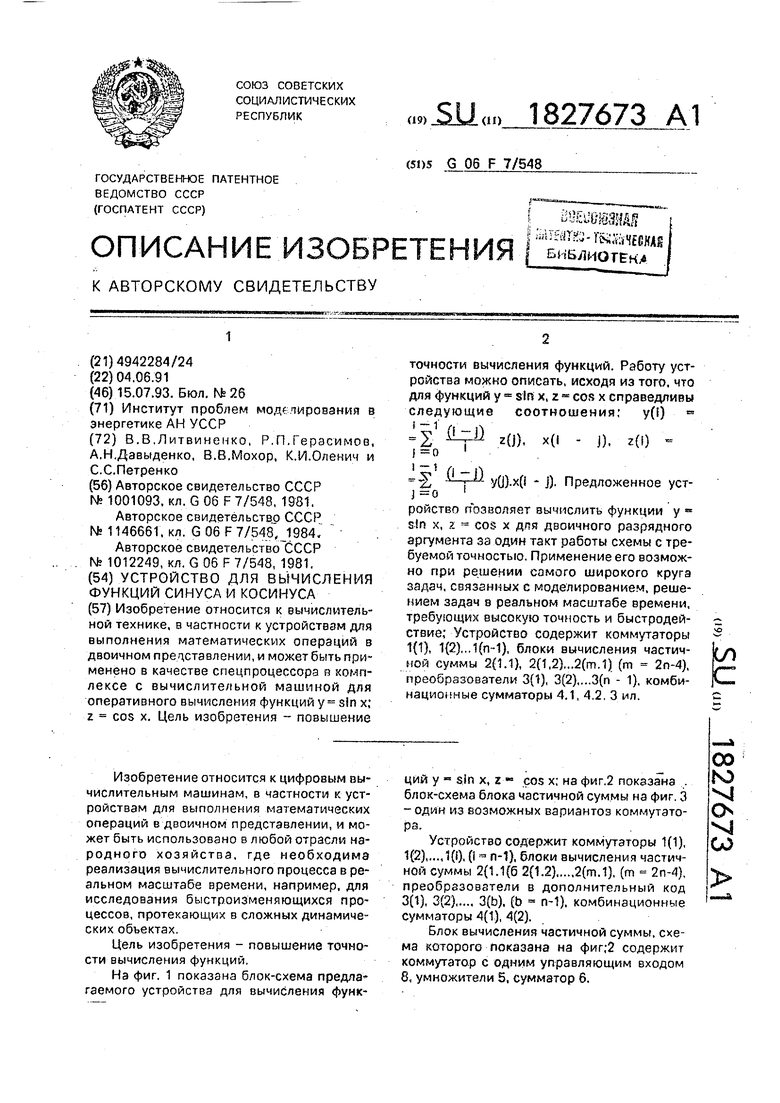

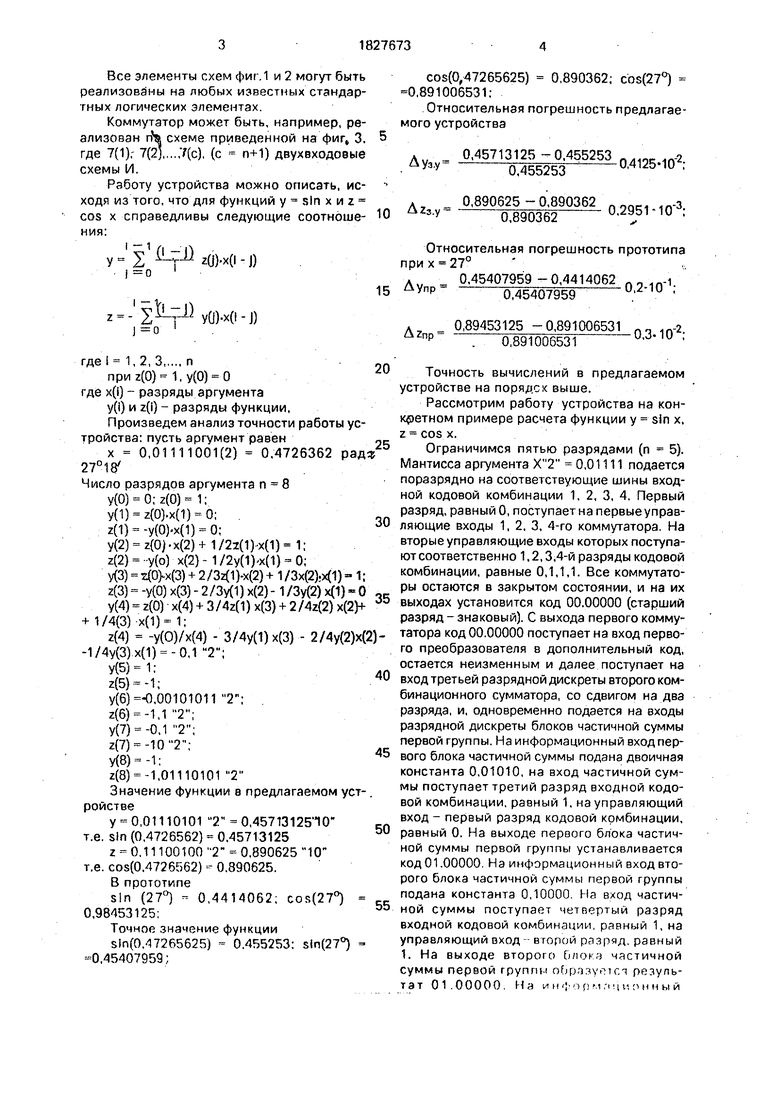

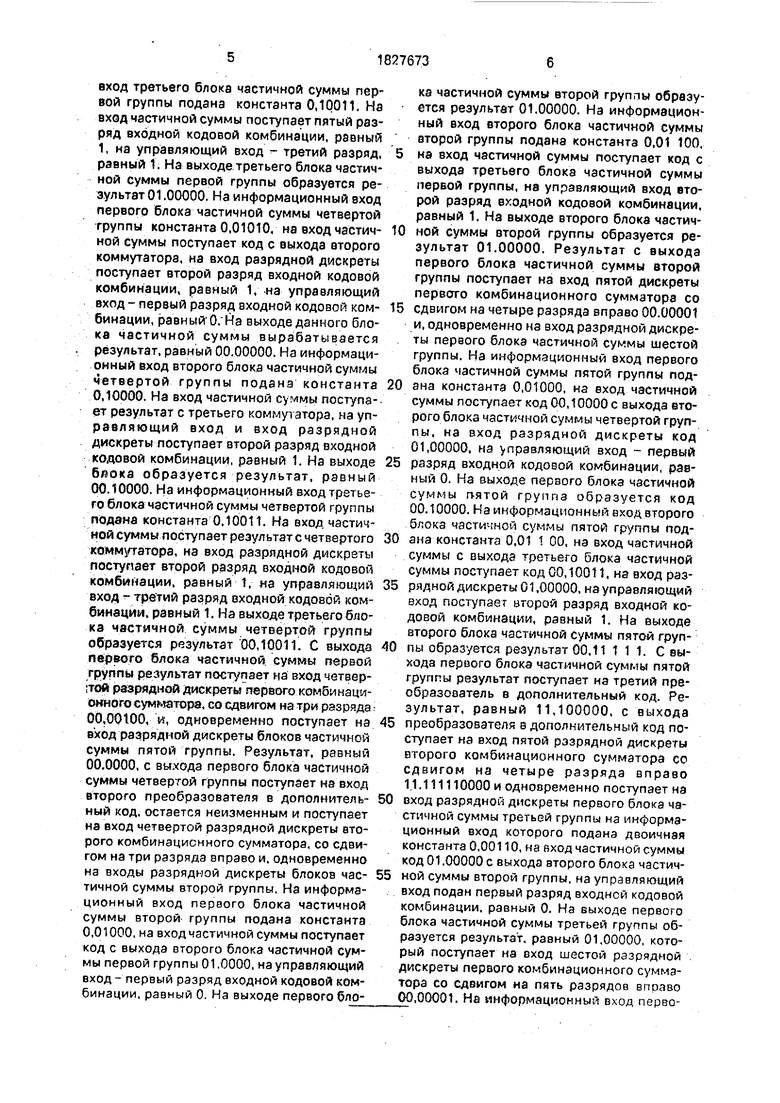

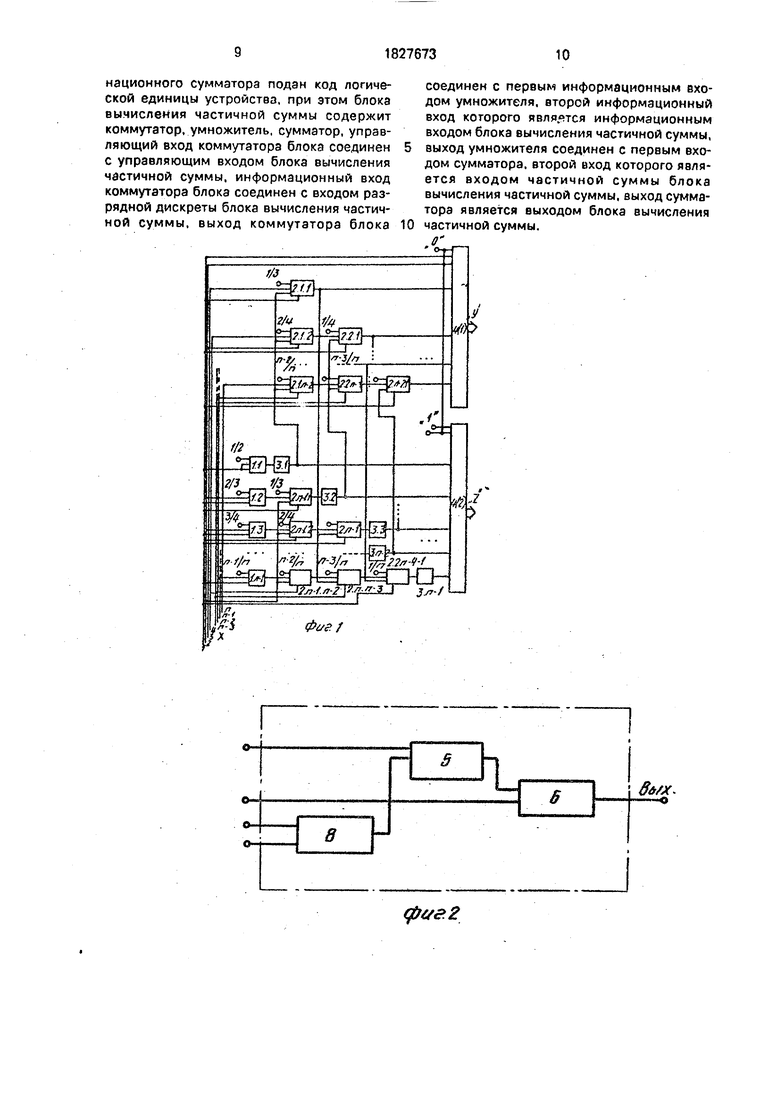

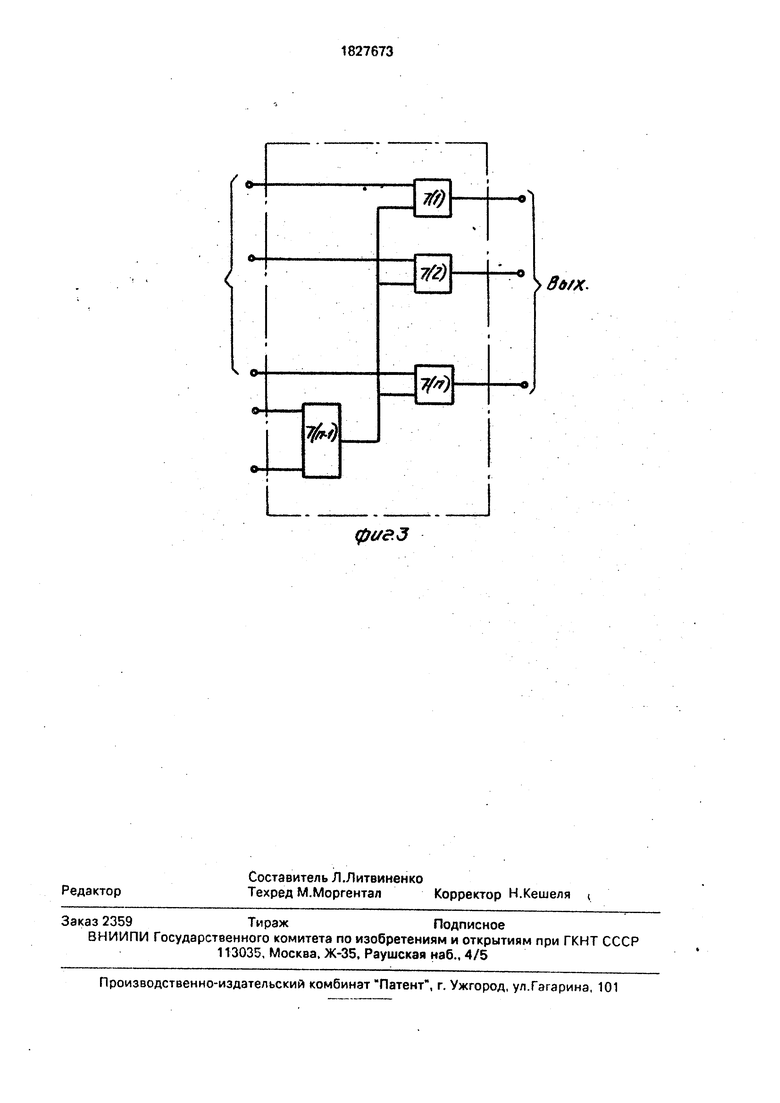

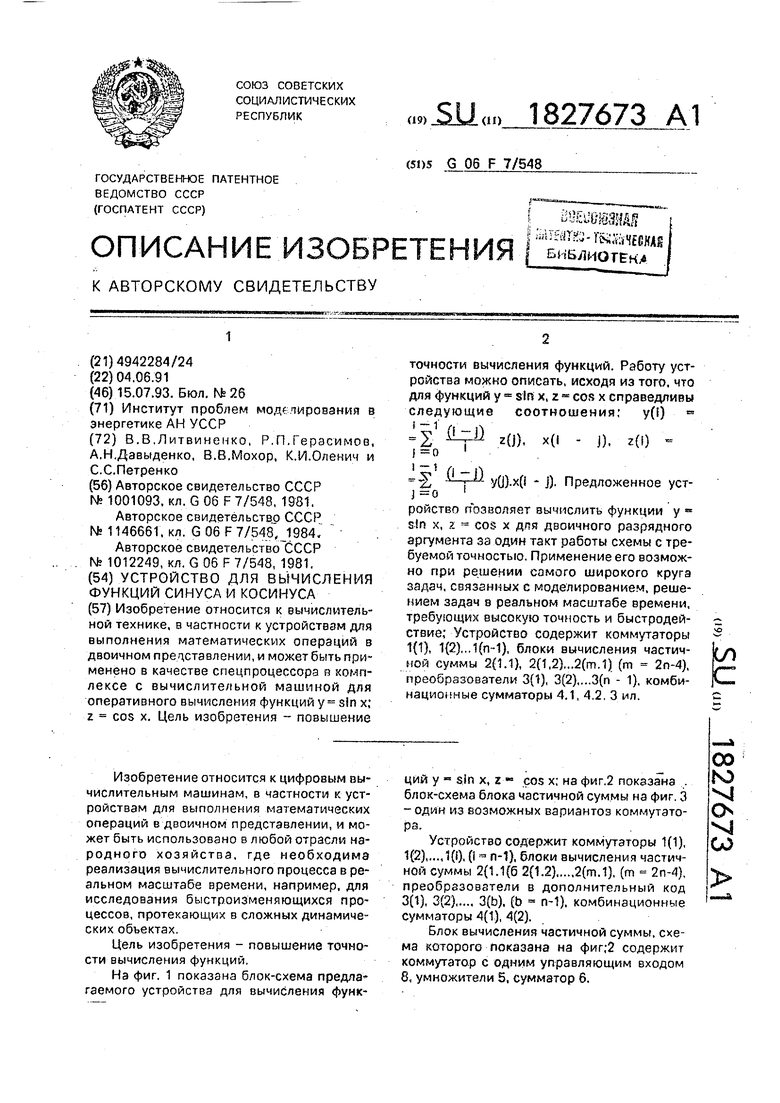

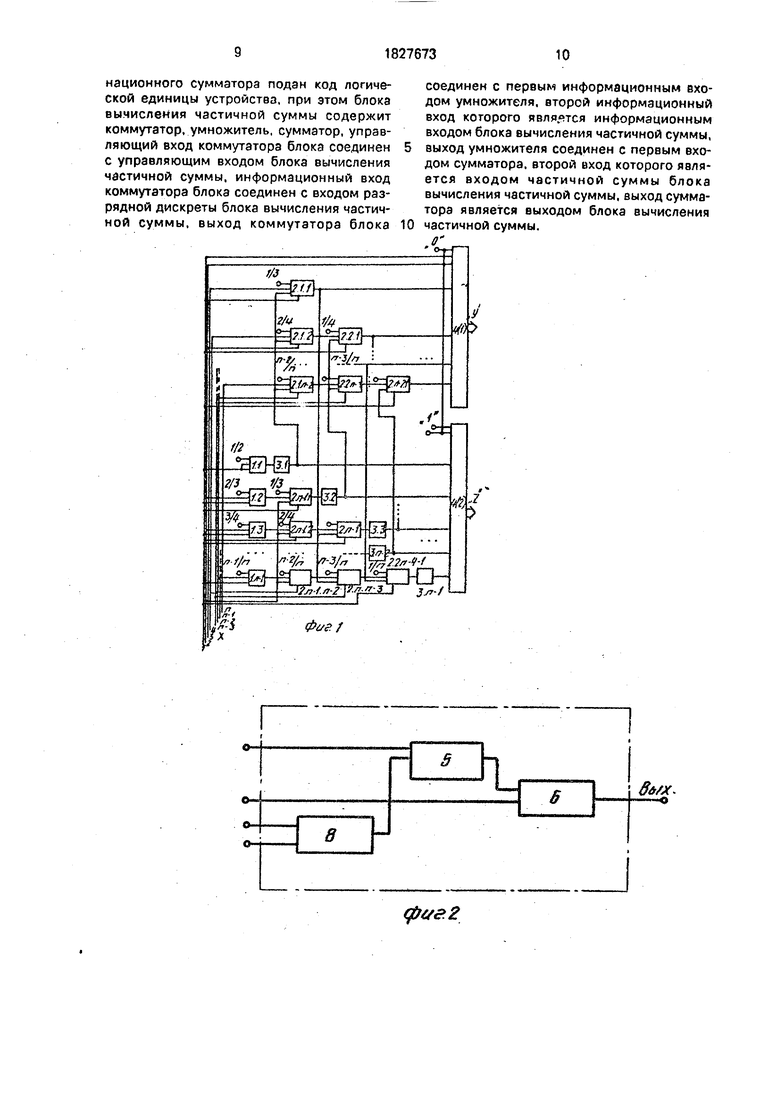

На фиг. 1 показана блок-схема предяа гаемого устройства для вычисления функций у sin x, z cos x; на фиг 2 показана блок-схема блока частичной суммы на фиг 3 -один из возможных вариантов коммутатора.

Устройство содержит коммутаторы 1(1), 1(2)1(1), (1 п-1), блоки вычисления частичной суммы 2(1.1(6 2(1.2)2(m.1). (m 2n-4).

преобразователи в дополнительный код

3(1), 3(2) 3(Ь). (Ь п-1). комбинационные

сумматоры 4(1), 4(2).

Блок вычисления частичной суммы, схема которого показана на фиг;2 содержит коммутатор с одним управляющим входом 8, умножители 5, сумматор 6.

00

К)

VI о ч

СА

Все элементы схем фиг.1 и 2 могут быть реализованы на любых известных стандартных логических элементах.

Коммутатор может быть, например, реализован rta схеме приведенной на фиг, 3, где 7(1),- 7(2j,...,7(c), (с п+1) двухвходовые схемы И.

Работу устройства можно описать, исходя из того, что для функций у sin х и z cos x справедливы следующие соотношения:

У- Ё1 zO)-x(l-J)

1М

vO)-x(i-J)

0

где 1,2,3п

приг(0) 1,у(0) 0 где x(i) - разряды аргумента y(i) и z(i) - разряды функции, Произведем анализ точности работы устройства: пусть аргумент равен

х 0,01111001(2) 0,4726362 радз 27о18/

Число разрядов аргумента п 8

у(0) 0; z(0) 1;

у(1) z(0).x(1) 0;

z(1) -y(0)-x(1) 0;

у(2) z(0)-x(2) + 1/2z(1)-x(1) - 1;

z(2) у(о) х(2}-1/2у(1)-х(1)-0;

у(3) ((3) + 2 /3z(1).x(2) + 1 /Зх(2);х(1) - 1 ;

z(3)- -у(0) х(3) - 2/Зу(1) х(2)-1 /Зу(2) х(1)-0 y(4) z(0) x(4) + 3/4z(1)x(3) + 2/4z{2)x(2)+ + 1/4(3) х(1)- 1;

z{4) -у(0)/х(4) - 3/4у(1)х(3) - 2/4у(2)х(2 -1/4у(3)х(1) -0,1

У(5)1:

2(5)--1:

у(6) -0,00101011

z(6) -1,1

у(7) -0,

z(7)

у(8)--1:

z(8) -1.01110101 2

Значение функции в предлагаемом устройстве

у 0,01110101 2 0,457131254 О т.е. sin (0,4726562) - 0.45713125

z 0,11100100 2 0.890625 10 т.е. cos(0.4726562) - 0.890625.

В прототипе

sin (27°) -- 0,4414062; cos(27°) 0,98453125:

Точное значение функции

sin(0.-17265625) - 0.455253: sin(27°) - -0,45407959;

cos(0,47265625) 0,890362; cos(27°) -0.891006531:

Относительная погрешность предлагаемого устройства

А 0,45713125 -0,455253 п/иос л(л Ауз.у гГл оцт0,4125-10

Az3.v

гз.у

0,455253 0,890625 - 0,890362

0,890362

0,2951-10 3;

Относительная погрешность прототипа прих 27°

Л - 0.45407959-0,4414062 . 15 ДУпр0,454079590 2 10

0

с

0

°

0

«

5

50

А0,89453125 -0,891006531 п, 1П-2

0,891006531а3 1°

Точность вычислений в предлагаемом устройстве на порядок выше.

Рассмотрим работу устройства на конкретном примере расчета функции у sin x, z cos х.

Ограничимся пятью разрядами (п 5). Мантисса аргумента 0,01111 подается поразрядно на соответствующие шины входной кодовой комбинации 1. 2, 3, 4. Первый разряд, равный 0, поступает на первые управляющие входы 1, 2. 3, 4-го коммутатора. На вторые управляющие входы которых поступают соответственно 1,2,3,4-й разряды кодовой комбинации, равные 0,1,1,1. Все коммутаторы остаются в закрытом состоянии, и на их выходах установится код 00.00000 (старший разряд - знаковый). С выхода первого коммутатора код 00.00000 поступает на вход первого преобразователя в дополнительный код, остается неизменным и далее поступает на вход третьей разрядной дискреты второго комбинационного сумматора, со сдвигом на два разряда, и, одновременно подается на входы разрядной дискреты блоков частичной суммы первой группы. На информационный вход первого блока частичной суммы подана двоичная константа 0,01010, на вход частичной суммы поступает третий разряд входной кодовой комбинации, равный 1. на управляющий вход - первый разряд кодовой комбинации, равный 0. На выходе первого блока частичной суммы первой группы устанавливается код 01.00000. На информационный вход второго блока частичной суммы первой группы подана константа 0,10000. На вход частичной суммы поступает четвертый разряд входной кодовой комбинации, равный 1, на управляющий вход-второй разряд, равный 1. На выходе второго Ыюнз частичной суммы первой группы оЬразу тгл результат 01.00000 Ня и мпми пн н ый

вход третьего блока частичной суммы первой группы подана константа 0,10011. На вход частичной суммы поступает пятый разряд входной кодовой комбинации, равный 1, на управляющий вход - третий разряд, равный 1. На выходе третьего блока частичной суммы первой группы образуется результат 01.00000. На информационный вход первого блока частичной суммы четвертой группы константа 0,01010, на вход частичной суммы поступает код с выхода второго коммутатора, на вход разрядной дискреты поступает второй разряд входной кодовой комбинации, равный 1, на управляющий вход - первый разряд входной кодовой комбинации, равный О. На выходе данного блоке частичной суммы вырабатывается результат, равный 00.00000. На информационный вход второго блока частичной суммы четвертой группы подана константа 0,10000. На вход частичной суммы поступает результат с третьего комму атора, на управляющий вход и вход разрядной дискреты поступает второй разряд входной кодовой комбинации, равный 1. На выходе блока образуется результат, равный 00.10000. На информационный вход третьего блока частичной суммы четвертой группы подана константа 0,10011. На вход частичной суммы поступает результат с четвертого коммутатора, на вход разрядной дискреты поступает второй разряд входной кодовой комбинации, равный Т, на управляющий вход - третий разряд входной кодовой комбинации, равный 1. На выходе третьего блока частичной суммы четвертой группы образуется результат 00,10011. С выхода первого блока частичной суммы первой группы результат поступает на вход четвер- :той разрядной дискреты первого комбинационного сумматора, со сдвигом на три разряда OO.QQtOO, и, одновременно поступает на вход разрядной дискреты блоков частичной суммы пятой группы. Результат, равный 00.0000, с выхода первого блока частичной суммы четвертой группы поступает на вход второго преобразователя в дополнительный код, остается неизменным и поступает на вход четвертой разрядной дискреты второго комбинационного сумматора, со сдвигом на три разряда вправо и. одновременно на входы разрядной дискреты блоков частичной суммы второй группы. На информационный вход первого блока частичной суммы второй группы подана константа 0,01000, на вход частичной суммы поступает код с выхода второго блока частичной суммы первой группы 01.0000, на управляющий вход - первый разряд входной кодовой комбинации, равный 0. На выходе первого блока частичной суммы второй группы обраэу- ется результат 01.00000. На информационный вход второго блока частичной суммы второй группы подана константа 0,01 100, 5 на вход частичной суммы поступает код с выхода третьего блока частичной суммы первой группы, на управляющий вход второй разряд входной кодовой комбинации, равный 1, На выходе второго блока частич0 ной суммы второй группы образуется результат 01.00000. Результат с выхода первого блока частичной суммы второй группы поступает на вход пятой дискреты первого комбинационного сумматора со

5 сдвигом на четыре разряда вправо 00.00001 и. одновременно на вход разрядной дискреты первого блока частичной суммы шестой группы. На информационный вход первого блока частичной суммы пятой группы под0 ана константа 0,01000, на вход частичной суммы поступает код 00,10000 с выхода второго блока частичной суммы четвертой группы, на вход разрядной дискреты код 01,00000. на управляющий вход - первый

5 разряд входной кодовой комбинации, равный 0. На выходе первого блока частичной суммы пятой группа образуется код 00.10000. На икформацноннь(й вход второго блока частичной суммы пятой группы под0 ана константа 0.01 1 00, на вход частичной суммы с выхода третьего блока частичной суммы поступает код 00,100 1. на вход раз5 ряд ной дискреты 01,00000, на управляющий еход поступает второй разряд входной кодовой комбинации, равный 1. На выходе второго блока частичной суммы пятой груп0 пы образуется результат 00.11 1 1 1. С выхода первого блока частичной суммы пятой группы результат поступает на третий преобразователь в дополнительный код. Результат, равный 11,100000, с выхода

5 преобразователя в дополнительный код поступает на вход пятой разрядной дискреты второго комбинационного сумматора со сдвигом на четыре разряда вправо 11.111110000 и одновременно поступает на

0 вход разрядной дискреты первого блока частичной суммы третьей группы на информационный вход которого поданз двоичная константа 0,00110, на вход частичной суммы код 01,00000 с выхода второго блока частич5 ной суммы второй группы, на управляющий вход подан первый разряд входной кодовой комбинации, равный 0. На выходе первого блока частичной суммы третьей группы образуется результат, равный 01,00000, который поступает на вход шестой разрядной дискреты первого комбинационного сумматора со сдвигом на пять разрядов вправо 00,00001. На информационный вход первого блока частичной суммы шестой группы подана константа 0.00.110, на вход частичной суммы поступает результат 00,11111 с выхода второго блока частичной суммы пятой .группы, на вход разрядной дискреты 01,00000, на управляющий вход поступает первый разряд входной кодовой комбинации, равный 0. На выходе первого блока- частичной суммы шестой группы образуется результат 00.11111, который поступает на вход четвертого преобразователя в дополнительный код. С выхода четвертого преобразователя в дополнительный код результат, равный 11,00001 поступает на вход шестой разрядной дискреты второго комбинационного сумматора со сдвигом на пять разрядов вправо 11,11111000001. На входы разрядных дискрет первого комбинационного сумматора также поступают первый код нуля, второй-первый разряд входной кодовой комбинации со сдвигом на один разряд 0,0, третьей - второй разряд входной кодовой комбинации со сдвигом на два разряда 0,01. На выходе первого комбинационного сумматора формируется окончательный результат у 0,01111, На входы разрядных дискрет второго комбинационного сумматора кроме вышеперечисленных также поступают: на вход первой разрядной дискреты код единицы 1,00000, второй код нуля. На, его выходе формируется окончательный результат 0,1111000001.

Изобретение было создано в порядке выполнения НИР по теме Разряд по плану Президиума АН УССР.

Ожидаемый экономический эффект от использования изобретения составит 1197,37 руб/год.

Формула изобретения Устройство для вычисления функций си- нуса и косинуса, содержащее два коммутатора, (п-1)/2, где п - разрядность входного аргумента, преобразователей в дополнительный код, отличающееся тем, что, с целью повышения точности, в него введены n-З коммутатора, (п-1)/2 преобразователя в дополнительный код, 2п-4 группы блоков вычисления частичной суммы, два комбинационных сумматора, причем первые управляющие входы коммутаторов являются входами первого разряда кодовой комбинации устройства, вторые управляющие входы 1-го (где I 1,2...,п-1) коммутаторов являются входами соответственно 1-го разряда кодовой комбинации устройства, информационный вход 1-го коммутатора соединен с входом двоичной соответствующей константы устройства, выход первого коммутатора соединен с входом первого

преобразователя в дополнительный код. выход которого соединен с входами разрядной дискреты блоков вычисления частичной суммы первой группы, состоящей из (п-2)-х

элементов, входы частичной суммы j-ro (где.

J - 1,2п-2) блока вычисления частичной

суммы первой группы являются соответст венно входами (j+2)-ro разряда кодовой комбинации устройства, информационные(

0 входы к-х блоков вычисления частичной суммы |-й,и Q+n-l)-1 групп соединены с входом константы устройства, равной К/(К+}+1), (где К - 1,....(n-J-1). управляющие входы к-х блоков вычисления частичной суммы j-й и

5 ()-й группы являются входами К-ro разряда кодовой комбинации устройства, выход 0+1)-то коммутатора соединен с входами частичной суммы j-ro блока частичной суммы (п-1)-й группы, входы разрядной дискре0 ты которых соединены с входом второго разряда кодовой комбинации устройства, выход f-ro разряда первого блока вычисления частичной суммы 1-й группы соединен с входом (1+3)-й разрядной дискреты (1+2)-го

5 разряда первого комбинационного суммгг- тора и с входами разрядной дискреты бяо- ков вычисления частичной суммы (1+п-1)-й группы, выход 1-го блока частичной суммы 1-й группы соединен с входом частичной

0 суммы (-1)-го блока частичной суммы (I И)-й. группы, где (I 2,... n-Й), выход первого блока вычисления частичной суммы (п-2)-й соединен с входом (п-И)-й разрядной дискреты п-го разряда первого комбинационно5 го сумматора, выход первого блока вычисления частичной суммы (+п-2)-й группы соединен с входом J-ro преобразователя в дополнительный код, который соединен с входом 0+2Но разряда OJKJJH разрядной ди-

0 скреты второго комбинационного сумматора и с входами разрядной дискреты блоков вычисления частичной суммы { +1}-й группы выход 1-го блока частичной суммы (1+п-2)-й группы соединен с входом частичной суммы

5 (1-1)-го блока частичной суммы (1+п-1)-й группы, выход первого блока вычисления частичной суммы (2п-4)-й группы соединен с входом (п-1)-го преобразователя в дополнительный код. выход (п-1)-го преобразовате0 ля в дополнительный код соединен с входом n-го разряда (п+1)-й разрядной дискреты второго комбинационного сумматора, входы первой и второй разрядных дискрет второго комбинационного сумматора соединен

5 с входом логического нуля, входы второй, третьей разрядных дискрет первого комбинационного сумматора являются входом соответственно первого и второго разрядов кодовой комбинации устройства, на вход первой разрядной дискреты рторого комбинационного сумматора подан код логической единицы устройства, при этом блока вычисления частичной суммы содержит коммутатор, умножитель, сумматор, управляющий вход коммутатора блока соединен с управляющим входом блока вычисления частичной суммы, информационный вход коммутатора блока соединен с входом разрядной дискреты блока вычисления частичной суммы, выход коммутатора блока

соединен с первым информационным входом умножителя, второй информационный вход которого является информационным входом блока вычисления частичной суммы, выход умножителя соединен с первым входом сумматора, второй вход которого является входом частичной суммы блока вычисления частичной суммы, выход сумматора является выходом блока вычисления частичной суммы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления гиперболических функций у = @ и у = с @ | 1990 |

|

SU1735845A1 |

| Устройство для умножения | 1991 |

|

SU1807481A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1984 |

|

SU1238078A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" | 2011 |

|

RU2475812C1 |

| Устройство для определения стационарности случайного процесса | 1984 |

|

SU1251120A1 |

| Цифровой нерекурсивный фильтр | 1989 |

|

SU1665502A1 |

| Устройство для вычисления суммы произведений | 1981 |

|

SU978144A1 |

| Коррелятор | 1986 |

|

SU1339584A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1315971A1 |

| Преобразователь кодов | 1989 |

|

SU1762410A1 |

Изобретение относится к вычислительной технике, в частности к устройствам для выполнения математических операций в двоичном представлении, и может быть применено в качестве спецпроцессора в комплексе с вычислительной машиной для оперативного вычисления функций у sin x; z cos x. Цель изобретения - повышение точности вычисления функций. Работу устройства можно описать, исходя из того, что для функций у sin x, z cos x справедливы следующие соотношения; y(i) 2)1 Ц z(J), x(l - J), z() I У(1) .) Предложенное уст-г1 ройство позволяет вычислить функции у « sin x, z - cos x для двоичного разрядного аргумента за один такт работы схемы с требуемой точностью. Применение его возможно при решении самого широкого круга задач, связанных с моделированием, решением задач в реальном масштабе времени, требующих высокую точность и быстродействие; Устройство содержит коммутаторы 1(1), 1(2),..1(п-1), блоки вычисления частичной суммы 2(1.1), 2(1.2)...2(m.1) (m 2n-4), преобразователи 3(1), 3(2),...3(n - 1), комбинационные сумматоры 4.1, 4 2 Зил. (Л С

.Сг5

JL

Ллг.

.

(pua.Z

о|.

7//;

.

Ь)

фа аз

| Устройство для вычисления функций синуса и косинуса | 1981 |

|

SU1001093A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР N; 1146661, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления функций синуса и косинуса | 1981 |

|

SU1012249A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-07-15—Публикация

1991-06-04—Подача