Изобретение относится к автоматике, вычислительной и измерительной технике, может использоваться, например, в системах цифровой обработки изображений для классификации сигналов по их корреляционным и спектральным характеристикам и является усовершенствованием изобретения по авт. ев, № 1568213.

Цель изобретения - расширение функциональных возможностей путем обеспечения дополнительной функции определения средневзвешенного расстояния между входным аналоговым и эталонным сигналами.

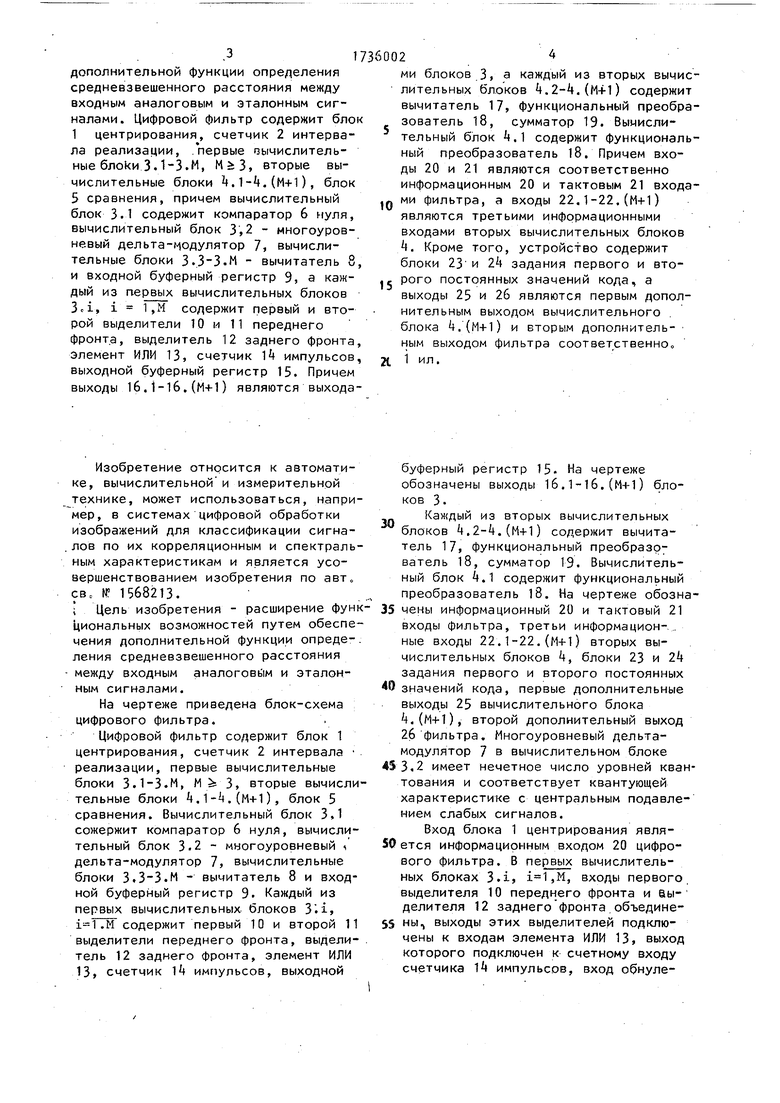

На чертеже приведена блок-схема цифрового фильтра.

Цифровой фильтр содержит блок 1 центрирования, счетчик 2 интервала реализации, первые вычислительные блоки 3.1-З.М, М Ь 3, вторые вычислительные блоки 4.1-4.(М+1), блок 5 сравнения. Вычислительный блок 3,1 сожержит компаратор 6 нуля, вычислительный блок 3.2 - многоуровневый , дельта-модулятор 7, вычислительные блоки .M - вычитатель 8 и входной буферный регистр 9. Каждый из первых вычислительных блоков 3.i, i-1.M содержит первый 10 и второй 11 выделители переднего фронта, выделитель 12 заднего фронта, элемент ИЛИ 13, счетчик 14 импульсов, выходной

0

буферный регистр 15- На чертеже обозначены выходы 16.1-16.(М+1) блоков 3.

Каждый из вторых вычислительных блоков 4.2-4.(М+1) содержит вычитатель 17, функциональный преобразователь 18, сумматор 19. Вычислительный блок 4.1 содержит функциональный преобразователь 18. На чертеже обозна5 чеиы информационный 20 и тактовый 21 входы фильтра, третьи информационные входы 22.1-22.(М+1) вторых вычислительных блоков 4, блоки 23 и 24 задания первого и второго постоянных значений кода, первые дополнительные выходы 25 вычислительного блока 4.(М+1), второй дополнительный выход 26 фильтра. Многоуровневый дельта- модулятор 7 в вычислительном блоке

53.2 имеет нечетное число уровней квантования и соответствует квантующей характеристике с центральным подавлением слабых сигналов.

Вход блока 1 центрирования явля0 ется информационным входом 20 цифрового фильтра. В первых вычислительных блоках 3.i, ,M, входы первого выделителя 10 переднего фронта и выделителя 12 заднего фронта объедине5 ны, выходы этих выделителей подключены к входам элемента ИЛИ 13, выход которого подключен к счетному входу счетчика 14 импульсов, вход обнулеия которого подключен к выходу торого выделителя 11 переднего фрона. Выходы счетчика И подключены информационным входам выходного уферного регистра 15,тактовый вход оторого объединен с входом второго выделителя 11 переднего фронта и подключен к выходу переполнения счетчика 2 интервала реализации. JQ

Выходы выходного буферного регистра 15 первых вычислительных блоков 3.1-З.М являются соответствующими выходами 16.1.-16.М указанных блоков. Все разрядные выходы многоуровневого 15 дельта-модулятора 7 вычислительного блока 3.2 и выходы всех разрядов вычитателей 8 вычислительных блоков 3.(М-1) подключены к информационным входам входных буферных регистров 20 9 и вторым, входам вычитателей 0 вычислительных блоков 3-3 - 3-Й соответственно. Выходы всех разрядов вычитателя 8 вычислительного блока З.М являются выходами 1б.(М+1) этого 25 блока. Вход компаратора 6 нуля вычислительного блока 3.1 объединен с информационным входом многоуровневого дельта-модулятора 7 вычислительного блока 3.2 и подключен к выходу 3Q блока 1 центрирования. Выход компаратора 6 нуля подключен к входам первого- выделителя 10 переднего фронта и выделителя 12 заднего фронта вычислительного блока 3.1. Выход знакового разряда разрядных выходов многоуровневого дельта-модулятора 7 вычислительного блока 3.2 и выходы знаковых разрядов выходов вычитателей 8 вычислительных блоков З.З З.М-подключены к входам первого выделителя 10 переднего фронта и выделителя 12 заднего фронта соответствующего вычислительного блока 3.2- З.М.

В блоках 3.3-З.М первые входы вы- 45 читателя 8 подключены к выходам входного буферного регистра Э, тактовые входы регистров 9 вычислительных блоков 3-3-З.М объединены с тактовыми входами многоуровневого дельта- модулятора 7 вычислительного блока 3.2, счетчика 2 интервала реализации и подключены к тактовому входу 21 / фильтра. Вторые вычислительные блоки А.2-А,(М+1) содержат вычитатель 17, & первые и вторые входы которого являются первыми и вторыми информационными входами соответствующего блока

35

40

50

5 5 Q

5

5

0

0

4, выходы вычитателя 17 подключены к первым входам функционального пре - образователя 18, вторые входы которого являются третьими информационными входами 22 соответствующего блока А. Выходы функционального преобразователя 18 соединены с первыми входами сумматора 19, вторые входы которого являются четвертыми информационными входами соответствующего вычислительного блока k. В вычислитепьном блоке k.1 первыми и вторыми информационными входами являются соответствующие входы функционального преобразователя 18, выходы которого являются выходами этого вычислительного блока.

Выходы J6.1 вычислительного блока 3.1, ,Л, подключены к первым информационным входам (1+1)-го вычислительного блока 4,(i+1) и вторым информационным входам 1-го блока А.1 (кроме блока .1), выходы 16.1 вычислительного блока 3.1 подключены также к первым информационным входам блока .1, выходы вычислительного блока ,i подключены к четвертым информационным входам вычислительного блока .(1ч-1). Выходы блока (.(Н+1) являются первыми дополнительными выходами 25 фильтра и подключены к первым входам блока 5 сравнения, вторые информационные входы которого и вторые информационные входы вычислительного блока 4.(М+1) подключены к выходам блоков 2k и 23 задания постоянного значения кода, выход блока 5 сравнения является вторым дополнительным выходом 26 фильтра.

Цифровой фильтр работает следующим оиразом,

Входной аналоговый сигнал x(t), поступающий на вход 20 фильтра, подвергается следующей обработке. С помощью блока 1 центрирования из сигнала x(t) исключается постоянная составляющая и производится коррекция спектра сигнала с подчеркиванием и подавлением отдельных полос частот. В каждом блоке 3-i, ,M, за время равное интервалу реализации (и), определяемому частотой Т дискретизации и коэффициентом N деления счетчика 2 интервала реализации, производится определение числа l);j нулей 1-го порядка входного сигнала: в первом блоке 3.1 V{ число пересечений входным сигналом нулевого уровня, во втором блоке 3.2 Бг - число пересечений производной входного сигнала нулевого уровня, в третьем блоке 3.3 DJ - число пересечений второй производной входного сигнала нулевого уровня и т.д. В конце интервала реализации @ указанные значения числа нулей записываются в выходные буферные регистры 15 блоков 3 и поступают на соответствующие выходы 16.

В следующем интервале реализации производится обработка полученной последовательности ЈD;} во вторых вычислительных блоках Ч, заключающаяся в вычислении средневзвешенного расстояния между входным и эталонным сигналами. Для этого определяется скорость роста числа нулей:

где

UDR -4

М.

D

1

k 1;

DK- DkM , ,M; (N-1)-Dk, ,,

(1)

N (

,M - число нулей соответствующего порядка;

)/Т - объем выборки. Затем вычисляются нормированные взвешенные значения отклонения скорости роста числа нулей соответствующего порядка от заданных

SD,

(UDK- AD)2

Г/360028

довательность импульсов, частота которых определяется частотой дискретизации входного сигнала при дельта- модуляции и соответствует отсутствию перегрузки по крутизне центрированного входного сигнала с блока 1. За время интервала реализации (и) TN в первом блоке 3.1 с помощью компаратора 6 и

Ю счетчика И производится подсчет пересечения входным центрированным сигнаг лом нулевого уровня (из плюса в минус и из минуса в плюс). В конце интервала реализации (и) по переднему

15 фронту импульса с выхода переполнения счетчики 2 содержимое счетчика 14 записывается в регистр 15, а счетчик 1 подготавливается к циклу накопления. Таким образом, на выхо20 дах регистра 15 блока 3.1 формируется число нулей первого порядка DJ центрированного входного сигнала„ которое сохраняется на этих выходах в течение следующего интервала реализации.

25 Во втором блоке 3-2 центрированный входной сигнал подвергается дискретизации и квантованию с частотой Т с помощью дельта-модулятора 7, на выходах которого формируется знак и

30 абсолютное значение приращения входного сигнала по правилу:

EJ«ENT(E-5 + 0,5),UD

ТЬТ

(2)

m

.

1 мин

(х) m

где

- заданные скорости роста (скорости роста эталонного сигнала). Суммирование последовательности значений {ЈиД, ,M+1, позволяет определить выборочное значение1., расстояния между входным и эталонным сигналами в предыдущем интервале реализации

yti

/ ИХ. (3)

К 1

Сравнение величины ( с некот торой заданной величиной уЈ (эталонного сигнала) позволяет подтвердить или отбросить гипотезу о соответствии входного сигнала x(t) эталонному сигналу.

Рассмотрим определение числа нулей 1-го порядка , центрирован- ного входного сигнала.

С входа 21 на тактовый вход счетчика 2 поступает непрерывная после «- EJ«ENT(E-5

m

.

1 мин

5

где d

(х) m

д xm x

.(d)

Г

0

ENT(-) s(x)

5

O

5

численное значение шага

квантования;

его знак;

отсчет входного сигнала

и оценки его в моменты

дискретизации;

целая часть величины ()

минимальный нулевой шаг

квантования. Использование дельта-модулятора 7 с нечетным числом уровней квантования приводит при постоянном значении входного центрированного сигнала к формированию последовательности значений fd Јol и не приводит к изменению шага квантования. Последовательность )1 соответствует первой разности дискретизированно- го и квантованного центрированного ; входного сигнала, т.е. аппроксимирует первую производную указанного сиг-1 нала. Поэтому изменение знака в последовательности fdwj соответствует изменению знака производной и

подсчитывается за интервал реализации (#) счетчиком 14. В конце интервала реализации по импульсу с выхода переполнения счетчика 2 накопленное в счетчике 14 значение записывается в регистр 15, а счетчик 14 обнуляется, чем подготавливается к следующему

периоду накопления. Таким образом, на выходах 16,2 регистра 15 блока 3.2 формируется число нулей второго порядка D2, которое сохраняется на этих выходах в течение следующего интервала реализации.

10

роста числа нулей ДИ, D,, т.е. скорость роста числа нулей равна числу нулеи первого порядка. В блоках 4.k, ,M скорость роста числа нулей k-ro и (k-1)-го порядков, поступающих на первые и вторые информационные входы блока 4.k, т.е. первые и вторые входы вычитателя 17. На выходах вычитателя 17 блока 4.k, k-2,M формируется значение сигнала

AD,

Dv- D

К-1Фррмирование числа нулей более

7

высоких порядков рассмотрим на примере блока значений многоуровневого дельта-модулято15

V - a i pfirn no ll JVtri

ca 3.k ().Последовательность 1Й idm j, поступающая с выходов

На вторые информационные входы блока 4.(М+1) с блока 23 задания постоянного значения кода поступает значение сигнала, соответствующее (N-1), где N равно коэффициенту де ления счетчика 2 интервала реализации. На выходах вычитателя 17 этого

,. , 0 то блока формируется соответствующее

ра 7 вычислительного блока 3.2, стро- «о. /, ; п

м значение скорости -Д Dm,., (N-1 )-Dvn.

. т

Значения сигналов ЛD«J, ,M+1, поступают на первые входы функционального преобразователя 18 соот,ъ.

25 ветствующуго блока 4.k, на вторые входы которого с третьих информационных входов 22.k соответствующего блока 4.k подается значение заданной

бируется в регистре 9, в результате чего за период дискретизации Т на выходах и входах регистра 9 присутствуют значения d и d,, поступающие на входы вычитателя 8. Вычитатель ,8 осуществляет выуитание

т.е.

i j сх) значения а

(x V

Yn - 4 KIO oriciMcnrm ч| j

формирует разностную операцию V -

(

d - d.( , которая для соответствует формированию второй разности дискрётизированного и квантованного центрированного входного сигна- . ла. Изменение знака сигнала (из минуса в плюс и из плюса в минус) подсчитывается счетчиком 14 за интервал реализации (и) и записывается по сигналу с выхода переполнения счетчика 2 в конце интервала реализации в регистр 15, а счетчик 14 обнуляется, чем подготавливается к новому циклу накопления. 1 Блоки 3.k (kb 3) работают аналогично, формируя разностную операцию

vk- xm v(vKX) скорости роста числа нулей

JQ эталонного сигнала, в результате чего на выходах функционального преобразователя 18 формируется нормированное (взвешенное) значение отклонения скорости роста числа нулей ДОК от заданной &U согласно выраже 5 нию (2). Функциональный преобразователь 18 наиболее просто может быть выполнен на постоянном запоминающем устройстве, первые и вторые адресные входы которого являются первыми и вто рыми входами преобразователя 18.

Значения сигналовГ&П, , k 1,11+1, с выходов функциональных преобразователей 18 последовательно суммируются сумматорами 19: на входах суммато ра 19 блока 4.2 формируется значение сигнала §D, + $DЈ на выходах сумматора 19 блока 4,3 - значение сигнала $1) ( + $ D2 + &D ь и т.д., в результате чего на первых дополнитель sTx

rri

-V

К-2.

и подсчитывая изменение знака сигнаг ла , за интервал реализации ©. Поэтому на входах l6.k регистра 15 вычислительного блока 3.k формируется число D нулей k-ro порядка, которое сохраняется на этих выходах в течение следующего интер- . вала реализации.

Скорость роста числа нулей опре- , деляется следующим образом. В блоке 4.1 согласно (1) значение скорости

роста числа нулей ДИ, D,, т.е. скорость роста числа нулей равна числу нулеи первого порядка. В блоках 4.k, ,M скорость роста числа нулей k-ro и (k-1)-го порядков, поступающих на первые и вторые информационные входы блока 4.k, т.е. первые и вторые входы вычитателя 17. На выходах вычитателя 17 блока 4.k, k-2,M формируется значение сигнала

AD,

Dv- D

К-115

5 ветствующуго блока 4.k, на вторые входы которого с третьих информационных входов 22.k соответствующего блока 4.k подается значение заданной

скорости роста числа нулей

Q эталонного сигнала, в результате чего на выходах функционального преобразователя 18 формируется нормированное (взвешенное) значение отклонения скорости роста числа нулей ДОК от заданной &U согласно выраже5 нию (2). Функциональный преобразователь 18 наиболее просто может быть выполнен на постоянном запоминающем устройстве, первые и вторые адресные входы которого являются первыми и вторыми входами преобразователя 18.

Значения сигналовГ&П, , k 1,11+1, с выходов функциональных преобразователей 18 последовательно суммируются сумматорами 19: на входах суммато ра 19 блока 4.2 формируется значение сигнала §D, + $DЈ на выходах сумматора 19 блока 4,3 - значение сигнала $1) ( + $ D2 + &D ь и т.д., в результате чего на первых дополнительV ных выходах 25 фильтра формируется значение сигнала, равное (р2 согласно (3), т.е. средневзвешенное расстояние между входным и эталонным сигналами.

5 Значение U2 , поступающее на первые входы блока 5 сравнения, сравнивается с постоянным значением ( , поступающим с блока 24 задания второго

постоянного значения кода. -При выполнении условия(/ (г на втором выходе 26 фильтра формируется сигнал логической единицы, сигнализирующей о совпадении входного центрированного и эталонного сигналов с заданной точностью. Точность указанного совпадения задается значением yg c бло- ка 2 задания постоянного кода.

Скорость роста числа нулейЈ&В|Л от их пррядка k является быстроубы- вающей функцией, поэтому для определения нормированного средневзвешенного расстояния между входным и эталонным сигналами используется незначительное число вычислительных блоков k (обычно не более шести),

соответственно первые и вторые входы вычитателя, выходы которого подключены к первым входам соответствующего функционального преобразователя, вторые входы которого являются третьими информационными входами соответствующего второго вычислительного блока, выходы функционального преобразователя подключены к первым входам соответствующего сумматора, вторые входы которого являются четвертыми . информационными входами соответствующего вычислительного блока в первом ., из М+1 вторых вычислительных блоков, первыми и вторыми информационными I входами являются соответствующие входы функционального преобразователя, выходы которого являются выходами

что при незначительных аппаратурных затратах позволяет проводить идеи- 20 данного вычислительного блока и сое- тификацию и обнаружение заданных динены с четвертыми информационными сигналов, а также проверку статисти- входами второго из вторых вычислитель-j ческих гипотез, например соответст- ных блоков соответственно, выходы вия входного центрированного сигнала 1-го первого вычислительного блока авторегрессионному процессу заданного 25 М подключены к первым информа- порядка.ционным входам 1то, кроме первого,

второго вычислительного блока соответственно, выходы первого из первых вычислительных блоков подключены к первым информационным входам первого и второго из вторых вычислительных блоков, выходы 1-го второго вычислительного блока подключены к соответствующим четвертым информационным входам (i+1 )-го второго вычислитель- 35 ного блока, выходы (М+1 )-го второго

Формула изобретения

Цифровой фильтр по авт.св.№ 1568213, отличающийся тем, что, с целью расширения функциональных возможностей путем обеспечения дополнительной функции определения средневзвешенного расстояния между входным аналоговым и эталонным сигналами, в него введены блок сравнения и М+1 вторых вычислительных блоков, первый из которых выполнен на функциональном преобразователе (каждый из М), а остальные - на вычитателе, функциональном преобразователе и сумматоре, выходы которого являются выходами соответствующего второго вычислительного блока, первыми и вторыми информационными входами которого являются

30

вычислительного блока являются первыми дополнительными выходами и подключены к первым входам блока сравне ния, вторые входы которого и вторые

40 информационные входы (М+1)-го второго вычислительного блока являются первой и второй шинами кода постоянного значения, выход блока сравнения является вторым дополнительным вы45 ходом.

соответственно первые и вторые входы вычитателя, выходы которого подключены к первым входам соответствующего функционального преобразователя, вторые входы которого являются третьими информационными входами соответствующего второго вычислительного блока, выходы функционального преобразователя подключены к первым входам соответствующего сумматора, вторые входы которого являются четвертыми . информационными входами соответствующего вычислительного блока в первом , из М+1 вторых вычислительных блоков, первыми и вторыми информационными I входами являются соответствующие входы функционального преобразователя, выходы которого являются выходами

данного вычислительного блока и сое- динены с четвертыми информационными входами второго из вторых вычислитель-j ных блоков соответственно, выходы 1-го первого вычислительного блока 5 М подключены к первым информа- ционным входам 1то, кроме первого,

вычислительного блока являются первыми дополнительными выходами и подключены к первым входам блока сравне ния, вторые входы которого и вторые

информационные входы (М+1)-го второго вычислительного блока являются первой и второй шинами кода постоянного значения, выход блока сравнения является вторым дополнительным выходом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр | 1990 |

|

SU1815797A1 |

| Цифровой фильтр | 1990 |

|

SU1758836A1 |

| Цифровой фильтр | 1989 |

|

SU1695493A2 |

| Цифровой фильтр | 1989 |

|

SU1695492A2 |

| Цифровой фильтр | 1989 |

|

SU1695323A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1990 |

|

SU1730723A2 |

| Дельта-модулятор | 1988 |

|

SU1543547A1 |

| Устройство для вычисления дискретного преобразования Фурье | 1987 |

|

SU1501085A1 |

| Устройство для многоуровневой дельта - модуляции | 1988 |

|

SU1674377A1 |

| Анализатор активности непрерывных сигналов | 1989 |

|

SU1658386A1 |

Изобретение относится к автоматике, вычислительной и измерительной технике и может использоваться, например, в системах цифровой обработки изображений для классификации сигналов,по их корреляционным и спектральным характеристикам. Цедь изобретения - расширение функциональных возможностей путем обеспечения

| Авторское свидетельство СССР У 1568213, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

Авторы

Даты

1992-05-23—Публикация

1990-01-25—Подача