22

О

ел

00

со со

Os

Изобретение относится к вычислительной технике и технике связи и может использоваться в системах с адаптивной дискретизацией непрерывных сигналов, например, в устройствах сжатия данных или распознавания образов.

Цель изобретения - повышение точности и расширение функциональных возможностей путем сравнения числа критических точек входного и эталонного сигналов в заданной полосе частот на заданном интервале реализации.

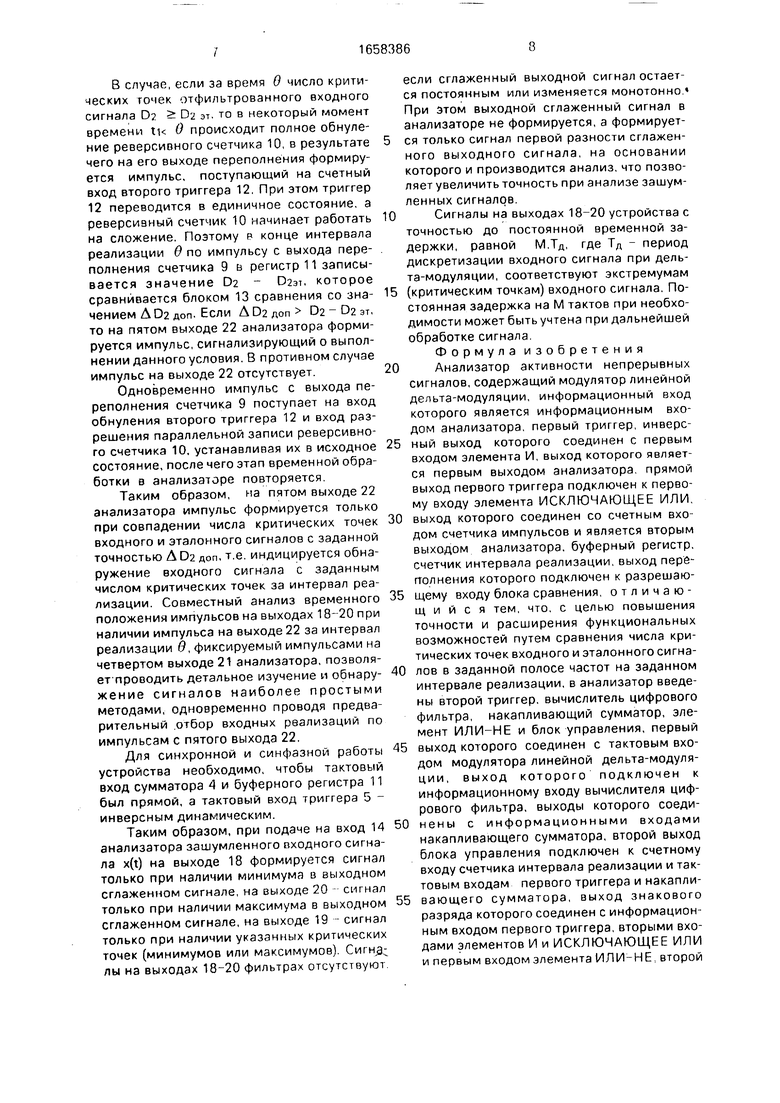

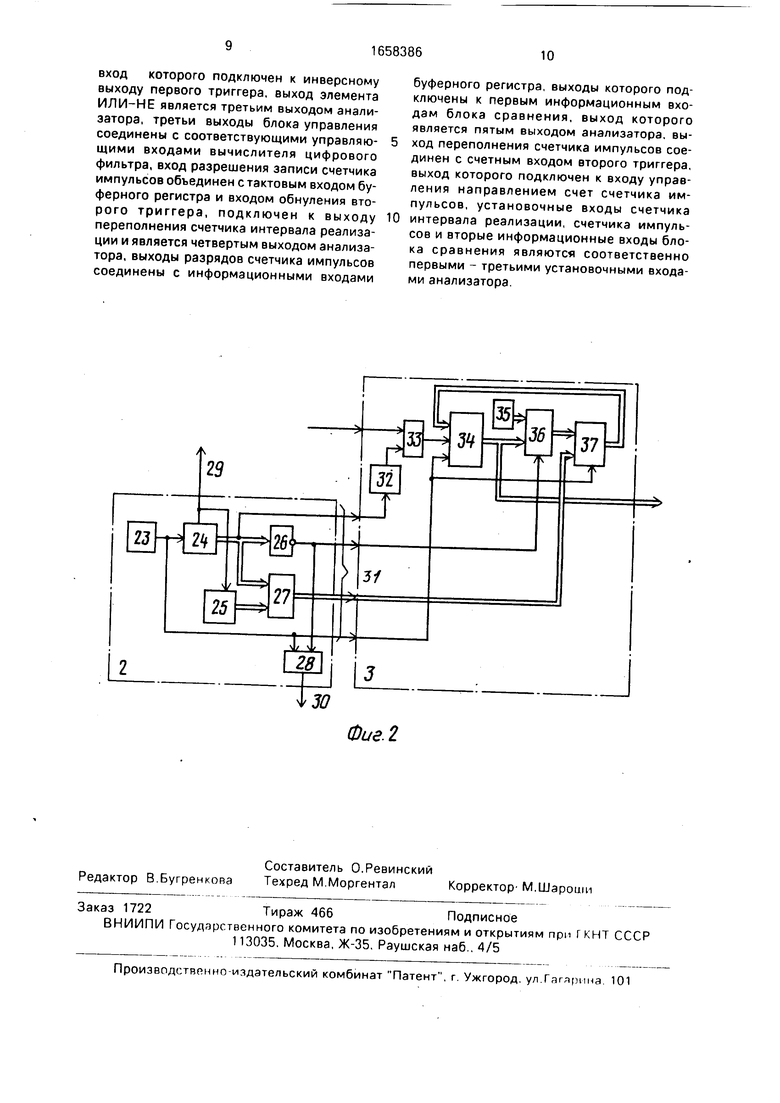

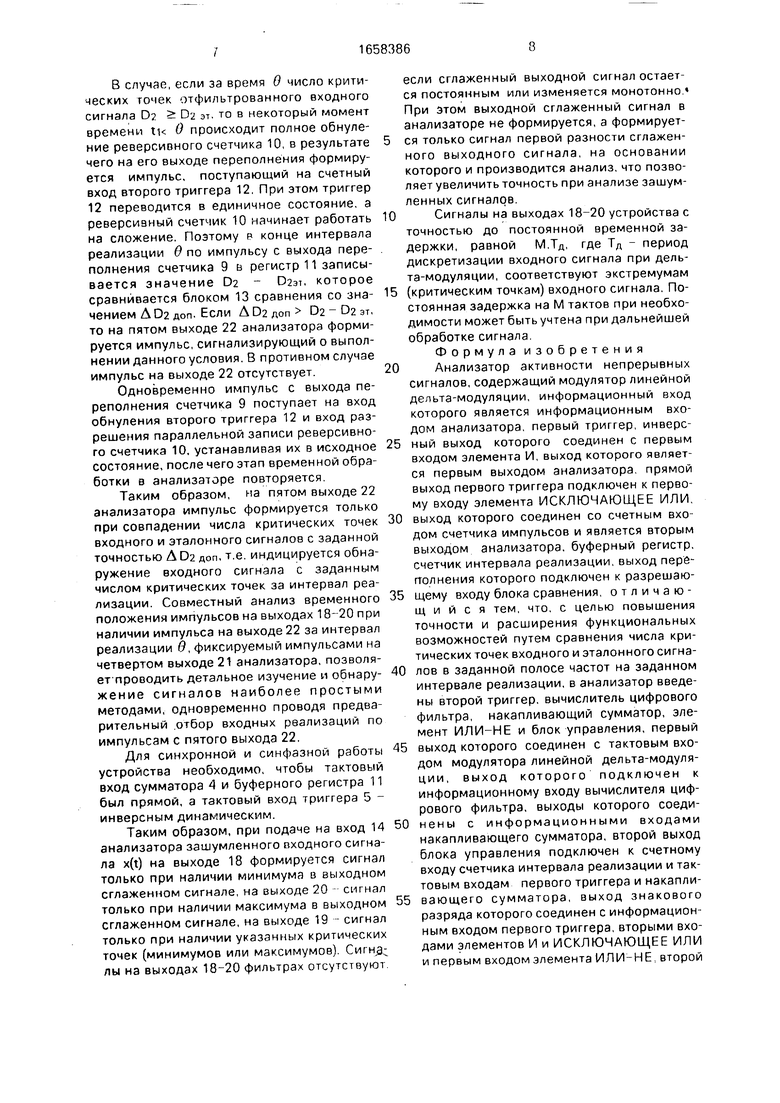

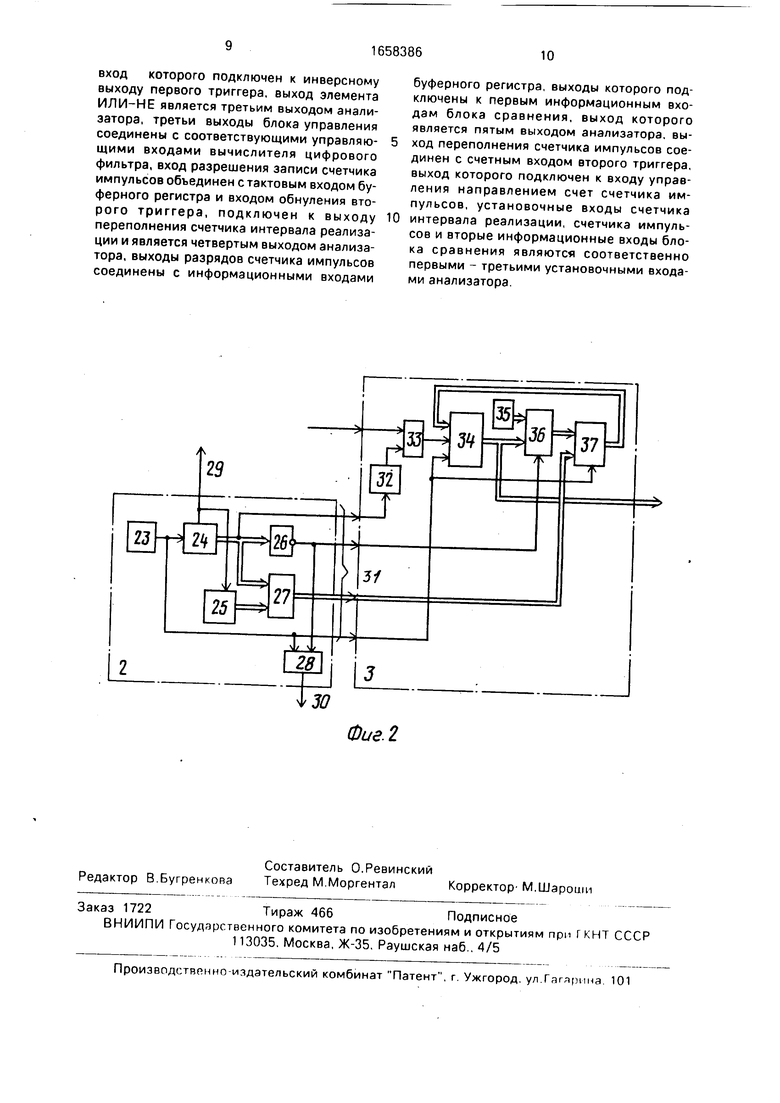

На фиг. 1 представлена блок-схема анализатора; на фиг. 2 - пример выполнения и подключения блока управления и вычислителя цифрового фильтра.

Анализатор содержит модулятор 1 линейной дельта-модуляции (ЛДМ), блок 2 управления, вычислитель 3 цифрового фильтра, накапливающий сумматор 4, первый триггер 5, элемент И 6, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 7, элемент ИЛИ-НЕ 8, счетчик 9 интервала реализации, счетчик 10 импульсов, буферный регистр 11, второй триггер 12 и блок 13 сравнения. На фиг. 1 обозначены информационный вход 14, первые - третьи установочные входы 15-17, первый - пятый выходы 18-22.

Блок 2 управления выполнен (фиг. 2) на тактовом генераторе 23, первом и втором счетчиках 24 и 25 импульсов, элемент ИЛИ- НЕ 26, сумматоре 27 и формирователе 28 импульсов. На фиг. 2 обозначены первый, второй и третьи выходы 29-31 блока 2 управления.

Вычислитель 3 цифрового фильтра содержит (фиг. 2) блок 32 постоянной памяти, элемент 33 эквивалентности, реверсивный счетчик 34, источник 35 постоянного (нулевого) кода, блок 36 переключения и блок 37 оперативной памяти.

Работа анализатора основана на принципе преобразования аналоговых сигналов в одноразрядную дельта-кодовую последовательность Вп , ее цифровой фильтрации с дальнейшей логической и временной обработкой. На первом этапе производится преобразование непрерывного аналогового сигнала x(t) в дельта-кодовую последовательность ,{enW}. n 0, еп х)е {-1.1}, en(x)BnW Bn(x) (1+en(x)/2.Bn(x)e {0,1} по правилу

BnW .

1 , Хп - Хп 0

О , хп - хп О

где x(t) - сигнал, предварительно восстановленный из сигнала Вп формирующийся в

цепи обратной связи модулятора 1 ЛДМ. На втором этапе производится фильтрация входного сигнала путем свертки входной и весовой последовательности в формате линейной дельта-модуляции, при этом текущее значение выходного сигнала вычислителя 3 фильтра равно

М-1 Уп - Ј еЛп-т(х)

m 0

0)

(h)

где {em }, m О, М-1 - весовая последовательность. Одновременно на этом этапе осуществляется накопление результатов свертки, т.е. в накапливающем сумматоре 4 формируется значение сигнала

20

Vyn 2 2yk,

k 1

представляющего собой последовательность первых разностей (приращений) отфильтрованного выходного сигнала.

Поэтому путем соответствующего выбора алгоритма фильтрации из входного зашум- ленного сигнала устраняется (ослабляется) шумовая составляющая, т.е. число критических точек в выходном сигнале фильтра равно (приближается) истинному в заданной полосе частот. На третьем этапе производится логическая обработка отфильтрованной последовательности первых разностей Vyn. При этом значение знакового разряда

равно:

40

Вп

0, Vyn 0 ,

1, Vyn 0 .

Тогда, при выполнении условия Вп/Вп-1 имеем наличие критической точки (максимума или минимума) во входном сигнале. Характер критической точки входного сигнала

уточняется следующим образом. Если в п-м периоде дискретизации Вп 0, Вп-1 1, то сигнал имеет максимум (или сигнал имел постоянное значение и начинает уменьшаться), если Вл 1, Вп-1 0 - сигнал имеет

минимум (или сигнал уменьшался и имеет постоянное значение).

На следующем этапе временной обработки число критических точек D2 отфильтрованного входного сигнала, т.е. суммарное число минимумов и максимумов, сравнивается с заданным О2эт на интервале реализации 0. Причем, при выполнении условия

D2 эт. A D2 доп D2 D2 эт 4 A D2 доп.

где Д D2 доп - допустимое отклонение числа критических точек эталонного и входного сигналов, формируется признак соответствия входного сигнала эталонному.

Анализатор работает следующим образом.

Входной аналоговый сигнал x(t), поступающий на вход 14 анализатора, по импульсам с первого выхода 29 блока 2 управления, поступающим на тактовый вход модулятора 1, преобразуется в дельта-кодовую последовательность Вп и поступает на информационный вход вычислителя 3 цифрового фильтра. По управляющим сигналам с третьих выходов блока 2 в вычислителе 3 за период дискретизации входного сигнала производится вычисление свертки входной {еп } последовательности (п 0) и записанной в блоке.З весовой {ет } последовательности согласно (1). Вычисление

второй разности уп является частью цифровой фильтрации (сглаживания) дельта- модулированного входного сигнала.

Значения свертки {Vе 2уп }, п 0, по импульсам с второго выхода 30 блока 2 записываются в накапливающий сумматор 4, в котором производится непрерывное суммирование (накопление) значений уп. В результате суммирования в накапливающем сумматоре 4 формируются текущие значения сигнала Vyn, соответствующие последовательности первых разностей (приращений) отфильтрованного (сглаженного) выходного сигнала.

Сигнал с выхода знакового разряда накапливающего сумматора 4, соответствующий значению Вп, поступает на информа- ционный вход первого триггера 5 и фиксируется в нем при поступлении заднего фронта импульса с второго выхода 30 блока 2, Поэтому до поступления указанного импульса на информационном входе и прямом выходе первого триггера 5 присутствуют сигналы Вп и Вп-1, поступающие на входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7. Если Вп , то на втором выходе 19 анализатора появляется импульс, сигнализирующий о наличии критической точки (экстремума) входного сигнала. Одновременно, если Вп Вп-1 1, то на выходе элемента И 6 появляется импульс, поступающий на первый выход 18 анализатора и сигнализирующий о наличии минимума. Аналогично, если Вп Вп-1 0, то на выходе элемента ИЛИ-НЕ 8 появляется импульс, поступающий на третий выход 20 анализатора, и свидетельствующий о наличии

максимума. Сигнал Вп 1 снимается с инверсного выхода первого триггера 5

Импульсы с частотой дискретизации Тд 1 поступают также на счетный вход счетчика

9, задающего длину интервала реализации, на котором производится временная отработка входного сигнала, заключающаяся в сравнении числа критических точек входного и заданного сигналов. Длина интервала

реализации д пропорциональна коэффициенту пересчета N счетчика 9 в Тд- N Время анализа (длина реализации) задается установкой соответствующего значения на первых установочных входах 15 анализатора, которые являются входами задания коэффициента деления счетчика 9. В конце интервала реализации 0 на выходе переполнения счетчика 9 формируется импульс, поступающий на вход разрешения параллельной записи реверсивного счетчика 10 и вход обнуления второго триггера 12. По импульсу переполнения счетчика 9 в реверсивный счетчик 10 с входов параллельной записи, являющихся вторыми установочными входами 16, записывается число критических точек эталонного входного сигнала D2 эт, а триггер 12 устанавливается в нулевое состояние.Сигнал с прямого выхода второго триггера 12 поступает на управляющий

вход реверсивного счетчика 10, который в этом случае работает на вычитание. Импульсы с выхода элемента ИСКЛЮЧАЮЩЕЕ . ИЛИ 7, сигнализирующие о наличии критической точки во входном сигнале, поступают

на счетный вход реверсивного счетчика 10. уменьшая его состояние.

Рассмотрим сначала случай, когда D2 D2 эт. Тогда в конце интервала реализации в по импульсу, поступающему с выхода переполнения счетчика 9. в буферном регистре 11 фиксируется значение разности числа критических точек эталонного и отфильтрованного входного сигналов D2 эт - D2, которая поступает на первые

информационные входы блока 13 сравнения. На вторые информационные входы блока 13 сравнения с третьих установочных входов 17 анализатора подается значение AD2 доп.. Если за интервал реализации

в выполняется ранее принятое условие D2 эт D2. то при выполнении условия AD2 доп D2 эт D2 по импульсу, поступающему с выхода переполнения счетчика 9. на выходе блока 13 сравнения, являющемся

пятым выходом 22 анализатора, формируется признак соответствия входного сигнала эталонному. Если же Л D: доп D2 эт D2. то импульс на выходе блока 13 сравнения отсутствует.

В случае, если за время 0 число критических точек отфильтрованного входного сигнала D D Зт. то в некоторый момент времени ti 0 происходит полное обнуление реверсивного счетчика 10, в результате чего на его выходе переполнения формируется импульс, поступающий на счетный вход второго триггера 12. При этом триггер 12 переводится в единичное состояние, а реверсивный счетчик 10 начинает работать на сложение. Поэтому в конце интервала реализации 9 по импульсу с выхода переполнения счетчика 9 в регистр 11 записывается значение D2 - Оаэт, которое сравнивается блоком 13 сравнения со значением ДО2 доп. ЕСЛИ Л02доп D2 D2 эт, то на пятом выходе 22 анализатора формируется импульс, сигнализирующий о выполнении данного условия. В противном случае импульс на выходе 22 отсутствует.

Одновременно импульс с выхода переполнения счетчика 9 поступает на вход обнуления второго триггера 12 и вход разрешения параллельной записи реверсивного счетчика 10, устанавливая их в исходное состояние, после чего этап временной обработки в анализаторе повторяется.

Таким образом, на пятом выходе 22 анализатора импульс формируется только при совпадении числа критических точек входного и эталонного сигналов с заданной точностью Д D2 доп, т.е. индицируется обнаружение входного сигнала с заданным числом критических точек за интервал реализации. Совместный анализ временного положения импульсов на выходах 18-20 при наличии импульса на выходе 22 за интервал реализации в, фиксируемый импульсами на четвертом выходе 21 анализатора, позволя- егпроводить детальное изучение и обнаружение сигналов наиболее простыми методами, одновременно проводя предварительный отбор входных реализаций по импульсам с пятого выхода 22.

Для синхронной и синфазной работы устройства необходимо, чтобы тактовый вход сумматора А и буферного регистра 11 был прямой, а тактовый вход триггера 5 - инверсным динамическим.

Таким образом, при подаче на вход 14 анализатора зашумленного входного сигнала x(t) на выходе 18 формируется сигнал только при наличии минимума в выходном сглаженном сигнале, на выходе 20 - сигнал только при наличии максимума в выходном сглаженном сигнале, на выходе 19 - сигнал только при наличии указанных критических точек (минимумов или максимумов). Сигн,а; лы на выходах 18-20 фильтрах отсутствуют

если сглаженный выходной сигнал остается постоянным или изменяется монотонно « При этом выходной сглаженный сигнал в анализаторе не формируется, а формируется только сигнал первой разности сглаженного выходного сигнала, на основании которого и производится анализ, что позволяет увеличить точность при анализе зашум- ленных сигналов.

Сигналы на выходах 18-20 устройства с

точностью до постоянной временной задержки, равной М.Тд, где Тд - период дискретизации входного сигнала при дельта-модуляции, соответствуют экстремумам

(критическим точкам) входного сигнала. Постоянная задержка на М тактов при необходимости может быть учтена при дальнейшей обработке сигнала.

Формула изобретения

Анализатор активности непрерывных сигналов, содержащий модулятор линейной дельта-модуляции, информационный вход которого является информационным входом анализатора, первый триггер, инверсный выход которого соединен с первым входом элемента И, выход которого является первым выходом анализатора, прямой выход первого триггера подключен к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ,

выход которого соединен со счетным входом счетчика импульсов и является вторым выходом анализатора, буферный регистр, счетчик интервала реализации, выход переполнения которого подключен к разрешающему входу блока сравнения, отличаю- щ и и с я тем, что, с целью повышения точности и расширения функциональных возможностей путем сравнения числа критических точек входного и эталонного сигналов в заданной полосе частот на заданном интервале реализации, в анализатор введены второй триггер, вычислитель цифрового фильтра, накапливающий сумматор, элемент ИЛИ-НЕ и блок управления, первый

выход которого соединен с тактовым входом модулятора линейной дельта-модуляции, выход которого подключен к информационному входу вычислителя цифрового фильтра, выходы которого соединены с информационными входами накапливающего сумматора, второй выход блока управления подключен к счетному входу счетчика интервала реализации и тактовым входам первого триггера и накапливающего сумматора, выход знакового разряда которого соединен с информационным входом первого триггера, вторыми входами элементов И и ИСКЛЮЧАЮЩЕЕ ИЛИ и первым входом элемента ИЛИ-НЕ второй

вход которого подключен к инверсному выходу первого триггера, выход элемента ИЛИ-НЕ является третьим выходом анализатора, третьи выходы блока управления соединены с соответствующими управляющими входами вычислителя цифрового фильтра, вход разрешения записи счетчика импульсов объединен с тактовым входом буферного регистра и входом обнуления второго триггера, подключен к выходу переполнения счетчика интервала реализации и является четвертым выходом анализатора, выходы разрядов счетчика импульсов соединены с информационными входами

буферного регистра, выходы которого подключены к первым информационным входам блока сравнения, выход которого является пятым выходом анализатора, выход переполнения счетчика импульсов соединен с счетным входом второго триггера, выход которого подключен к входу управления направлением счет счетчика импульсов, установочные входы счетчика интервала реализации, счетчика импульсов и вторые информационные входы блока сравнения являются соответственно первыми - третьими установочными входами анализатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр | 1990 |

|

SU1736002A2 |

| Дельта-модулятор | 1987 |

|

SU1508350A2 |

| Цифровой фильтр | 1989 |

|

SU1695493A2 |

| Дельта-модулятор | 1987 |

|

SU1425838A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1989 |

|

SU1661969A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1988 |

|

SU1589383A1 |

| Цифровой фильтр с симметричной импульсной характеристикой | 1987 |

|

SU1495979A1 |

| Цифровой фильтр | 1990 |

|

SU1815797A1 |

| Цифровой фильтр | 1990 |

|

SU1758836A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1989 |

|

SU1661968A1 |

Изобретение относится к вычислительной технике связи. Его использование в системах с адаптивной дискретизацией К непрерывных сигналов (для сжатия данных или распознавания образов) позволяет повысить точность и расширить функциональные возможности путем сравнения числа критических точек входного и эталонного сигналов в заданной полосе частот на заданном интервале реализации. Анализатор содержит модулятор 1 линейной дельта-модуляции, триггер 5, элемент И 6, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 7, счетчик 9 интервала реализации, счетчик 10 импульсов, буферный регистр 11 и блок 13 сравнения. Поставленная цель достигается благодаря введению блока 2 управления, вычислителя 3 цифрового фильтра, накапливающего сумматора 4, элемента ИЛИ-НЕ 8 и триггера 12, а также выполнению счетчика 10 импульсов реверсивным. 2 ил, &

Фие.2

| Анализатор активности непрерывных сигналов | 1987 |

|

SU1438004A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР № 1568242, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-06-23—Публикация

1989-05-03—Подача