Изобретение относится к автоматике, вычислительной и измерительной технике и может быть использовано, например, в системах сжатия данных и обработки изображений, корреляционного и спектрального анализа и т.п.

Цель изобретения - расширение функциональных возможностей цифрового фильтра за счет определения числа нулей высоких порядков повторно-суммарных и повторно-разностно-суммарных входных сигналов на интервале реализации.

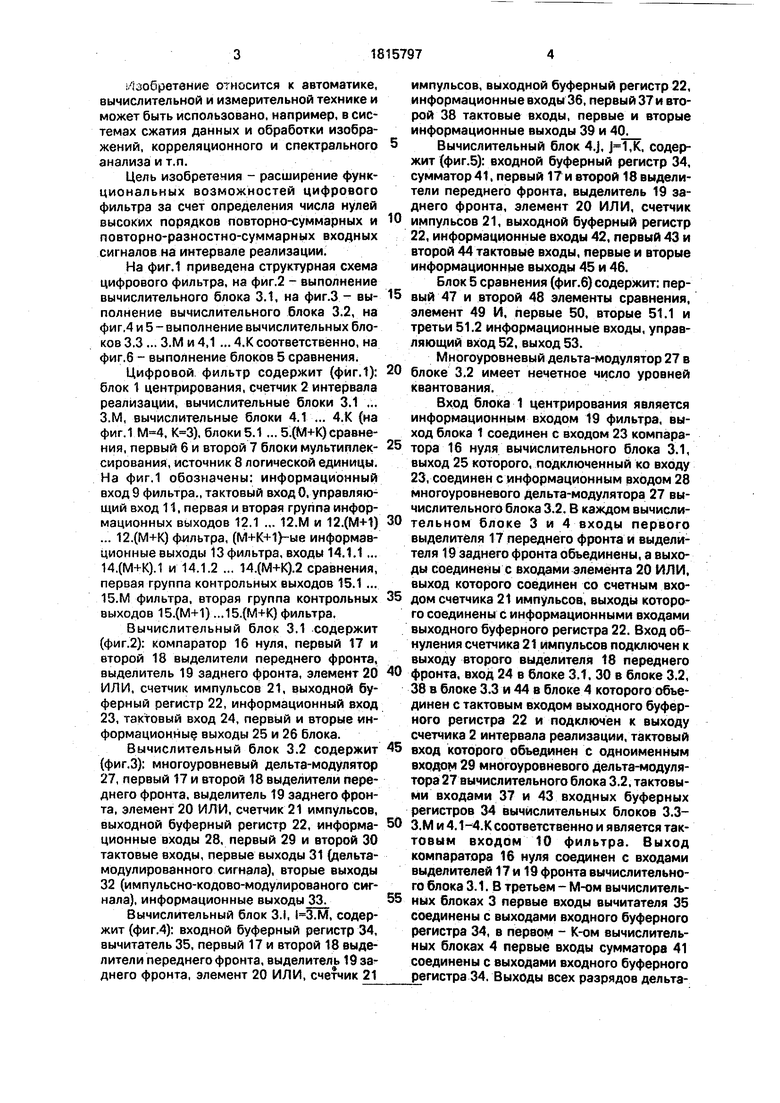

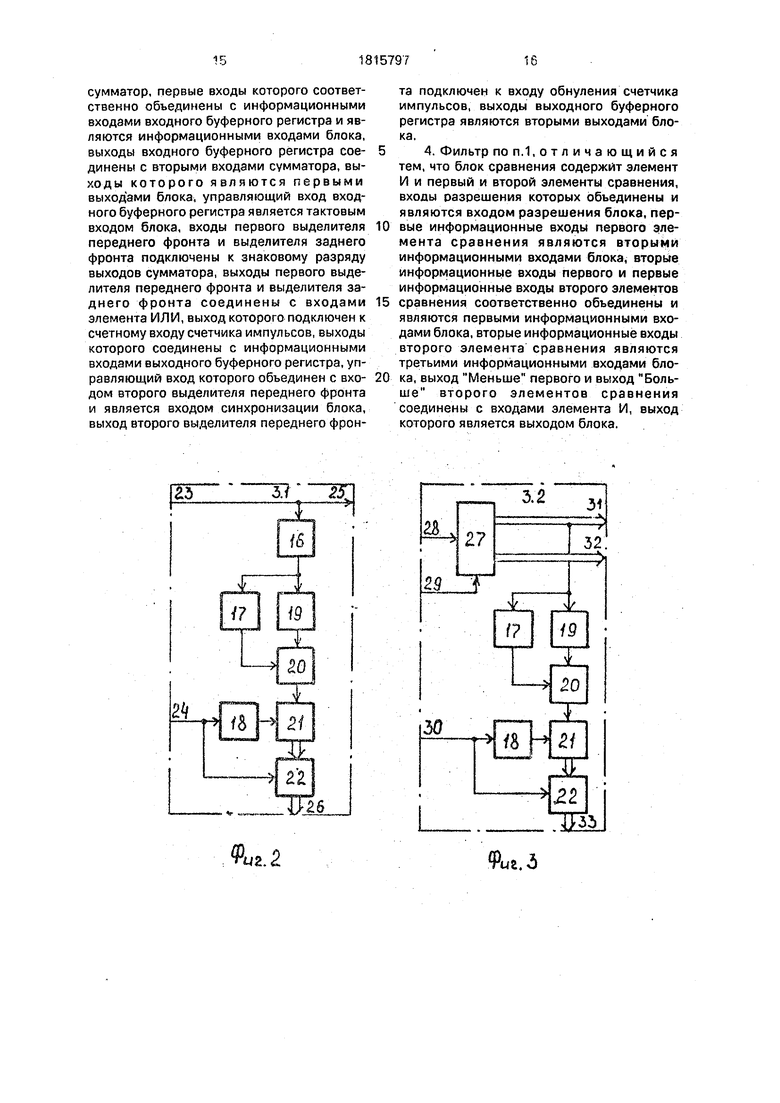

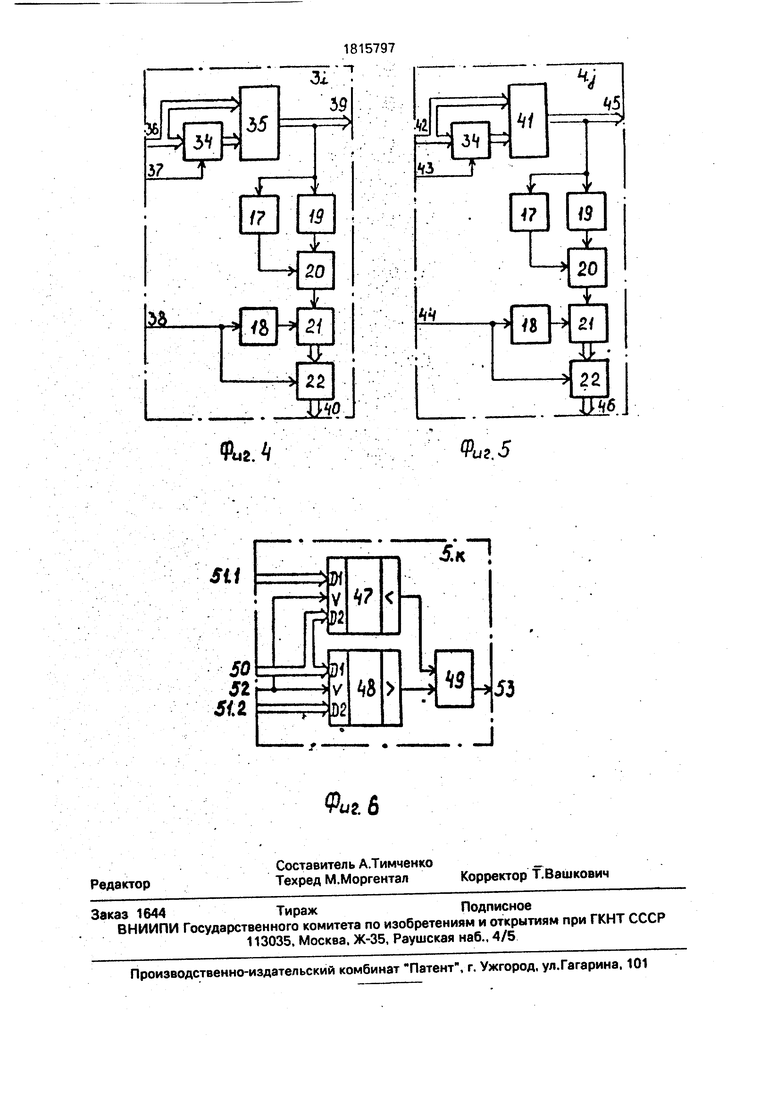

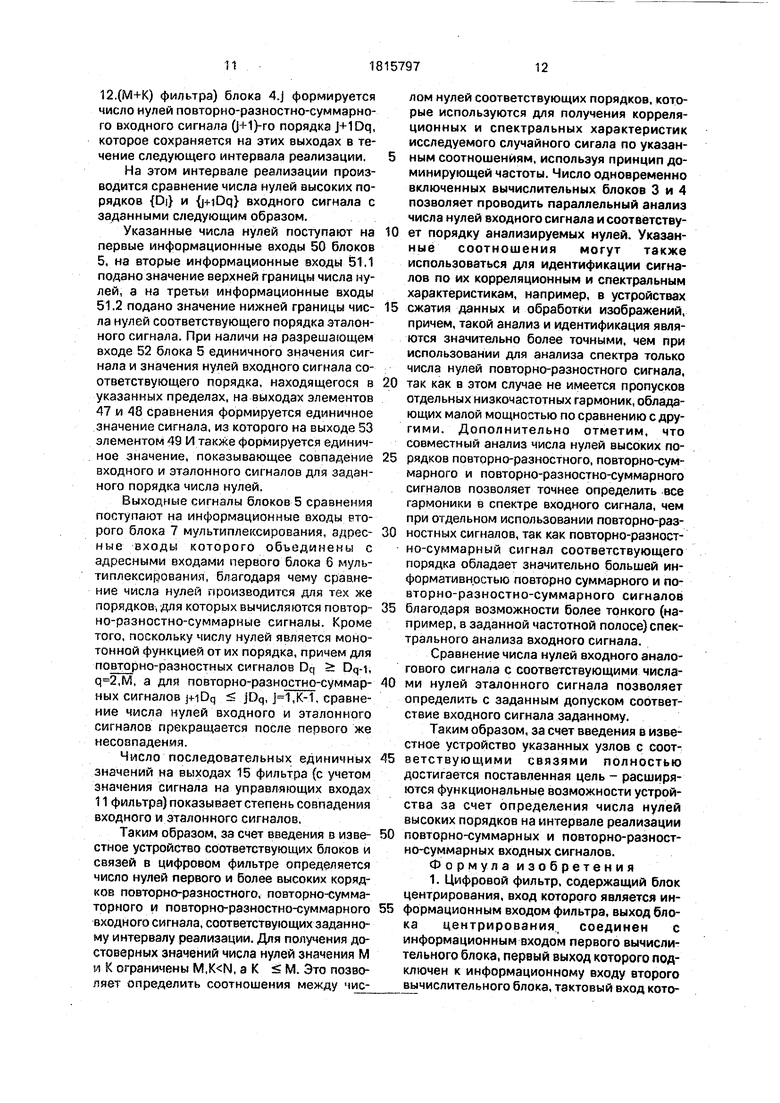

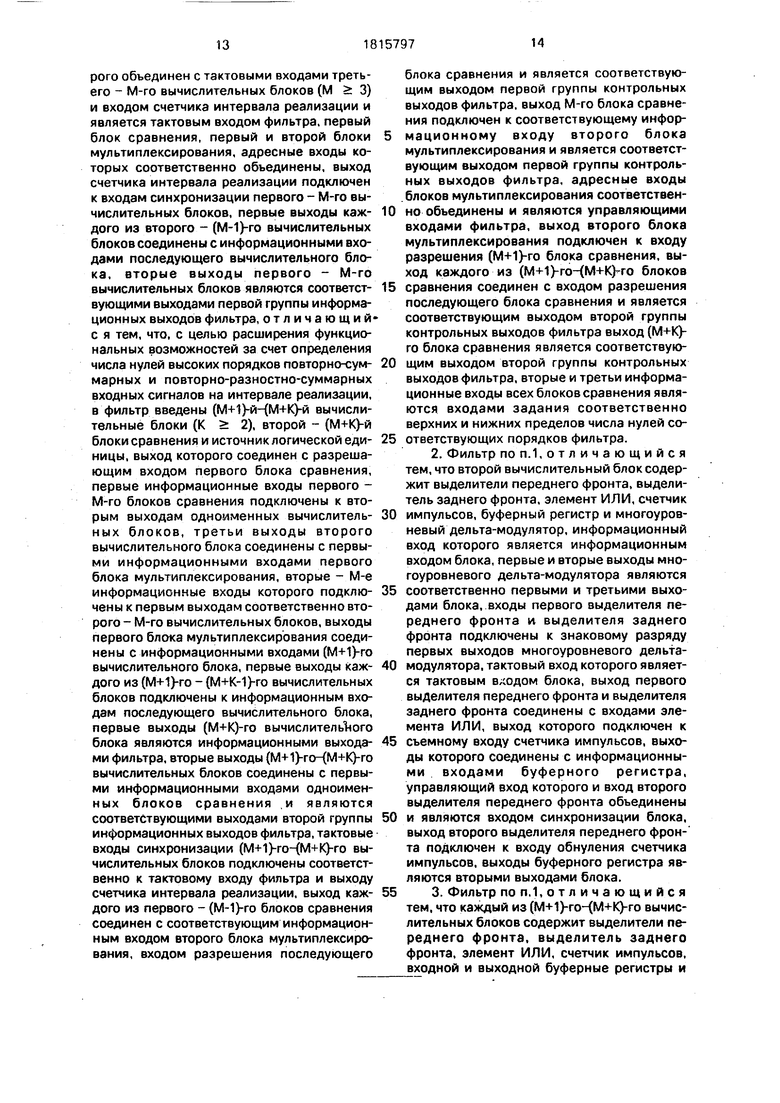

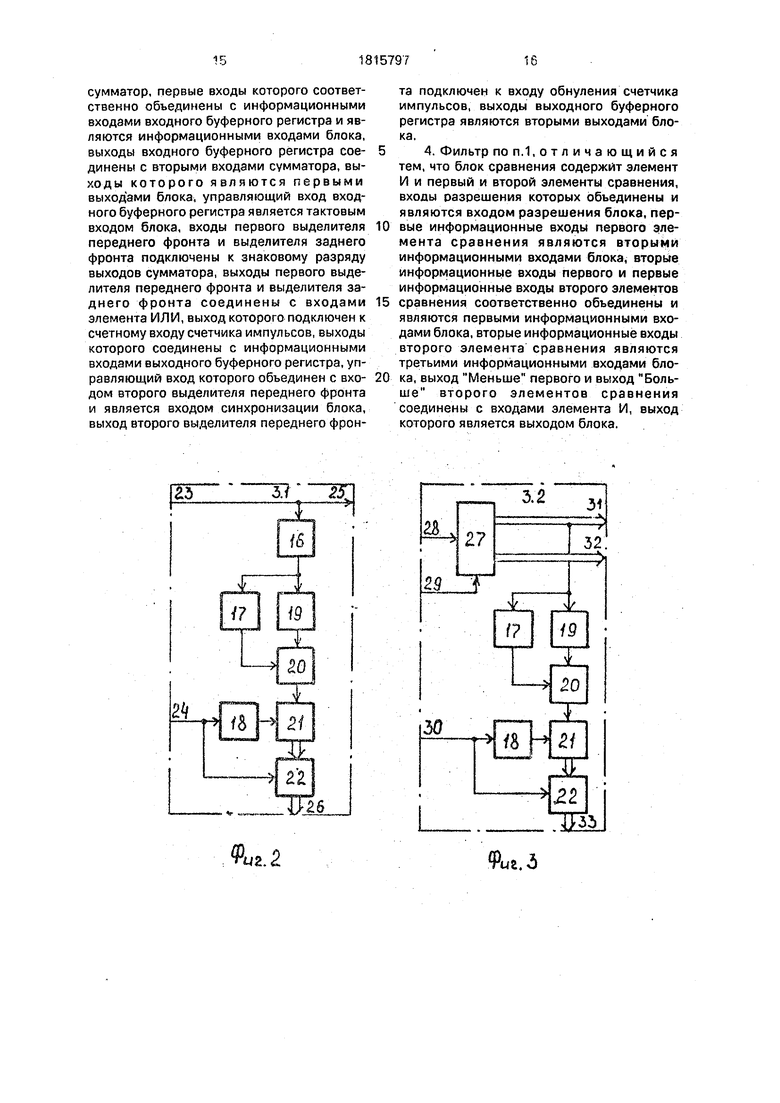

На фиг.1 приведена структурная схема цифрового фильтра, на фиг.2 - выполнение вычислительного блока 3.1, на фиг.З - выполнение вычислительного блока 3.2, на фиг,4 и 5 - выполнение вычислительных блоков 3.3... З.М и 4,1 ... 4.К соответственно, на фиг.б - выполнение блоков 5 сравнения.

Цифровой фильтр содержит (фиг.1): блок 1 центрирования, счетчик 2 интервала реализации, вычислительные блоки 3.1 ... З.М, вычислительные блоки 4.1 ... 4.К (на фиг.1 , ), блоки 5.1... 5.(М+К) сравнения, первый 6 и второй 7 блоки мультиплексирования, источник 8 логической единицы. На фиг.1 обозначены: информационный вход 9 фильтра., тактовый вход 0, управляющий вход 11, первая и вторая группа информационных выходов 12.1 ... 12.М и 12.(М+1) ... 12.(М+К) фильтра, (М+К+1 -ые информав- ционные выходы 13 фильтра, входы 14.1.1...

14.(М+К).1 и 14.1.2 ... 14.(М+К).2 сравнения, первая группа контрольных выходов 15.1 ...

15.М фильтра, вторая группа контрольных выходов 15.(М+1) ...15.{М+К) фильтра.

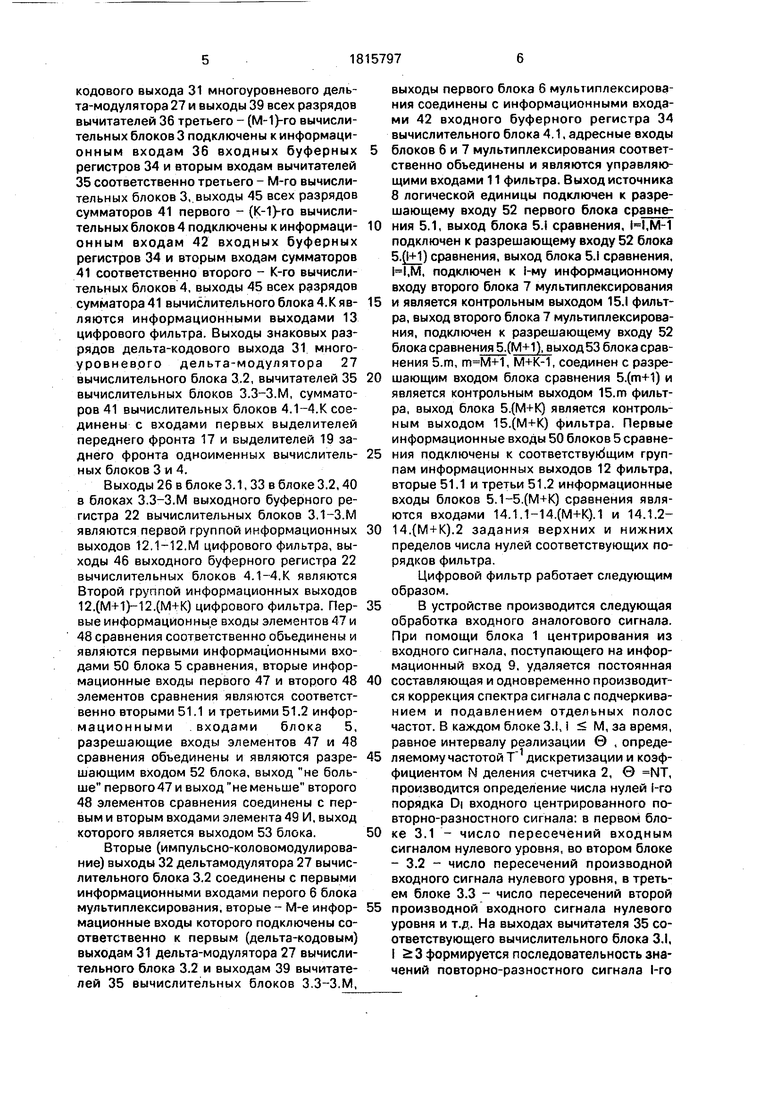

Вычислительный блок 3.1 содержит (фиг.2): компаратор 16 нуля, первый 17 и второй 18 выделители переднего фронта, выделитель 19 заднего фронта, элемент 20 ИЛИ, счетчик импульсов 21, выходной буферный регистр 22, информационный вход 23, тактовый вход 24, первый и вторые информационны выходы 25 и 26 блока.

Вычислительный блок 3.2 содержит (фиг.З): многоуровневый дельта-модулятор 27, первый 17 и второй 18 выделители переднего фронта, выделитель 19 заднего фронта, элемент 20 ИЛИ, счетчик 21 импульсов, выходной буферный регистр 22, информационные входы 28, первый 29 и второй 30 тактовые входы, первые выходы 31 (дельта- модулированного сигнала), вторые выходы 32 (импульсно-кодово-модулированого сигнала), информационные выходы 33.

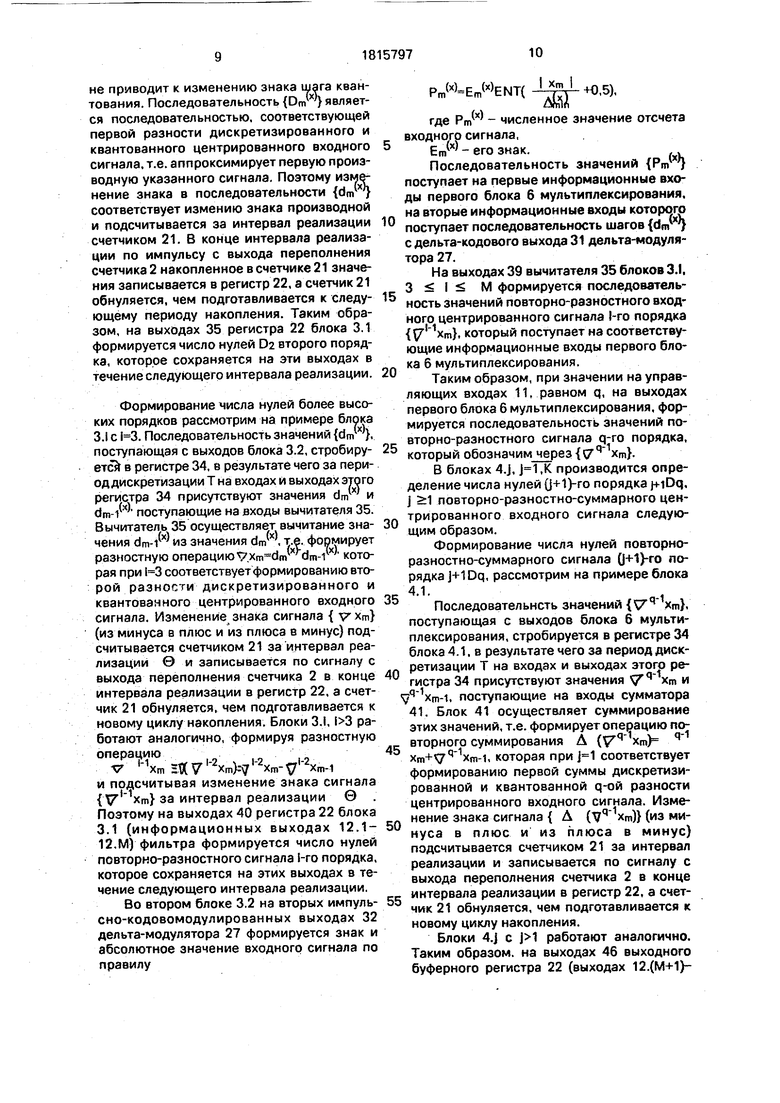

Вычислительный блок 3.I, .M, содержит (фиг.4): входной буферный регистр 34, вычитатель 35, первый 17 и второй 18 выделители переднего фронта, выделитель 19 заднего фронта, элемент 20 ИЛИ, счетчик 21

импульсов, выходной буферный регистр 22, информационные входы 36, первый 37и второй 38 тактовые входы, первые и вторые информационные выходы 39 и 40.

Вычислительный блок 4.J, ,K, содержит (фиг.5): входной буферный регистр 34, сумматор 41, первый 17 и второй 18 выделители переднего фронта, выделитель 19 заднего фронта, элемент 20 ИЛИ, счетчик

импульсов 21, выходной буферный регистр

22. информационные входы 42, первый 43 и второй 44 тактовые входы, первые и вторые информационные выходы 45 и 46.

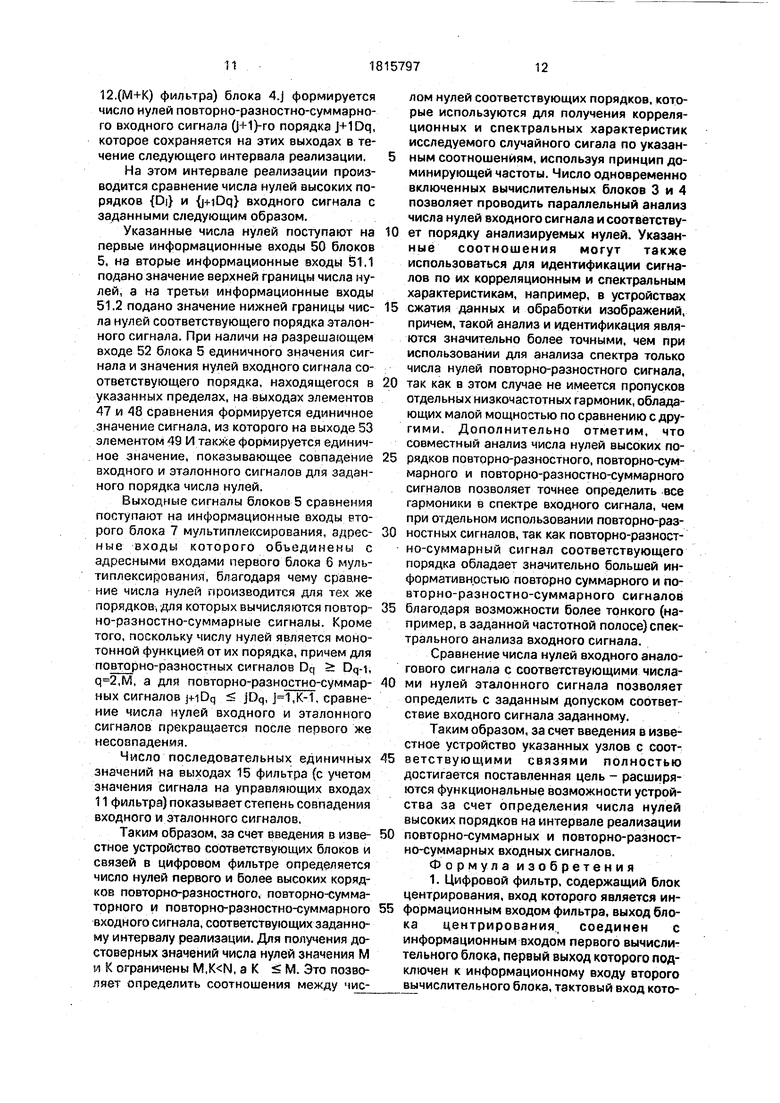

Блок 5 сравнения (фиг.б) содержит; пер5 вый 47 и второй 48 элементы сравнения, элемент 49 И, первые 50, вторые 51.1 и третьи 51.2 информационные входы, управляющий вход 52, выход 53.

Многоуровневый дельта-модулятор 27 в

0 блоке 3.2 имеет нечетное число уровней квантования.

Вход блока 1 центрирования является информационным входом 19 фильтра, выход блока 1 соединен с входом 23 компара5 тора 16 нуля вычислительного блока 3.1, выход 25 которого, подключенный ко входу

23. соединен с информационным входом 28 многоуровневого Дельта-модулятора 27 вычислительного блока 3.2. В каждом вычисли0 тельном блоке 3 и 4 входы первого выделителя 17 переднего фронта и выделителя 19 заднего фронта объединены, а выходы соединены с входами элемента 20 ИЛИ, выход которого соединен со счетным вхо5 дом счетчика 21 импульсов, выходы которого соединены с информационными входами выходного буферного регистра 22. Вход обнуления счетчика 21 импульсов подключен к выходу второго выделителя 18 переднего

0 фронта, вход 24 в блоке 3.1. 30 в блоке 3.2, 38 в блоке 3.3 и 44 в блоке 4 которого объединен с тактовым входом выходного буферного регистра 22 и подключен к выходу счетчика 2 интервала реализации, тактовый

5 вход которого объединен с одноименным входом 29 многоуровневого дельта-модулятора 27 вычислительного блока 3.2, тактовыми входами 37 и 43 входных буферных регистров 34 вычислительных блоков 3.30 З.М и 4.1-4.К соответственно и является тактовым входом 10 фильтра. Выход компаратора 16 нуля соединен с входами выделителей 17 и 19 фронта вычислительного блока 3.1. В третьем - М-ом вычислитель5 ных блоках 3 первые входы вычитателя 35 соединены с выходами входного буферного регистра 34, в первом - К-ом вычислительных блоках 4 первые входы сумматора 41 соединены с выходами входного буферного регистра 34. Выходы всех разрядов дельтакодового выхода 31 многоуровневого дельта-модулятора 27 и выходы 39 всех разрядов вычитателей 36 третьего - (М-1)-го вычислительных блоков 3 подключены к информаци- онным входам 36 входных буферных регистров 34 и вторым входам вычитателей 35 соответственно третьего - M-го вычислительных блоков 3,. выходы 45 всех разрядов сумматоров 41 первого - (К-1)-го вычислительных блоков 4 подключены к информаци- онным входам 42 входных буферных регистров 34 и вторым входам сумматоров 41 соответственно второго - К-го вычислительных блоков 4, выходы 45 всех разрядов сумматора 41 вычислительного блока 4.К яв- ляются информационными выходами 13 цифрового фильтра. Выходы знаковых разрядов дельта-кодового выхода 31 многоуровневого дельта-модулятора 27 вычислительного блока 3,2, вычитателей 35 вычислительных блоков 3.3-3.М, сумматоров 41 вычислительных блоков 4.1-4.К соединены с входами первых выделителей переднего фронта 17 и выделителей 19 заднего фронта одноименных вычислитель- ных блоков 3 и 4.

Выходы 26 в блоке 3.1, 33 в блоке 3.2,40 в блоках 3.3-3.М выходного буферного регистра 22 вычислительных блоков 3.1-З.М являются первой группой информационных выходов 12.1-12.М цифрового фильтра, выходы 46 выходного буферного регистра 22 вычислительных блоков 4.1-4.К являются Второй группой информационных выходов 12.(М+1)-12.(М+К) цифрового фильтра. Пер- вые информационные входы элементов 47 и 48 сравнения соответственно объединены и являются первыми информационными входами 50 блока 5 сравнения, вторые информационные входы первого 47 и второго 48 элементов сравнения являются соответственно вторыми 51.1 и третьими 51.2 информационными входами блока 5, разрешающие входы элементов 47 и 48 сравнения объединены и являются разре- шающим входом 52 блока, выход не больше первого47 и выход не меньше второго 48 элементов сравнения соединены с первым и вторым входами элемента 49 И, выход которого является выходом 53 блока,

Вторые (импульсно-коловомодулирова- ние) выходы 32 дельтамодулятора 27 вычислительного блока 3.2 соединены с первыми информационными входами перого 6 блока мультиплексирования, вторые - M-е инфор- мационные входы которого подключены соответственно к первым (дельта-кодовым) выходам 31 дельта-модулятора 27 вычислительного блока 3.2 и выходам 39 вычитателей 35 вычислительных блоков 3.3-З.М,

выходы первого блока 6 мультиплексирования соединены с информационными входами 42 входного буферного регистра 34 вычислительного блока 4.1, адресные входы блоков 6 и 7 мультиплексирования соответственно объединены и являются управляющими входами 11 фильтра. Выход источника 8 логической единицы подключен к разрешающему входу 52 первого блока сравне- ния 5.1, выход блока 5.1 сравнения, ,M-1 подключен к разрешающему входу 52 блока 5.Q+1) сравнения, выход блока 5.1 сравнения, ,М, подключен к 1-му информационному входу второго блока 7 мультиплексирования и является контрольным выходом 15.1 фильтра, выход второго блока 7 мультиплексирования, подключен к разрешающему входу 52 блока сравнения 5.(М+1), выход 53 блока сравнения 5.m, , M+K-1, соединен с разрешающим входом блока сравнения 5.(т+1) и является контрольным выходом 15.лп фильтра, выход блока 5.(М+К) является контрольным выходом 15.(М+К) фильтра. Первые информационные входы 50 блоков 5сравнения подключены к соответствующим группам информационных выходов 12 фильтра, вторые 51.1 и третьи 51.2 информационные входы блоков 5.1-5.(М+К) сравнения являются входами 14.1.1-14.(М+К).1 и 14.1.2- 14.(М+К).2 задания верхних и нижних пределов числа нулей соответствующих порядков фильтра.

Цифровой фильтр работает следующим образом.

В устройстве производится следующая обработка входного аналогового сигнала. При помощи блока 1 центрирования из входного сигнала, поступающего на информационный вход 9. удаляется постоянная составляющая и одновременно производится коррекция спектра сигнала с подчеркиванием и подавлением отдельных полос частот. В каждом блоке 3.i, i М, за время, равное интервалу реализации 0 , определяемому частотой Т1 дискретизации и коэффициентом N деления счетчика 2, 0 NT, производится определение числа нулей 1-го порядка DI входного центрированного повторно-разностного сигнала: в первом блоке 3.1 - число пересечений входным сигналом нулевого уровня, во втором блоке - 3.2 - число пересечений производной входного сигнала нулевого уровня, в третьем блоке 3.3 - число пересечений второй производной входного сигнала нулевого уровня и т.д. На выходах вычитателя 35 соответствующего вычислительного блока 3.1, I S: 3 формируется последовательность значений повторно-разностного сигнала 1-го

пирмдка, причем нормированное значение числа нулей этого сигнала позволяет определить доминирующую частоту спектра лО|/(Ы-1) ад. Увеличение порядка повторно-разностного сигнала приводит к сдвигу мощности сигнала и нормированного значения числа нулей в сторону частоты дискретизации йл , а при этом нормированные значения числа нулей стремятся посетить все частоты спектра от частоты () доя (частоты дискретизации).

На входы вычислительного блока 4.1 поступает последовательность значений повторно-разностного сигнала q-ro порядка, Q Ј {d, ,M}-значение управляющего сигнала на входах 11, которые подвергаются в блоках 4.J, J :Ј К операции повторного суммирования. Поэтому в каждом вычислительном блоке 4,j, J К за время, равное интервалу реализации, производится определение числа нулей 0+1)-го порядка j+1Dq входного центрированного повторно-разностно-суммарного сигнала: в первом блоке 4.1 - число пересечений первой суммой повторно-разностного входного сигнала q-ro порядка нулевого, во втором блоке 4.2 - число пересечений второй суммой входного повторно-разностного сигнала q-ro порядка нулевого уровня и т.д. Увеличение порядка повторно-разностно- суммарного сигнала приводит к сдвигу мощности сигнала и нормированного значения числа нулей tt)+iDq/(N-1) ад+1- 0 а сторону нулевой частоты, причем, нормированные значения числа нулей стремятся посетить все частоты спектра сигнала от частоты дискретизации (я) до нулевой частоты. В конце интервала реализации Э числа нулей {Di} и {j+1Dq} записываются в выходные буферные регистры 22 блоков 3 и 4 и поступают на их выходы 26,33.40 и 46 - выходы 12.1-12.(М+К) фильтра.

Поскольку-при входной сигнал не подвергается операции повторного вычитания, число нулей Q+1}-ro порядка J+1 DI явля- ется числом нулей (j-t)-ro порядка повторно-суммарного входного сигнала, причем значение .

Указанные числа нулей {Di} и {J+1Dq} в блоках 5.1-5.(М+К) сравниваются с нижней и верхней границей числа нулей соответствующего порядка эталонного сигнала. В случае, если число нулей входного сигнала находится в указанных пределах, на выходе всех блоков 5 сравнения формируется единичное значение сигнала. Число нулей является монотонной функцией от их порядка, как для повторно-разностных сигналов: DI

Di-i, так и для повторно-разностно-сум- марных сигналов j+iDq jDq, поэтому сравнение числа нулей входного сигнала и заданного прекращается после первого же

несовпадения, а число последовательных единичных значений на выходах 15.1- 15.(М+К) сравнения показывает степень совпадения этих сигналов.

Это осуществляется следующим обра0 зом.

Рассмотрим сначала определение числа нулей 1-го порядка, i 2:1 повторно-разностного центрированного входного сигнала. С входа 10 на тактовый вход счетчика 2

5 поступает непрерывная последовательность импульсов, частота которых определяется частотной дискретизацией входного сигнала при дельта-модуляции и соответствует отсутствию перегрузки по

0 крутизне центрированного входного сигнала с блока 1. За время интервала реализации 0 TN в первом блоке 3.1 при помощи компаратора 16 и счетчика 21 производится подсчет пересечения входным центриро5 ванным сигналом нулевого уровня (из плюса в минус и из минуса в плюс). В конце интервала реализации Э по переднему фронту импульса с выхода счетчика 2 содержимое счетчика 21 записывается в регистр 22, а

0 счетчик 21 обнуляется, т.е. подготавливается к следующему циклу накопления. Таким образом, на выходах 26 регистра 22 блока 3.1 формируется число нулей первого порядка DI центрированного входного сигна5 ла, которое сохраняется на этих выходах в течение следующего интервала реализации.

Во втором блоке 3.2 центрированный входной сигнал подвергается дискретиза- 0 ции и квантованию с частотой Т при помощи дельта-модулятора 27, на дельта-кодовых выходах 31 которого формируется знак и абсолютное значение приращения входного сигнала по правилу

5

dm(x)Em(d)ENT(

)

I Xm - xm I Щ

+0,5),

его знак;

где - численное значение шага квантования;

0 - А

Xm. xm - отсчет входного сигнала и его оценка в моменты дискретизации;

ENTO - целая часть величины (.);

Дл1ггх минимальный ненулевой шаг 5 квантования.

Использование дельта-модулятора 27 с нечетным числом уровней квантования приводит при постоянном значении входного центрированного сигнала к формированию последовательности значений {dmw} {0} и

не приводит к изменению знака шага квантования. Последовательность {Dm } является последовательностью, соответствующей первой разности дискретизированного и квантованного центрированного входного сигнала, т.е. аппроксимирует первую производную указанного сигнала. Поэтому изменение знака в последовательности {dm xfy соответствует измению знака производной и подсчитывается за интервал реализации счетчиком 21. В конце интервала реализации по импульсу с выхода переполнения счетчика 2 накопленное в счетчике 21 значения записывается в регистр 22, а счетчик 21 обнуляется, чем подготавливается к следующему периоду накопления. Таким образом, на выходах 35 регистра 22 блока 3.1 формируется число нулей D2 второго порядка, которое сохраняется на эти выходах в течение следующего интервала реализации.

Формирование числа нулей более высоких порядков рассмотрим на примере блока 3.1 с . Последовательность значений {dm }. поступающая с выходов блока 3.2, стробиру- етсй в регистре 34, в результате чего за период дискретизации Т на входах и выходах этого регистра 34 присутствуют значения dm и dm-1 поступающие на входы вычитателя 35. Вычитатель 35 осуществляет вычитание значения dm-1 из значения dm , т.е. формирует

Дх).

разностную операцию V. rdm-r которая при соответствует формированию второй разности дискретизированного и квантованного центрированного входного сигнала. Изменение знака сигнала { vxm} (из минуса в плюс и из плюса в минус) подсчитывается счетчиком 21 за интервал реализаций 0 и записывается по сигналу с выхода переполнения счетчика 2 в конце интервала реализации в регистр 22, а счетчик 21 обнуляется, чем подготавливается к новому циклу накопления. Блоки 3.1, 3 работают аналогично, формируя разностную операцию

V xm HtK У Хт)--7 tf ZXm-1

и подсчитывая изменение знака сигнала { за интервал реализации 0 . Поэтому на выходах 40 регистра 22 блока 3.1 (информационных выходах 12.1- 12,М) фильтра формируется число нулей повторно-разностного сигнала 1-го порядка, которое сохраняется на этих выходах в течение следующего интервала реализации.

Во втором блоке 3.2 на вторых импуль- сно-кодовомодулированных выходах 32 дельта-модулятора 27 формируется знак и абсолютное значение входного сигнала по правилу

PmM EmWENT(),5),

где Р,

(х)

численное значение отсчета

5

входного сигнала,

EmW - его знак.

Последовательность значений {Рт } поступает на первые информационные входы первого блока 6 мультиплексирования, на вторые информационные входы которого поступает последовательность шагов {dm } с дельта-кодового выхода 31 дельта-модулятора 27.

На выходах 39 вычитателя 35 блоков 3.1. М формируется последовательность значений повторно-разностного входного центрированного сигнала 1-го порядка 1хт}, который поступает на соответствующие информационные входы первого блоп ка6 мультиплексирования.

Таким образом, при значении на управляющих входах 11, равном q, на выходах первого блока 6 мультиплексирования, формируется последовательность значений повторно-разностного сигнала q-ro порядка, который обозначим через .

В блоках 4.j, ,K производится определение числа нулей (+1)-го порядка j+iDq, j 1 повторно-разностно-суммарного ценп трированного входного сигнала следующим образом.

Формирование числя нулей повторно- разностно-суммарного сигнала ()+1}-го порядка J+1Dq, рассмотрим на примере блока

4.1.

Последовательнсть значений (V4 хт), поступающая с выходов блока 6 мультиплексирования, стробируется в регистре 34 блока 4.1, в результате чего за период диск- ретизации Т на входах и выходах этого регистра 34 присутствуют значения и V4 Хт-1. поступающие на входы сумматора 41. Блок 41 осуществляет суммирование этих значений, т.е. формирует операцию по5 вторного суммирования A Cf хт+К/ ХпИ, которая при соответствует формированию первой суммы дискретизи- рованной и квантованной q-ой разности центрированного входного сигнала. Изме0 нение знака сигнала { Д (47q 1xm)} (из минуса в плюс и из плюса в минус) подсчитывается счетчиком 21 за интервал реализации и записывается по сигналу с выхода переполнения счетчика 2 в конце

g интервала реализации в регистр 22, а счетчик 21 обнуляется, чем подготавливается к новому циклу накопления.

Блоки 4.J с работают аналогично. Таким образом, на выходах 46 выходного буферного регистра 22 (выходах 12.(М+1)12,(М+К) фильтра) блока 4.J формируется число нулей повторно-разностно-суммарно- го входного сигнала Q+1)-ro порядка J+1Dq, которое сохраняется на этих выходах в течение следующего интервала реализации.

На этом интервале реализации производится сравнение числа нулей высоких порядков {Di} и {j+iDq} входного сигнала с заданными следующим образом.

Указанные числа нулей поступают на первые информационные входы 50 блоков 5, на вторые информационные входы 51.1 подано значение верхней границы числа нулей, а на третьи информационные входы 51.2 подано значение нижней границы числа нулей соответствующего порядка эталонного сигнала. При наличи на разрешающем входе 52 блока 5 единичного значения сигнала и значения нулей входного сигнала соответствующего порядка, находящегося в указанных пределах, на выходах элементов 47 и 48 сравнения формируется единичное значение сигнала, из которого на выходе 53 элементом 49 И также формируется единичное значение, показывающее совпадение входного и эталонного сигналов для заданного порядка числа нулей.

Выходные сигналы блоков 5 сравнения поступают на информационные входы второго блока 7 мультиплексирования, адресные входы которого объединены с адресными входами первого блока 6 мультиплексирования, благодаря чему сравнение числа нулей производится для тех же порядков, для которых вычисляются повтор- но-рззностно-суммарные сигналы. Кроме того, поскольку числу нулей является монотонной функцией от их порядка, причем для повторно-разностных сигналов Dq Dq-i, ,M, а для повторно-разностно-суммар- ных сигналов j-nDq jDq, ,K-1, сравнение числа нулей входного и эталонного сигналов прекращается после первого же несовпадения.

Число последовательных единичных значений на выходах 15 фильтра (с учетом значения сигнала на управляющих входах 11 фильтра) показывает степень совпадения входного и эталонного сигналов.

Таким образом, за счет введения в известное устройство соответствующих блоков и связей в цифровом фильтре определяется число нулей первого и более высоких коряд- ков повторно-разностного, повторно-сумма- торного и повторно-разностно-суммарного входного сигнала, соответствующих заданному интервалу реализации. Для получения достоверных значений числа нулей значения М и К ограничены M,, а К М. Это позволяет определить соотношения между числом нулей соответствующих порядков, которые используются для получения корреляционных и спектральных характеристик исследуемого случайного сигала по указанным соотношениям, используя принцип доминирующей частоты. Число одновременно включенных вычислительных блоков 3 и 4 позволяет проводить параллельный анализ числа нулей входного сигнала и соответству0 ет порядку анализируемых нулей. Указанные соотношения могут также использоваться для идентификации сигналов по их корреляционным и спектральным характеристикам, например, в устройствах

5 сжатия данных и обработки изображений, причем, такой анализ и идентификация являются значительно более точными, чем при использовании для анализа спектра только числа нулей повторно-разностного сигнала,

0 так как в этом случае не имеется пропусков отдельных низкочастотных гармоник, обладающих малой мощностью по сравнению с дру- гими. Дополнительно отметим, что совместный анализ числа нулей высоких по5 рядков повторно-разностного, повторно-суммарного и повторно-разностно-суммарного сигналов позволяет точнее определить все гармоники в спектре входного сигнала, чем при отдельном использовании повторно-раз0 ностных сигналов, так как повторно-разност- но-суммарный сигнал соответствующего порядка обладает значительно большей информативностью повторно суммарного и повторно-разностно-суммарного сигналов

5 благодаря возможности более тонкого (например, в заданной частотной полосе) спектрального анализа входного сигнала.

Сравнение числа нулей входного аналогового сигнала с соответствующими числа0 ми нулей эталонного сигнала позволяет определить с заданным допуском соответствие входного сигнала заданному.

Таким образом, за счет введения в известное устройство указанных узлов с соот5 ветствующими связями полностью достигается поставленная цель - расширяются функциональные возможности устройства за счет определения числа нулей высоких порядков на интервале реализации

0 повторно-суммарных и повторно-разност- но-суммарных входных сигналов. Формула изобретения 1. Цифровой фильтр, содержащий блок центрирования, вход которого является ин5 формационным входом фильтра, выход блока центрирования соединен с информационным входом первого вычислительного блока, первый выход которого подключен к информационному входу второго вычислительного блока, тактовый вход которого объединен с тактовыми входами третьего - M-го вычислительных блоков (М 3) и входом счетчика интервала реализации и является тактовым входом фильтра, первый блок сравнения, первый и второй блоки мультиплексирования, адресные входы которых соответственно объединены, выход счетчика интервала реализации подключен к входам синхронизации первого - M-го вычислительных блоков, первые выходы каждого из второго - (М-1)-го вычислительных блоков соединены с информационными входами последующего вычислительного блока, вторые выходы первого - М-го вычислительных блоков являются соответствующими выходами первой группы информационных выходов фильтра, отличающий с я тем, что, с целью расширения функциональных возможностей за счет определения числа нулей высоких порядков повторно-суммарных и повторно-разностно-суммарных входных сигналов на интервале реализации, в фильтр введены (М+1)-й-(М+К)-й вычислительные блоки (К 2), второй - (М+К)-й блоки сравнения и источник логической единицы, выход которого соединен с разрешающим входом первого блока сравнения, первые информационные входы первого - M-го блоков сравнения подключены к вторым выходам одноименных вычислительных блоков, третьи выходы второго вычислительного блока соединены с первыми информационными входами первого блока мультиплексирования, вторые - М-е информационные входы которого подключены к первым выходам соответственно второго - M-го вычислительных блоков, выходы первого блока мультиплексирования соединены с информационными входами (М+1)-го вычислительного блока, первые выходы каждого из (М+1)-го - (М+К-1)то вычислительных блоков подключены к информационным входам последующего вычислительного блока, первые выходы (М+К)-го вычислительного блока являются информационными выходами фильтра, вторые выходы (М+1)-го-(М+К}-го вычислительных блоков соединены с первыми информационными входами одноименных блоков сравнения и являются соответствующими выходами второй группы информационных выходов фильтра, тактовые входы синхронизации (М+1)-го-(М+К)-го вычислительных блоков подключены соответственно к тактовому входу фильтра и выходу счетчика интервала реализации, выход каждого из первого - (М-1)-го блоков сравнения соединен с соответствующим информационным входом второго блока мультиплексирования, входом разрешения последующего

блока сравнения и является соответствующим выходом первой группы контрольных выходов фильтра, выход M-го блока сравнения подключен к соответствующему инфор5 мационному входу второго блока мультиплексирования и является соответствующим выходом первой группы контрольных выходов фильтра, адресные входы .блоков мультиплексирования соответствен0 но объединены и являются управляющими входами фильтра, выход второго блока мультиплексирования подключен к входу разрешения (М+1)-го блока сравнения, выход каждого из (М+1}-го-{М+К.)-го блоков

5 сравнения соединен с входом разрешения последующего блока сравнения и является соответствующим выходом второй группы контрольных выходов фильтра выход (М+К)- го блока сравнения является соответствую0 щим выходом второй группы контрольных выходов фильтра, вторые и третьи информационные входы всех блоков сравнения являются входами задания соответственно верхних и нижних пределов числа нулей со5 ответствующих порядков фильтра.

2. Фильтр по п. 1, о т л и ч а ю щ и и с я тем, что второй вычислительный блок содержит выделители переднего фронта, выделитель заднего фронта, элемент ИЛИ, счетчик

0 импульсов, буферный регистр и многоуровневый дельта-модулятор, информационный вход которого является информационным входом блока, первые и вторые выходы многоуровневого дельта-модулятора являются

5 соответственно первыми и третьими выходами блока, входы первого выделителя переднего фронта и выделителя заднего фронта подключены к знаковому разряду первых выходов многоуровневого дельта0 модулятора, тактовый вход которого является тактовым входом блока, выход первого выделителя переднего фронта и выделителя заднего фронта соединены с входами элемента ИЛИ, выход которого подключен к

5 съемному входу счетчика импульсов, выходы которого соединены с информационными входами буферного регистра, управляющий вход которого и вход второго выделителя переднего фронта объединены

0 и являются входом синхронизации блока, выход второго выделителя переднего фронта подключен к входу обнуления счетчика импульсов, выходы буферного регистра являются вторыми выходами блока.

5 3. Фильтр по п.1,отличающийся тем, что каждый из (М+1)-го-(М+К)-го вычислительных блоков содержит выделители переднего фронта, выделитель заднего фронта, элемент ИЛИ, счетчик импульсов,

входной и выходной буферные регистры и

сумматор, первые входы которого соответственно объединены с информационными входами входного буферного регистра и являются информационными входами блока, выходы входного буферного регистра соединены с вторыми входами сумматора, выходы которого являются первыми выходами блока управляющий вход входного буферного регистра является тактовым входом блока, входы первого выделителя переднего фронта и выделителя заднего фронта подключены к знаковому разряду выходов сумматора, выходы первого выделителя переднего фронта и выделителя заднего фронта соединены с входами элемента ИЛИ, выход которого подключен к счетному входу счетчика импульсов, выходы которого соединены с информационными входами выходного буферного регистра, управляющий вход которого объединен с входом второго выделителя переднего фронта и является входом синхронизации блока, выход второго выделителя переднего фронта подключен к входу обнуления счетчика импульсов, выходы выходного буферного регистра являются вторыми выходами блока.

4. Фильтр по п.1,отличающийся тем, что блок сравнения содержит элемент И и первый и второй элементы сравнения, входы разрешения которых объединены и являются входом разрешения блока, первые информационные входы первого элемента сравнения являются вторыми информационными входами блока, вторые информационные входы первого и первые информационные входы второго элементов

сравнения соответственно объединены и являются первыми информационными входами блока, вторые информационные входы второго элемента сравнения являются третьими информационными входами блока, выход Меньше первого и выход Больше второго элементов сравнения соединены с входами элемента И, выход которого является выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр | 1990 |

|

SU1758836A1 |

| Цифровой фильтр | 1990 |

|

SU1736002A2 |

| Цифровой фильтр | 1989 |

|

SU1695493A2 |

| Цифровой фильтр | 1989 |

|

SU1695492A2 |

| Цифровой фильтр | 1989 |

|

SU1695323A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1987 |

|

SU1481893A1 |

| Цифровой фильтр с симметричной импульсной характеристикой | 1987 |

|

SU1495979A1 |

| Цифровой фильтр | 1986 |

|

SU1387174A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1989 |

|

SU1631707A1 |

| Цифровой фильтр | 1987 |

|

SU1425840A1 |

Изобретение относится к автоматике, вычислительной и измерительной технике. Его использование в системах сжатия данных и обработки изображений, корреляционного и спектрального анализа позволяет расширить функциональные возможности фильтра за счет определения числа нулей высоких порядков повторно-суммарных и повторно-разностно-суммарных входных сигналов на интервале реализации. Цифровой фильтр содержит блок 1 центрирования, счетчик 2 интервала реализации, вычислительные блоки 3, блок 5.1 сравнения и блоки 6, 7 мультиплексирования. Поставленная цель достигается благодаря введению вычислительных блоков 4, блоков 5 сравнения и источника 8 логической единицы, а также специфического выполнения вычислительных блоков и блоков сравнения. 3 з.п.ф-лы, бил.

И 2

Фиг. 6

4U.4

Фиг. 5

| Авторское свидетельство СССР Ms 1568213, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровой фильтр | 1989 |

|

SU1695493A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1993-05-15—Публикация

1990-12-13—Подача