сл

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения характеристик синусоидального сигнала | 1990 |

|

SU1758575A1 |

| Устройство для измерения фазовых сдвигов | 1984 |

|

SU1226341A1 |

| Устройство для регистрации одиночных ударов | 1987 |

|

SU1479878A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2500025C2 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ ПОМЕХ | 1990 |

|

RU2074516C1 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ КОЭФФИЦИЕНТА ГАРМОНИКИ НАПРЯЖЕНИЯ | 1990 |

|

RU2030753C1 |

| ЦИФРОВОЙ ДАЛЬНОМЕР | 1992 |

|

RU2069003C1 |

| Умножитель частоты следования импульсов | 1989 |

|

SU1728964A2 |

Изобретение относится к измерительной технике и предназначено для измерения параметров амплитудно-модулированных сигналов, а именно глубины модуляции и амплитуды несущей. Глубина модуляции исследуемого амплитудно-модулированного сигнала определяется по одному объему выборки отсчетов амплитуд несущей амплитудно-модулированного сигнала, получаемому в течение одного периода огибающей, Измеритель содержит аналого-цифровой преобразователь 1, задатчик 2, моментов измерений, делитель 3, сумматор 4, демуль- типлексор 5, оперативное запоминающее устройство 6, вычитатель 7, квадратор 8, сумматор 9, блок 10 извлечения квадратного корня, блок 11 деления, реверсивный счетчик 12 адреса, элемент И 13, триггер 14, элемент ИЛИ 15. 1 ил.

j

Сл)

1

Сл) VI О

Изобретение относится к измерительной технике и предназначено для измерения параметров амплитудно-модулированных (AM) сигналов, а именно: глубины модуляции и амплитуды несущей.

Цель изобретения - повышение точности измерений за счет исключения методической погрешности и уменьшение времени измерений.

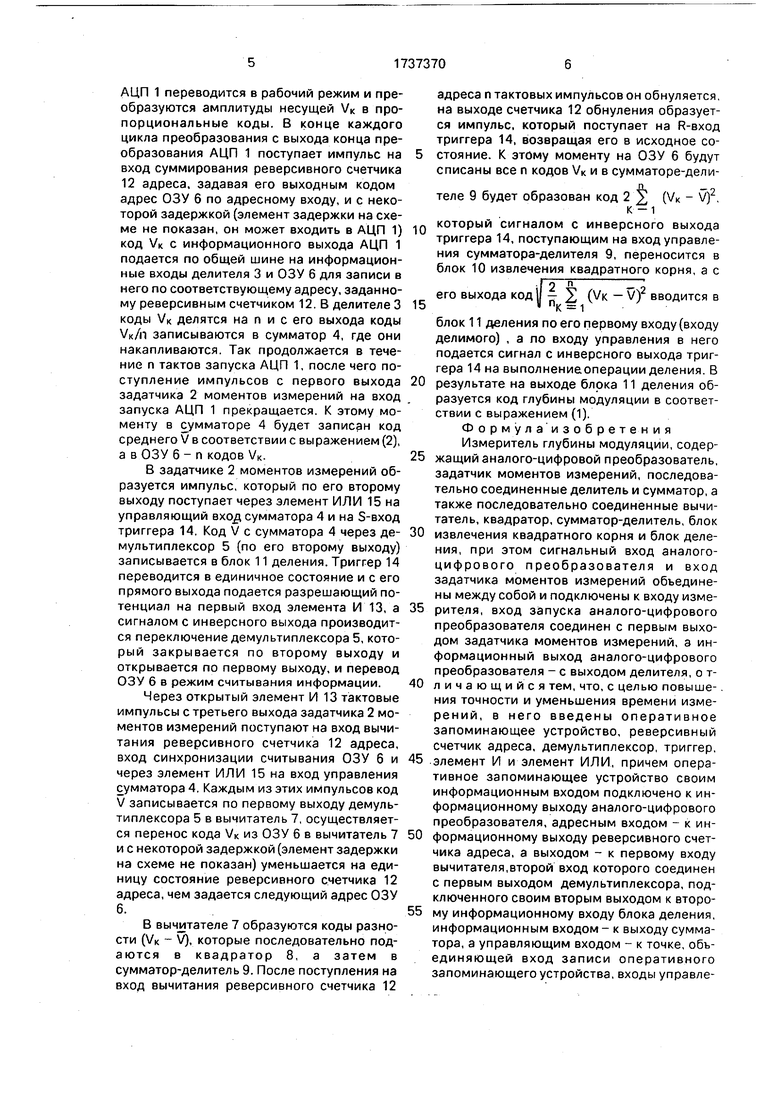

На чертеже приведена структурная электрическая схема измерителя глубины модуляции.

Измеритель глубины модуляции содержит аналого-цифровой преобразователь (АЦП) 1, задатчик 2 моментов измерений, делитель 3, сумматор 4, демультиплексор 5, оперативное запоминающее устройство (ОЗУ) 6, вычитатель 7, квадратор 8, сумматор-делитель 9, блок 10 извлечения квадратного корня, блок 11 деления, реверсивный счетчик 12 адреса, элемент И 13, триггер 14 и элемент ИЛИ 15.

Вход измерителя соединен с точкой, объединяющей сигнальный вход АЦП 1 и вход задатчика 2 моментов измерений, первый выход которого подключен к входу управления (или входу запуска) АЦП 1, Информационный выход АЦП 1 соединен через общую шину с информационными входами делителя 3 и ОЗУ 6, выход которого подключен к входу (входу суммирования) вычитателя 7. Делитель 3 имеет постоянный коэффициент деления п, его выход подключен к информационному входу сумматора 4, выход которого соединен с информационным входом демультиплексора 5. Первый выход демультиплексора 5 подключен к второму входу (входу вычитания) вычитателя 7, выход которого соединен через квадратор 8, сумматор-делитель 9, блок 10 извлечения квадратного корня с первым информационным входом (входом делимого) блока 11 деления, второй информационный вход (вход делителя) которого подключен к второму выходу демультиплексора 5. Адресный вход ОЗУ 6 соединен с информационным (кодовым) выходом реверсивного счетчика 12 адреса, вход суммирования которого подключен к выходу конца преобразователя АЦП 1, вход вычитания - к точке, объединяющей один из входов элемента ИЛИ 15, выход которого соединен с входом управления сумматора 4, вход синхронизации считывания оперативного запоминающего устройства 6 и выход элемента И 13. Выход обнуления счетчика 12 соединен с R-входом триггера 14, S-вход которого объединен с другим входом элемента ИЛИ 15 и соединен с вторым выходом задатчика 2 моментов измерений. Прямой выход триггера 14 подключен к первому входу элемента И 13, второй вход которого соединен с третьим входом задатчика 2 моментов измерений. Инверсный выход триггера 14 подключен к

точке, объединяющей вход управления демультиплексора 5, вход управления записи ОЗУ 6, вход управления сумматора-делителя 9 и вход управления блока 11 деления. Принцип действия измерителя модуляции основан на определении глубины модуляции AM сигнала по формуле КАМОД/ТТГ

м

f S/W-V)2,

.1;

где VK - коды амплитуд несущей в п точках отсчета tK за период огибающей, т е. k - 1, п;,

V - среднее значение AM сигнала или амплитуда несущей в отсутствии модуляции, определяется соотношением

vk,(с)

пк 1

Камод - коэффициент амплитуды модулирующего сигнала или огибающей.

Измеритель работает следующим образом.

Амплитудно-модулированный сигнал U(t) подается на объединенные между собой сигнальный вход АЦП 1 и вход задатчика 2

моментов измерений. В исходном состоянии АЦП 1 находится в ждущем режиме, потенциалом с прямого выхода триггера 14 элемент И 13 закрыт по первому входу, потенциалом с инверсного выхода триггера 14

демультиплексор 5 открыт по второму выходу, а ОЗУ 6 установлено в режим записи кодов. Реверсивный счетчик 12 адреса, сумматор 4, вычитатель 7, сумматор-делитель 9 обнулены.

в задатчике 2 моментов измерений выделяются моменты времени тк. , соответствующие амплитудам VK несущей AM сигнала, и в эти моменты времени формируются импульсы запуска АЦП 1, но на вход

запуска АЦП 1 они в исходном состоянии не подаются.

Исходное состояние схемы измерителя задается импульсом сброса, формируемым в задатчике 2 моментов измерений (шина

сброса не показана).

Процесс измерений начинается по сигналу пуска, который образуется либо от кнопки Пуск или тактового генератора в задатчике 2 моментов измерений, либо поступает на него дистанционно от внешнего источника.

На вход запуска АЦП 1 с первого выхода задатчика 2 моментов измерений t« поступает п импульсов запуска, каждым из них

АЦП 1 переводится в рабочий режим и преобразуются амплитуды несущей VK в пропорциональные коды. В конце каждого цикла преобразования с выхода конца преобразования АЦП 1 поступает импульс на вход суммирования реверсивного счетчика 12 адреса, задавая его выходным кодом адрес ОЗУ 6 по адресному входу, и с некоторой задержкой (элемент задержки на схеме не показан, он может входить в АЦП 1) код VK с информационного выхода АЦП 1 подается по общей шине на информационные входы делителя 3 и ОЗУ 6 для записи в него по соответствующему адресу, заданному реверсивным счетчиком 12. В делителе 3 коды VK делятся на п и с его выхода коды VK/n записываются в сумматор 4, где они накапливаются. Так продолжается в течение п тактов запуска АЦП 1, после чего поступление импульсов с первого выхода задатчика 2 моментов измерений на вход запуска АЦП 1 прекращается. К этому моменту в сумматоре 4 будет записан код среднего V в соответствии с выражением (2), а в ОЗУ 6 - п кодов VK.

В задатчике 2 моментов измерений образуется импульс, который по его второму выходу поступает через элемент ИЛИ 15 на управляющий вхО|Д сумматора 4 и на S-вход триггера 14, Код V с сумматора 4 через де- мультиплексор 5 (по его второму выходу) записывается в блок 11 деления. Триггер 14 переводится в единичное состояние и с его прямого выхода подается разрешающий потенциал на первый вход элемента И 13, а сигналом с инверсного выхода производится переключение демультиплексора 5, который закрывается по второму выходу и открывается по первому выходу, и перевод ОЗУ 6 в режим считывания информации.

Через открытый элемент И 13 тактовые импульсы с третьего выхода задатчика 2 моментов измерений поступают на вход вычитания реверсивного счетчика 12 адреса, вход синхронизации считывания ОЗУ 6 и через элемент ИЛИ 15 на вход управления сумматора 4. Каждым из этих импульсов код V записывается по первому выходу демультиплексора 5 в вычитатель 7, осуществляется перенос кода VK из ОЗУ 6 в вычитатель 7 и с некоторой задержкой (элемент задержки на схеме не показан) уменьшается на единицу состояние реверсивного счетчика 12 адреса, чем задается следующий адрес ОЗУ 6.

В выч тателе 7 образуются коды разности (VK - V), которые последовательно под- аются в квадратор 8, а затем в сумматор-делитель 9. После поступления на вход вычитания реверсивного счетчика 12

его

адреса п тактовых импульсов он обнуляется, на выходе счетчика 12 обнуления образуется импульс, который поступает на R-вход триггера 14, возвращая его в исходное состояние. К этому моменту на ОЗУ 6 будут списаны все п кодов VK и в сумматоре-делителе 9 будет образован код 2 jЈ (VK - V)2,

к - 1

который сигналом с инверсного выхода триггера 14, поступающим на вход управления сумматора-делителя 9, переносится в блок 10 извлечения квадратного корня, а с

выхода код У - У (VK - V)2 вводится в Ч пк 1

блок 11 деления по его первому входу (входу делимого) , а по входу управления в него подается сигнал с инверсного выхода триггера 14 на выполнениеоперации деления. В результате на выходе блока 11 деления образуется код глубины модуляции в соответствии с выражением (1).

Формулаизобретения Измеритель глубины модуляции, содержащий аналого-цифровой преобразователь, задатчик моментов измерений, последовательно соединенные делитель и сумматор, а также последовательно соединенные вычитатель, квадратор, сумматор-делитель, блок извлечения квадратного корня и блок деления, при этом сигнальный вход аналого- цифрового преобразователя и вход задатчика моментов измерений объединены между собой и подключены к входу измерителя, вход запуска аналого-цифрового преобразователя соединен с первым выходом задатчика моментов измерений, а информационный выход аналого-цифрового преобразователя - с выходом делителя, о т- личающийся тем, что, с целью повышения точности и уменьшения времени измерений, в него введены оперативное запоминающее устройство, реверсивный счетчик адреса, демультиплексор, триггер, элемент И и элемент ИЛИ, причем оперативное запоминающее устройство своим информационным входом подключено к информационному выходу аналого-цифрового преобразователя, адресным входом - к информационному выходу реверсивного счетчика адреса, а выходом - к первому входу вычитателя,второй вход которого соединен с первым выходом демультиплексора, подключенного своим вторым выходом к второму информационному входу блока деления, информационным входом - к выходу сумматора, а управляющим входом - к точке, объединяющей вход записи оперативного запоминающего устройства, входы управления блока деления и сумматора-делителя и инверсный выход триггера, прямой выход которого соединен с первым входом элемента 1/1,Р-вход триггера подключен к выходу обнуления реверсивного счетчика адреса.а S-вход объединен с первым входом элемента ИЛИ и подключен к второму выходу задатчика моментов измерений, третий выход которого соединен с вторым входом элемента И, подключенного своим выходом

0

к точке, объединяющей второй вход элемента ИЛИ, выход которого соединен с входом управления сумматора, вход синхронизации считывания оперативного запоминающего устройства и вход вычитания реверсивного счетчика адреса, вход суммирования которого соединен с выходом конца преобразования аналого-цифрового преобразователя.

| Измеритель глубины модуляции | 1978 |

|

SU721771A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-05-30—Публикация

1989-10-11—Подача