Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах с плавающей запятой, устройствах управления

Известно устройство для шифрации крайней единицы в n-разрядном двоичном коде, содержащее первую группу узлов частичной шифрации, группа входов первой группы узлов частичной шифрации является группой входов устройства, узел коммутации и вторую группу узлов частичной шифрации, причем первые, вторые и третьи выходы всех узлов частичной шифрации первой группы соединены с соответствующими группами входов узла коммутации, а их дополнительные выходы соединены с соответствующими входами узлов частичной шифрации второй группы, группа выходов второй группы узлов частичной шифрации соединена с группой управляющих входов узла коммутации и. с группой выходов устройства, группа выходов узла коммутации соединена с группой выходов устройства.

Недостатком указанного устройства является отсутствие возможности формирования выходного кода с разрядностью, не зависящей от разрядности входного кода, и произвольной кодировкой. Кроме того, указанное устройство не позволяет произвольно наращивать разрядность входного кода

Наиболее близким к предлагаемому по технической сущности является устройство прерывания, содержащее два регистра, группу элементов ИЛИ, группу элементов НЕ и три элемента И, причем входы второго регистра являются выходами устройства, прямые выходы 1-го и следующих разрядов первого регистра (, n - число запросов) соединены с входами i-ro и следующих элементов ИЛИ группы, устройство также содержит две группы элементов И-НЕ и элемент И-НЕ, причем выходы нечетных элементов ИЛИ группы соединены с первыми входами элементов И-НЕ первой группы, выходы J-x (. 6, 10 ) четных элементов ИЛИ группы через элементы НЕ группы соединены с вторыми входами эле(Л

С

х|

сл

„ VJ

СЛ 00

ментов И-НЕ первой группы, выходы К-х (, 8, 12...) четных элементов ИЛИ группы соединены с первыми входами элементов И-НЕ второй группы, выходы четных зле- ментоп ИЛИ группы, начиная с четвертого, через элементы НЕ группы соединены с пто рыми входами элементов И-МЕ второй группы, выход первого четного элемента ИЛИ группы соединен с первыми входом элемента И-НЕ, второй вход которого через четвертый элемент НЕ группы соединен с выходом второго черного элемента ИЛИ группы, выходы элементов И-НЕ первой группы соединены с входами первого элемента И, инверсный выход последнего раз ряда первого регистра соединен с входом первого элемента И, выходы элементов И-НЕ второй группы соединены с входами второго элемента И, выход последнего элемента ИЛИ группы через последний элемент НЕ группы соединен с входом второго элемента И, первый и второй входы третьего элемента И,соединены соответственно с выходом элемента И-НЕ и с выходом предпоследнего элемента НЕ группы, входы разрядов с первого по четвертый второго регистра соединены соответственно с выходами с первого по третий элементов И и с выходом четвертого элемента НЕ группы.

Недостатками известного устройства явпяются ограниченность функциональных возможностей, обусловленная строгой зависимостью кодировки и разрядное)и формируемого выходного кода от входного, и сысокие аппаратурные затраты.

Цель изобретения - расширение функциональных возможностей устройства путем формирования выходного кода произвольной разрядности и кодировки, сокращения аппаратурных затрат,

Поставленная цель достигается тем, что в устройство прерывания, содержащее группу элементов ИЛИ дополнительно введены группа элементов НЕРАВНОЗНАЧНОСТЬ, группа элементов НЕ и коммутатор, причем пыход первого элемента ИЛИ соединен с входом U1 первой группы управляющих входов KOMMyfaTopaY BxoA 1-го элемента неравнозначность группы (1-1...п- 2), где п - количество входов шифратора) соединен с входом U1 (Н-1)-й группы управляющих входов коммутатора и через 1-й элемент НЕ группы с входом U2 (П1)-й группы управляющих входов коммутатора, выход (п-1)-го элемента НЕРАВНОЗНАЧНОСТЬ группы соединен с входом (п-1)-го элемента НЕ группы, первый вход первого элемента ИЛИ группы соединен с первым информационным входом шифратора, вход логического нуля которого соединен с вторым

входом первого элемента ИЛИ группы, входы (.,.n) элемента ИЛИ группы соединен с первого по 1-го входами шифратора входы К-го элемента НЕРАВНОЗНАЧНОСТЬ группы ( ,.п-1) соединены с выходами К-ro и (Ю 1)-го элементов ИЛИ группы, выходы коммутатора являются выходами шифратора.

Кроме того, в шифраторе коммутатор

содержит п групп МДП-транзисторов и од2П шин, причем затворы п-канальных транзисторов 1-й группы соединены с входом U1 1-й группы управляющих входов коммутатора, затворы р-канальных

транзисторов 1-й группы соединены с входом U2 1-й группы управляющих входов коммутатора, истоки всех транзисторов являются информационными входами коммутатора, стоки транзисторов К.1-К.1од2П

(,.,п, К - номер группы транзисторов) соединены с шинами S ф S(log2n-1) соответст- венно, шины являются выходами коммутатора.

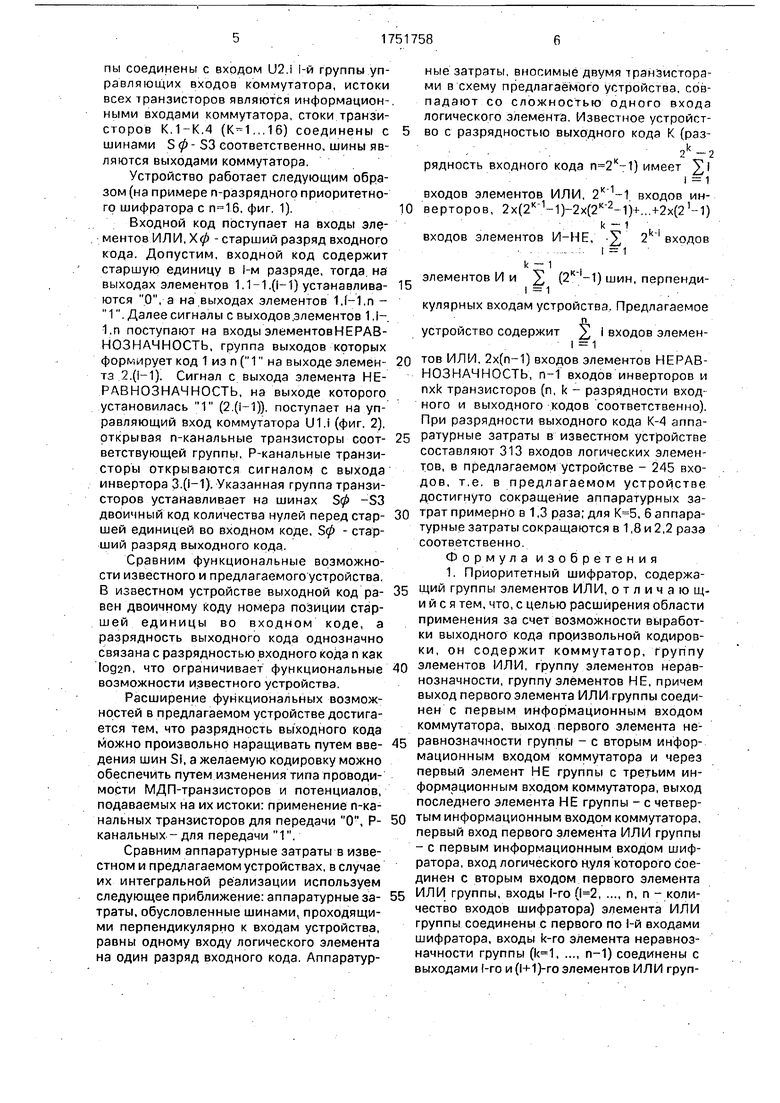

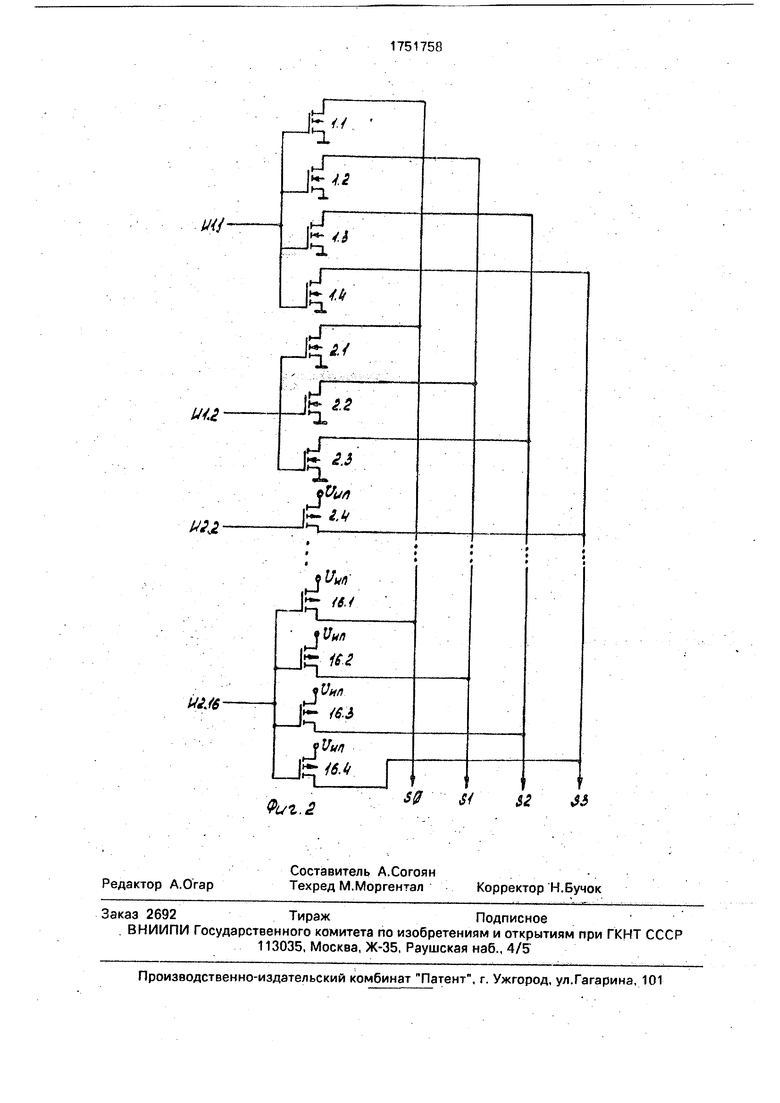

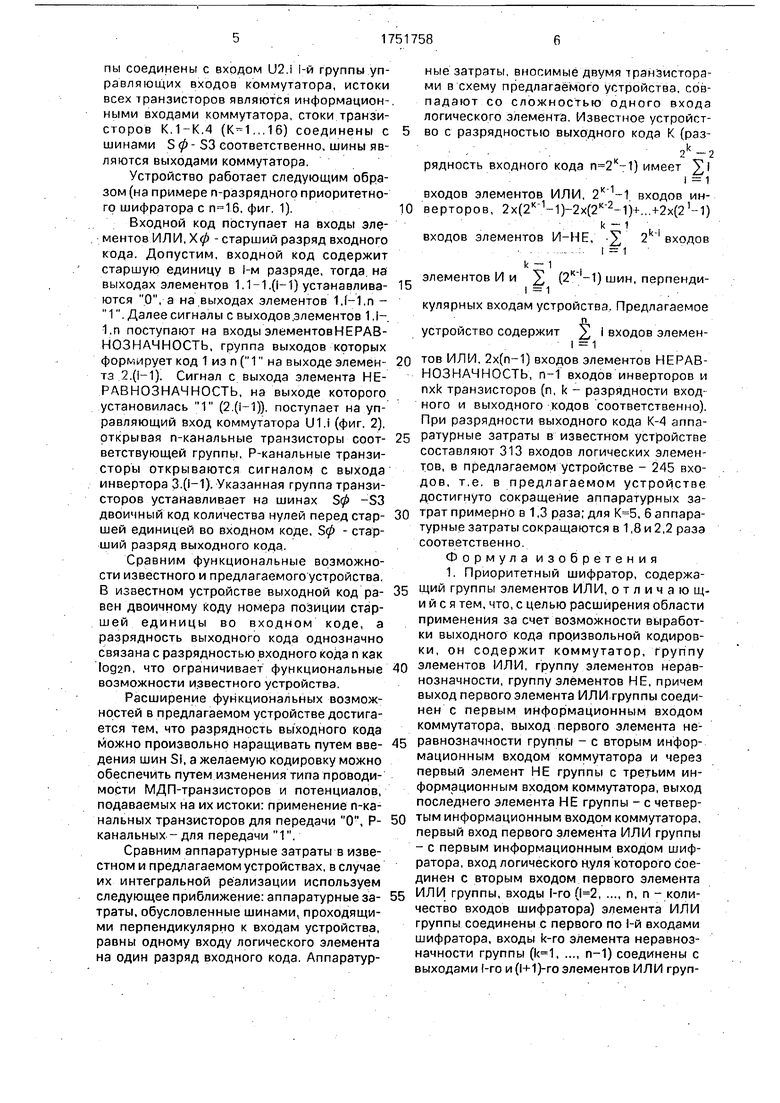

На фиг. 1 изображен приоритетный

шифратор для случая (п - разрядность входного кода).

Приоритетный шифратор содержит группу элементов ИЛИ 1.1-1.л, группу элементов НЕРАВНОЗНАЧНОСТЬ 2.1-2.(п-1).

группу инверторов 3.1-3.(п-1), коммутатор 4, причем выход первого элемента ИЛИ 1.1 соединен с входом U1.1 первой группы управляющих входов коммутатора, выход элемента НЕРАВНОЗНАЧНОСТЬ 2.I группы

(,..14) соединен с входом U1.(i+1)(it 1)-й группы управляющих входов коммутатора и через элемент НЕ 3.1 группы - с входом U2.(1-Й) (И 1)-й группы управляющих входов коммутатора, выход элемента НЕРАВНОЗНАЧНОСТЬ 2.15 соединен с входом элемента НЕ 3.15, первый вход элемента ИЛИ 1.1 соединен с первым информационным входом шифратора X ф , вход логического нуля которого соединен с вторым входом элемента 1.1, входы элемента ИЛИ 1.1 соединены с входами шифратора Хф -Х(Ы), входы элемента НЕРАВНОЗНАЧНОСТЬ 2.К(.. 15) соединены с выходами элементов ИЛИ 1.К и 1.(К+1), выходы коммутатора S S3 являются выходами шифратора.

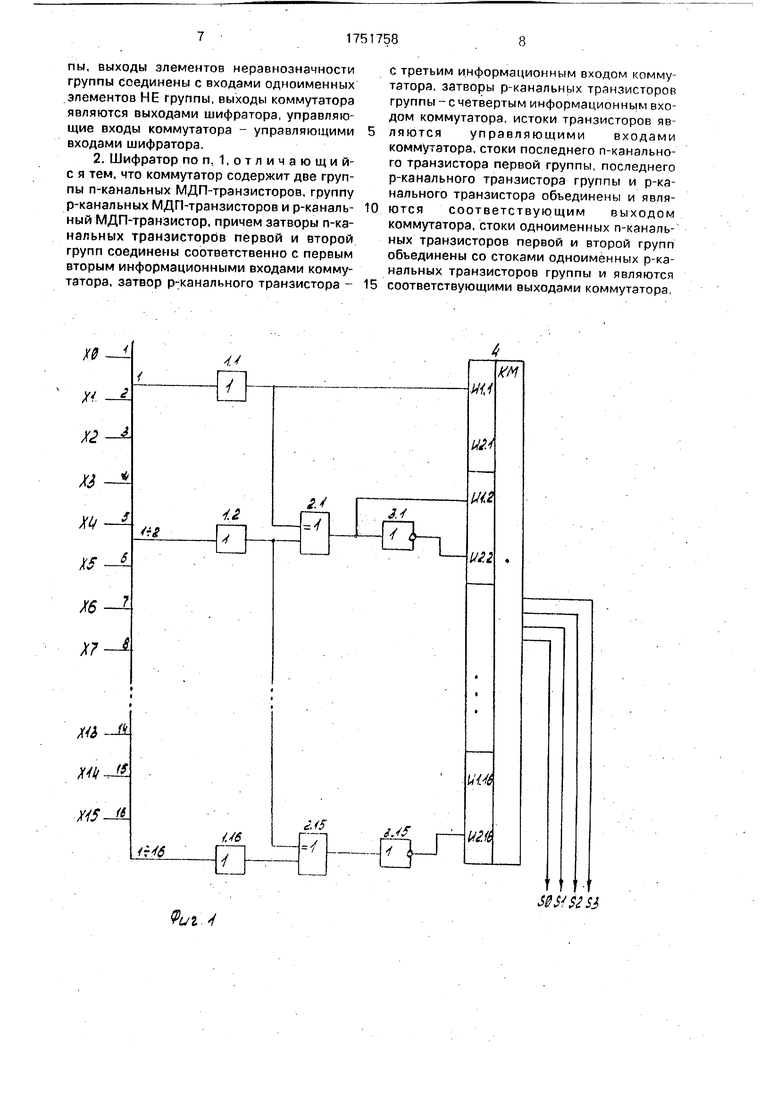

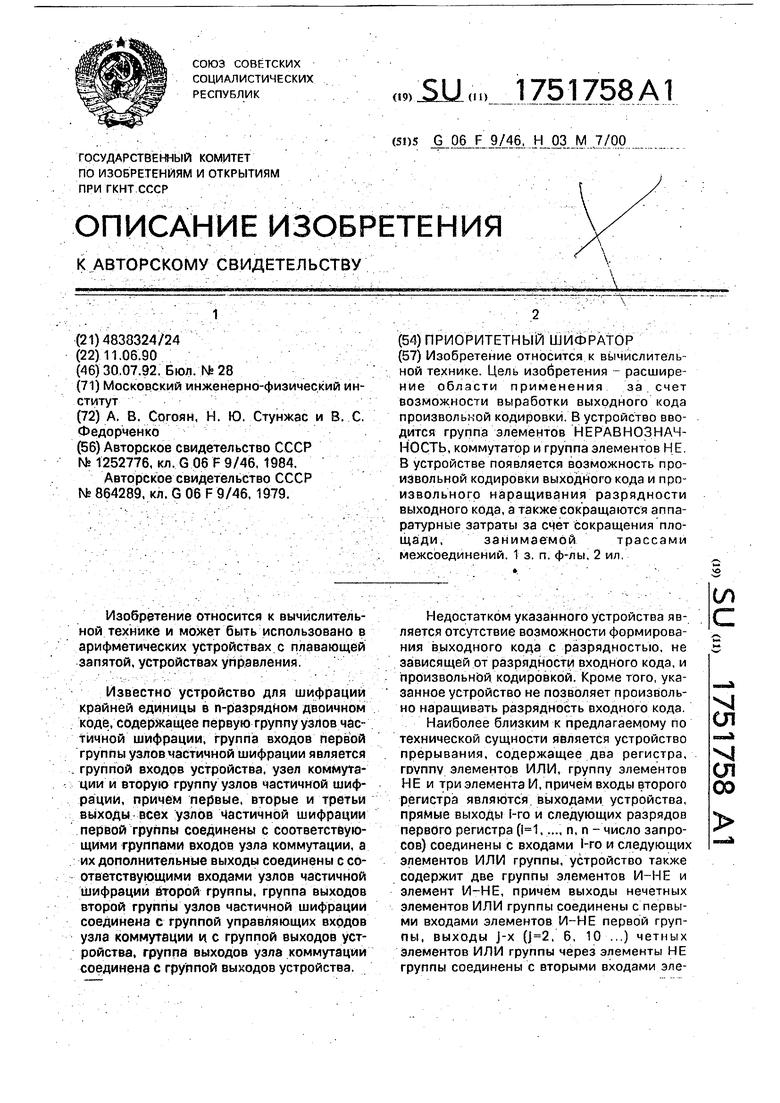

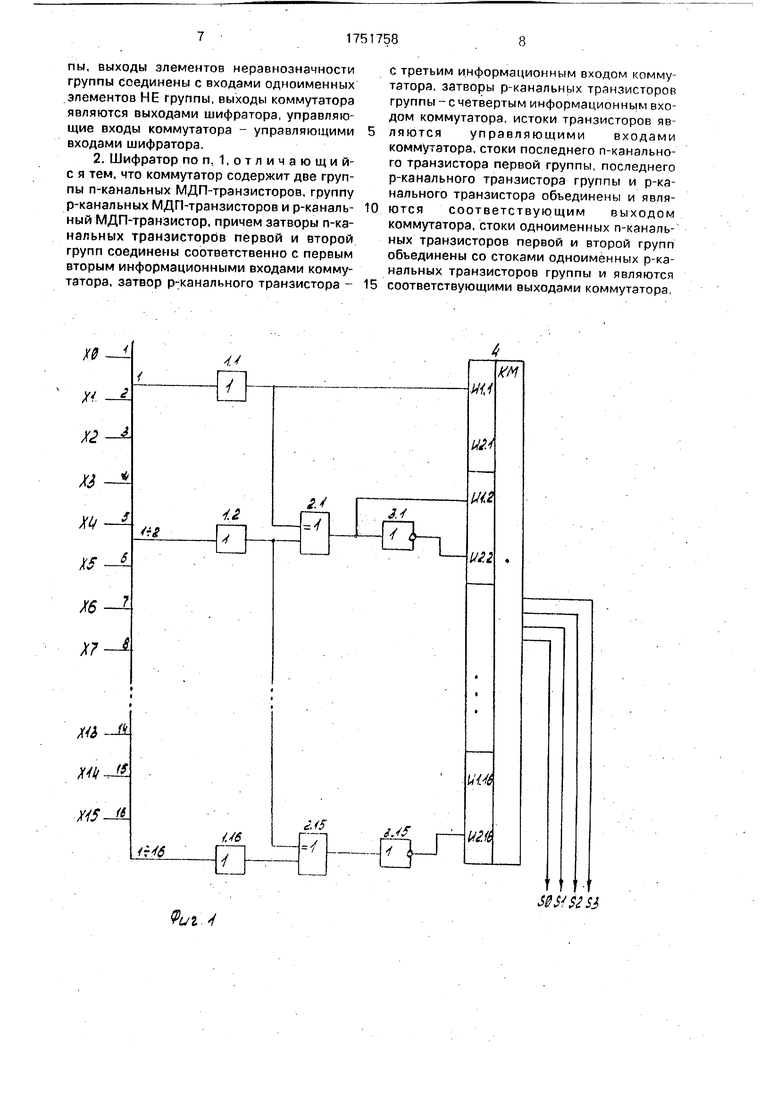

На фиг. 2 изображен коммутатор для случая (п - разрядность входного кода приоритетного шифратора).

Коммутатор содержит 16 групп МДПтранзисторов и четыре шины 5ф -S3, причем затворы n-канальных транзисторов 1-й группы (...15) соединены с входом U1 i 1-й группы управляющих входов коммутатора, затворы р-канальных транзисторов 1-й труппы соединены с входом U2.i 1-й группы управляющих входов коммутатора, истоки всех транзисторов являются информационными входами коммутатора, стоки транзисторов К.1-К.4 (КМ...16) соединены с шинами S ф - S3 соответственно, шины являются выходами коммутатора.

Устройство работает следующим образом (на примере n-разрядного приоритетного шифратора с , фиг. 1).

Входной код поступает на входы элементов ИЛИ, Хф - старший разряд входного кода. Допустим, входной код содержит старшую единицу в l-м разряде, тогда на выходах элементов 1.1-1.(i-1) устанавливаются О, а на выходах элементов 1.1-1,п - 1. Далее сигналы с выходов.злементов 1.I-. 1.п поступают на входы элементовНЕРАВ- НОЗНАЧНОСТЬ, группа выходов которых формирует код 1 из п ( 1 на выходе элемента 2.(1-1). Сигнал с выхода элемента НЕРАВНОЗНАЧНОСТЬ, на выходе которого установилась 1 (2 (i-1)). поступает на управляющий вход коммутатора U1.I (фиг. 2), открывая n-канальные транзисторы соответствующей группы, Р-канальные транзисторы открываются сигналом с выхода инвертора 3.(i-1). Указанная группа транзисторов устанавливает на шинах S0 -S3 двоичный код количества нулей перед старшей единицей во входном коде, Зф - старший разряд выходного кода.

Сравним функциональные возможности известного и предлагаемого устройства. В известном устройстве выходной код равен двоичному коду номера позиции старшей единицы во входном коде, а разрядность выходного кода однозначно связана с разрядностью входного кода п как logan, что ограничивает функциональные возможности известного устройства.

Расширение функциональных возможностей в предлагаемом устройстве достигается тем, что разрядность выходного кода можно произвольно наращивать путем введения шин Si, а желаемую кодировку можно обеспечить путем изменения типа проводимости МДП-транзисторов и потенциалов, подаваемых на их истоки: применение п-ка- нальных транзисторов для передачи О, Р- канальных - для передачи 1.

Сравним аппаратурные затраты в известном и предлагаемом устройствах, в случае их интегральной реализации используем следующее приближение: аппаратурные затраты, обусловленные шинами, проходящими перпендикулярно к входам устройства, равны одному входу логического элемента на один разряд входного кода. Аппаратурные затраты, вносимые двумя транзисторами в схему предлагаемого устройства, совпадают со сложностью одного входа логического элемента. Известное устройст- во с разрядностью выходного кода К (разь2-2

рядность входного кода ) имеет У I

i 1

входов элементов ИЛИ, входов ин- 0 верторов, 2x()-2x()f...+2x(21-1)

k - 1

входов элементов И-НЕ, 2й входов

I 1

k - 1

элементов И и (2 -1) шин. перпенди151 1

кулярных входам устройства. Предлагаемое

устройство содержит Ј входов элеменI 1

тов ИЛИ, 2х(п-1) входов элементов НЕРАВНОЗНАЧНОСТЬ, п-1 входов инверторов и nxk транзисторов (n, k - разрядности входного и выходного кодов соответственно). При разрядности выходного кода К-4 аппаратурные затраты в известном устройстве составляют 313 входов логических элементов, в предлагаемом устройстве - 245 входов, т.е. в предлагаемом устройстве достигнуто сокращение аппаратурных затрат примерно в 1,3 раза; для . 6 аппаратурные затраты сокращаются в 1,8 и 2,2 раза соответственно.

Формула изобретения

1. Приоритетный шифратор, содержаЩий группы элементов ИЛИ, отличающийся тем, что, с целью расширения области применения за счет возможности выработки выходного кода произвольной кодировки, он содержит коммутатор, группу

элементов ИЛИ, группу элементов неравнозначности, группу элементов НЕ, причем выход первого элемента ИЛИ группы соединен с первым информационным входом коммутатора, выход первого элемента неравнозначности группы - с вторым информационным входом коммутатора и через первый элемент НЕ группы с третьим информационным входом коммутатора, выход последнего элемента НЕ группы - с четвертым информационным входом коммутатора, первый вход первого элемента ИЛИ группы - с первым информационным входом шифратора, вход логического нуля которого соединен с вторым входом первого элемента

ИЛИ группы, входы 1-го (, п - количество входов шифратора) элемента ИЛИ группы соединены с первого по 1-й входами шифратора, входы k-ro элемента неравнозначности группы ( п-1) соединены с

выходами 1-го и (i+1)-ro элементов ИЛИ труппы, выходы элементов неравнозначности группы соединены с входами одноименных элементов НЕ группы, выходы коммутатора являются выходами шифратора, управляющие входы коммутатора - управляющими входами шифратора.

2. Шифратор по п. 1,отличающий- с я тем, что коммутатор содержит две группы п-канальных МДП-транзисторов. группу р-канальных МДП-транзисторов и р-каналь- ный МДГНгранзистор, причем затворы п-канальных транзисторов первой и второй групп соединены соответственно с первым вторым информационными входами коммутатора, затвор р-канального транзистора 0

5

с третьим информационным входом коммутатора, затворы р-канальных транзисторов группы - с четвертым информационным входом коммутатора, истоки транзисторов являются управляющими входами коммутатора, стоки последнего п-канально- го транзистора первой группы, последнего р-канального транзистора группы и р-канального транзистора объединены и являются соответствующим выходом коммутатора, стоки одноименных п-канальных транзисторов первой и второй групп объединены со стоками одноименных р-канальных транзисторов группы и являются соответствующими выходами коммутатора

| название | год | авторы | номер документа |

|---|---|---|---|

| Шифратор приоритета | 1990 |

|

SU1737448A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ МНОГОРАЗРЯДНОГО КОДА | 1992 |

|

RU2029438C1 |

| Устройство для деления чисел | 1981 |

|

SU1119006A1 |

| Устройство для сравнения кодов | 1982 |

|

SU1027715A1 |

| Каскадное устройство ортогонального типа для сдвигов многоразрядных операндов | 1989 |

|

SU1661757A1 |

| Устройство для обмена информацией | 1980 |

|

SU955014A1 |

| Устройство для сортировки чисел | 1981 |

|

SU981989A1 |

| Шифратор | 1978 |

|

SU783786A1 |

| Устройство для сопряжения абонентов с магистралью | 1986 |

|

SU1361570A1 |

| Устройство для поиска информации | 1989 |

|

SU1686464A1 |

Изобретение относится к вычислительной технике. Цель изобретения - расширение области применения за счет возможности выработки выходного кода произвольной кодировки. В устройство вводится группа элементов НЕРАВНОЗНАЧНОСТЬ, коммутатор и группа элементов НЕ В устройстве появляется возможность произвольной кодировки выходного кода и произвольного наращивания разрядности выходного кода, а также сокращаются аппаратурные затраты за счет сокращения площади,занимаемойтрассами межсоединений. 1 з п. ф-лы, 2 ил

Фиг 4

WMSJ

| Устройство прерывания | 1983 |

|

SU1252776A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для шифрации крайней единицы в -разрядном двоичном коде | 1979 |

|

SU864289A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-07-30—Публикация

1990-06-11—Подача