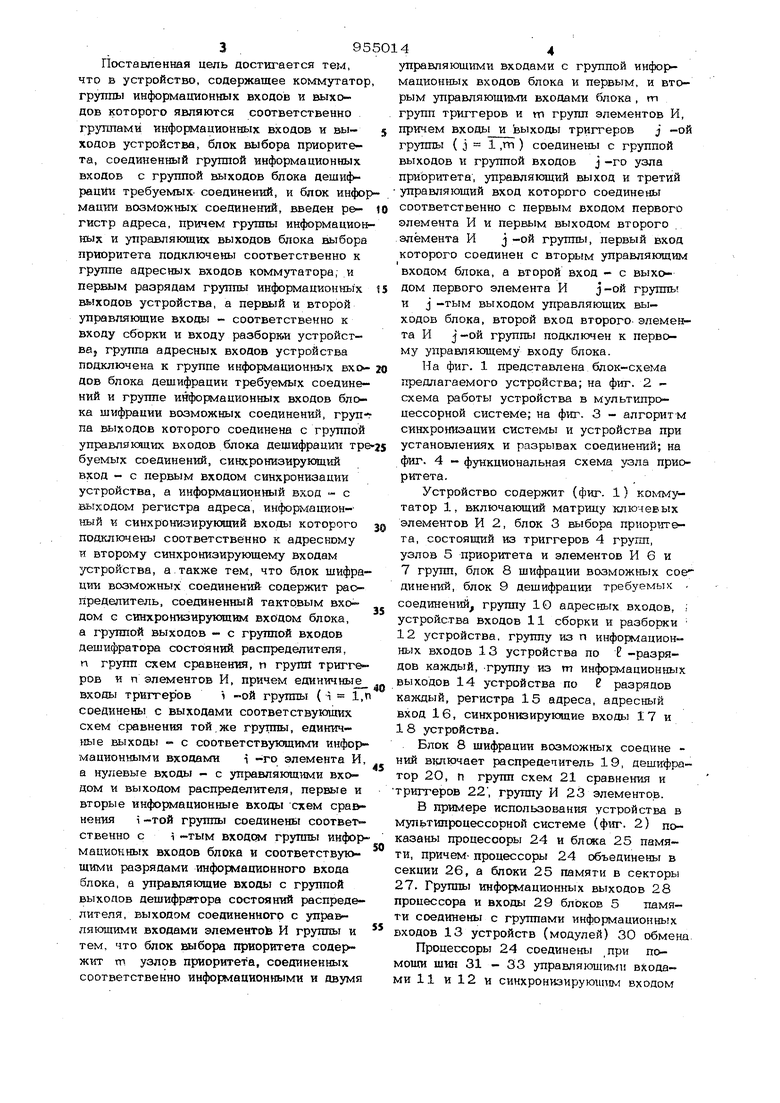

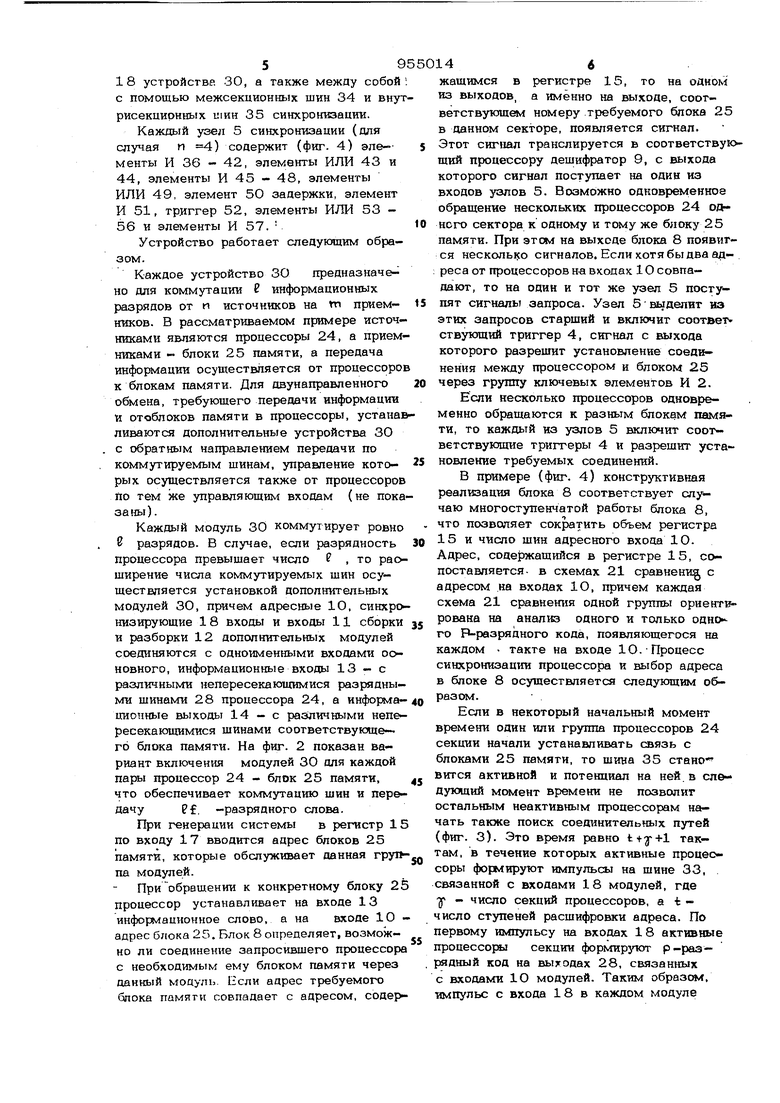

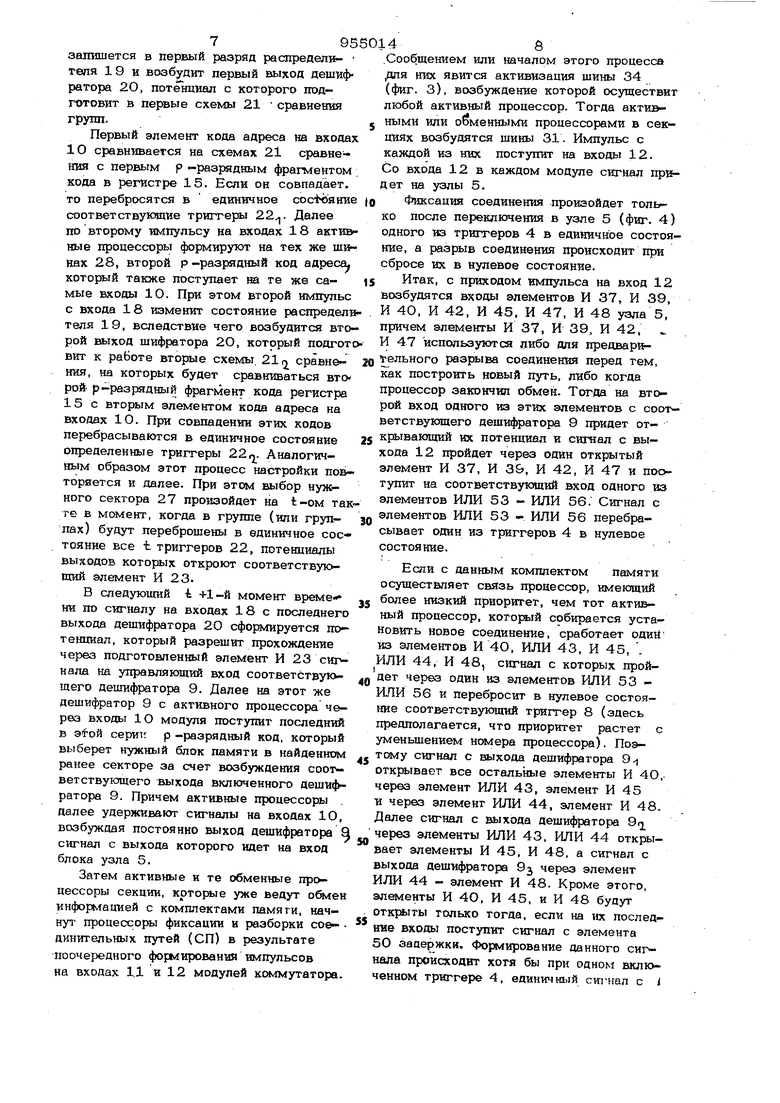

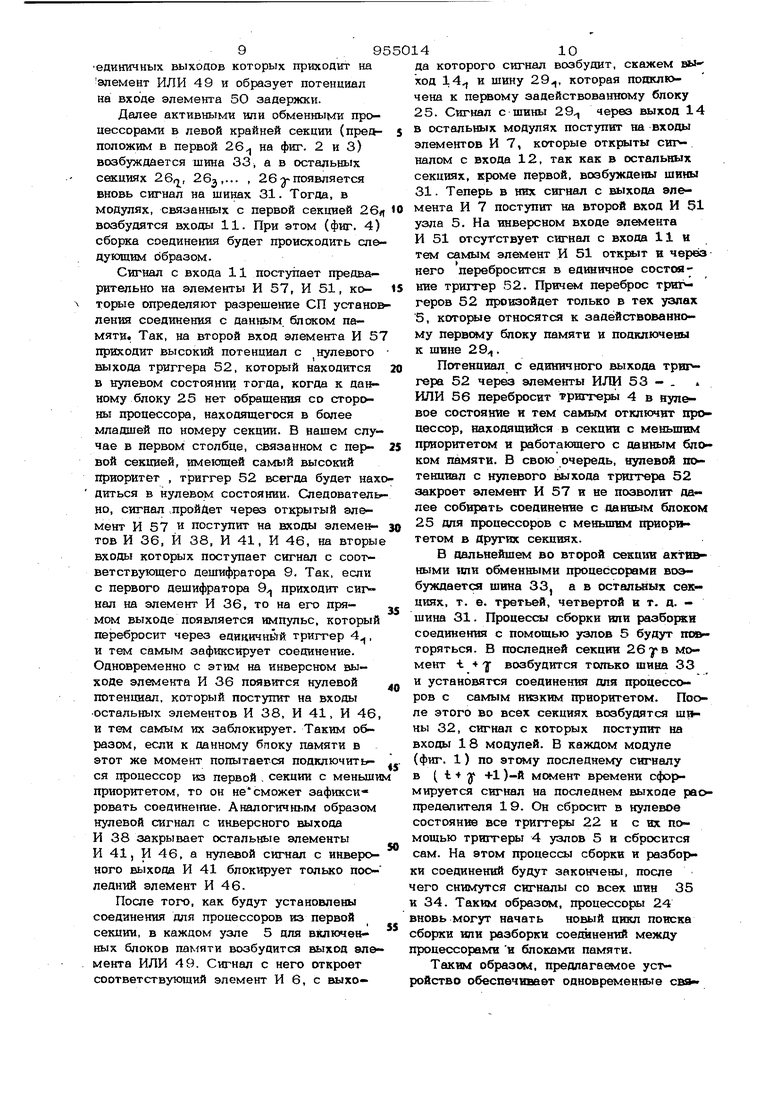

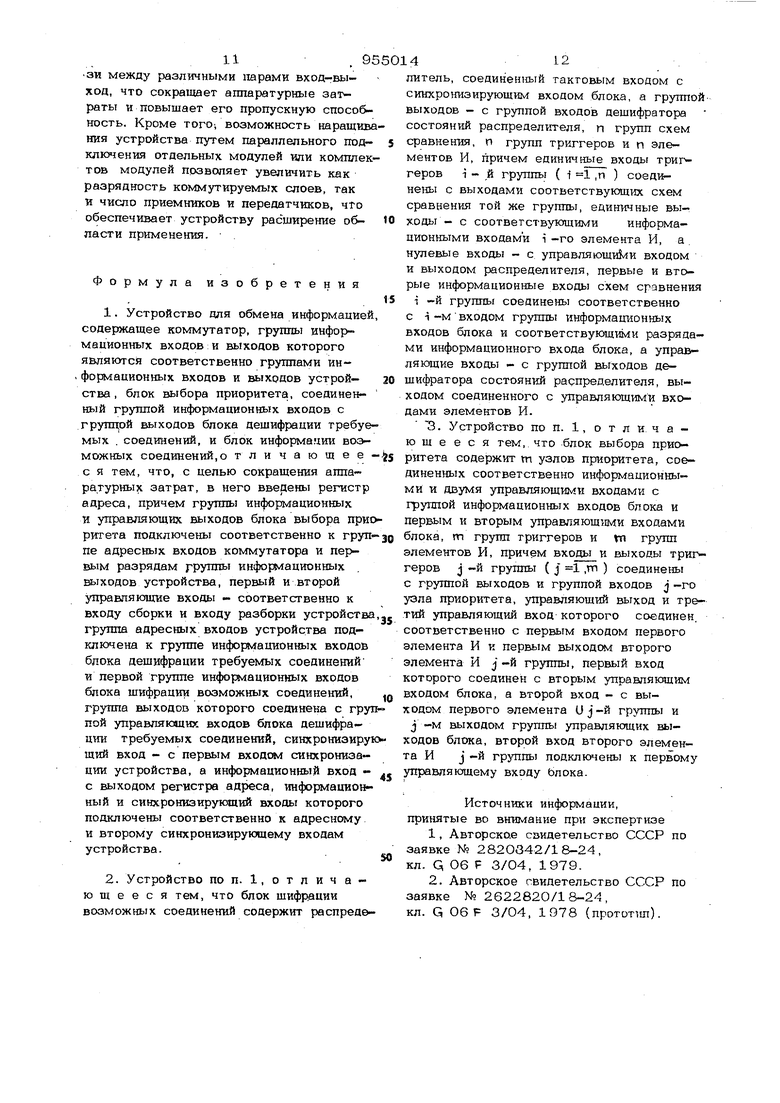

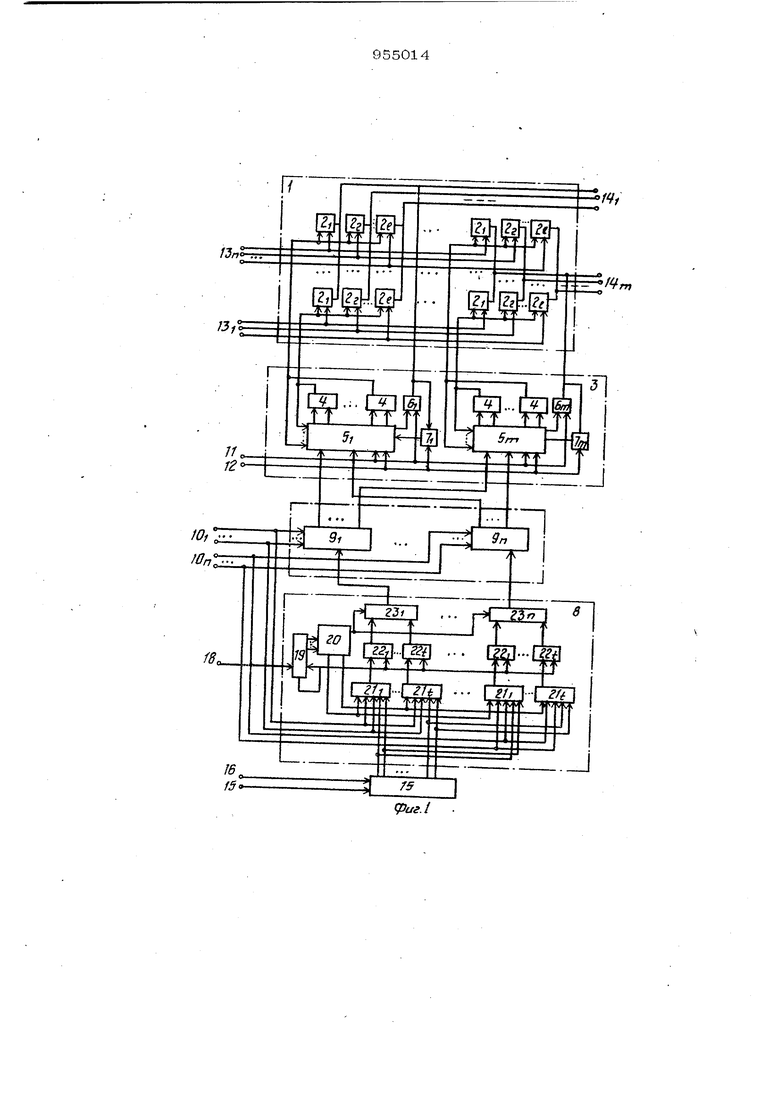

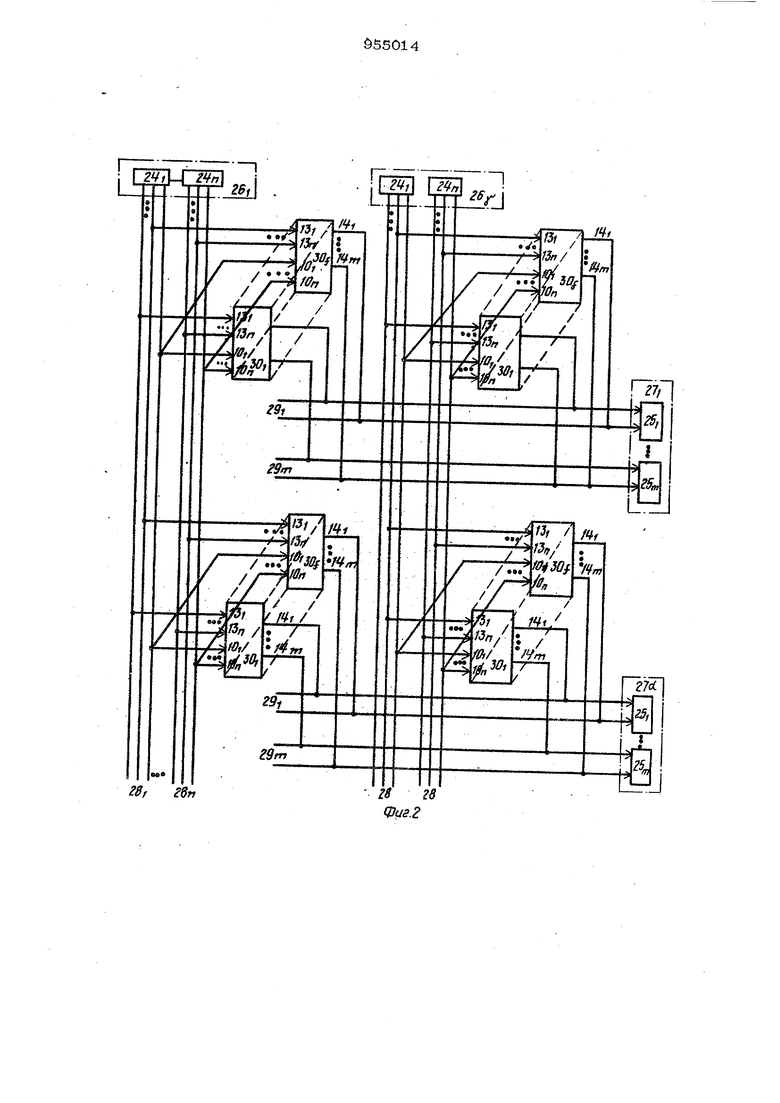

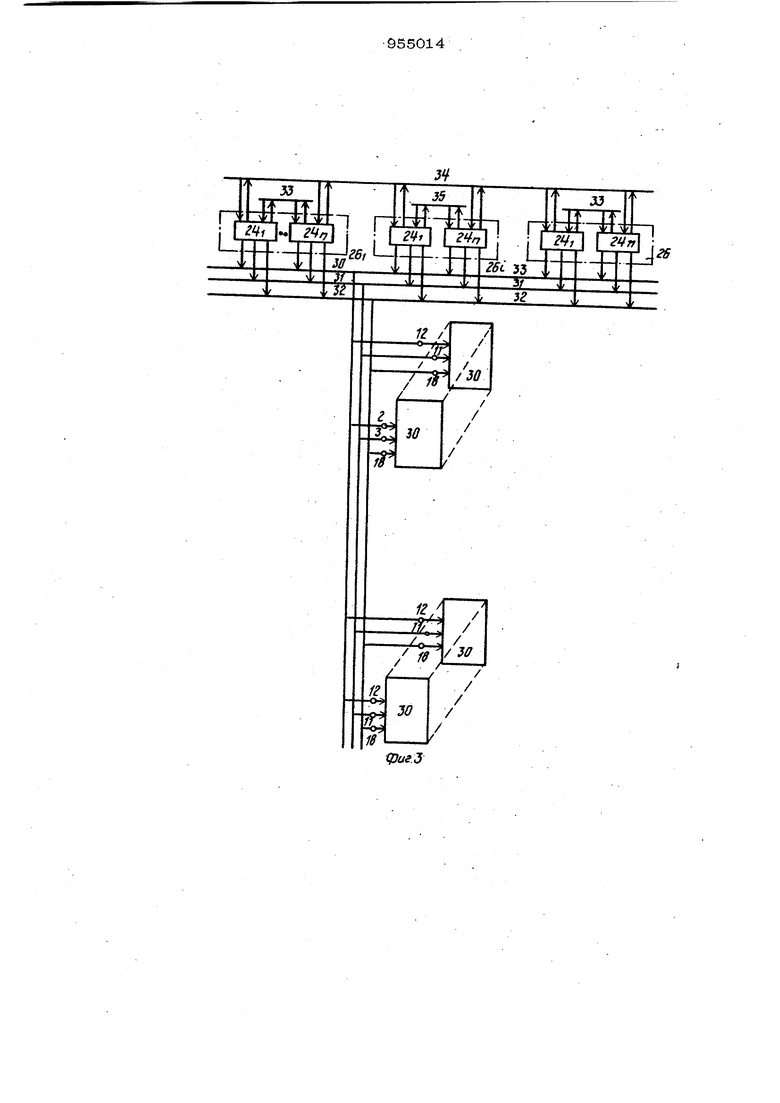

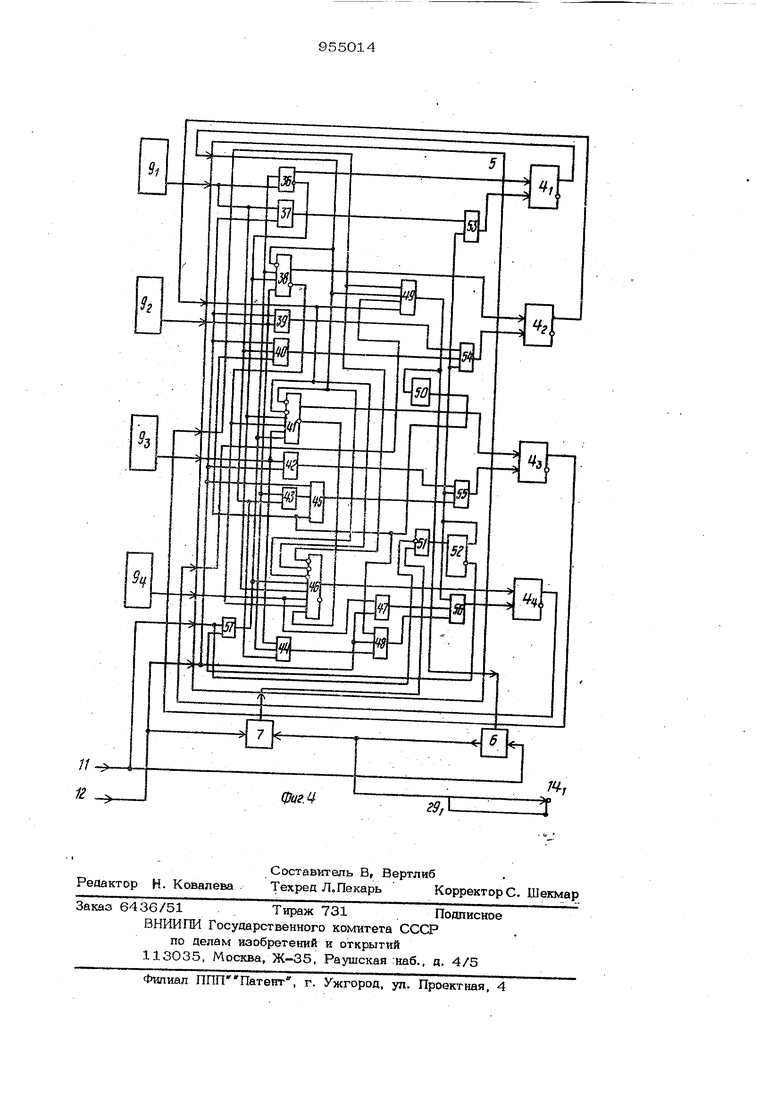

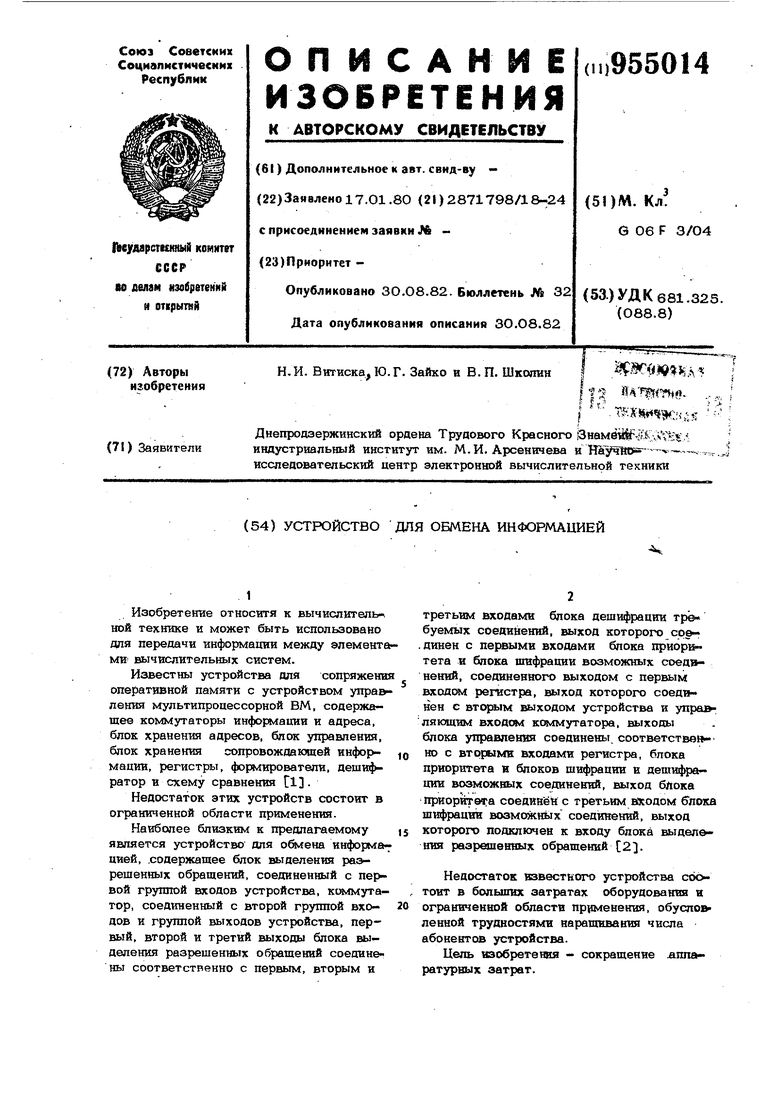

Изобретение относитя к вычислительной технике и может быть использовано для передачи информации между элемента ми вычислительных систем. Известны устройства для сопряжени оперативной памяти с устройством упра& ления мультипроцессорной ЕМ, содержащее коммутаторы инфоумации и адреса, блок хранения адресов, блок управления, блок хранения сопровождающей информации, регистры, формирователи, деши ратор и схему сравнения Г1 Недостаток этих устройств состоит в ограниченной области применения. Наиболее близким к предлагаемому является устройство для oftvieHa информа цией, .содержашее блок выделения разрешенных обращений, соединенный с группой входов устройства, ксммута- тор, соединенный с второй группой входов и группой выходов устройства, первый, второй и третий выходы блока выделения разрешенных обращений соединены соответственно с первым, вторым и третьим входами блока дешифрации трв« буемых соединений, выход которого срединен с первыми входами блока приор) тета н блока шифрации возможных соединений, соединенного выходом с первым входом регистра, выход которого соединен с BTOf&iM выходом устройства и упра&ляющим входом коммутатора, выходы блока управления соединены, соответственно с втррымн входами регистра, блока приоритета и блоков шифрации и дешифрации возможных соединений, выход блока приоритета соединён с третьим входом блока шифрации возможных соединений, выход которого подключен к входу блока выдел&ния разрешенных обращений 2. Недостаток известного устройства соотоит в больших затратах оборудования и ограниченной области пр11менения, обусдов ленной трудностями наращивания числа абонентов устройства. Цель изобретения - сокращение лшшратурных затрат. Поставленная цель достигается тем, что в устройство, содержащее ко гмутатор группы информахгаонных входов и выходов которого являются соответственно группами информационных входов и выходов устройства, блок выбора приоритета, соединенный группой информационных входов с группой выходов блока дешифрации требуемых соединений, и блок инфор мации возможных соединений, введен регистр адреса, причем группы информацион ных и управляющих выходов блока выбора приоритета подключены соответственно к группе адресных входов коммутатора, и первым разрядам группы информационных выходов устройства, а первый и второй управляющие входы - соответственно к входу сборки и входу разборки устройства j группа адресных входов устройства подключена к группе информационных входов блока дешифрации требуемых соединений и группе информационных входов блока шифрации возможных соединений, группа выходов которого соединена с группой управляющих входов блока дешифрации тре буемых соединений, синхронизирующий вход - с первым входом синхронизации устройства, а информационный вход - с вь ходом регистра адреса, информационньгй V. синхронизирующий входы которого подключены соответственно к адресному и второму синхронизирующему входам устройства, а также тем, что блок шифра ции возможных соединений содержит распределитель, соединенный тактовым входом с синхронизирующим входом блока, а группой выходов - с группой входов дешифратора состояний распределителя, п групп схем сравнеюш, п груПН триггеров и п элементов И, причем единичные входы триггеров i -ой группы { i 1, соединены с выходами соответствующих схем сравнения той,же группы, единичные выходы - с соответствующими информационными входами i -го элемента И а нулевые входы - с управляющими входом и выходом распределителя, первые и вторые информационные входы схем сравнения i-той группы соединены соответственно с i -тым входом группы инфор мационных входов блока и соответствующими разрядами информационного входа блока, а управляющие входы с группой выходов дешифреггора состояний распределителя, выходом соединенного с управляющими входами эпементоЬ И группы и тем, что блок выбора приоритета содерьжит m узлов приоритета, соединенных соответственно информационными и двумя управляющими входами с группой инфор мадионных входов блока и первым, и вторым управляющими входами блока , m групп триггеров и m групп элементов И, причем входы и выходы триггеров j -ой группы (j 1 ,m) соединены с группой выходов и группой входов j-го узла приоритета, управляющий выход и третий управляющий вход которого соединены соответственно с первым входом первого элемента И и первым выходом второго элемента И j -ой группы, первый вход которого соединен с вторым управляющим входом блока, а второй вход - с выходом первого элемента И j-ой группь и j -тым выходом управляющих выходов блока, второй вход второго- элемента И j -ой группы подключен к первому управляющему входу блока. На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 схема работы устройства в мультипроцессорной системе; на фиг. 3 - алгоритм синхронизации системы и устройства при установлениях и разрывах соединений; на фиг. 4 - функциональная схема узла приоритета. Устройство содержит (фиг. 1) кo тмyтатор 1, включающий матрицу ключевых элементов И 2, блок 3 выбора приортггега, состоящий из триггеров 4 групп, узлов 5 приоритета и элементов И б и 7 групп, блок 8 шифрации возможных сое диненкй, блок 9 дешифрации требуемых; . соединений группу 10 адресных входов, ; устройства входов 11 сборки и разборки 12 устройства, группу из п информационных входов 13 устройства по В -разрядов каждый, -группу из m информационных выходов 14 устройства по В разрядов каждый, регистра 15 адреса, адресный вход 16, синхронизирующие входь 17 и 18 устройства. Блок 8 шифрации возможных соедине НИИ включает распредепитель 19, дешифратор 2О, п групп схем 21 сравнения и триггеров 22, группу И 23 элементов. В примере использования устройства в мультипроцессорной системе (фиг. 2) показаны процессоры 24 и блока 25 памяти, причем- процессоры 24 объединены в секции 26, а блоки 25 памяти в секторы 27. Группы информационных выходов 28 процессора и входы 29 блоков 5 памяти соединены с группами информационнь х входов 13 устройств (модулей) 30 обмена Процессоры 24 соединены при помощи шин 31 - 33 управляющими входами 11 и 12 и cинxpoнизиpyюlщDvt входом 59 18 устройства 30, а также между собой с помощью межсекционных шин 34 и внут рисекиирнных ишн 35 синхронизации. Каждый узел 5 синхронизации (для случая п 4) содержит (фиг. 4) эле-менты И 36 - 42, элементы ИЛИ 43 и 44, элементы И 45 - 48, элементы ИЛИ 49, элемент 50 задержки, элемент И 51, триггер 52, элементы ИЛИ 53 56 и элементы И 57. Устройство работает следующим образом. Каждое устройство 30 предназначено для коммутации 2 информационных разрядов от м источников на w приемНИКОВ. В рассматриваемом примере источниками являются процессоры 24, а приемниками - блоки 25 памяти, а передача информации осуществляется от процессоров к блокам памяти. Для двунаправленного обмена, требующего передачи информации и отоблоков памяти в процессоры, устанав ливаются дополнительные устройства 30 с обратным направлением передачи по коммутируемым шинам, управление которых осуществляется также от процессоров По тем же управляющим входам (не пока заны). Каждый модуль 30 коммутирует ровно 2 разрядов. В случае, если разрядность процессора превыщает число , то раоширение числа коммутируемых шин осуществляется установкой дополнительных модулей 30, причем адресные 10, синхро низирующие 18 входы и входы 11 сборки и разборки 12 дополнительных модулей соединяются с одноименными входами ос новного, информационные входы 13 - с различными непересекающимися разрядными шинами 28 процессора 24, а инфоругациоиные выходы 14 - с различными непересекающимися шинами соответствующе-, го блока памяти. На фиг. 2 показан вариант включения модулей 30 для каждой пары процессор 24 - блок 25 памяти, что обеспечивает коммутацию шин и передачу8, -разрядного слова. При генерации системы в регистр 15 по входу 17 вводится адрес блоков 25 памяти, которые обслуживает данная группа модулей. При обращении к конкретному блоку 25 процессор устанавливает на входе 13 информационное слово, а на входе 10 адрес блока 25. Блок 8 определяет, возможно ли соединетге запросившего процессора с необходимым ему блоком памяти через данный модуль. Если адрес требуемого блока памяти совпадает с адресом, содерь14жащимся в регистре 15, то на одном из выходов, а именно на выходе, соответствующем номеру .требуемого блока 25 в данном секторе, появляется сигнал. Этот сигнал транслируется в соответствук щий процессору дешифратор 9, с выхода которого сигнал поступает на один из входов узлов 5. Возможно одновременное обращение нескольких процессоров 24 одного сектора к одному и тому же блоку 25 памяти. При этом на выходе блока 8 появится несколько сигналов. Если хотя бы два адреса от процессоров на входах 10 совпадают, то на один и тот же узел 5 поступят сигналы запроса. Узел 5 выделит из этих запросов старший и включит соответ ствутощий триггер 4, сигнал с выхода которого разрешит установление соединения между процессором и блоком 25 через группу ключевых элементов И 2. Если несколько процессоров одновременно обращаются к разным блокам памяти, то каждый из узлов 5 включит соответствующие триггеры 4 и разрешит установление требуемых соединений. В примере (фиг. 4) конструктивная реализация блока 8 соответствует многоступенчатой работы блока 8, что позволяет сократить объем регистра 15 и число щин адресного входа 10. Адрес, содержащийся в регистре 15, сопоставляется- в схемах 21 сравнени с адресом на входах 10, причем каждая схема 21 сравнения одной группы ориенти рована на анализ одного и только одно го Р-разрядного кода, появляющегося на каждом такте на входе 10. Процесс синхронизации процессора и выбор адреса в блоке 8 осуществляется следующим образом. Если в некоторый начальный момент времени один или группа процессоров 24 секции начали устанавливать связь с блоками 25 памяти, то шина 35 становится активной и потеициал на ней в следующий момент времени не позволит остальным неактивным процессорам начать также поиск соединительных путей (фиг. 3). Это время ровно tf2-+l тактам, в течение которых активные процессоры формируют импульсы на шине 33, связанной с входами 18 модулей, где у - число секций процессоров, а i число ступеней расшифровки адреса. По первому импульсу на входах 18 активные процессоры секции формирзтот р-раэ- ртдный код на выходах 28, связанных с входами 1О модулей. Таким образом, импульс с входа 18 в каждом модуле 795 залишется в первый разряд распредели- теля 19 и возбудит первый выход дешифратора 20, потенциал с которого подготовит в первые схемы 21 сравнения групп. Первый элемент кода адреса на входах 10 сравнивается на схемах 21 сравнения с первым р -разрядным фрагментом кода в регистре 15. Если он совпадает, то перебросятся в единичное соответствующие триггеры 22. Далее повторому импульсу на входах 18 актиЕ ные процессоры формируют на тех же ши вах 28, второй р-разрядный код адреса, который также поступает на те же самые входы 10. При этом второй импульс с входа 18 изменит состояние распредели теля 19, вследствие чего возбудится второй шифратора 2О, который подгото вит к работе вторые схемы, 21 ij сравнения, на которых будет сравниваться второй -разрядный фрагмент кода регистра 15с вторым элементом кода адреса на входах 1О. При совпадении этих кодов перебрасываются в единичное состояние определенные триггеры 22. Аналогичным образом этот процесс настройки повторяется и далее. При этом выбор нужного сектора 27 произойдет на t-oM так те в момент, когда в группе (или группах) будут переброшены в единичное состояние все t триггеров 22, потенциалы выходов которых откроют соответствующий элемент И 23. В следуюитй t +1-й момент времени по сигналу на входах 18с последнего выхода дешифратора 2О сформируется потенциал, который разрешит прохождение через подготовленный элемент И 23 сигнала на управляющий вход соответствующего дешифратора 9. Далее на этот же дешифратор 9 с активного процессора через входа: 1О модуля поступит последний в серии р -разрядный код, который выберет нужный блок памяти в найденнстл ранее секторе за счет возбуждения соответствующего выхода включенного ратора 9. Причем активные процессоры . далее удерживают сигналы на входах 10, возбуждая постоянно выход дешифратора сигнал с выхода которого идет на вход блока узла 5. Затем активные и те обменные процессоры секции, KOTojaje уже ведут обмен инфop aциeй с комплектами памяти, начну1 процессоры фиксации н разборки сое- динительных путей (СП) в результате поочередного формирования импульсов на входах 11 и 12 модулей коммутатора. 4 .Сообщением или началом этого процесса fljia них явится активизация шины 34 (фиг. 3), возбуждение которой осуществит любой активный процессор. Тогда акти&ными или обменными процессорами в секциях возбудятся шины 31. Импульс с каждой из них поступит на входы 12. Со входа 12 в каждом модуле сигнал приет на узлы 5. Фиксация соединения произойдет только после переключения в узле 5 (фиг. 4) одного из триггеров 4 в единичное состояние, а разрыв соединения происходит при сбросе их в нулевое состояние. Итак, с приходом импульса на вход 12 возбудятся входы элементов И 37, И 39, И 40, И 42, И 45, И 47, И 48 узла 5, причем элементы И 37, И 39, И 42, i И 47 используются либо для предвар тельного разрыва соединения перед тем, как построить новый путь, либо когда процессор закончил обмен. Тогда на второй вход одного из этих элементов с соответствующего дешифратора 9 придет открывающий их потенциал и сигнал с выхода 12 пройдет через один открытый элемент И 37, И 39, И 42, И 47 w поотупит на соответствующий вход одного из элементов ИЛИ 53 - ИЛИ 56. Сигнал с элементов ИЛИ 53 - ИЛИ 56 перебрасывает один из триггеров 4 в нулевое состояние. Если с данным комплектом памяти осуществляет связь процессор, имеющий более низкий приоритет, чем тот активный процессор, который собирается установить новое соединение, сработает одий из элементов И 40, ИЛИ 43, И 45, . ИЛИ 44, И 48, сигнал с которых пройдет через один из элементов ИЛИ 53 ИЛИ 56 и перебросит в нулевое состояние соответствующий триггер 8 (здесь предполагается, что приоритет растет с уменьшением номера процессора). Поэтому сигнал с выхода дешифратора 9-) открывает все остальные элементы И 4О,, через элемент ИЛИ 43, элемент И 45 и через элемент ИЛИ 44, элемент И 48. Далее сигнал с выхода дешифратора через элементы ИЛИ 43, ИЛИ 44 открывает элементы И 45, И 48, а сигнал с выхода дешифратора 9з через элемент ИЛИ 44 - элемент И 48. Кроме этого, элементы И 4О, И 45, и И 48 будут только тогда, если на их последние входы поступит сигнал с элемента 50 задержки. Формирование данного сигнала происходит хотя бы при одном включенном триггере 4, единичный cm-нал с I единичных выходов которых приходит на элемент ИЛИ 49 и образует потенциал на входе элемента 50 задержки. Далее активными или обменными процессорами в левой крайней секции (пред положим в первой 26 на фиг. 2 и 3) возбуждается шина 33, а в остальных секциях 26f, 26,... , 26 появляется вновь сигнал на шинах 31. Тогда, в модулях, связанных с первой секцией 26 возбудятся входы 11. При этом (фиг. 4) сборка соединения будет происходить сле дующим образом. Сигнал с входа 11 поступает предварительно на элементы И 57, И 51, которые определяют разрешение СП устано ления соединения с данным, блоком памяти. Так, на второй вход элемента И 5 приходит высокий потенциал с нулевого выхода триггера 52, который находится в нулевом состоянии тогда, когда к данному блоку 25 нет обращения со стороны процессора, находящегося в более младшей по номеру секции. В нашем слу чае в первом столбце, связанном с первой секцией, имеющей самый высокий приоритет , триггер 52 всегда будет нах диться в нулевом состоянии. Следователь но, сигнал пройДет через открытый элемент И 57 и поступит на входы элементов И 36, И 38, И 41, И 46, на вторы входы которых поступает сигнал с соответствующего дешифратора 9. Так, если с первого дешифратора Q приходит сигнал на элемент И 36, то на его прямом выходе появляется импульс, который перебросит через едикичнйй триггер 4, и тем самым зафиксирует соединение. Одновременно с этим на инверсном выходе элемента И 36 появится нулевой потенциал, который поступит на входы остальных элементов И 38, И 41, И 46 и тем самым их заблокирует. Таким образом, если к данному бпоку памяти в этот же момент попытается подключить ся процессор из первой , секции с меньш приоритетом, то он не сможет зафиксировать соедине тие. Аналогичным образом нулевой сигнал с инверсного выхода И 38 закрывает остальные элементы И 41, И 46, а нулевой сигнал с инвероного выхода И 41 блокирует только последний элемент И 46. После того, как будут установлены соединения для процессоров из первой секции, в каждом узле 5 для включенных блоков памяти возбудится выход эле мента ИЛИ 49. Сигнал с него откроет соответствующий элемент И 6, с выхо- да которого сигнал возбудит, скажем вы-ход 14 и шину 29, которая подклк чена к пеужому задействованному блоку 25. Сигнал с шины 29 через выход 14 в остальных модулях поступит на входы элементов И 7, которые открыты сиг налом с входа 12, так как в остальных секциях, кроме первой, возбуждены шины 31. Теперь в них сигнал с выхода элемента И 7 поступит на второй вход И 51 узла 5. На инверсном входе элемента И 51 отсугствует сигнал с входа 11 и тем самым элемент И 51 открыт и через него перебросится в единичное состояние триггер 52. Причем переброс трт геров 52 произойдет только в тех узлах 5, которые относятся к задействованному первому блоку памяти и подключены к шнне 29,. Потенциал с единичного выхода триргера 52 через элементы ИЛИ 53 - . . ИЛИ 56 перебросит триггеры 4 в нулевое состояние и тем самым отключит процессор, находящийся в секции с меньшим приоритетом и работающего с данным блоком памяти. В свою очередь, нулевой потенциал с нулевого выхода триггера 52 закроет элемент И 57 и не позволит далее собнрать соединенве с данным блоком 25 для процессоров с меньшим приор тетом в других секциях. В дальнейшем во второй секции актвз ными пли обменными процессорами возбуждается шина 33, а в остальных секциях, т. о. третьей, четвертой и т. д. - шина 31. Процессы сборки или разборки соединения с помощью узлов 5 будут повторяться. В последней секции 26 у в момент t + f возбудится только шива 33 и установятся соединения для процессоров с самым низким приоритетом. Пооле этого во всех секциях возбудятся 32, сигнал с которых поступит на входы 18 модулей. В каждом модуле (фиг. 1) по этому последнему сигналу в ( t + у +1 )-й момент времени сфо1 мируется сигнал на последнем выходе раопределителя 19. Он сбросит в нулевое состояние все триггеры 22 и с их помощью триггеры 4 узлов 5 и сбросится сам. На этом процессы сборки и разборки соединений будут закончены, после его снимутся сигналы со всех шин 35 34. Таким образом, процессоры 24 новь могут начать новый цикл поиска борки или разборки соединений между роцессорами и блоками памяти. Таким образом, предлагаемое уст ойство обеспечивает одновременные CBS

11. 95501412

аи между различными парами вход-вы- -питель, соединенный тактовым входом с

ход, что сокращает аппаратурные звт синхрокизирующим входом блока, а группой

раты и повышает его пропускную способ-выходов - с группой входов дешифратора

ность. Кроме ТОГО; возможность наращива-состояний распределителя, п групп схем

ния устройства путем параллельного под- 5сравнения, п групп триггеров и п элеключения отдельных модулей или комплек-ментов И, причем единичные входы тригтов модулей позволяет увеличить как разрядность коммутируемых слоев, так и число приемников и передатчиков, что обеспечивает устройству раёширение об- to ходы - с соответствующими информаласти применения. Формула изобретения 1. Устройство для обмена информацией, содержащее коммутатор, группы инфор мационных входов и выходов которого являются соответственно группами ин. формационных входов и выходов устройства , блок выбора приоритета, соединенный группой информационных входов с грушт;ой выходов блока дешифрации требуемых . соединений, и блок информации возможных соединений,о тличающее с я тем, что, с целью сокращения аппаратурных затрат, в него вверены регистр адреса, причем группы информационных И управляющих выходов блока выбора прио ригета подключены соответственно к rpynпе адресных входов коммутатора и первым разрядам группы информационных . выходов устройства, первый и второй упраьпяющие входы - соответственно к входу сборки и входу разборки устройства группа адресных входов устройства подключена к группе информационных входов блока дешифрации требуемых соединений и первой группе информационных входов блока шифрации возможных соединений. грутша выходов которого соединена с груп пой управляющих входов блока дешифрации требуемых соединений, синхронизирую щий вход - с первым входом синхронизации устройства, а информационный вход с выходом регистра адреса, информационный и синхронизирующий входы которого подключены соответственно к адресному и второму синхронизирующему входам устройства. 2. Устройство по п. 1, отличающее с я тем, что блок шифрации возможных соединений содержит распредегеров i- и группы ( i 1 ,п ) соединены с выходами соответствующих схем сравнения той же группы, единичные выционными входами i -го элемента И, а нулевые входы - с управляющими входом и выходом распределителя, первые и вторые информационные входы схем сравнения i -и группы соединены соответственно с i-Mвходом группы информационных входов блока и соответствующими разрядами информационного входа блока, а управляющие входы - с группой выходов дешифратора состояний распределителя, выходом соединенного с управляющими входами элементов И. 3. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что блок выбора приоритета содержит m узлов приоритета, соединенных соответственно информационными и двумя управляющими входами с группой информационных входов блока и первым и вторым управляющими входами блока, m групп триггеров и я групп элементов И, причем входы и выходы триггеров j -и группы ( j 1 ,m ) соединены с группой выходов и группой входов j -го узла приоритета, управляющий выход и третий управляющий вход которого соединен, соответственно с первым входом первого элемента И и первым выходсм второго элемента И j-и группы, первый вход которого соединен с вторым управляющим входом блока, а второй вход - с выходом первого элемента Uj-й и j -м выходом группы управляющих выходов блока, второй вход второго элемента И j -и группы подключены к первому управляющему входу блока. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР по заявке № 2820342/18-24, кл. Q 06 F 3/04, 1979. 2.Авторское свидетельство СССР по заявке № 2622820/18-24, кл. Q 06 F 3/04, 1978 (прототип).

Г/5

z0f гвп

IB фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с линиями связи | 1988 |

|

SU1536393A1 |

| Система для обмена информацией | 1980 |

|

SU980087A1 |

| Устройство для сопряжения вычислительного модуля с магистралью | 1985 |

|

SU1325495A1 |

| Устройство для сопряжения процессора с устройствами вывода | 1984 |

|

SU1206788A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Устройство для формирования и анализа семантических сетей | 1989 |

|

SU1619289A1 |

| Устройство для сопряжения процессора с группой блоков памяти | 1987 |

|

SU1587518A1 |

| Устройство для сопряжения вычислительной машины с периферийными устройствами | 1981 |

|

SU960787A1 |

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

| Устройство для управления обменом информации процессора с внешними устройствами | 1988 |

|

SU1508223A1 |

Авторы

Даты

1982-08-30—Публикация

1980-01-17—Подача