Изобретение относится к вычислительной технике и может быть использовано в устройствах контроля правильности выполнения программ на ЭВМ.

Цель изобретения - повышение достоверности контроля за счет оперативного исправления ошибок, возникающих в случае сбоев в процессе выполнения операций условных переходов при решении программы на ЭВМ.

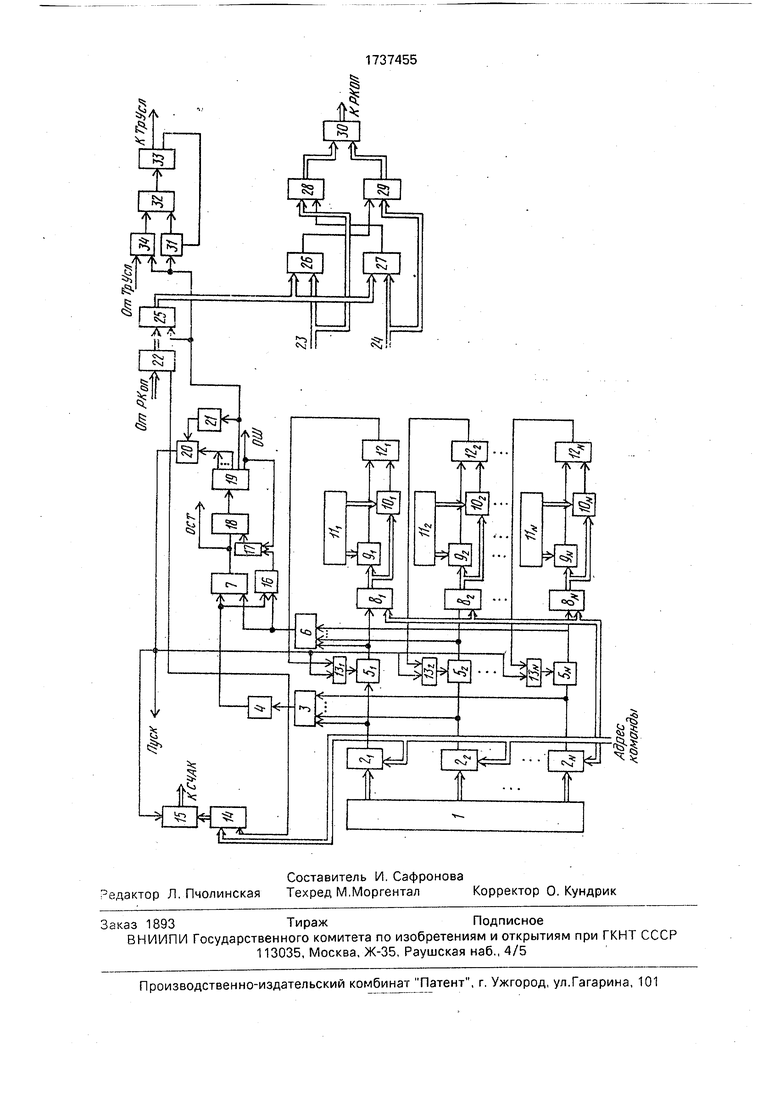

На чертеже приведена функциональная схема устройства.

Устройство содержит блок регистров адресов контрольных точек 1, первую группу схем сравнения 2.1-2.N, первый элемент ИЛИ 3, первый элемент задержки 4, N триггеров 5.1-5.N, второй элемент ИЛИ 6, элемент И 7, N блоков И 8.1-8.N, вторую 9.1-9.N и третью 10.1-10.N группы из N схем сравнения, N блоков регистров эталонных значений 11.1-11.N, первую 12.1-12.N и вторую 13.1-13.N группы из N элементов ИЛИ, регистр 14 адреса, четвертый блок элементовИ 15, второй элемент И 16,третий элемент ИЛИ 17, счетчик 18, дешифратор 19, четвертый элемент ИЛИ 20, второй элемент 21 задержки, регистр 22 кода операции, вход 23 кода операции условного перехода, вход 24 кода парной операции условного перехода, первый блок элементов И 25, схемы сравнения 26 и 27, второй 28 и третий 29 блоки элементов И, блок элементов ИЛИ 30, третий элемент И 31, пятый элемент ИЛИ 32, триггер 33 и четвертый элемент И 34.

Устройство работает следующим образом.

В исходном состоянии в блоке 1 регистров адресов контрольных точек записаны адреса команд условного перехода, подлеVI

OJ iVi

сл ел

ND

жащих контролю в процессе выполнения программы на ЭВМ (блок 1 содержит регистры, количество которых соответствует числу контрольных точек контролируемых команд условных переходов в программе). В К-м(К 1, N) блоке 11.К регистров эталон- ных значений (содержащих два регистра) записаны адреса команд условного, которые могут следовать после выполнения команды К-го условного перехода. В регистр кода операции условного перехода занесен код контролируемой команды условного перехода (например, логический переход по Больше). В регистр кода парной операции условного перехода занесен код парной контролируемой команды условного пере- хода (в нашем примере - логический переход по Меньше). Триггеры 5.1-5.N и 33, регистры кода адреса 14 и кода операции 22, счетчик 18 и дешифратор 19 обнулены.

Очередной адрес команды, проходя по входу устройства от регистра адреса команд ЭВМ (не показан), поступает на входы схем 2 сравнения первой группы, на входы блоков элементов И 8 и на информационные входы регистра 14 адреса. Если очередная команда выполняемой программы не является контролируемой программой условного перехода, то в результате сравнения в схемах 2 и на их выходах имеются нулевые сигналы, блоки элементов И 8 остаются за- крытыми, запись в регистры 14 и 22 не производится. В случае если очередная команда программы является К-й контролируемой командой условного перехода, то в схеме 2.К происходит сравнение кодов, на выходе этой схемы появляется единичный сигнал, устанавливающий триггер 5.К в единичное состояние и поступающий через элемент ИЛИ 3 на вход элемента 4 задержки и входы разрешения записи регистров адреса 14 и кода операции 22, разрешая запись информации в эти регистры. Высокий потенциал с выхода триггера 5.К поступает на первые входы блока элементов И 8.К, открывая его и разрешая прохождение значения кода адреса команды с входа устройства через вторые входы блока элементов И 8. К на первые входы схем сравнения 9.К и 10.К на вторые входы этих схем сравнения поступают значения адресов команд, которые мо- гут следовать после выполнения контролируемой команды К-го условного перехода. Элемент задержки 4 задерживает импульс, поступающий с выхода элемента ИЛИ 3 на время выполнения двух команд ЭВМ. Если за это время произошло сравнение кодов в схемах 9.К и 10.К, то импульс с выхода одной из них поступает через элементы ИЛИ 12,К и 13.К на нулевой вход

триггера 5, устанавливая его в исходное состояние, вследствие чего элемент И 7 закрыт при поступлении импульса с выхода элемента 4 задержки, а на вход сброса счетчика 18 через элементы И 16 и ИЛИ 17 поступает импульс. Устройство готово к операции проверки правильности очередного контролируемого условного перехода. Если за время задержки импульса в элементе 4 не произошло сравнения кодов в схемах 9. К и 10.К, то есть произошла ошибка при выполнении команды условного перехода, то триггер 5 остается в единичном состоянии и на выходе элемента ИЛИ 6 присутствует высокий потенциал, открывающий элемент И 7 и закрывающий элемент И 16, Импульс, задержанный в элементе 4, проходит через открытый элемент И 7 на выход остановки работ устройства (ОСТ), прекращая выполнение программы и сигнализируя об ошибке, а также на счетный вход счетчика 18, прибавляя к его содержимому единицу. Код со счетчика 18 поступает на дешифратор 19 и далее через элемент ИЛИ 20 на входы блока элементов И 15, разрешая перепись информации, занесенной в регистр адреса 14, на счетчик адреса команд ЭВМ (СЧАК), а также через элемент ИЛИ 13.К на нулевой вход триггера 5.К, устанавливая его в исходное состояние. Импульс с выхода элемента ИЛИ 20 запускает выполнение программы с адреса, записанного в СЧАК, т.е. осуществляется повтор выполнения контролируемой команды условного перехода. Если при этом не произойдет ошибка, то на вход сброса счетчика 18 поступает импульс, устанавливающий его в исходное состояние. В противном случае к содержимому счетчика 18 прибавляется единица (аналогично описанному) и происходит новый перезапуск программы с контролируемой команды. Число перезапусков определяется числом выходов дешифратора 19 (М 2-3), Если в результате (М + 1)-го повторного выполнения контролируемой команды происходит ошибка, то сигнал появляется на (М + 1)-м выходе дешифратора 19. Данный сигнал через элемент 21 задержки и элемент ИЛИ 20 поступает на элементы ИЛИ 13, а также на вторые входы блока элементов И 25, разрешая поступление кода операции контролируемой команды на первые входы схем 26 и 27 сравнения. В триггере 33 в зависимости от содержимого триггера условия ЭВМ (ТрУсл) записывается 1 или О. Сигнал с (М + 1)-го выхода дешифратора поступает на инверсный вход элемента И 34, закрывая его, и на первый вход элемента И 31, открывая его. Таким образом, содержимое триггера 33 противоположно содержимому триггера условия ЭВМ.

В схемах 26 и 27 сравнения сравниваются коды контролируемой пары команд условного перехода с кодом команды, при выполнении которой происходит ошибка. На выходе соответствующего блока схем сравнения появляется единичный сигнал, открывающий соответствующий блок элементов (29 или 28) и разрешающий передачу кода соответствующей (парной выполняемой) команды через блок элементов ИЛИ 30 и регистр кода операции ЭВМ (РКОП). Таким образом в СЧАК находится адрес команды условного перехода, которая выполняется с ошибкой, в РКОП - коя команды условного перехода, парной выполняемой, с ошибкой, в триггере условия ЭВМ - код, обратный тому, который имеет место при выполнении команды условного пере- хода, т.е. вместо команды условного перехода, выполняемой с ошибкой при перезапуске, выполняется парная команда условного перехода (например, вместо команды переход по условию Равно нулю выполняется переход по условию Не равно нулю). После занесения в СЧАК, РКОП и ТрУсл новой информации через элемент ИЛИ 20 поступает си нал пуска программы. Если при этом команда условного перехода (новая) выполняется с ошибкой, то к содержимому счетчика 18 прибавляется единица и на (М + 2)-м выходе дешифратора 19 появляется сигнал о неустраняемой ошибке при выполнении программы.

С помощью данного устройства можно контролировать парные операции условного перехода, отличающиеся содержимым триггера условия ЭВМ.

Формулаизобретения

Устройство для контроля хода программ по авт. св. Ms 1543409, отличающееся тем, что, с целью повышения достоверности контроля, оно дополнительно содержит вторую группу элементов ИЛИ, две схемы сравнения, четыре блока элементов И, блок элементов ИЛИ, три элемента И, три элемента ИЛИ, триггер, регистр адреса, регистр кода операции, счетчик, дешифратор и второй элемент задержки, причем ин- формационный вход регистра кода операции является входом задания кода операции устройства, выход регистра кода операции соединен с информационным входом первого блока элементов И, выход ко- торого соединен с первыми входами первой и второй схем сравнения, вторые входы которых подключены соответственно к входу кода операции условного-перехода и входу

парной операции условного перехода устройства, подключенным соответственно к информационным входам второго и третьего блоков элементов И, управляющие входы которых соединены соответственно с выходами второй и первой схем сравнения, выходы второго и третьего блоков элементов И соединены с входами блока элементов ИЛИ, выход которого является выходом устройства для подключения к регистру кода операции отлаживаемой ЭВМ, выход первого элемента И соединен со счетным входом счетчика, вход сброса которого соединен с выходом третьего элемента ИЛИ, выход счетчика соединен с входом дешифратора, группа М - выходов которого соединена с группой входов четвертого элемента ИЛИ, (М + 1)-й выход дешифратора через второй элемент задержки соединен с (М + 1)-м входом четвертого элемента ИЛИ, (М + 2)-й выход дешифратора является выходом ошибки устройства и соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, первый и второй входы которого соединены соответственно с выходами первого элемента задержки и второго элемента ИЛИ, выход четвертого элемента ИЛИ является выходом перезапуска программы устройства и соединен с первыми входами элементов ИЛИ второй группы, вторые входы которых соединены с выходами соответствующих элементов ИЛИ первой группы, выходы элементов ИЛИ второй группы - с нулевыми входами соответствующих триггеров группы, (М + 1)-й выход дешифратора соединен с управляющим входом первого блока элементов И, первым входом третьего и инверсным входом четвертого элементов И, выходы третьего и четвертого элементов И соединены с входами пятого элемента ИЛИ, выход которого соединен с единичным входом триггера, прямой выход которого является выходом условия перехода устройства, инверсный выход триггера соединен с вторым входом третьего элемента И, прямой вход четвертого элемента И является входом признака условия перехода устройства, информационный вход и вход разрешения регистра адреса соединены с адресным входом устройства и выходом первого элемента ИЛИ, выход регистра адреса соединен с информационным входом четвертого блока элементов И, управляющий вход которого соединен с выходом четвертого элемента ИЛИ, выход четвертого блока элементов И является выходом устройства для подключения к счетчику адреса отлаживаемой ЭВМ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для контроля полупроводниковой памяти | 1985 |

|

SU1319079A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЭЛЕКТРОННОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1992 |

|

RU2066877C1 |

| Устройство для контроля хода программ | 1988 |

|

SU1539785A1 |

| Устройство для контроля хода программ | 1989 |

|

SU1645960A1 |

| Устройство для контроля хода программ | 1987 |

|

SU1501065A1 |

| Устройство для контроля электронной вычислительной машины | 1981 |

|

SU1019451A1 |

| Устройство для поиска информации в памяти | 1985 |

|

SU1352494A1 |

| Устройство для отладки программ | 1983 |

|

SU1104521A1 |

| Устройство для контроля микропроцессорной системы | 1985 |

|

SU1287161A1 |

Изобретение относится к вычислительной технике, может быть использовано в устройствах контроля правильности выполнения программ на ЭВМ и является усовершенствованием изобретения по авт. св. № 1543409. Целью изобретения является повышение достоверности контроля за счет оперативного исправления ошибок, возникающих в случае сбоев в процессе выполнения операций условных переходов при решении программы на ЭВМ. В устройство дополнительно введены вторая группа элементов ИЛИ, две схемы сравнения, четыре блока элементов И, блок элементов ИЛИ, три элемента И, три элемента ИЛИ, триггер, регистр адреса, регистр кода операции, счетчик, дешифратор, второй элемент задержки, а также соответствующие связи между элементами устройства. Использование изобретения позволяет оперативно исправлять ошибки, возникающие при сбоях в ходе выполнения команд условных переходов, и, следовательно, повысить достоверность контроля хода программы. 1 ил.

| Устройство для контроля хода программ | 1988 |

|

SU1543409A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-05-30—Публикация

1990-05-21—Подача