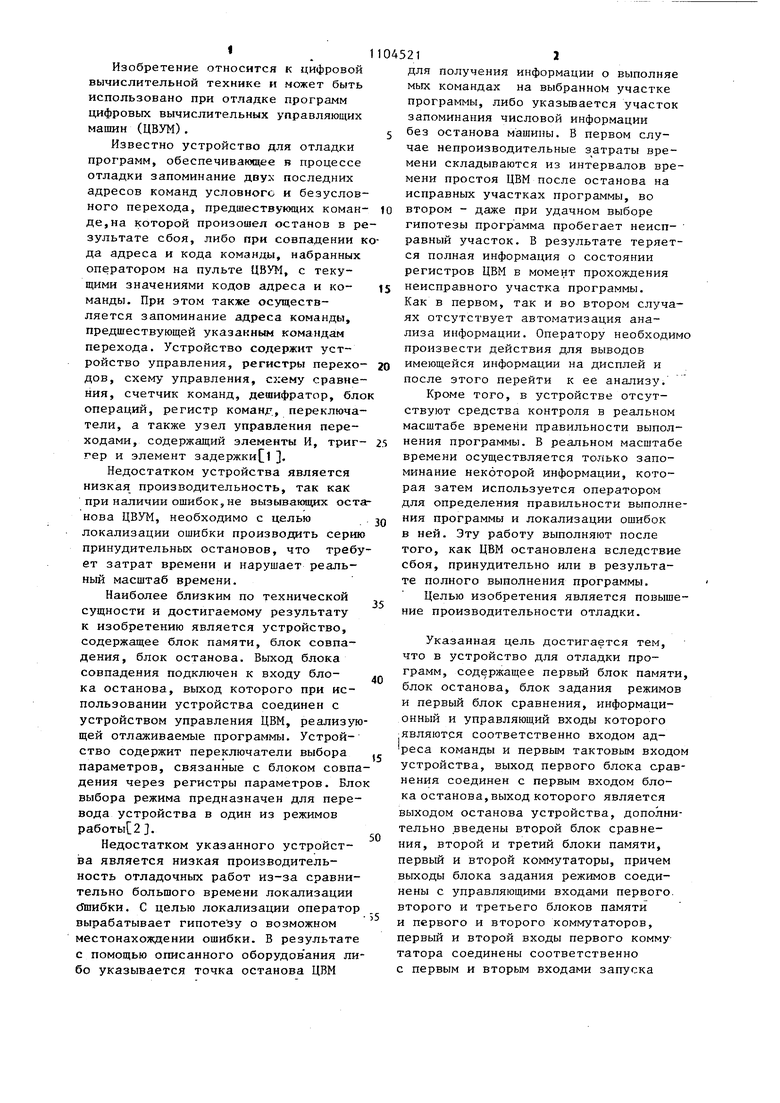

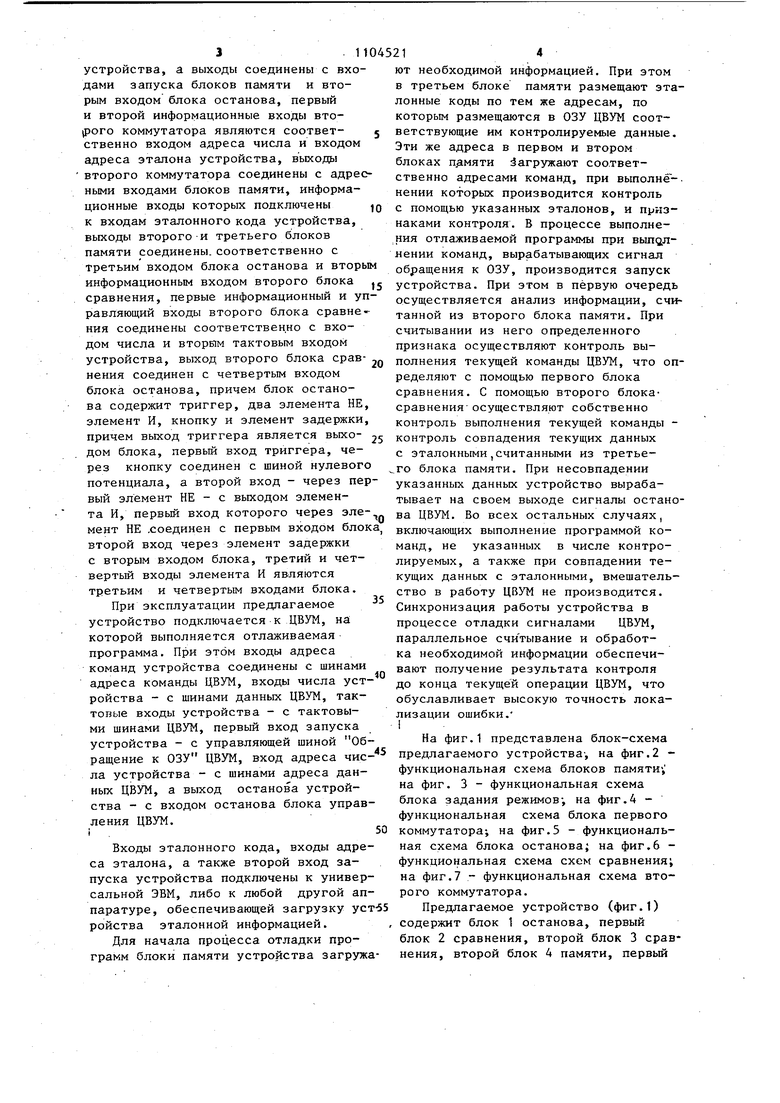

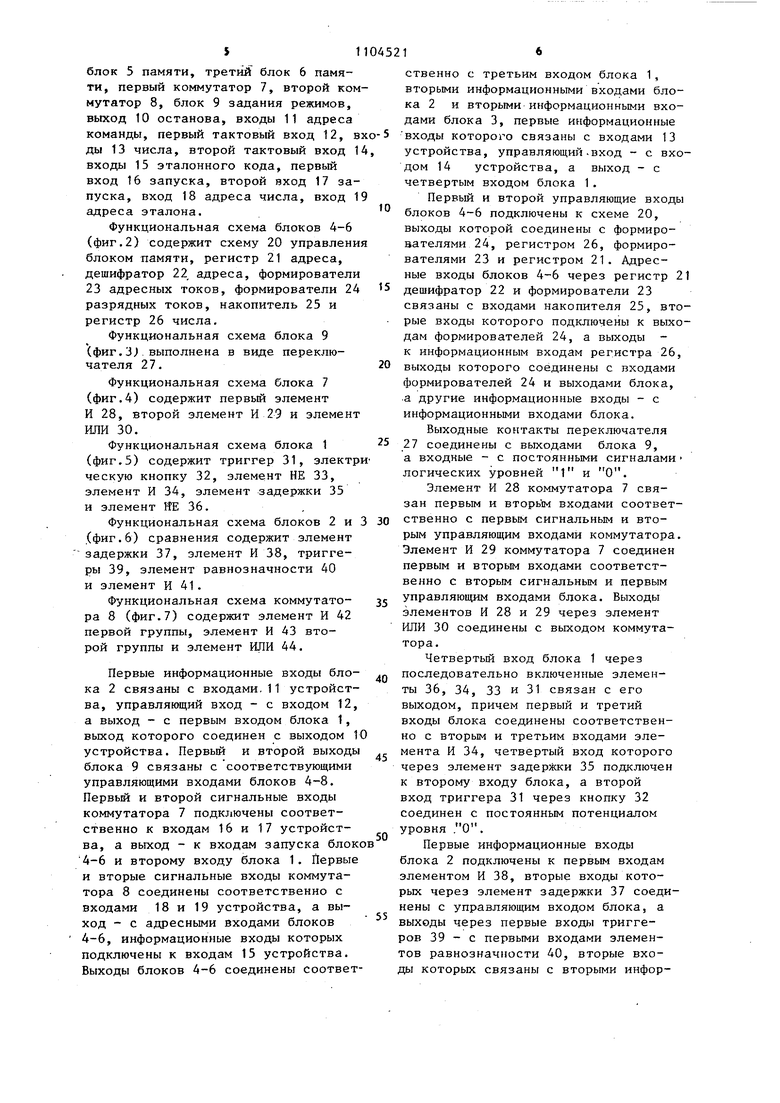

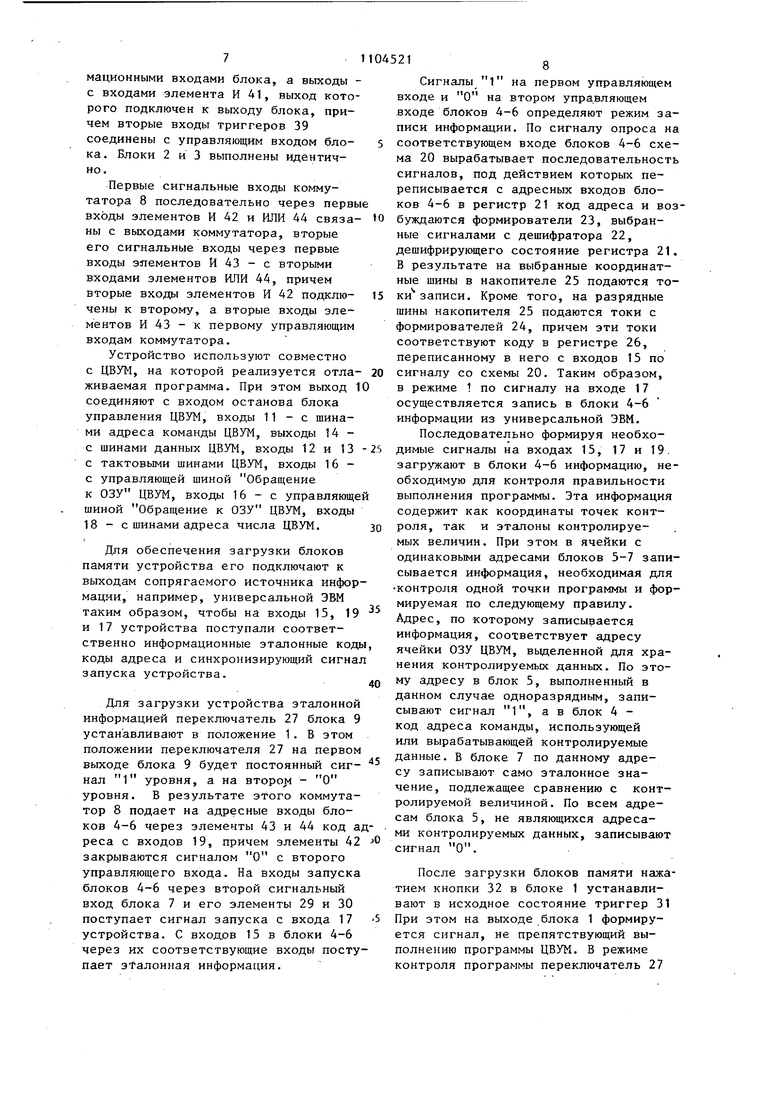

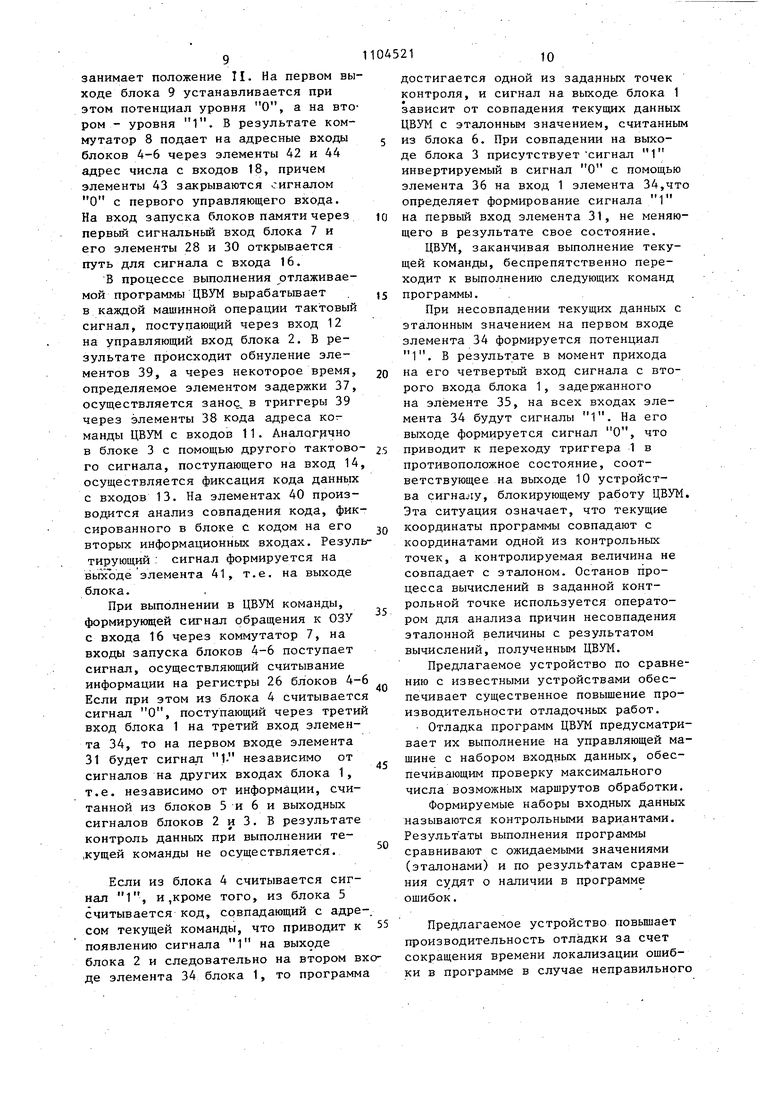

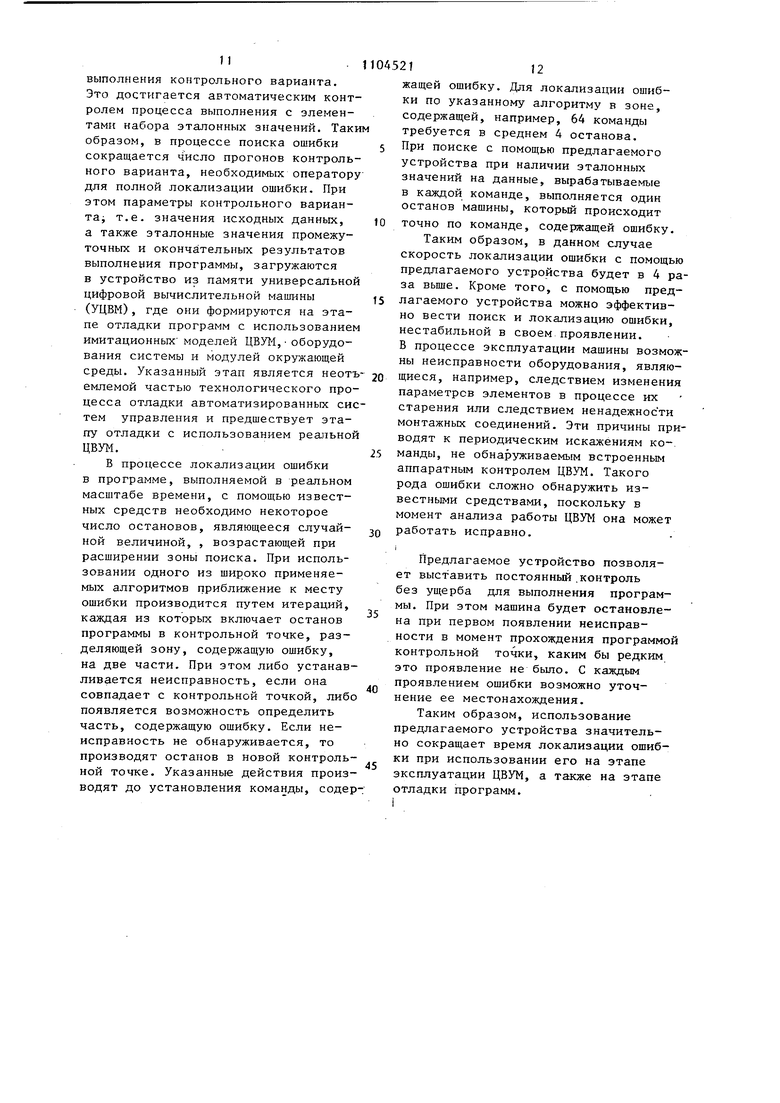

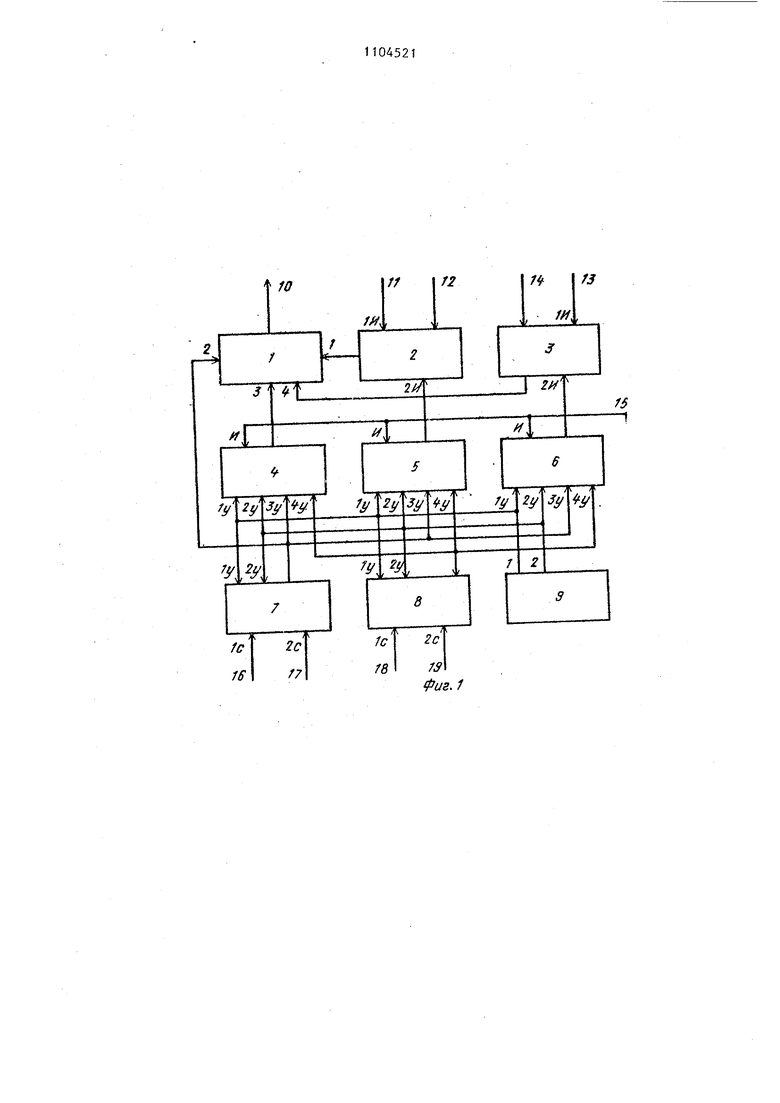

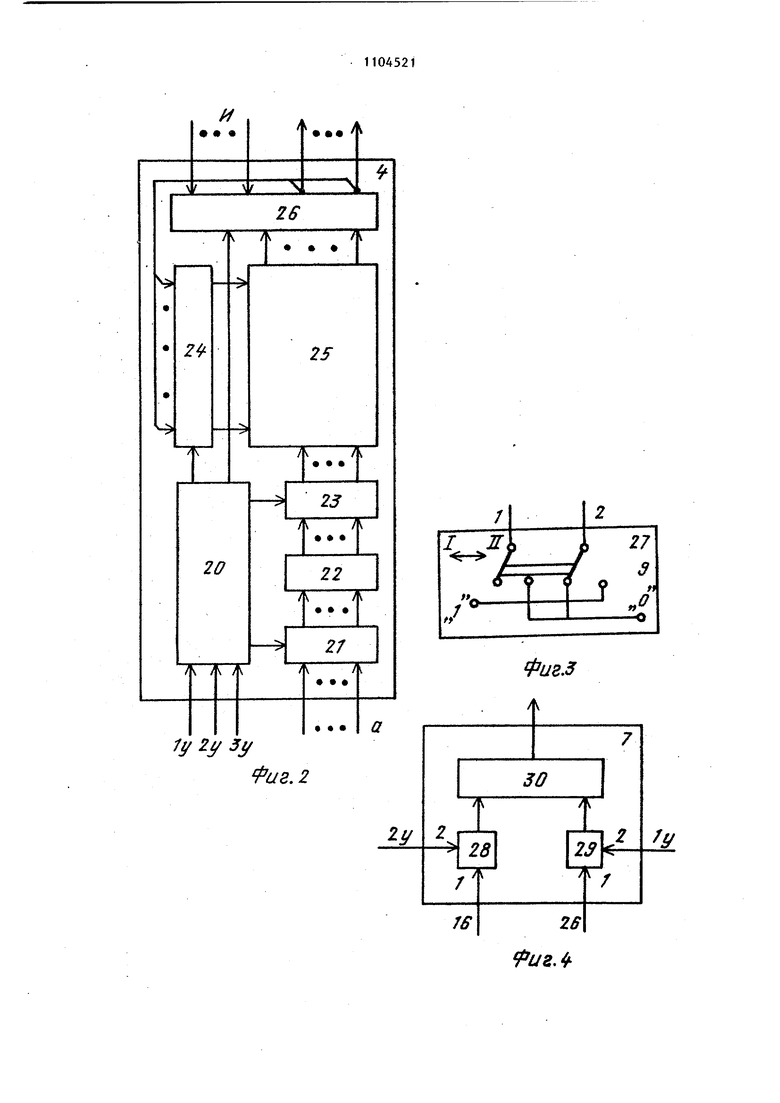

Изобретение относится к цифровой вычислительной технике и может быть использовано при отладке программ цифровых вычислительных управляющих машин (ДВУМ). Известно устройство для отладки программ, обеспечивающее в процессе отладки запоминание двух последних адресов команд условного и безусловного перехода, предшествующих команде, на которой произошел останов в ре зультате сбоя, либо при совпадении к да адреса и кода команды, набранных оператором на пульте ЦВУМ, с текущими значениями кодов адреса и команды. При этом также осуществляется запоминание адреса команды, предшествующей указанным командам перехода. Устройство содержит устройство управления, регистры переходов, схему управления, схему сравнения, счетчик команд, дешифратор, бло операции, регистр команд, переключатели, а также узел управления переходами, содержащий элементы И, триггер и элемент задержки 1, Недостатком устройства является низкая производительность, так как при наличии ошибок, не вызывающих оста нова ЦВУМ, необходимо с целью локализации ошибки производить серию принудительных остановов, что требу ет затрат времени и нарушает реальный масштаб времени. Наиболее близким по технической сущности и достигаемому результату к изобретению является устройство, содержащее блок памяти, блок совпадения, блок останова. Выход блока совпадения подключен к входу блока останова, выход которого при использовании устройства соединен с устройством управления ЦВМ, реализую щей отлаживаемые программы. Устройство содержит переключатели выбора параметров, связанные с блоком совпа дения через регистры параметров. Бло выбора режима предназначен для перевода устройства в один из режимов работы 2 J. Недостатком указанного устройст1ва является низкая производительность отладочных работ из-за сравнительно большого времени локализации (Лпибки. С целью локализации оператор вырабатывает гипотезу о возможном местонахождении ошибки. В результате с помощью описанного оборудования ли бо указывается точка останова ЦВМ 21J для получения информации о выполняе мых командах на выбранном участке программы, либо указьтается участок запоминания числовой информации без останова машины. В первом случае непроизводительные затраты времени складываются из интервалов времени простоя ЦВМ после останова на исправных участках программы, во втором - даже при удачном выборе гипотезы программа пробегает неисправный участок. В результате теряется полная информация о состоянии регистров ЦВМ в момент прохождения неисправного участка программы. Как в первом, так и во втором случаях отсутствует автоматизация анализа информации. Оператору необходимо произвести действия для выводов имеющейся информации на дисплей и после этого перейти к ее анализу. Кроме того, в устройстве отсутствуют средства контроля в реальном масштабе времени правильности выполнения программы. В реальном масштабе времени осуществляется только запоминание некоторой информации, которая затем используется оператором для определения правильности выполнения программы и локализации ошибок в ней. Эту работу выполняют после того, как ЦВМ остановлена вследствие сбоя, принудительно или в результате полного выполнения программы. Целью изобретения является повышение производительности отладки. Указанная цель достигается тем, что в устройство для отладки программ, содержащее первый блок памяти, блок останова, блок задания режимов и первый блок сравнения, информационный и управляющий входы которого являются соответственно входом адреса команды и первым тактовым входом устройства, выход первого блока сравнения соединен с первым входом блока останова, выход которого является выходом останова устройства, дополнительно введены второй блок сравнения, второй и третий блоки памяти, первый и второй коммутаторы, причем выходы блока задания режимов соединены с управляющими входами первого, второго и третьего блоков памяти и первого и второго коммутаторов, первый и второй входы первого комму татора соединены соответственно с первым и вторым входами запуска устройства, а выходы соединены с входами запуска блоков памяти и вторым входом блока останова, первый и второй информационные входы вто(Рого коммутатора являются соответственно входом адреса числа и входом адреса эталона устройства, выходы второго коммутатора соединены с адрес ными входами блоков памяти, информационные входы которых подключены к входам эталонного кода устройства, выходы второго-и третьего блоков памяти соединены.соответственно с третьим входом блока останова и вторы информационным входом второго блока сравнения, первые информационный и уп равляющий входы второго блока сравне ния соединены соответственно с входом числа и вторим тактовым входом устройства, выход второго блока срав нения соединен с четвертым входом блока останова, причем блок останова содержит триггер, два элемента НЕ элемент И, кнопку и элемент задержки причем выход триггера является выходом блока, первый вход триггера, через кнопку соединен с шиной нулевог потенциала, а второй вход - через пе вый элемент НЕ - с выходом элемента И, первый вход которого через эле мент НЕ .соединен с первым входом бло второй вход через элемент задержки с вторым входом блока, третий и четвертый входы элемента И являются третьим и четвертым входами блока. При эксплуатации предлагаемое устройство подключается к ДВУМ, на которой выполняется отлаживаемая программа. При этом входы адреса команд устройства соединены с шинами адреса команды ДВУМ, входы числа уст ройства - с шинами данных ДВУМ, тактопые входы устройства - с тактовыми шинами ДВУМ, первый вход запуска устройства - с управляющей шиной Об ращение к ОЗУ ДВУМ, вход адреса чис ла устройства - с шинами адреса данных ДВУМ, а выход останова устройства - с входом останова блока управ ления ДВУМ, i , Входы эталонного кода, входы адре са эталона, а также второй вход запуска устройства подключены к универ сальной ЭВМ, либо к любой другой ап паратуре, обеспечивающей загрузку ус ройства эталонной информацией. Для начала процесса отладки программ блоки памяти устройства загруж ЮТ необходимой информацией. При этом в третьем блоке памяти размещают эталонные коды по тем же адресам, по которым размещаются в ОЗУ ДВУМ соответствующие им контролируемые данные. Эти же адреса в первом и втором блоках пдмяти Загружают соответственно адресами команд, при выполнё-, нении которых производится контроль с помощью указанных эталонов, и признаками контроля. В процессе выполнения отлаживаемой программы при вьшалнении команд, вырабатывающих сигнал обращения к ОЗУ, производится запуск устройства. При этом в первую очередь осуществляется анализ информации, считанной из второго блока памяти. При считывании из него определенного признака осуществляют контроль выполнения текущей команды ДВУМ, что определяют с помощью первого блока сравнения. С помощью второго блокасравнения- осуществляют собственно контроль выполнения текущей команды контроль совпадения текущих данных с эталонными,считанными из третьего блока памяти. При несовпадении указанных данных устройство вырабатывает на своем выходе сигналы останова ДВУМ. Во всех остальных случаях, включающих выполнение программой команд, не указанных в числе контролируемых, а также при совпадении текущих данных с эталонными, вмешательство в работу ДВШ не производится. Синхронизация работы устройства в процессе отладки сигналами ДВУМ, параллельное считывание и обработка необходимой информации обеспечивают получение результата контроля до конца текущей операции ДВУМ, что обуславливает высокую точность локализации ошибки. На фиг.1 представлена блок-схема предлагаемого устройства-, на фиг.2 функциональная схема блоков памяти; на фиг. 3 - функциональная схема блока задания режимов-, на фиг.4 функциональная схема блока первого коммутатора-, на фиг.5 - функциональная схема блока останова; на фиг.6 функциональная схема схем сравнения; на фиг.7 - функциональная схема второго коммутатора. Предлагаемое устройство (фиг.1) содержит блок 1 останова, первый блок 2 сравнения, второй блок 3 сравнения, второй блок 4 памяти, первый блок 5 памяти, третий блок 6 памяти, первый коммутатор 7, второй ко мутатор 8, блок 9 задания режимов, выход 10 останова, входы 11 адреса команды, первый тактовый вход 12, ды 13 числа, второй тактовый вход входы 15 эталонного кода, первый вход 16 запуска, второй вход 17 за пуска, вход 18 адреса числа, вход адреса эталона. Функциональная схема блоков 4-6 (фиг.2) содержит схему 20 управлен блоком памяти, регистр 21 адреса, дешифратор 22 адреса, формировател 23 адресных токов, формирователи 2 разрядных токов, накопитель 25 и регистр 26 числа. Функциональная схема блока 9 (фиг,3J. выполнена в виде переключателя 27. Функциональная схема блока 7 (фиг.4) содержит первый элемент И 28, второй элемент И 29 и элемен ИЛИ 30. Функциональная схема блока 1 (фиг.5) содержит триггер 31, элект ческую кнопку 32, элемент НЕ 33, элемент И 34, элемент задержки 35 и элемент НЕ 36. Функциональная схема блоков 2 и .(фиг. 6) сравнения содержит элемент задержки 37, элемент И 38, триггеры 39, элемент равнозначности 40 и элемент И 41. Функциональная схема коммутатора 8 (фиг.7) содержит элемент И 42 первой группы, элемент И 43 второй группы и элемент ИЛИ 44. Первые информационные входы бло ка 2 связаны с входами,11 устройст ва, управляющий вход - с входом 12 а выход - с первым входом блока 1, выход которого соединен с выходом устройства. Первый и второй выход блока 9 связаны с соответствующими управляющими входами блоков 4-8. Первый и второй сигнальные входы коммутатора 7 подключены соответственно к входам 16 и 17 устройства, а выход - к входам запуска бло 4-6 и второму входу блока 1. Первы и вторые сигнальные входы коммутатора 8 соединены соответственно с входами 18 и 19 устройства, а выход - с адресными входами блоков 4-6, информационные входы которых подключены к входам 15 устройства. Выходы блоков 4-6 соединены соотве ственно с третьим входом блока 1, вторыми информационными входами блока 2 и вторыми информационными входами блока 3, первые информационные входы которого связаны с входами 13 устройства, управляющий-вход - с входом 14 устройства, а выход - с четвертым входом блока 1. Первый и второй управляющие входы блоков 4-6 подключены к схеме 20, выходы которой соединены с формирователями 24, регистром 26, формирователями 23 и регистром 21. Адресные входы блоков 4-6 через регистр 21 дешифратор 22 и формирователи 23 связаны с входами накопителя 25, вторые входы которого подключены к выходам формирователей 24, а выходы к информационным входам регистра 26, выходы которого соединены с входами формирователей 24 и выходами блока, а другие информационные входы - с информационными входами блока. Выходные контакты переключателя 27 соединены с выходами блока 9, а входные - с постоянными сигналами логических уровней 1 и О. Элемент И 28 коммутатора 7 связан первьм и вторьм входами соответственно с первым сигнальным и вторым управляющим входами коммутатора. Элемент И 29 коммутатора 7 соединен первым и вторым входами соответственно с вторым сигнальным и первым управляющим входами блока. Выходы элементов И 28 и 29 через элемент ИЛИ 30 соединены с выходом коммутатора. Четвертый вход блока 1 через последовательно включенные элементы 36, 34, 33 и 31 связан с его выходом, причем первый и третий входы блока соединены соответственно с вторым и третьим входами элемента И 34, четвертый вход которого через элемент задержки 35 подключен к второму входу блока, а второй вход триггера 31 через кнопку 32 соединен с постоянным потенциалом уровня .О. Первые информационные входы блока 2 подключены к первым входам элементом И 38, вторые входы котоых через элемент задержки 37 соединены с управляющим входом блока, а ыходы через первые входы триггеов 39 - с первыми входами элеменов равнозначности 40, вторые вхоы которых связаны с вторыми информационными входами блока, а выходы с входами элемента И 41, выход которого подключен к выходу блока, причем вторые входы триггеров 39 соединены с управляющим входом блока. Блоки 2 и 3 выполнены идентично. Первые сигнальные входы коммутатора 8 последовательно через первы входы элементов И 42 и ИЛИ 44 связаны с выходами коммутатора, вторые его сигнальные входы через первые входы элементов И 43 - с вторыми входами элементов ИЛИ 44, причем вторые входы элементов И 42 подключены к второму, а вторые входы элементов И 43 - к первому управляющим входам коммутатора. Устройство используют совместно с ДВУМ, на которой реализуется отла живаемая программа. При этом выход соединяют с входом останова блока управления ДВУМ, входы 11 - с шинами адреса команды ДВУМ, выходы 14 с шинами данных ДВУМ, входы 12 и 13 с тактовыми шинами ДВУМ, входы 16 с управляющей шиной Обращение к ОЗУ ДВУМ, входы 16 - с управляющ шиной Обращение к ОЗУ ДВУМ, входы 18 - с шинами адреса числа ДВУМ. Для обеспечения загрузки блоков памяти устройства его подключают к выходам сопрягаемого источника инфор мации, например, универсальной ЭВМ таким образом, чтобы на входы 15, 19 и 17 устройства поступали соответственно информационные эталонные код коды адреса и синхронизирующий сигна запуска устройства. Для загрузки устройства эталонно информацией переключатель 27 блока устанавливают в положение 1. В этом положении переключателя 27 на перво выходе блока 9 будет постоянный сиг нал 1 уровня, а на втором - О уровня. В результате этого коммута тор 8 подает на адресные входы блоков 4-6 через элементы 43 и 44 код реса с входов 19, причем элементы 4 закрываются сигналом О с второго управляющего входа. На входы запуск блоков 4-6 через второй сигнальный вход блока 7 и его элементы 29 и 30 поступает сигнал запуска с входа 17 устройства. С входов 15 в блоки 4-6 через их соответствующие входы пост пает эtaлoннaя информация. Сигналы 1 на первом управляющем входе и О на втором управляющем входе блоков 4-6 определяют режим записи информации. По сигналу опроса на соответствующем входе блоков 4-6 схема 20 вырабатывает последовательность сигналов, под действием которых переписывается с адресных входов блоков 4-6 в регистр 21 код адреса и возбуждаются формирователи 23, выбранные сигналами с дешифратора 22, дешифрирующего состояние регистра 21. В результате на выбранные координатные шины в накопителе 25 подаются токи записи. Кроме того, на разрядные шины накопителя 25 подаются токи с формирователей 24, причем эти токи соответствуют коду в регистре 26, переписанному в него с входов 15 по сигналу со схемы 20. Таким образом, в режиме 1 по сигналу на входе 17 осуществляется запись в блоки 4-6 информации из универсальной ЭВМ. Последовательно формируя необходимые сигналы на входах 15, 17 и 19. загружают в блоки 4-6 информацию, необходимую для контроля правильности выполнения программы. Эта информация содержит как координаты точек контроля, так и эталоны контролируемых величин. При этом в ячейки с одинаковыми адресами блоков 5-7 записывается информация, необходимая для контроля одной точки программы и формируемая по следующему правилу. Адрес, по которому записывается информация, соответствует адресу ячейки ОЗУ ДВУМ, выделенной для хранения контролируемых данных. По этому адресу в блок 5, выполненный в данном случае одноразрядным, записывают сигнал 1, а в блок 4 код адреса команды, использующей или вырабатывающей контролируемые данные. В блоке 7 по данному адресу записывают само эталонное значение, подлежащее сравнению с контролируемой величиной. По всем адресам блока 5, не являющихся адресами контролируемых данных, записывают сигнал О. После загрузки блоков памяти нажатием кнопки 32 в блоке 1 устанавливают в исходное состояние триггер 31 При этом на выходе блока 1 формируется сигнал, не препятствующий выполнению программы ДВУМ. В режиме контроля программы переключатель 27 9 занимает положение II. На первом вы ходе блока 9 устанавливается при этом потенциал уровня О, а на вто ром - уровня 1. В результате коммутатор 8 подает на адресные входы блоков 4-6 через элементы 42 и 44 адрес числа с входов 18, причем элементы 43 закрываются сигналом О с первого управляющего входа. На вход запуска блоков памяти через первый сигнальньй вход блока 7 и его элементы 28 и 30 открывается путь для сигнала с входа 16. В процессе выполнения этлаживаемой программы ДВУМ вырабатывает . в каждой машинной операции тактовый сигнал, поступающий через вход 12 на управляющий вход блока 2. В результате происходит обнуление элементов 39, а через некоторое время, определяемое элементом задержки 37, осуществляется занос в триггеры 39 через элементы 38 кода адреса команды ДВУМ с входов 11. Аналогично в блоке 3 с помощью другого тактово го сигнала, поступающего на вход 14 осуществляется фиксация кода данных с входов 13. На элементах 40 производится анализ совпадения кода, фик сированного в блоке с кодом на его вторых информационных входах. Резул тирующий : сигнал формируется на выхЪдеэлемента 41, т.е. на выходе блока. При выполнении в ДВУМ команды, формирующей сигнал обращения к ОЗУ с входа 16 через коммутатор 7, на входы запуска блоков 4-6 поступает сигнал, осуществляющий считывание информации на регистры 26 блоков 4Если при этом из блока 4 считываетс сигнал О, поступающий через трети вход блока 1 на третий вход элемента 34, то на первом входе элемента 31 будет сигнал 1 независимо от сигналов на других входах блока 1, т.е. независимо от информации, считанной из блоков 5 и 6 и выходных сигналов блоков 2 и 3. В результате контроль данных при выполнении те,кущей команды не осуществляется. Если из блока 4 считывается сигнал 1, и,кроме того, из блока 5 считывается код, совпадающий с адре сом текущей команды, что приводит к появлению сигнала 1 на выходе блока 2 и следовательно на втором в де элемента 34 блока 1, то программ 21 достигается одной из заданных точек контроля, и сигнал на выходе блока 1 зависит от совпадения текущих данных ДВУМ с эталонным значением, считанным из блока 6. При совпадении на выходе блока 3 присутствуетсигнал 1 инвертируемый в сигнал О с помощью элемента 36 на вход 1 элемента 34,что определяет формирование сигнала 1 на первый вход элемента 31, не меняющего в результате свое состояние. ДВУМ, заканчивая выполнение текущей команды, беспрепятственно переходит к выполнению следующих команд программы. При несовпадении текущих данных с эталонным значением на первом входе элемента 34 формируется потенциал 1. В результате в момент прихода на его четвертый вход сигнала с второго входа блока 1, задержанного на элементе 35, на всех входах элемента 34 будут сигналы 1. На его выходе формируется сигнал О, что приводит к переходу триггера 1 в противоположное состояние, соответствующее на выходе 10 устройства сигналу, блокирующему работу ДВУМ. Эта ситуация означает, что текущие координаты программы совпадают с координатами одной из контрольных точек, а контролируемая величина не совпадает с эталоном. Останов процесса вычислений в заданной контрольной точке используется оператором для анализа причин несовпадения эталонной величины с результатом вычислений, полученным ДВУМ. Предлагаемое устройство по сравнению с известными устройствами обеспечивает существенное повышение производительности отладочных работ. Отладка программ ДВУМ предусматривает их выполнение на управляющей машине с набором входных данных, обеспечивающим проверку максимального числа возможных маршрутов обработки. Формируемые наборы входных данных называются контрольными вариантами. Результаты выполнения программы сравнивают с ожидаемыми значениями (эталонами) и по pe3ynbtaTaM сравнеия судят о наличии в программе шибок. Предлагаемое устройство повышает роизводительность отладки за счет окращения времени локализации ошиби в программе в случае неправильного выполнения контрольного варианта. Это достигается автоматическим контролем процесса выполнения с элементами набора эталонных значений. Так образом, в процессе поиска ошибки сокращается число прогонов контроль ного варианта, необходимых оператор для полной локализации ошибки. При этом параметры контрольного варианта т.е. значения исходных данных, а также эталонные значения промежуточных и окончательных результатов выполнения программы, загружаются в устройство из памяти универсально цифровой вычислительной машины (УЦВМ), где они формируются на этапе отладки программ с использование имитационных моделей ДВУМ,- оборудования системы и модулей окружающей среды. Указанный этап является неот емлемой частью технологического про цесса отладки автоматизированных си тем управления и предшествует этапу отладки с использованием реально ДВУМ. В процессе локализации ошибки в программе, выполняемой в реальном масштабе времени, с помощью известных средств необходимо некоторое число остановов, являющееся случайной величиной, , возрастающей при расширении зоны поиска. При использовании одного из широко применяемых алгоритмов приближение к месту ошибки производится путем итераций, каждая из которых включает останов программы в контрольной точке, разделяющей зону, содержащую ошибку, на две части. При этом либо устанав ливается неисправность, если она совпадает с контрольной точкой, либ появляется возможность определить часть, содержащую ошибку. Если неисправность не обнаруживается, то производят останов в новой контроль ной точке. Указанные действия произ водят до установления команды, соде жащей ошибку. Для локализации ошибки по указанному алгоритму в зоне, содержащей, например, 64 команды требуется в среднем 4 останова. При поиске с помощью предлагаемого устройства при наличии эталонных значений на данные, вырабатываемые в каждой команде, выполняется один останов машины, который происходит точно по команде, содержащей ошибку. Таким образом, в данном случае скорость локализации ошибки с помощью предлагаемого устройства будет в 4 раза выше. Кроме того, с помощью предлагаемого устройства можно эффективно вести поиск и локализацию ошибки, нестабильной в своем проявлении. В процессе эксплуатации машины возможны неисправности оборудования, являющиеся, например, следствием изменения параметров элементов в процессе их старения или следствием ненадежности монтажных соединений. Эти причины приводят к периодическим искажениям команды, не обнаруживаемым встроенным аппаратным контролем ДВУМ. Такого рода ошибки сложно обнаружить известными средствами, поскольку в момент анализа работы ДВУМ она может работать исправно. Предлагаемое устройство позволяет выставить постоянный.контроль без ущерба для выполнения программы. При этом машина будет остановлена при первом появлении неисправности в момент прохождения программой контрольной точки, каким бы редким это проявление не бьшо. С каждьпу проявлением ошибки возможно уточнение ее местонахождения. Таким образом, использование предлагаемого устройства значительно сокращает время локализации ошибки при использовании его на этапе эксплуатации ДВУМ, а также на этапе отладки программ.

Фиг. 1

Фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1987 |

|

SU1522203A1 |

| СПОСОБ КОНТРОЛЯ И ОТЛАДКИ ПРОГРАММ РЕАЛЬНОГО ВРЕМЕНИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2050588C1 |

| Устройство для контроля программных автоматов | 1988 |

|

SU1571552A1 |

| Устройство для отладки программ | 1980 |

|

SU960828A1 |

| Устройство для отладки программ | 1988 |

|

SU1624461A1 |

| Устройство для отладки микропроцессорных систем | 1986 |

|

SU1462326A1 |

| Устройство для отладки программ | 1985 |

|

SU1251087A1 |

| Устройство для микропрограммного управления | 1983 |

|

SU1188742A1 |

| Устройство для обработки цифровых данных | 1980 |

|

SU964650A1 |

| УСТРОЙСТВО ДЛЯ ПРОВЕРКИ РАБОТОСПОСОБНОСТИ ОБЪЕКТОВ | 1992 |

|

RU2036505C1 |

УСТРОЙСТВО ДЛЯ ОТЛАДКИ ПРОГРАММ, содержащее первый блок памяти, блок останова, блок задания режимов и первый блок сравнения, информационный и управляющий входы которого являются соответственно входом адреса команды и первым тактовым входом устройства, выход первого блока сравнения соединен с первым входом блока останова, выход которого является выходом останова устройства, отличающееся тем, что, с целью повышения производительности, в устройство введены второй блок сравнения, второй и третий блоки памяти, первый и второй коммутаторы, причем выходы блока задания режимов соединены с управляющпми входами первого, второго и третьего блоков памяти и первого и второго коммутаторов, первый и второй входы первого коммутатора соединены соответственно с первым и вторым входами запуска устройства, а выходы соединены с входами запуска блоков памяти и вторым входом блока останова, первый и второй информационные входы второго коммутатора являются соответственно входом адреса числа и входом адреса . эталона устройства, выходы второго коммутатора соединены с адресными входами блоков памяти, информационные входы которых подключены к входам эталонного кода устройства, выходы второго и третьего блоков памяти соединены соответственно с третьим входом блока останова и вторым информацион}1ым входом второго блока сравнений, первые информационный и управляющий входы второго блока сравнения соединены соответственно с входом числа и вторым тактовым (Л входом устройства, выход второго блока сравнения соединен с четвертым входом блока останова, причем блок останова содержит триггер, два элемента НЕ, элемент И, кнопку и элемент задержки, причем выход триггера является выходом блока, первый вход триггера через кнопку соединен 4 с шиной нулевого потенцигша, а второй tn вход через первый элемент НЕ - с вы- . lN9 ходом эл емента И, первый вход которого через элемент НЕ соединен с первым входом блока, второй вход через элемент задержки - с вторым входом блока, третий и четвертый входы элемента И являются третьим и четвертым входами блока.

У /

аг.2

30

У

23

28

Ж

/

Г6

26

иг. /1 J

Фаг. 5

1104521 1И

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для отладки программ | 1978 |

|

SU763900A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 3937938, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| (прототип) | |||

Авторы

Даты

1984-07-23—Публикация

1983-01-28—Подача