Изобретение относится к вычислительной технике и может быть использовано для контроля хода выполнения программы ЭВМ, работающих в реальном масштабе времени.

Целью изобретения является повышение глубины контроля хода программ.

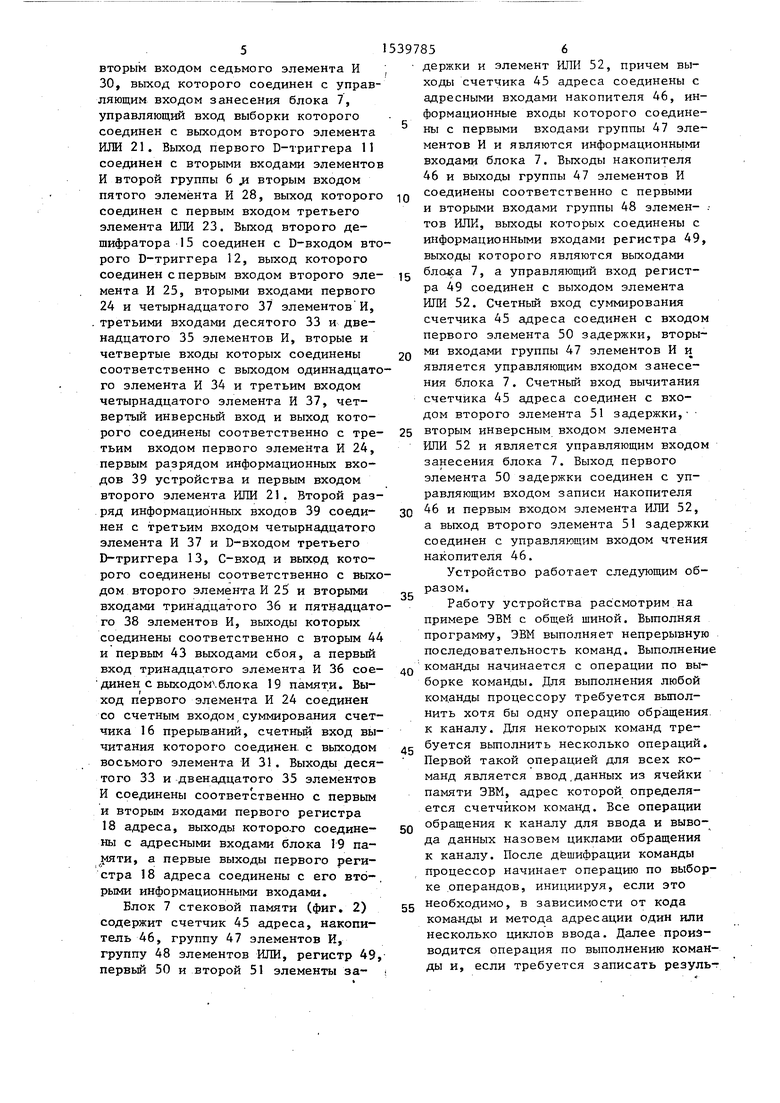

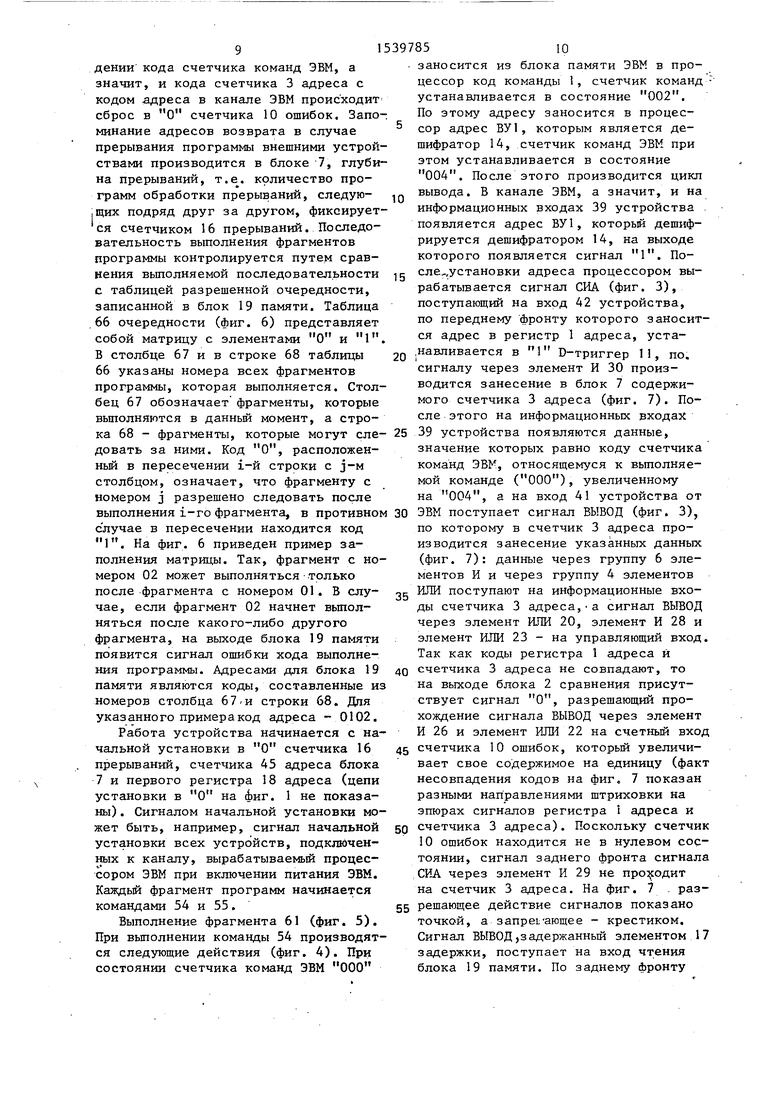

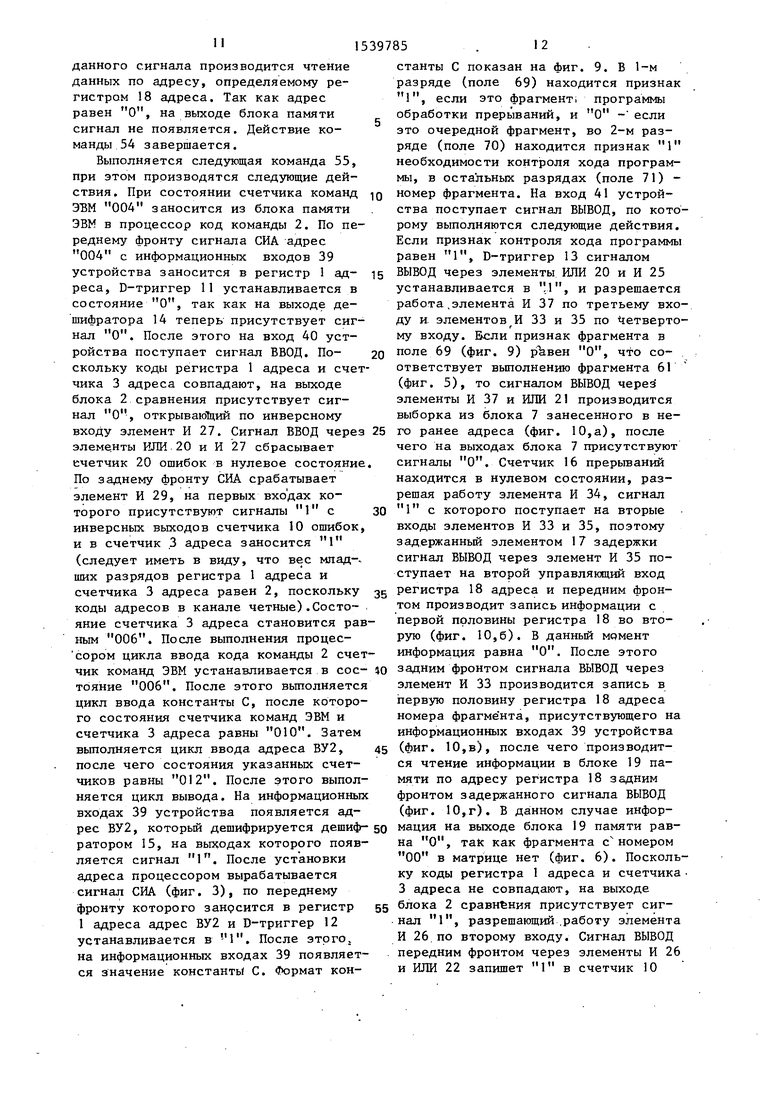

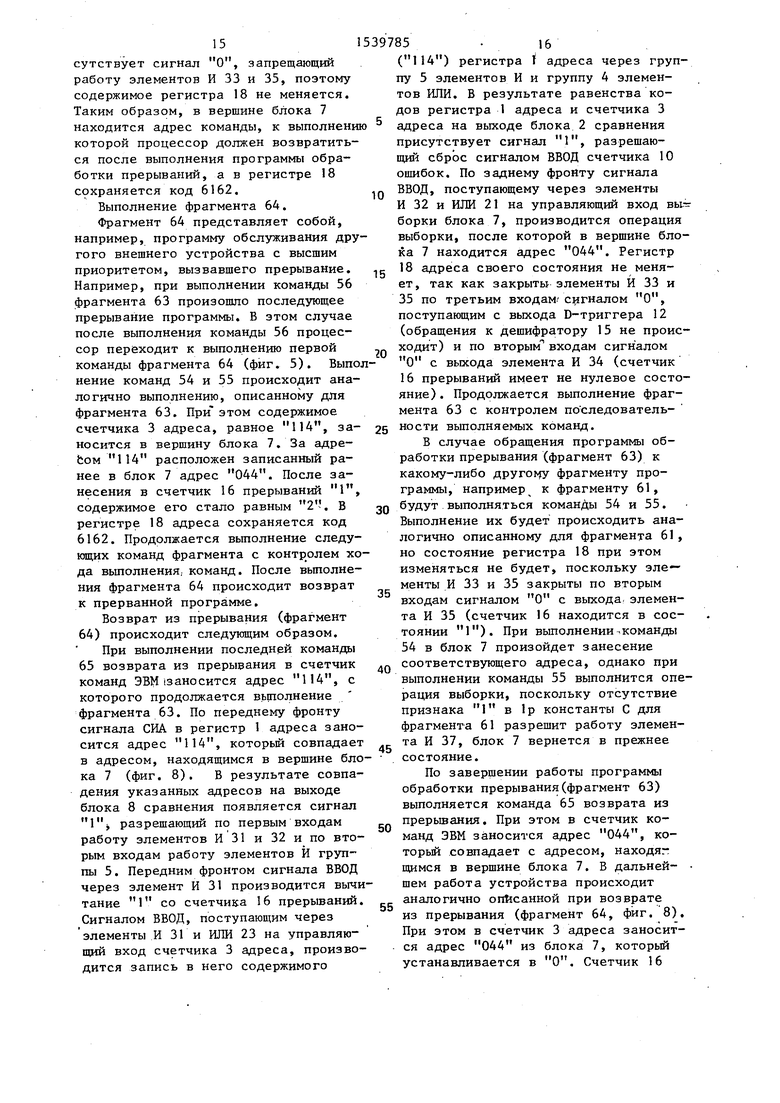

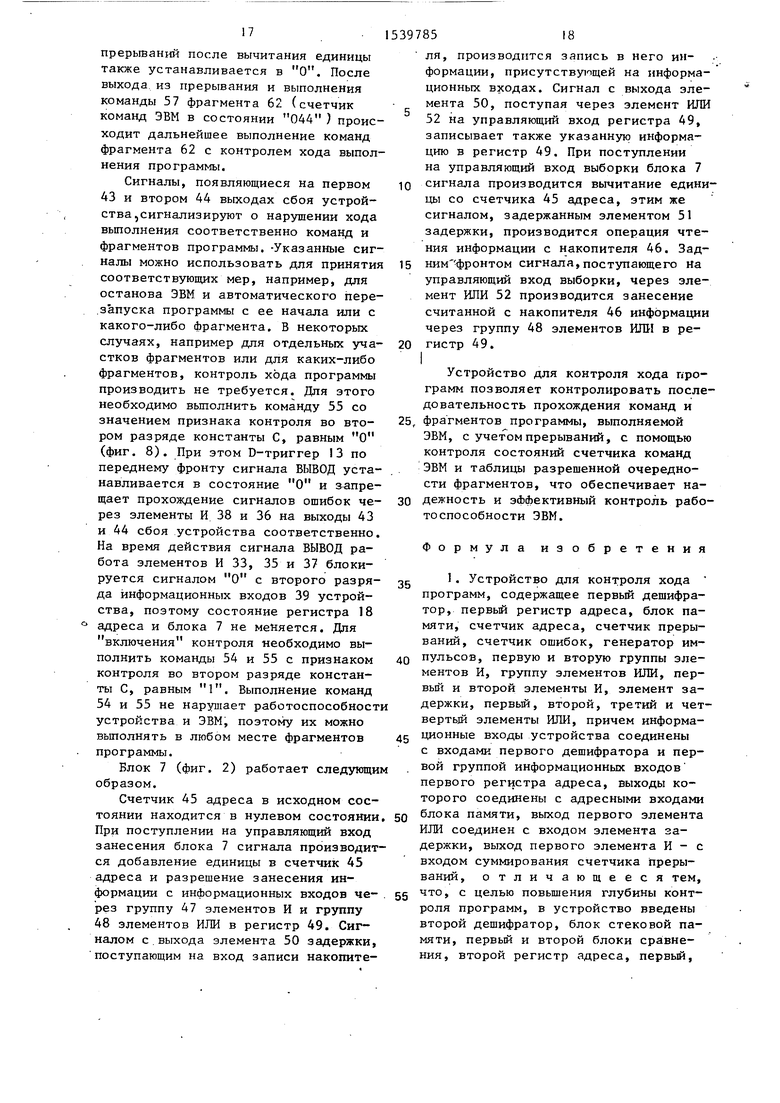

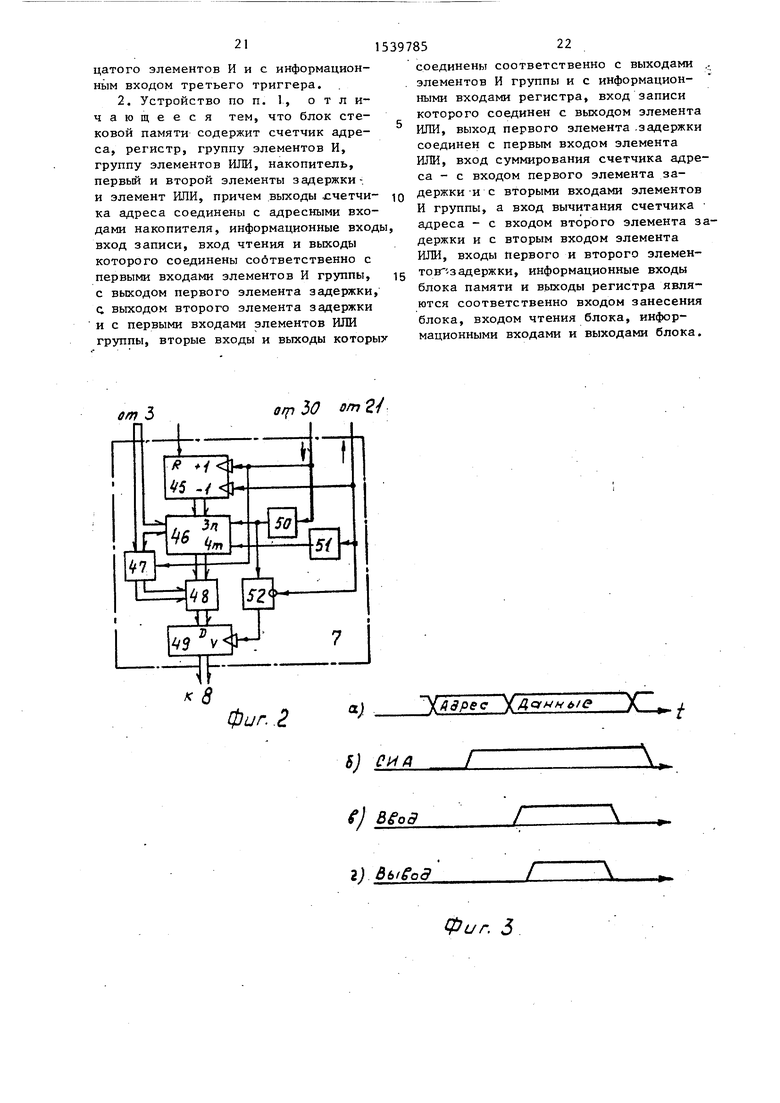

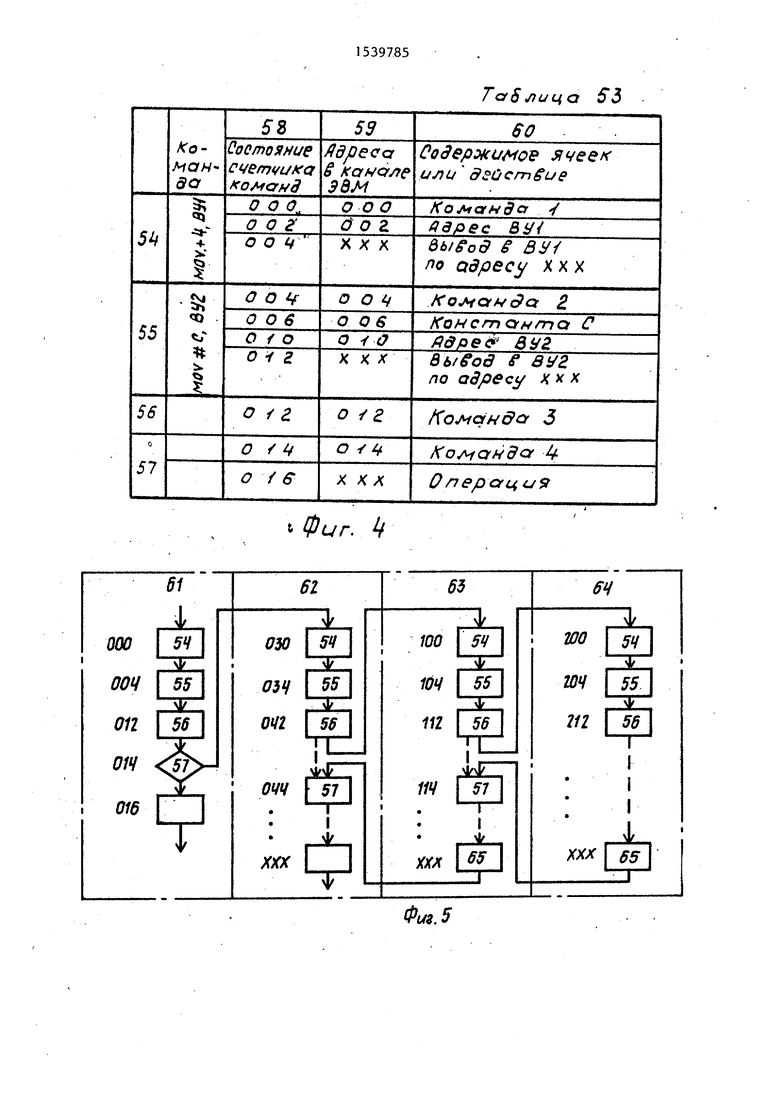

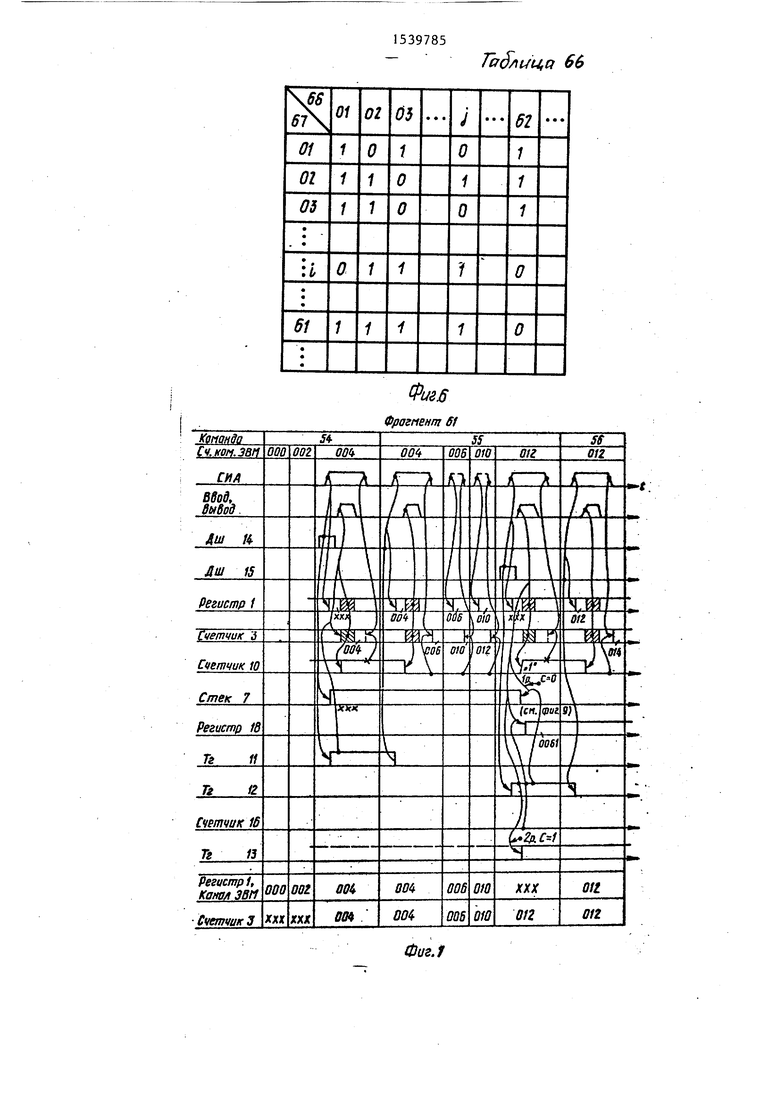

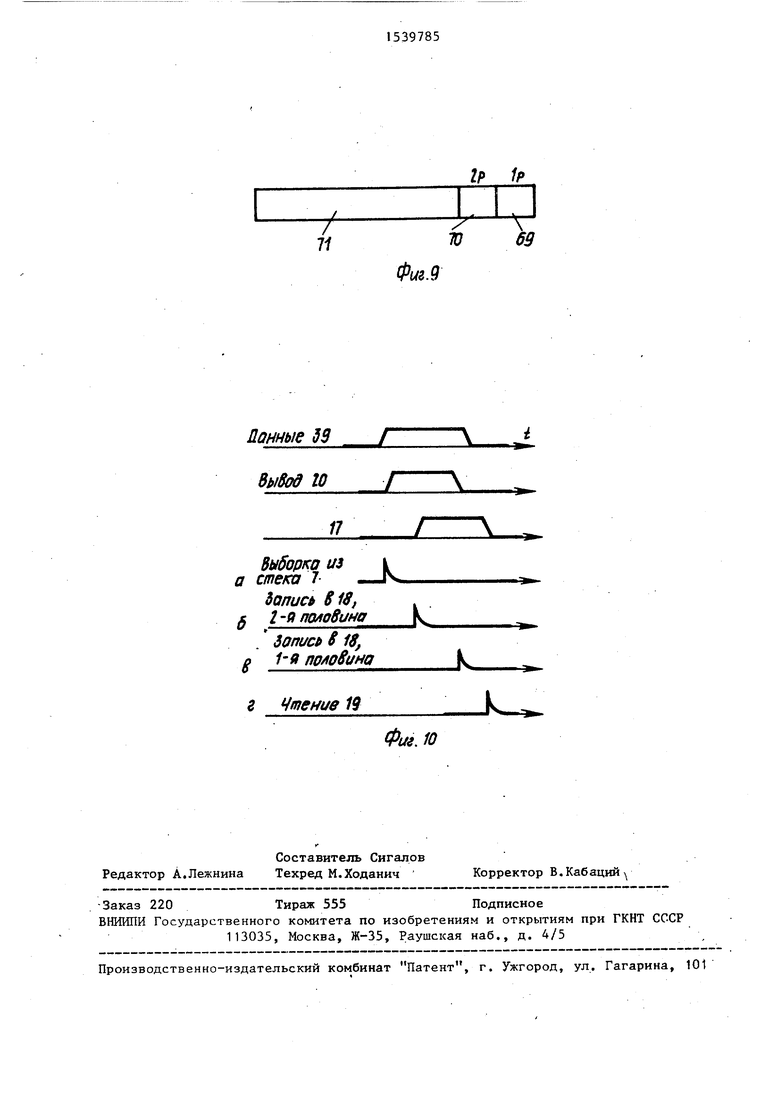

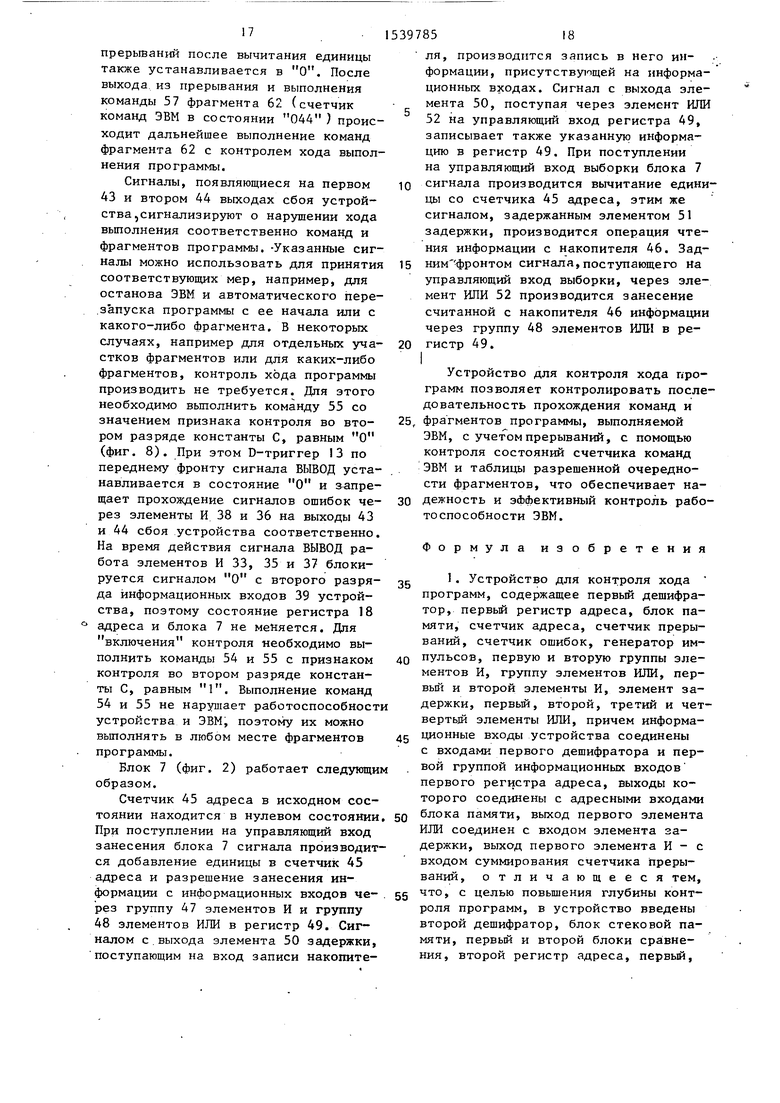

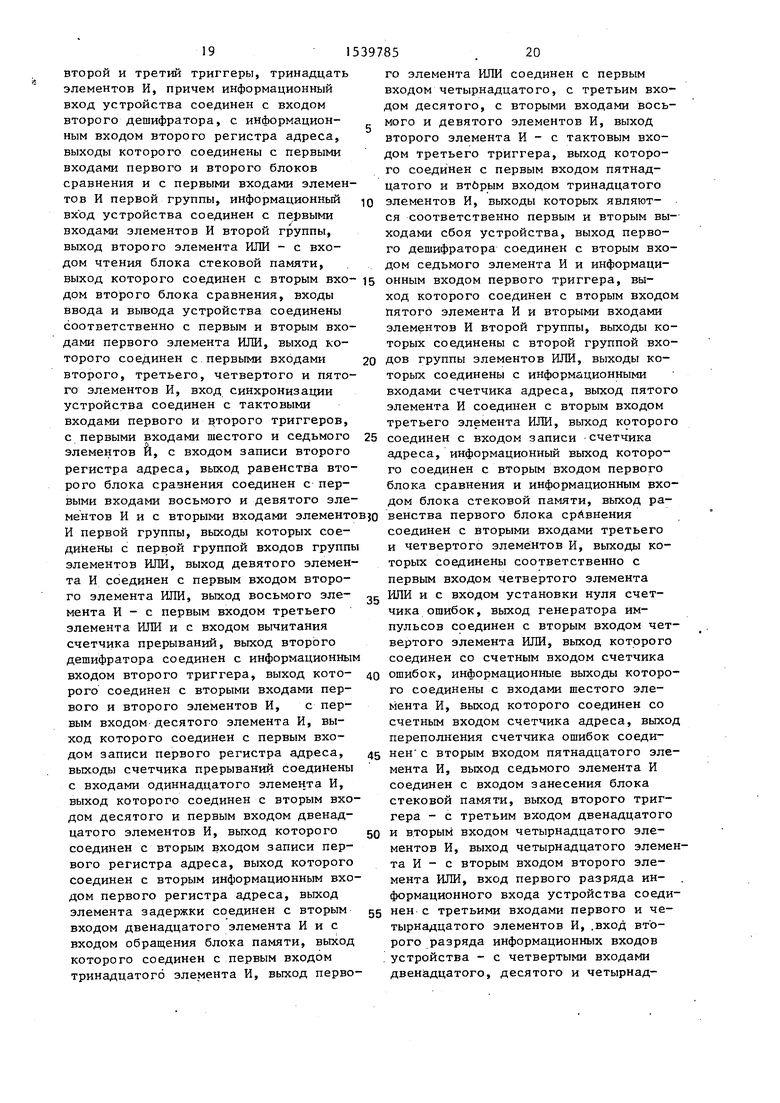

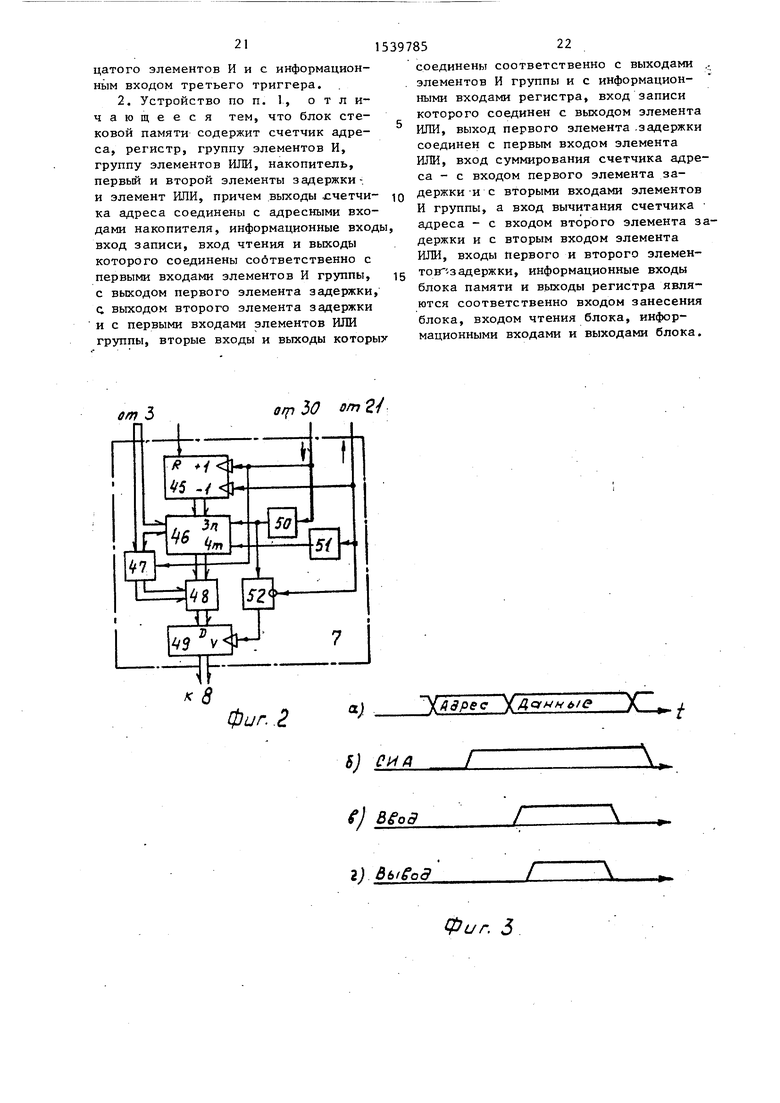

На фиг. 1 представлена структурная схема устройства для контроля .Q хода программы; на фиг. 2 - структурная схема блока стековой памяти; на фиг. 3 - диаграммы сигналов ЭВМ с общей шиной: а - диаграмма сигналов информационных шин контролируемого ,- канала; б - диаграмма сигнала синхронизации активного устройства (СИЛ); в и г - диаграммы сигналов соответственно ВВОД и ВЫВОД; на фиг. 4 - таблица команд ЭВМ с разбивкой по опера- JQ ции; на фиг. 5 - пример фрагментов выполняемой программы; на фиг. 6 - таблица разрешенной очередности фрагментов; на фиг. 7 и 8 - временные диаграммы работы устройства; на 25 фиг.. 9.- формат константы; на фиг.10- ди-аграммы сигналов при занесении информации в первый регистр адреса.

Устройство для контроля хода провыми входами элементов И первой группы 5, выходы которых соединены с первыми входами группы 4 элементов ИЛИ. Информационные входы и выходы блока 7 соединены соответственно с выходами счетчика 3 адреса и первыми входами второго блока 8 сравнения, выход которого соединен с вторыми входами элементов И первой группы 5 и первыми входами восьмого 31 и девятого 32 элементов И, выходы которых соединены соответственно с вторыми входами четвертого 23 и второго 21 элементов ИЛИ. Вход 42 сигнала синхронизации соединен с первым входом седьмого элемента И 30, управляющим входом второго регистра 1 адреса, С-входами первого 1 1 и второго 12 D-триггеров и вторым инверсным входов шестого элемента И 29, первые входы которого соединены с инверсными входами счетчика 10 ошибок, а выход - со счетным входом счетчика 3 адреса, управляющий вход которого соединен с выходом четвертого элемента ИЛИ 23. Вход 40 сигнала ВВОД и вход 41 сигнала ВЫВОД соединены соответственно с первым и вторым входами первого элемента ИЛИ

грамм (фиг. 1) содержит второй регистр 20 выход которого соединен с первыми

1 адреса, первьй блок 2 сравнения, счетчик 3 адреса, группу 4 элементов ИЛИ, первую 5 и вторую 6 группы элементов И, блок 7 стековой памяти, второй блок 8 сравнения, генератор 9 импульсов, счетчик 10 ошибок, первый 11, второй 12 и третий 13 D-триггеры, первьй 14 и второй 15 дешифраторы, счетчик 16 прерываний, элемент 17 задержки, первьй регистр 18 адреса, блок 19 памяти, первьй 20, второй 21, третий 22 и четвертый 23 элементы ИЛИ, элементы И 24-38, информационные входы 39 устройства, вход 40 сигнала ВВОД, вход 41 сигнала ВЫВОД, вход 42 сигнала синхронизации и первьй 43 и второй 44 выходы сбоя. Информационные входы второго регистра 1 соединены с информационными входами 39 устройства, входами первого 14 и второго 15 дешифраторов, первыми информационными входами первого регистра 18 адреса и первыми входами элементов И второй группы 6, выходы которых соединены с вторыми входами группы 4 элементов ИЛИ. Выходы второго регистра 1 адреса-соединены с первыми входами первого 2 и второго 8 блоков сравнения и пер35

40

45

50

55

входами первого 24, третьего 26, четвертого 27, пятого 28 и четырнадцатого 37 элементов И, вторыми входами второго 25 и восьмого 31 элементов И, первым инверсным и .вторым инверсным входами соответственно десятого 33 и девятого .32 элементов И и входом элемента 17 задержки, выход которого сое динен с первым входом двенадцатого элемента И 35 и инверсным входом чтения блока 19 памяти. Входы первого блока 2 сравнения соединены с выходами счетчика 3 адреса, информационные входы которого соединены с выходами группы 4 элементов ИЛИ, а выход блока 2 сравнения соединен с вторыми входами третьего 26 и четвертого 27 элементов И, выходы которых соединены соответственно с первым входом четвертого элемента ИЛИ 22 и входом сброса счетчика 10 ошибок, выход переноса которого соединен с первым входом пятнадцатого элемента И 38, а счетный вход - с выходом четвертого элемента ИЛИ 22, второй вход которого соединен с выходом генератора 9 импульсов. Выход первого дешифратора 14 соединен с D-входом первого D-триггера 11 и

выми входами элементов И первой группы 5, выходы которых соединены с первыми входами группы 4 элементов ИЛИ. Информационные входы и выходы блока 7 соединены соответственно с выходами счетчика 3 адреса и первыми входами второго блока 8 сравнения, выход которого соединен с вторыми входами элементов И первой группы 5 и первыми входами восьмого 31 и девятого 32 элементов И, выходы которых соединены соответственно с вторыми входами четвертого 23 и второго 21 элементов ИЛИ. Вход 42 сигнала синхронизации соединен с первым входом седьмого элемента И 30, управляющим входом второго регистра 1 адреса, С-входами первого 1 1 и второго 12 D-триггеров и вторым инверсным входов шестого элемента И 29, первые входы которого соединены с инверсными входами счетчика 10 ошибок, а выход - со счетным входом счетчика 3 адреса, управляющий вход которого соединен с выходом четвертого элемента ИЛИ 23. Вход 40 сигнала ВВОД и вход 41 сигнала ВЫВОД соединены соответственно с первым и вторым входами первого элемента ИЛИ

20 выход которого соединен с первыми

5

0

5

0

5

входами первого 24, третьего 26, четвертого 27, пятого 28 и четырнадцатого 37 элементов И, вторыми входами второго 25 и восьмого 31 элементов И, первым инверсным и .вторым инверсным входами соответственно десятого 33 и девятого .32 элементов И и входом элемента 17 задержки, выход которого соединен с первым входом двенадцатого элемента И 35 и инверсным входом чтения блока 19 памяти. Входы первого блока 2 сравнения соединены с выходами счетчика 3 адреса, информационные входы которого соединены с выходами группы 4 элементов ИЛИ, а выход блока 2 сравнения соединен с вторыми входами третьего 26 и четвертого 27 элементов И, выходы которых соединены соответственно с первым входом четвертого элемента ИЛИ 22 и входом сброса счетчика 10 ошибок, выход переноса которого соединен с первым входом пятнадцатого элемента И 38, а счетный вход - с выходом четвертого элемента ИЛИ 22, второй вход которого соединен с выходом генератора 9 импульсов. Выход первого дешифратора 14 соединен с D-входом первого D-триггера 11 и

51

вторым входом седьмого элемента И , 30, выход которого соединен с управляющим входом занесения блока 7, управляющий вход выборки которого соединен с выходом второго элемента ИЛИ 21. Выход первого D-триггера 11 соединен с вторыми входами элементов И второй группы 6 fi вторым входом пятого элемента И 28, выход которого соединен с первым входом третьего элемента ИЛИ 23. Выход второго дешифратора 15 соединен с D-входом второго D-триггера 12, выход которого соединен с первым входом второго элемента И 25, вторыми входами первого 24 и четырнадцатого 37 элементов И, третьими входами десятого 33 и двенадцатого 35 элементов И, вторые и четвертые входы которых соединены соответственно с выходом одиннадцатого элемента И 34 и третьим входом четырнадцатого элемента И 37, четвертый инверсный вход и выход которого соединены соответственно с третьим входом первого элемента И 24, первым разрядом информационных входов 39 устройства и первым входом второго элемента ИЛИ 21. Второй разряд информационных входов 39 соединен с третьим входом четырнадцатого элемента И 37 и D-входом третьего D-триггера 13, С-вход и выход которого соединены соответственно с выходом второго элемента И 25 и вторыми входами тринадцатого 36 и пятнадцатого 38 элементов И, выходы которых соединены соответственно с вторым 44 и первым 43 выходами сбоя, а первый вход тринадцатого элемента И 36 соединен с выходом блока 19 памяти. Выход первого элемента И 24 соединен со счетным входом,суммирования счетчика 16 прерываний, счетный вход вычитания которого соединен с выходом восьмого элемента И 31. Выходы десятого 33 и двенадцатого 35 элементов И соединены соответственно с первым и вторым входами первого регистра 18 адреса, выходы которо.го соединены с адресными входами блока 19 памяти, а первые выходы первого регистра 18 адреса соединены с его вторыми информационными входами.

Блок 7 стековой памяти (фиг. 2) содержит счетчик 45 адреса, накопитель 46, группу 47 элементов И, группу 48 элементов ИЛИ, регистр 49, первьй 50 и второй 51 элементы за10

20

25

397856

держки и элемент ИЛИ 52, причем выходы счетчика 45 адреса соединены с адресными входами накопителя 46, информационные входы которого соедине- ны с первыми входами группы 47 элементов И и являются информационными входами блока 7. Выходы накопителя 46 и выходы группы 47 элементов И соединены соответственно с первыми и вторыми входами группы 48 элементов ИЛИ, выходы которых соединены с информационными входами регистра 49, выходы которого являются выходами 15 блока 7, а управляющий вход регистра 49 соединен с выходом элемента ИЛИ 52. Счетный вход суммирования счетчика 45 адреса соединен с входом первого элемента 50 задержки, вторыми входами группы 47 элементов И и является управляющим входом занесения блока 7. Счетный вход вычитания счетчика 45 адреса соединен с входом второго элемента 51 задержки, вторым инверсным входом элемента ИЛИ 52 и является управляющим входом занесения блока 7. Выход первого элемента 50 задержки соединен с управляющим входом записи накопителя 46 и первым входом элемента ИЛИ 52, а выход второго элемента 51 задержки соединен с управляющим входом чтения накопителя 46.

Устройство работает следующим образом.

Работу устройства рассмотрим на примере ЭВМ с общей шиной. Выполняя программу, ЭВМ выполняет непрерывную последовательность команд. Выполнение команды начинается с операции по выборке команды. Для выполнения любой команды процессору требуется выполнить хотя бы одну операцию обращения к каналу. Для некоторых команд требуется выполнить несколько операций. Первой такой операцией для всех команд является ввод данных из ячейки памяти ЭВМ, адрес которой определяется счетчиком команд. Все операции обращения к каналу для ввода и вывода данных назовем циклами обращения к каналу. После дешифрации команды процессор начинает операцию по выборке операндов, инициируя, если это необходимо, в зависимости от кода команды и метода адресации один или несколько циклов ввода. Далее производится операция по выполнению команды и, если требуется записать резуль30

35

40

45

50

55

тат в память или регистр ВУ, здесь и в дальнейшем ВУ - внешнее устройство, начинается цикл вывода. Затем процессор может начать операцию об- служивания,которая вызывается выполнением внутренних или внешних прерываний. Для различных команд последовательность операций может быть различной. Но любую из команд процессор начинает с операции по выборке команды, переходя затем к выполнению какой-либо другой операции или к их последовательности. В некоторых случаях после операции выборки текущей команды процессор может перейти к операции выборки следующей команды, для чего ему требуется выполнить хотя бы одну операцию обращения к каналу. Как правило, ЭВМ с общей шиной выполняют байтовые операции, поэтому, когда процессор использует счетчик команд для выборки слова из памяти ЭВМ, его содержимое автоматически увеличивается на 2. Новое содержимое счетчика команд являет.ся адресом слова используемого при выполнении данной команды, или адресом следующей команды, которую необходимо выполнить

На фиг. 4 в таблице 53 представлены для примера некоторые команды с разбивкой по операциям: команда 1 - MOV. +4, ВУ1, определяющая вывод значения счетчика команд, увеличенного на 4 единицы, в регистр ВУ1; команда 2 - MOV#C, ВУ2, определяющая вывод константы С в регистр внешнего устройства ВУ2; команды 3 и 4 - любые команды ЭВМ. В строках 54-57 таблицы 53 показаны указанные команды, в столбце 58 - коды счетчика команд, которые он имеет при выполнении команд; в столбце 59 - коды адресов, которые пересылаются в канале ЭВМ при выполнении указанных команд; в столбце 60 - содержимое ячеек или регистров с адресами, указанными в столбце 59. Значения кодов счетчика команд и адресов здесь и далее отно- сительные и приведены в восьмиричных кодах. Знаками XXX указаны произвольные значения кодов.

В -процессе выполнения ЭВМ программы производится выполнение команд, следующих по порядку, или происходит переход по новому адресу по командам условного и .безусловного перехода и по прерываниям от ВУ.

На фиг. 5 показан пример выполнения фрагментов программы: Фрагмент

61- программа выполнения команд, следующих друг за другом; фрагмент

62- программа, к которой происходит переход по новому адресу в результате выполнения заданного условия; фрагмент 63 - программа обслуживания устройства 1, вызвавшего прерывание; фрагмент 64 - программа обслуживания устройства 2, вызвавшего прерывание.

На фиг. 5 команды изображены прямугольниками, внутри которых помещены позиции команд в соответствии с таблицей 53, слева от прямоугольников помещены значения кодов счетчика команд.

65 - команда возврата из прерывания.

Как видно из таблицы 53 (фиг. 4) и из фрагментов 61-64 (фиг. 5),счетчик команд в пределах каждого фрагмента занимает последовательные состояния с дискретностью наращивания, равной 2. При переходе программы из одного фрагмента к другому код счетчика изменяется в зависимости от структуры программы. Код адреса в канале ЭВМ, кроме упорядоченных значений кодов счетчика, принимает периодически значения произвольных кодов, определяемые местом положения операндов в памяти ЭВМ. Аппаратного доступа к счетчику команд в ЭВМ не имеется, доступ возможен только к каналу ЭВМ.Способом контроля хода выполнения программы является контроль последовательности кодов состояний счетчика команд ЭВМ с помощью дублирующего счетчика 3 адреса в устройстве для контроля по векторам адресов в канал ЭВМ. При переходе программы из одног фрагмента в другой производится программная запись нового адреса в дублирующий счетчик 3 адреса устройства Учет произвольных кодов адресов, периодически появляющихся в канале ЭВМ и не совпадающих с кодами счетчика команд ЭВМ, производится счетчиком 1 ошибок, выход переноса которого является сигналом ошибки хода выполне- ния программы. Разрядность счетчика 10 ошибок определяет зону нечувствительности устройства, количественно выражающуюся в числе не совпадающих произвольных кодов, следующих подряд друг за другом. При очередном совпадении кода счетчика команд ЭВМ, а значит, и кода счетчика 3 адреса с кодом адреса в канале ЭВМ происходит сброс в О счетчика 10 ошибок. Запоминание адресов возврата в случае прерывания программы внешними устройствами производится в блоке 7, глубина прерываний, т.е. крличество программ обработки прерываний, следую- ,щих подряд друг за другом, фиксируется счетчиком 16 прерываний. Последовательность выполнения фрагментов программы контролируется путем сравнения выполняемой последовательности с таблицей разрешенной очередности, записанной в блок 19 памяти. Таблица 66 очередности (фиг. 6) представляет

собой матрицу с элементами 0 и 1

Hi

заносится из блока памяти ЭВМ в процессор код команды 1, счетчик команд устанавливается в состояние 002. По этому адресу заносится в процессор адрес ВУ1, которым является дешифратор 14, счетчик команд ЭВМ при этом устанавливается в состояние 004. После этого производится цикл вывода. В канале ЭВМ, а значит, и на информационных входах 39 устройства появляется адрес ВУ1, который дешифрируется дешифратором 14, на выходе которого появляется сигнал 1. По- сле,,установки адреса процессором вырабатывается сигнал СИА (фиг. 3), поступающий на вход 42 устройства, по переднему бронту которого заносится адрес в регистр 1 адреса, устанавливается в 1 D-триггер 11, по. сигналу через элемент И 30 производится занесение в блок 7 содержимого счетчика 3 адреса (фиг. 7). После этого на информационных входах

20

В столбце 67 и в строке 68 таблицы 66 указаны номера всех фрагментов программы, которая выполняется. Столбец 67 обозначает фрагменты, которые выполняются в данный момент, а строка 68 - фрагменты, которые могут еле- 25 39 устройства появляются данные, довать за ними. Код О, расположен- значение которых равно коду счетчика ньй в пересечении i-й строки с j-м команд ЭВМ, относящемуся к выполняе- столбцом, означает, что фрагменту с мой команде (000), увеличенному номером j разрешено следовать после на 004, а на вход 41 устройства от выполнения 1-го фрагмента, в противном 30 ЭВМ поступает сигнал ВЫВОД (фиг. 3), случае в пересечении находится код по которому в счетчик 3 адреса проJQ

39785Ю

заносится из блока памяти ЭВМ в процессор код команды 1, счетчик команд : устанавливается в состояние 002. По этому адресу заносится в процессор адрес ВУ1, которым является дешифратор 14, счетчик команд ЭВМ при этом устанавливается в состояние 004. После этого производится цикл вывода. В канале ЭВМ, а значит, и на информационных входах 39 устройства появляется адрес ВУ1, который дешифрируется дешифратором 14, на выходе которого появляется сигнал 1. По- сле,,установки адреса процессором вырабатывается сигнал СИА (фиг. 3), поступающий на вход 42 устройства, по переднему бронту которого заносится адрес в регистр 1 адреса, устанавливается в 1 D-триггер 11, по. сигналу через элемент И 30 производится занесение в блок 7 содержимого счетчика 3 адреса (фиг. 7). После этого на информационных входах

15

20

25 39 устройства появляются данные, значение которых равно коду счетчика команд ЭВМ, относящемуся к выполняе- мой команде (000), увеличенному на 004, а на вход 41 устройства от 30 ЭВМ поступает сигнал ВЫВОД (фиг. 3), по которому в счетчик 3 адреса про

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля хода программ | 1989 |

|

SU1645960A1 |

| Устройство для прерывания программ | 1985 |

|

SU1256029A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| Устройство для отладки микропроцессорной системы | 1987 |

|

SU1453408A1 |

| Устройство для контроля выполнения программ | 1989 |

|

SU1709319A1 |

| Устройство для отладки программно-аппаратных комплексов | 1990 |

|

SU1795464A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1988 |

|

SU1536393A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЭЛЕКТРОННОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1992 |

|

RU2066877C1 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля хода выполнения программ ЭВМ, работающих в реальном масштабе времени. Цель изобретения - повышение глубины контроля хода программ. Устройство для контроля хода программ содержит два регистра адреса 1 и 18, два блока сравнения 2 и 8, счетчик 3 адреса, счетчик 10 ошибок, счетчик 16 прерываний, блок 19 памяти, блок 7 стековой памяти, три D-триггера 11, 12 и 13, элементы И 24-38, элементы ИЛИ 22, 23, элемент 17 задержки. Устройство обеспечивает контроль хода выполнения программы ЭВМ путем контроля последовательности состояний счетчика команд ЭВМ с помощью дублирующего счетчика адреса в устройстве по векторам адресов в канале ЭВМ. 1 з.п. ф-лы, 9 ил.

после фрагмента с номером 01. В слу- 35 ИЛИ поступают на информационные вхо

чае, если фрагмент 02 начнет выполняться после какого-либо другого фрагмента, на выходе блока 19 памяти появится сигнал ошибки хода выполнения программы. Адресами для блока 19 памяти являются коды, составленные из номеров столбца 67.и строки 68. Для указанного пример а код адреса - 0102.

Работа устройства начинается с начальной установки в О счетчика 16 прерываний, счетчика 45 адреса блока 7 и первого регистра 18 адреса (цепи установки в О на фиг. 1 не показаны) . Сигналом начальной установки может быть, например, сигнал начальной установки всех устройств, подключенных к каналу, вырабатываемый процессором ЭВМ при включении питания ЭВМ. Каждый фрагмент программ начинается командами 54 и 55.

Выполнение фрагмента 61 (фиг. 5). При выполнении команды 54 производятся следующие действия (фиг. 4). При состоянии счетчика команд ЭВМ 000

40

ды счетчика 3 адресата сигнал ВЫВОД через элемент ИЛИ 20, элемент И 28 и элемент ИЛИ 23 - на управляющий вход Так как коды регистра 1 адреса и счетчика 3 адреса не совпадают, то на выходе блока 2 сравнения присутствует сигнал О, разрешающий прохождение сигнала ВЫВОД через элемен И 26 и элемент ИЛИ 22 на счетный вхо

45 счетчика 10 ошибок, который увеличивает свое содержимое на единицу (фак несовпадения кодов на фиг. 7 показан разными направлениями штриховки на эпюрах сигналов регистра 1 адреса и счетчика 3 адреса). Поскольку счетчи 10 ошибок находится не в нулевом сос тоянии, сигнал заднего фронта сигнал СИА через элемент И 29 не проходит на счетчик 3 адреса. На фиг. 7 раз

55 решающее действие сигналов показано точкой, а запрещающее - крестиком. Сигнал ВЫВОД ,задержанный элементом задержки, поступает на вход чтения блока 19 памяти. По заднему сЬронту

50

изводится занесение указанных данных (фиг. 7): данные через группу 6 элементов И и через группу 4 элементов

ИЛИ поступают на информационные вхо

ды счетчика 3 адресата сигнал ВЫВОД через элемент ИЛИ 20, элемент И 28 и элемент ИЛИ 23 - на управляющий вход. Так как коды регистра 1 адреса и счетчика 3 адреса не совпадают, то на выходе блока 2 сравнения присутствует сигнал О, разрешающий прохождение сигнала ВЫВОД через элемент И 26 и элемент ИЛИ 22 на счетный вход

счетчика 10 ошибок, который увеличивает свое содержимое на единицу (факт несовпадения кодов на фиг. 7 показан разными направлениями штриховки на эпюрах сигналов регистра 1 адреса и счетчика 3 адреса). Поскольку счетчик 10 ошибок находится не в нулевом состоянии, сигнал заднего фронта сигнала СИА через элемент И 29 не проходит на счетчик 3 адреса. На фиг. 7 разрешающее действие сигналов показано точкой, а запрещающее - крестиком. Сигнал ВЫВОД ,задержанный элементом 17 задержки, поступает на вход чтения блока 19 памяти. По заднему сЬронту

111

данного сигнала производится чтение данных по адресу, определяемому регистром 18 адреса. Так как адрес равен О, на выходе блока памяти сигнал не появляется. Действие команды 54 завершается.

Выполняется следующая команда 55, при этом производятся следующие действия. При состоянии счетчика команд ЭВМ 004 заносится из блока памяти ЭВМ в процессор код команды 2. По переднему фронту сигнала СИЛ адрес 004 с информационных входов 39 устройства заносится в регистр 1 адреса, D-триггер 11 устанавливается в состояние О, так как на выходе дешифратора 14 теперь присутствует сигнал О. После этого на вход 40 устройства поступает сигнал ВВОД. По- скольку коды регистра 1 адреса и счечика 3 адреса совпадают, на выходе блока 2 сравнения присутствует сигнал О, открывающий по инверсному

входу элемент И 27. Сигнал ВВОД через 25 го ранее адреса (фиг. 10,а), после элементы ИЛИ 20 и И 27 сбрасывает чего на выходах блока 7 присутствуют

ечетчик 20 ошибок в нулевое состояние. По заднему фронту СИА срабатывает элемент И 29, на первых входах которого присутствуют сигналы 1 с инверсных выходов счетчика 10 ошибок, и в счетчик 3 адреса заносится 1 (следует иметь в виду, что вес млад- ших разрядов регистра 1 адреса и

сигналы О. Счетчик 16 прерываний находится в нулевом состоянии, разрешая работу элемента И 34, сигнал 30 1 с которого поступает на вторые входы элементов И 33 и 35, поэтому задержанный элементом 17 задержки сигнал ВЫВОД через элемент И 35 поступает на второй управляющий вход

счетчика 3 адреса равен 2, поскольку 35 Регистра 18 адреса и передним фрон- коды адресов в канале четные) .Состо- том производит запись информации с яние счетчика 3 адреса становится рав- первой половины регистра 18 во вто- ным 006. После выполнения процес- РУю (Фиг. 10,6). В данный момент сором цикла ввода кода команды 2 счет- информация равна О. После этого чик команд ЭВМ устанавливается в сое- 10 задним фронтом сигнала ВЫВОД через тояние 006. После этого выполняется элемент И 33 производится запись в цикл ввода константы С, после которого состояния счетчика команд ЭВМ и счетчика 3 адреса равны 010. Затем выполняется цикл ввода адреса ВУ2, 45 (Фиг. Ю,в), после чего производит- после чего состояния указанных счет- ся чтение информации в блоке 19 па- чиков равны 012. После этого выполняется цикл вывода. На информационных входах 39 устройства появляется адпервую половину регистра 18 адреса номера фрагмента, присутствующего на информационных входах 39 устройства

мяти по адресу регистра 18 задним фронтом задержанного сигнала ВЫВОД (фиг. 10,г). В данном случае инфоррес ВУ2, который дешифрируется дешиф- 50 мация на выходе блока 19 памяти рав- ратором 15, на выходах которого появ- на О, так как фрагмента с4номером

1П. После установки 00 в матрице нет (фиг. 6). Поскольку коды регистра 1 адреса и счетчика 3 адреса не совпадают, на выходе 55 блока 2 сравнения присутствует сигнал 1, разрешающий работу элемента И 26 по второму входу. Сигнал ВЫВОД передним фронтом через элементы И 26 и ИЛИ 22 запишет 1 в счетчик 10

ляется сигнал

адреса процессором вырабатывается сигнал СИА (фиг. 3), по переднему фронту которого занрсится в регистр 1 адреса адрес ВУ2 и D-триггер 12 устанавливается в 1. После этого, на информационных входах 39 появляется значение константь С. Формат кон0

9785

0

12

станты С показан на фиг. 9. В 1-м разряде (поле 69) находится признак 1, если это фрагмент, программы обработки прерываний, и О - если это очередной фрагмент, во 2-м разряде (поле 70) находится признак 1 необходимости контроля хода программы, в остальных разрядах (поле 71) - номер фрагмента. На вход 41 устройства поступает сигнал ВЫВОД, по которому выполняются следующие действия. Если признак контроля хода программы равен 1, D-триггер 13 сигналом 5 ВЫВОД через элементы ИЛИ 20 и И 25 устанавливается в VI, и разрешается работа .элемента И 37 по третьему входу и элементовtИ 33 и 35 по четвертому входу. Бели признак фрагмента в поле 69 (фиг. 9) равен О, что соответствует выполнению фрагмента 61 (фиг. 5), то сигналом ВЫВОД через элементы И 37 и ИЛИ 21 производится выборка из блока 7 занесенного в несигналы О. Счетчик 16 прерываний находится в нулевом состоянии, разрешая работу элемента И 34, сигнал 1 с которого поступает на вторые входы элементов И 33 и 35, поэтому задержанный элементом 17 задержки сигнал ВЫВОД через элемент И 35 поступает на второй управляющий вход

Регистра 18 адреса и передним фрон- том производит запись информации с первой половины регистра 18 во вто- РУю (Фиг. 10,6). В данный момент информация равна О. После этого задним фронтом сигнала ВЫВОД через элемент И 33 производится запись в (Фиг. Ю,в), после чего производит- ся чтение информации в блоке 19 па-

первую половину регистра 18 адреса номера фрагмента, присутствующего н информационных входах 39 устройства

Регистра 18 адреса и передним фрон- том производит запись информации с первой половины регистра 18 во вто- РУю (Фиг. 10,6). В данный момент информация равна О. После этого задним фронтом сигнала ВЫВОД через элемент И 33 производится запись в (Фиг. Ю,в), после чего производит- ся чтение информации в блоке 19 па-

мяти по адресу регистра 18 задним фронтом задержанного сигнала ВЫВОД (фиг. 10,г). В данном случае инфор13

ошибок, сигнал О с инверсного выхода первого разряда которого запретит работу элемента И 29, что не позволит пройти заднему фронту сигнала СИА на счетный вход счетчика 3 адреса, который остался в состоянии 012. На этом выполнение команды 55 заканчивается.

Выполняется следующая команда 56. При этом передним фронтом сигнала СИА в регистр 1 адреса с информационных входов 39 устройства заносится код счетчика команд ЭВМ, равный 012 D-триггер 12 устанавливается в О. Совпадение кодов регистра 1 адреса и счетчика 3 адреса приводит к сбросу в О счетчика 10 ошибок сигналом

1

Выполнение фрагмента 63. Фрагмент 63 представляет собой, например, программу обслуживания

ВВОД через элемент И 27 и добавлению 1 в счетчик 3 адреса по заднему фрон- 20 внешнего устройства, вызвавшего п&ерывание, т.е. программу обработки прерывания. Например, при выполнении команды 56 фрагмента 62 произошло прерывание программы (Фиг. 5). При

25 этом, гроцессор заканчивает выполнение команды 56, код счетчика команд ЭВМ и код счетчика 3 адреса становятся равными 044. Затем в результате выполнения операций по прерыванию

30 программы код счетчика команд ЭВМ становится равным адресу первой команды программы прерывания (в данном примере 100) и выполняется первая команда 54 фрагмента 63 аналогично

35 описанной для фрагмента 61. Содержимое счетчика 3 адреса заносится в блок 7. Значение кода счетчика команд ЭВМ, увеличенное на 4 (104), заносится в счетчик 3 адреса. Из-за

4Q несовпадения кодов регистра 1 адреса и счетчика 3 адреса увеличение содержимого последнего не происходит.Следующая команда 55 выполняется аналогично описанной для фрагмента 61, но

45 при выполнении последней операции вывода (код счетчика команд ЭВМ равен 112, см. фиг., 8) имеются следующие отличия. В первом разряде (поле 69, фиг. 9) находится признак

50 признак программы прерывания, . поэтому выборки из блока 7 сигналов ВЫВОД не происходит, поскольку, элемент И 37 закрыт по четвертому входу сигналом с первого разряда ин55 формационных входов 39 устройства. По переднему фронту сигнала ВЫВОД в (счетчик 16 прерываний через открытый элемент И 24 заносится 1, в связи с чем на выходе элемента И 34 приту сигнала СИА через элемент И 29, после чего его код равен 014.

В дальнейшем выполняются последующие команды фрагмента 61. Счетчик 10 накапливает единицы в случаях несовпадения адреса в канале ЭВМ и кода в счетчике 3 адреса, что происходит при обращении процессора по произвольному адресу для получения операнда или к внешнему устройству. А в случае совпадения указанных адресов, что происходит по крайней мере всегда при выполнении процессором операции по выборке команды, с которой начинается выполнение любой команды, счетчик 10 ошибок сбрасывается в О. Если нарушается ход выполнения программы, то коды счетчика команд ЭВМ и счетчика 3 адресов не совпадают, счетчик 10 ошибок переполняется, и сигнал с его выхода переноса через элемент И 38 поступает на первый выход 43 сбоя устройства, сигнализируя об ошибке в ходе выполнения команд.

Выполнение фрагмента 62. Например, после выполнения команды 57 фрагмента 61 в результате УСЛОВНОГО перехода процессор переходит к выполнению фрагмента 62 (Лиг. 5). В этом случае происходит выполнение команд

54и 55 аналогично описанному для фрагмента 61, но с учетом других кодов счетчика команд ЭВМ. При этом во время выполнения операции команды

55вывода информации в ВУ2 номер фрагмента 61 переписывается с первой половины регистра 18 во вторую, а в первую половину записывается номер

,

539785 Ь

фрагмента 62. По заднему фронту задержанного сигнала ВЫВОД производится чтение блока 19 памяти. В бите, определемом адресом 6162, находится признак О, поэтому сигнала ошибки на выходе блока 19 не будет. Если же переход программы произойдет ошибочно от фрагмента 61 к какому либо

10 другому фрагменту, например к фрагменту 03, тогда при чтении информации с блока 19 памяти по адресу 6103 на втором выходе 44 сбоя устройства появится сигнал 1, сигнализирую15 щий-.об ошибке в ходе выполнения фрагментов программы.

Выполнение фрагмента 63. Фрагмент 63 представляет собой, например, программу обслуживания

20 внешнего устройства, вызвавшего п&е

15

сутствует сигнал О, запрещающий работу элементов И 33 и 35, поэтому содержимое регистра 18 не меняется. Таким образом, в вершине блока 7 находится адрес команды, к выполнен которой процессор должен возвратиться после выполнения программы обработки прерываний, а в регистре 18 сохраняется код 6162,

Выполнение фрагмента 64.

Фрагмент 64 представляет собой, например, программу обслуживания другого внешнего устройства с высшим приоритетом, вызвавшего прерывание. Например, при выполнении команды 56 фрагмента 63 произошло последующее прерывание программы. В этом случае после выполнения команды 56 процессор переходит к выполнению первой команды фрагмента 64 (фиг. 5). Выпнение команд 54 и 55 происходит аналогично выполнению, описанному для фрагмента 63. При этом содержимое счетчика 3 адреса, равное 114, заносится в вершину блока 7. За адресом 114 расположен записанный ранее в блок 7 адрес 044. После занесения в счетчик 16 прерываний 1 содержимое его стало равным 2. В регистре 18 адреса сохраняется код 6162. Продолжается выполнение следующих команд фрагмента с контролем хда выполнения, команд. После выполнения фрагмента 64 происходит возврат к прерванной программе.

Возврат из прерывания (фрагмент 64) происходит следующим образом.

При выполнении последней команды 65 возврата из прерывания в счетчик команд ЭВМ заносится адрес 114, с которого продолжается выполнение фрагмента 63. По переднему фронту сигнала СИЛ в регистр 1 адреса заносится адрес 114, который совпадае в адресом, находящимся в вершине блка 7 (фиг. 8). В результате совпадения указанных адресов на выходе блока 8 сравнения появляется сигнал 1, разрешающий по первым входам работу элементов И 31 и 32 и по вторым входам работу элементов И группы 5. Передним фронтом сигнала ВВОД через элемент И 31 производится вычтание 1 со счетчика 16 прерываний Сигналом ВВОД, поступающим через элементы И 31 и ИЛИ 23 на управляющий вход счетчика 3 адреса, производится запись в него содержимого

5

0

5

9785

0

5

0

5

0

5

16

(114) регистра f адреса через группу 5 элементов И и группу 4 элементов ИЛИ. В результате равенства кодов регистра 1 адреса и счетчика 3 адреса на выходе блока 2 сравнения присутствует сигнал 1, разрешающий сброс сигналом ВВОД счетчика 10 ошибок. По заднему фронту сигнала ВВОД, поступающему через элементы И 32 и ИЛИ 21 на управляющий вход вы-- борки блока 7, производится операция выборки, после которой в вершине блока 7 находится адрес 044. Регистр 18 адреса своего состояния не меняет, так как закрыты элементы И 33 и 35 по третьим входам- сигналом О, поступающим с выхода D-триггера 12 (обращения к дешифратору 15 не происходит) и по вторым0 входам сигналом О с выхода элемента И 34 (счетчик 16 прерываний имеет не нулевое состояние) . Продолжается выполнение фрагмента 63 с контролем последовательности выполняемых команд.

В случае обращения программы обработки прерывания (фрагмент 63) к какому-либо другому фрагменту программы, например к фрагменту 61, будут выполняться команды 54 и 55. Выполнение их будет происходить аналогично описанному для фрагмента 61, но состояние регистра 18 при этом изменяться не будет, поскольку элементы И 33 и 35 закрыты по вторым входам сигналом О с выхода элемента И 35 (счетчик 16 находится в состоянии 1). При выполнении .команды 54 в блок 7 произойдет занесение соответствующего адреса, однако при выполнении команды 55 выполнится операция выборки, поскольку отсутствие признака 1 в 1р константы С для фрагмента 61 разрешит работу элемента И 37, блок 7 вернется в прежнее состояние.

По завершении работы программы обработки прерывания(фрагмент 63) выполняется команда 65 возврата из прерывания. При этом в счетчик команд ЭВМ заносится адрес 044, который совпадает с адресом, находят щимся в вершине блока 7. В дальней- шем работа устройства происходит аналогично описанной при возврате из прерывания (фрагмент 64, фиг. 8). При этом в счетчик 3 адреса заносится адрес 044 из блока 7, который устанавливается в О. Счетчик 16

прерываний после вычитания единицы также устанавливается в О. После выхода из прерывания и выполнения команды 57 фрагмента 62 (счетчик команд ЭВМ в состоянии 044 ) происходит дальнейшее выполнение команд фрагмента 62 с контролем хода выполнения программы.

Сигналы, появляющиеся на первом ю 43 и втором 44 выходах сбоя устройства,сигнализируют о нарушении хода выполнения соответственно команд и фрагментов программы. -Указанные сигналы можно использовать для принятия 15 соответствующих мер, например, для останова ЭВМ и автоматического перезапуска программы с ее начала или с какого-либо Фрагмента. В некоторых случаях, например для отдельных уча- 20 стков фрагментов или для каких-либо фрагментов, контроль хода программы производить не требуется. Для этого необходимо выполнить команду 55 со значением признака контроля во вто- 25, ром разряде константы С, равным О (фиг. 8). При этом D-триггер 13 по переднему фронту сигнала ВЫВОД устанавливается в состояние О и запрещает прохождение сигналов ошибок че- 30 рез элементы И 38 и 36 на выходы 43 и 44 сбоя устройства соответственно. На время действия сигнала ВЫВОД работа элементов И 33, 35 и 37 блокируется сигналом О с второго разря- 35 да информационных входов 39 устройства, поэтому состояние регистра 18 адреса и блока 7 не меняется. Для включения контроля необходимо выполнить команды 54 и 55 с признаком 40 контроля во втором разряде константы С, равным 1. Выполнение команд 54 и 55 не нарушает работоспособности устройства и ЭВМ, поэтому их можно выполнять в любом месте фрагментов 45 программы.

Блок 7 (фиг. 2) работает следующим образом.

Счетчик 45 адреса в исходном состоянии находится в нулевом состоянии. 50 При поступлении на управляющий вход занесения блока 7 сигнала производится добавление единицы в счетчик 45 адреса и разрешение занесения информации с информационных входов че- 55 рез группу 47 элементов И и группу 48 элементов ИЛИ в регистр 49. Сигналом с выхода элемента 50 задержки, поступающим на вход записи накопителя, производится запись в него информации, присутствующей на информационных входах. Сигнал с выхода элемента 50, поступая через элемент ИЛИ 52 на управляющий вход регистра 49, записывает также указанную информацию в регистр 49. При поступлении на управляющий вход выборки блока 7 сигнала производится вычитание единицы со счетчика 45 адреса, этим же сигналом, задержанным элементом 51 задержки, производится операция чтения информации с накопителя 46. Зад- ним фронтом сигнала, поступающего На управляющий вход выборки, через элемент ИЛИ 52 производится занесение считанной с накопителя 46 информации через группу 48 элементов ИЛИ в регистр 49. I

Устройство для контроля хода программ позволяет контролировать последовательность прохождения команд и фрагментов программы, выполняемой ЭВМ, с учетом прерываний, с помощью контроля состояний счетчика команд ЭВМ и таблицы разрешенной очередности фрагментов, что обеспечивает надежность и эффективный контроль работоспособности ЭВМ.

Формула изобретения

второй и третий триггеры, тринадцать элементов И, причем информационный вход устройства соединен с входом второго дешифратора, с информационным входом второго регистра адреса, выходы которого соединены с первыми входами первого и второго блоков сравнения и с первыми входами элементов И первой группы, информационный вход устройства соединен с первыми входами элементов И второй группы, выход второго элемента ИЛИ - с входом чтения блока стековой памяти,

выход которого соединен с вторым вхо- $ онным входом первого триггера, вы- дом второго блока сравнения, входы ход которого соединен с вторым входом

ввода и вывода устройства соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход которого соединен с первыми входами второго, третьего, четвертого и пятого элементов И, вход синхронизации устройства соединен с тактовыми входами первого и второго триггеров, с первыми входами шестого и седьмого элементов И, с входом записи второго регистра адреса, выход равенства второго блока сравнения соединен с первыми входами восьмого и девятого элементов И и с вторыми входами элементов венства первого блока сравнения

И первой группы, выходы которых соединены с первой группой входов группы элементов ИЛИ, выход девятого элемента И соединен с первым входом второго элемента ИЛИ, выход восьмого элемента И - с первым входом третьего элемента ИЛИ и с входом вычитания счетчика прерываний, выход второго дешифратора соединен с информационным входом второго триггера, выход которого соединен с вторыми входами первого и второго элементов И, с первым входом десятого элемента И, выход которого соединен с первым входом записи первого регистра адреса, выходы счетчика прерываний соединены с входами одиннадцатого элемента И, выход которого соединен с вторым входом десятого и первым входом двенадцатого элементов И, выход которого соединен с вторым входом записи первого регистра адреса, выход которого соединен с вторым информационным входом первого регистра адреса, выход элемента задержки соединен с вторым входом двенадцатого элемента И и с входом обращения блока памяти, выход которого соединен с первым входом тринадцатого элемента И, выход первого элемента ИЛИ соединен с первым входом четырнадцатого, с третьим входом десятого, с вторыми входами вось- мого и девятого элементов И, выход второго элемента И - с тактовым входом третьего триггера, выход которого соединен с первым входом пятнадцатого и вторым входом тринадцатого элементов И, выходы которых являются соответственно первым и вторым выходами сбоя устройства, выход первого дешифратора соединен с вторым входом седьмого элемента И и информациПятого элемента И и вторыми входами элементов И второй группы, выходы которых соединены с второй группой входов группы элементов ИЛИ, выходы которых соединены с информационными входами счетчика адреса, выход пятого элемента И соединен с вторым входом третьего элемента ИЛИ, выход которого соединен с входом записи счетчика адреса, информационный выход которого соединен с вторым входом первого блока сравнения и информационным входом блока стековой памяти, выход ра5

соединен с вторыми входами третьего и четвертого элементов И, выходы которых соединены соответственно с первым входом четвертого элемента ИЛИ и с входом установки нуля счетчика ошибок, выход генератора импульсов соединен с вторым входом четвертого элемента ИЛИ, выход которого соединен со счетным входом счетчика

0 ошибок, информационные выходы которого соединены с входами шестого элемента И, Выход которого соединен со счетным входом счетчика адреса, выход переполнения счетчика ошибок соеди5 вторым входом пятнадцатого элемента И, выход седьмого элемента И соединен с входом занесения блока стековой памяти, выход второго триггера - с третьим входом двенадцатого

0 и вторым входом четырнадцатого элементов И, выход четырнадцатого элемента И - с вторым входом второго элемента ИЛИ, вход первого разряда ин- . формационного входа устройства соеди5 нен с третьими входами первого и четырнадцатого элементов И,.вход второго разряда информационных входов устройства - с четвертыми входами двенадцатого, десятого и четырнадцатого элементов И и с информационным входом третьего триггера.

от 3

огр 50 от Ј/

соединены соответственно с выходами элементов И группы и с информационными входами регистра, вход записи которого соединен с выходом элемента ИЛИ, выход первого элемента задержки соединен с первым входом элемента ИЛИ, вход суммирования счетчика адреса - с входом первого элемента задержки и с вторыми входами элементов И группы, а вход вычитания счетчика адреса - с входом второго элемента здержки и с вторым входом элемента ИЛИ, входы первого и второго элементов адержки, информационные входы блока памяти и выходы регистра являются соответственно входом занесения блока, входом чтения блока, информационными входами и выходами блока.

Фиг. 3

ъ о

о

з- S ч

ъ

к

U1

oo

Г-сг

го u-i

1г

4

L г

.

1539785

Таблица 66

Фиги

Фрагмент 61

Фиг.1

Фрагпвнт 63

Фрагпент 6

Фиг.8

ионные S3

Выбод 10

17

Выборка аз i а стека 7

Ьопись 618, Ј 1-ft половина К

Запись $ 18, 8

г Чтение 19

IP IP

Фиг.9

Л

Фиг. Ю

| Устройство для контроля хода программы | 1983 |

|

SU1236487A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля следования модулей программы | 1985 |

|

SU1249521A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-01-30—Публикация

1988-01-20—Подача