Изобретение относится к вычислительной технике и может быть использовано для вычисления логических функций в отказоустойчивых вычислительных системах.

Известно программируемое логическое устройство, содержащее матрицу реализации конъюнкций, матрицу реализации дизъюнкций, блок программируемых инверторов (С. И. Баранов, В.А.Скляров, Цифровые устройства на программируемых БИС с матричной структурой, М.: Радио и связь, 1986, с. 43). Недостатком такого устройства является низкое быстродействие в режиме перепрограммирования.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее g n-входовых элементов И (n - количество информационных входов устройства, 2≤g≤2n), t элементов ИЛИ ( t - количество информационных выходов устройства), первую, вторую и третью группы D-триггеров, первую группу элементов И с тремя состояниями выхода, группу элементов И-НЕ с тремя состояниями выхода, g•t двухвходовых элементов И, счетчик и дешифратор, первый, второй и третий RS-триггеры, дополнительный элемент ИЛИ и вторую группу элементов И с тремя состояниями выхода, причем D-входы [i+(k-1)•n]-x D-триггеров первой и второй групп, первые входы соответствующих элементов И с тремя состояниями выхода первой группы и первые входы элементов И-НЕ с тремя состояниями выхода (1≤i≤n; 1≤k≤g) являются i-м информационным входом устройства, выходы D-триггеров первой группы соединены с вторыми входами соответствующих элементов И с тремя состояниями выхода первой группы, а выходы D-триггеров второй группы - с вторыми входами соответствующих элементов И-НЕ с тремя состояниями выхода, выходы которых соединены с выходами соответствующих элементов И с тремя состояниями выхода первой группы, C-входы [(k-1)n+i] -x D-триггеров первой группы соединены с k-м нечетным выходом дешифратора, а C-входы одноименных D-триггеров второй группы с k-м четным выходом дешифратора, выходы [(k-1)n+i]-x элементов И с тремя состояниями выхода первой группы соединены с входами k-го n-входового элемента И, выход которого соединен с первыми входами [k+(j-1)g]-x двухвходовых элементов И (1≤j≤t), вторые входы которых соединены с выходами соответствующих D-триггеров третьей группы, а выходы - с k-м входом j-х элементов ИЛИ, информационные выходы счетчика соединены с входами дешифратора, а счетный вход счетчика является тактовым входом устройства, первые входы второй группы элементов И с тремя состояниями выхода соединены с выходами соответствующих элементов ИЛИ, а вторые входы - с инверсным выходом третьего RS-триггера, S-вход которого соединен с нулевым выходом дешифратора, а R-вход - с выходом дополнительного элемента ИЛИ, выход j-го элемента И с тремя состояниями выхода второй группы соединен с D-входами [k+(j-1)g]-x D-триггеров третьей группы и является соответствующим информационным выходом устройства, p-й выход дешифратора (1≤p≤g) соединен с C-входами [(p-1)t+j]-x D-триггеров третьей группы, S-входы первого и второго RS-триггеров соединены соответственно с g-м выходом дешифратора и с выходом переполнения счетчика, выход первого RS-триггера является выходом индикации программирования элементов ИЛИ устройства, выход второго RS-триггера соединен с первым входом дополнительного элемента ИЛИ и является выходом индикации программирования элементов И устройства, R-входы D- и RS-триггеров и второй вход дополнительного элемента ИЛИ являются входом сброса устройства (Авт. св. СССР N 1444892, кл. G 11 C 17/00, G 06 F 7/00, 1988 г.).

Недостатком известного устройства является низкое быстродействие вычисления логических функций при наличии отказов.

Технические средства прототипа ориентированы на вычисление логических функций в условиях отсутствия отказов без какой-либо перестройки (реконфигурации) схемы. При отказе технических средств реализации одной из функций, что выясняется путем тестирования с помощью внешних технических средств, может быть реализовано вычисление этой функции на оставшихся технических средствах с предварительным перепрограммированием всего устройства и запоминанием результата во внешних по отношению к устройству-прототипу технических средствах. Однако это существенно снижает быстродействие. Кроме того, при наличии одного отказа, приводящего к невозможности вычислении по каждой из функций, устройство-прототип неспособно вычислить логические функции даже с перепрограммированием.

Все это снижает быстродействие устройства в задачах обеспечения работоспособности при наличии отказов.

Целью изобретения является повышение быстродействия при вычислении логических функций в условиях возникновения отказов.

Поставленная цель достигается тем, что программируемое логическое устройство, содержащее первую, вторую и третью группы D-триггеров количеством по m•2n (n - число входных переменных, m - число выходных функций), третью группу D-триггеров количеством 2(n-1)m, группу m(n-1) элементов И, счетчик, группу m•2n элементов И с тремя состояниями на выходе, дешифратор, группу m(n-1) элементов ИЛИ, причем входом сброса D-триггеров первой, второй и третьей групп, счетчика является вход сброса устройства, счетный вход счетчика является входом программирования устройства, а информационные выходы счетчика подключены к информационным входам дешифратора, неинверсные выходы D-триггеров второй группы подключены к управляющим входам соответствующих элементов И с тремя состояниями на выходе группы m•2n элементов И с тремя состояниями на выходе, неинверсные выходы D-триггеров третьей группы подключены ко вторым входам соответствующих элементов И группы m•2n элементов И, согласно изобретению введены вторая группа m•2n элементов И с тремя состояниями на выходе и m блоков вычисления функций, причем управляющий входы элементов второй группы m•2n элементов И с тремя состояниями на выходе подключены к инверсным выходам соответствующих D-триггеров второй группы D-триггеров, а информационные входы элементов второй группы m•2n элементов И с тремя состояниями на выходе являются соответствующими входами расширения соответствующей группы из m групп входов расширения, выходы элементов И с тремя состояниями на выходе объединены и подключены ко входам настройки соответствующего из m блоков вычисления функций, первый выход дешифратора подключен ко входам синхронизации D-триггеров первой группы, второй выход дешифратора подключен ко входам синхронизации D-триггеров второй группы, третий выход дешифратора подключен ко входам синхронизации D-триггеров третьей группы, четвертый выход дешифратора является выходом окончания программирования устройства, информационные входы D-триггеров первой и второй группы являются соответствующими входами расширения соответствующей из m групп входов расширения, информационные входы D-триггеров третьей группы являются 2(n-1) входами расширения соответствующей из m групп входов расширения, первые входы элементов И группы m(n-1) элементов И являются соответствующими из n-1 неинверсных входов группы 2n•m входов парафазных входных переменных (по 2m разрядов на каждый блок вычисления функций), первые входы элементов ИЛИ группы m(m-1) элементов ИЛИ являются соответствующими из n-1 инверсных входов группы 2n•m входов парафазных входных переменных (по 2m разрядов на каждый из m блоков вычисления функций), выходы элементов И группы m(n-1) элементов И подключены к соответствующим i-м инверсным входам парафазных входных переменных соответствующего из m блоков вычисления функций  , а старший неинверсный разряд этих входов является соответствующим n-м неинверсным входом группы 2n•m входов парафазных входных переменных, выходы элементов ИЛИ группы m(n-1) элементов ИЛИ подключены к соответствующим i-м инверсным входам парафазных входных переменных соответствующего из m блоков вычисления функций

, а старший неинверсный разряд этих входов является соответствующим n-м неинверсным входом группы 2n•m входов парафазных входных переменных, выходы элементов ИЛИ группы m(n-1) элементов ИЛИ подключены к соответствующим i-м инверсным входам парафазных входных переменных соответствующего из m блоков вычисления функций  , а старший инверсный разряд этих входов является соответствующим n-м инверсным входам группы 2n•m входов парафазных входных переменных, входы сброса блоков вычисления функций являются входом сброса устройства, входы синхронизации блоков вычисления функций являются входом синхронизации устройства, дополнительные входы сброса блоков вычисления функций являются группой m входов дополнительного сброса устройства, входы реконфигурации m блоков вычисления функций являются группой m входов реконфигурации блоков вычисления функций при отказах, входы типа реконфигурации m блоков вычисления функции при отказах являются группой m входов типа реконфигурации блоков вычисления функций при отказах, выходы неинверсного значения функции блоков вычисления функций являются соответствующими разрядами группы m выходов значений функции устройства, выходы инверсного значения функции блоков вычисления функций являются соответствующими разрядами группы m выходов инверсных значений функций устройства, выходы готовности результатов вычислений блоков вычисления функций являются группой m выходов готовности результатов вычисления функций устройства, каждый блок вычисления функций содержит группу 4•2n элементов И с тремя состояниями на выходе, два D-триггера, T-триггер, RS-триггер фиксации импульса, пять элементов ИЛИ, три элемента И, четыре инвертора, n групп элементов 2•2 НЕ-И-ИЛИ (в каждую i-ю группу входит 2n-1 элементов,

, а старший инверсный разряд этих входов является соответствующим n-м инверсным входам группы 2n•m входов парафазных входных переменных, входы сброса блоков вычисления функций являются входом сброса устройства, входы синхронизации блоков вычисления функций являются входом синхронизации устройства, дополнительные входы сброса блоков вычисления функций являются группой m входов дополнительного сброса устройства, входы реконфигурации m блоков вычисления функций являются группой m входов реконфигурации блоков вычисления функций при отказах, входы типа реконфигурации m блоков вычисления функции при отказах являются группой m входов типа реконфигурации блоков вычисления функций при отказах, выходы неинверсного значения функции блоков вычисления функций являются соответствующими разрядами группы m выходов значений функции устройства, выходы инверсного значения функции блоков вычисления функций являются соответствующими разрядами группы m выходов инверсных значений функций устройства, выходы готовности результатов вычислений блоков вычисления функций являются группой m выходов готовности результатов вычисления функций устройства, каждый блок вычисления функций содержит группу 4•2n элементов И с тремя состояниями на выходе, два D-триггера, T-триггер, RS-триггер фиксации импульса, пять элементов ИЛИ, три элемента И, четыре инвертора, n групп элементов 2•2 НЕ-И-ИЛИ (в каждую i-ю группу входит 2n-1 элементов,  ), элемент задержки, дополнительную группу элементов И с тремя состояниями на выходе, причем входы управления нечетных элементов И с тремя состояниями на выходе из группы 4•2n элементов И с тремя состояниями на выходе подключены к неинверсному выходу T-триггера, инверсный выход которого подключен ко входам управления четырех элементов И с тремя состояниями на выходе из группы 4•2n элементов И с тремя состояниями на выходе, информационные выходы которых являются соответствующими разрядами входов настройки блока, информационные входы нечетных элементов И с тремя состояниями на выходе из первой половины группы 4•2n элементов И с тремя состояниями на выходе подключены к соответствующим j-м элементам второй половины входов настройки,

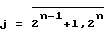

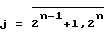

), элемент задержки, дополнительную группу элементов И с тремя состояниями на выходе, причем входы управления нечетных элементов И с тремя состояниями на выходе из группы 4•2n элементов И с тремя состояниями на выходе подключены к неинверсному выходу T-триггера, инверсный выход которого подключен ко входам управления четырех элементов И с тремя состояниями на выходе из группы 4•2n элементов И с тремя состояниями на выходе, информационные выходы которых являются соответствующими разрядами входов настройки блока, информационные входы нечетных элементов И с тремя состояниями на выходе из первой половины группы 4•2n элементов И с тремя состояниями на выходе подключены к соответствующим j-м элементам второй половины входов настройки,  , информационные входы нечетных элементов И с тремя состояниями на выходе из второй половины 4•2n элементов И с тремя состояниями на выходе подключены к соответствующим M разрядам первой половины входов настройки,

, информационные входы нечетных элементов И с тремя состояниями на выходе из второй половины 4•2n элементов И с тремя состояниями на выходе подключены к соответствующим M разрядам первой половины входов настройки,  , выходы нечетных элементов И с тремя состояниями на выходе группы 4•2n элементов И с тремя состояниями на выходе объединены с выходами соответствующих четных элементов И с тремя состояниями на выходе и подключены к соответствующим нечетным входам соответствующего элемента 2•2 НЕ-И-ИЛИ первой группы из n групп элементов 2•2 НЕ-И-ИЛИ (по две пары нечетный - четный элемент И с тремя состояниями выхода на каждый элемент 2•2 НЕ-И-ИЛИ, четные входы элементов 2•2 НЕ-И-ИЛИ каждой S-й группы,

, выходы нечетных элементов И с тремя состояниями на выходе группы 4•2n элементов И с тремя состояниями на выходе объединены с выходами соответствующих четных элементов И с тремя состояниями на выходе и подключены к соответствующим нечетным входам соответствующего элемента 2•2 НЕ-И-ИЛИ первой группы из n групп элементов 2•2 НЕ-И-ИЛИ (по две пары нечетный - четный элемент И с тремя состояниями выхода на каждый элемент 2•2 НЕ-И-ИЛИ, четные входы элементов 2•2 НЕ-И-ИЛИ каждой S-й группы,  , элементов 2•2 НЕ-И-ИЛИ являются соответствующими разрядами входов парафазных входных переменных блока (второй вход каждого элемента 2•2 НЕ-И-ИЛИ S-й группы является входом XS, четвертый -

, элементов 2•2 НЕ-И-ИЛИ являются соответствующими разрядами входов парафазных входных переменных блока (второй вход каждого элемента 2•2 НЕ-И-ИЛИ S-й группы является входом XS, четвертый -  ), выходы элементов 2•2 НЕ-И-ИЛИ S-й группы,

), выходы элементов 2•2 НЕ-И-ИЛИ S-й группы,  , где n - число входных переменных, подключены к соответствующим нечетным входам элементов 2•2 НЕ-И-ИЛИ S+1 группы, причем к каждому элементу 2•2 НЕ-И-ИЛИ в группы

, где n - число входных переменных, подключены к соответствующим нечетным входам элементов 2•2 НЕ-И-ИЛИ S+1 группы, причем к каждому элементу 2•2 НЕ-И-ИЛИ в группы  подключены выходы двух элементов i-1 групп, выход единственного элемента 2•2 НЕ-И-ИЛИ последней n-й группы из n групп элементов 2•2 НЕ-И-ИЛИ подключен к информационному входу первого D-триггера, второй вход этого элемента подключен к выходу первого элемента ИЛИ, а четвертый вход этого элемента 2•2 НЕ-И-ИЛИ n-й группы подключен к выходу второго элемента ИЛИ, первые входы первого и второго элементов ИЛИ подключены к выходам первого и второго элементов И соответственно, второй вход первого элемента ИЛИ подключен к объединенным выходами первого и второго элементов И с тремя состояниями на выходе дополнительной группы элементов И с тремя состояниями при выходе, второй вход второго элемента ИЛИ подключен к объединенным выходам третьего и четвертого элементов И с тремя состояниями на выходе дополнительной группы элементов И с тремя состояниями на выходе, вторые входы первого и второго элементов И, входы второго и четвертого инвертора являются видом реконфигурации блока при отказах, первый вход первого элемента И и вход первого инвертора являются входом типа реконфигурации блока при отказах, выход первого инвертора подключен к первому входу второго элемента И, вход обнуления первого D-триггера и первый вход четвертого элемента ИЛИ являются входом сброса блока, входы синхронизации первого и второго D-триггеров, счетный вход T-триггера, вход элемента задержки являются входом синхронизации блока, выход второго инвертора подключен ко второму входу четвертого элемента ИЛИ, третий вход которого является входом дополнительного сброса блока, выход четвертого элемента ИЛИ подключен ко входам обнуления второго D-триггера, RS-триггера фиксации импульса и T-триггера, выход первого D-триггера подключен к информационному входу второго D-триггера и первому входу третьего элемента ИЛИ, второй вход которого подключен к выходу второго D-триггера, выход третьего элемента ИЛИ является выходом значения функции блока и подключен ко входу третьего инвертора и первому входу пятого элемента ИЛИ, выход третьего инвертора является выходом инверсного значения функции блока, выход четвертого инвертора подключен ко второму входу пятого элемента ИЛИ, третий вход которого подключен ко входу третьего элемента И, выход пятого элемента ИЛИ является выходом готовности результатов вычисления функций блока, первый вход третьего элемента И подключен к выходу RS-триггера функции импульса, а второй вход третьего элемента И подключен к инверсному выходу T-триггера, который также подключен ко входам управления нечетных элементов И с тремя состояниями на выходе дополнительной группы элементов с тремя состояниями на выходе, ко входам управления четных элементов которой подключен неинверсный выход T-триггера, информационные входы первого и четвертого элементов И с тремя состояниями на выходе являются n-м инверсным входом xn парафазных входных переменных блока, а информационные входы второго и третьего элементов И с тремя состояниями на выходе дополнительной группы элементов И с тремя состояниями на выходе являются n-м инверсным входом

подключены выходы двух элементов i-1 групп, выход единственного элемента 2•2 НЕ-И-ИЛИ последней n-й группы из n групп элементов 2•2 НЕ-И-ИЛИ подключен к информационному входу первого D-триггера, второй вход этого элемента подключен к выходу первого элемента ИЛИ, а четвертый вход этого элемента 2•2 НЕ-И-ИЛИ n-й группы подключен к выходу второго элемента ИЛИ, первые входы первого и второго элементов ИЛИ подключены к выходам первого и второго элементов И соответственно, второй вход первого элемента ИЛИ подключен к объединенным выходами первого и второго элементов И с тремя состояниями на выходе дополнительной группы элементов И с тремя состояниями при выходе, второй вход второго элемента ИЛИ подключен к объединенным выходам третьего и четвертого элементов И с тремя состояниями на выходе дополнительной группы элементов И с тремя состояниями на выходе, вторые входы первого и второго элементов И, входы второго и четвертого инвертора являются видом реконфигурации блока при отказах, первый вход первого элемента И и вход первого инвертора являются входом типа реконфигурации блока при отказах, выход первого инвертора подключен к первому входу второго элемента И, вход обнуления первого D-триггера и первый вход четвертого элемента ИЛИ являются входом сброса блока, входы синхронизации первого и второго D-триггеров, счетный вход T-триггера, вход элемента задержки являются входом синхронизации блока, выход второго инвертора подключен ко второму входу четвертого элемента ИЛИ, третий вход которого является входом дополнительного сброса блока, выход четвертого элемента ИЛИ подключен ко входам обнуления второго D-триггера, RS-триггера фиксации импульса и T-триггера, выход первого D-триггера подключен к информационному входу второго D-триггера и первому входу третьего элемента ИЛИ, второй вход которого подключен к выходу второго D-триггера, выход третьего элемента ИЛИ является выходом значения функции блока и подключен ко входу третьего инвертора и первому входу пятого элемента ИЛИ, выход третьего инвертора является выходом инверсного значения функции блока, выход четвертого инвертора подключен ко второму входу пятого элемента ИЛИ, третий вход которого подключен ко входу третьего элемента И, выход пятого элемента ИЛИ является выходом готовности результатов вычисления функций блока, первый вход третьего элемента И подключен к выходу RS-триггера функции импульса, а второй вход третьего элемента И подключен к инверсному выходу T-триггера, который также подключен ко входам управления нечетных элементов И с тремя состояниями на выходе дополнительной группы элементов с тремя состояниями на выходе, ко входам управления четных элементов которой подключен неинверсный выход T-триггера, информационные входы первого и четвертого элементов И с тремя состояниями на выходе являются n-м инверсным входом xn парафазных входных переменных блока, а информационные входы второго и третьего элементов И с тремя состояниями на выходе дополнительной группы элементов И с тремя состояниями на выходе являются n-м инверсным входом  парафазных входных переменных блока.

парафазных входных переменных блока.

Сущность изобретения заключается в повышении быстродействия при вычислении логических функций в условиях возникновения отказов путем введения дисциплины вычисления логических функций за два такта по двум подфункциям с дизъюнкцией промежуточных результатов.

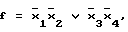

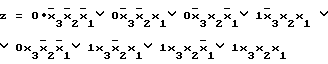

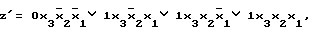

Суть новой введенной дисциплины заключается в следующем:

а) в отключении половины логических элементов, вычисляющих логическую функцию в соответствие с парафазными входными сигналами и кодами настройки;

б) в вычислении первой подфункции логической функции на половине логических элементов с использованием половины кодов настройки с запоминанием результата;

в) в вычислении второй подфункции логической функции на этой же половине логических элементов с использованием второй половины кодов настройки с заменой старшей переменной на ее инверсию и запоминанием результата;

г) в дизъюнкции результатов вычисления подфункций;

д) в использовании для вычисления логических функций элементов 2•2 НЕ-И-ИЛИ, сохраняющих функциональную полноту при однократных константных отказах входов (так называемых функционально-полных толерантных элементов, реализующих функцию С.Тюрина).

Сущность изобретения реализуется за счет введения следующей совокупности конструктивных признаков - новых элементов и связей, соответствующих критерию "новизна".

Введение блоков вычисления функции с предлагаемой структурой и соответствующим им связей позволяет вычислять логические функции как в случае отсутствия отказов, так и в случае наличия отказов, реализуя дисциплину вычисления логических функций за два такта по двум подфункциям с дизъюнкцией промежуточных результатов.

Введение новых связей для группы m(n-1) элементов И, группы m(n-1) элементов ИЛИ позволяет подключать ко входам парафазных входных переменных блоков вычисления функций существенные переменные с группы 2n•m входов парафазных входных переменных устройства как в случае вычисления логических функций при отсутствии отказов, так и при их наличии во время реализации новой введенной дисциплины.

Введение второй группы m•2n элементов ИЛИ с тремя состояниями на выходе и соответствующей ей связей, а также новых связей для первой группы m•2n элементов И с тремя состояниями на выходе позволяет подключать ко входам настройки блоков вычисления функций как настроечную информацию с выходов первой группы D-триггеров, так и внешние входы m групп входов расширения в целях расширения разрядности в процессе вычислений при отсутствии отказов, а также в процессе реализации новой введенной дисциплины.

Введение новых связей для D-триггеров первой группы позволяет обеспечить настройку блоков вычисления функций для реализации в них вычислений как в процессе вычислений при отсутствии отказов, так и в процессе реализации новой введенной дисциплины.

Введение новых связей для D-триггеров второй группы позволяет обеспечить подключение ко входам настройки блоков вычисления функций разрядов m групп входов расширения для обеспечения расширения разрядности в процессе вычислений при отсутствии отказов, а также в процессе реализации новой введенной дисциплины.

Введение новых связей для D-триггеров второй группы позволяет обеспечить их программирование для последующего участия их в реализации вычислений при отсутствии отказов, так и в процессе реализации новой введенной дисциплины.

Введение новых связей для дешифратора позволяет обеспечить программирование D-триггеров первой, второй и третьей групп для последующего участия их в реализации вычислений логических функций при отсутствии отказов, так и в процессе реализации новой введенной дисциплины.

Таким образом, предлагаемое техническое решение соответствует критерию "существенные отличия", поскольку в известных устройствах - аналоге и прототипе не достигается свойство повышения быстродействия при вычислении логических функций в условиях возникновения отказов вследствие отсутствия указанной совокупности конструктивных признаков.

При использовании предлагаемого программируемого логического устройства может быть получен положительный эффект повышения быстродействия при вычислении логических функций в условиях возникновения отказов. Количественный расчет приведен в разделе технико-экономического обоснования.

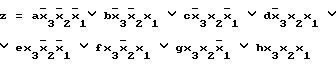

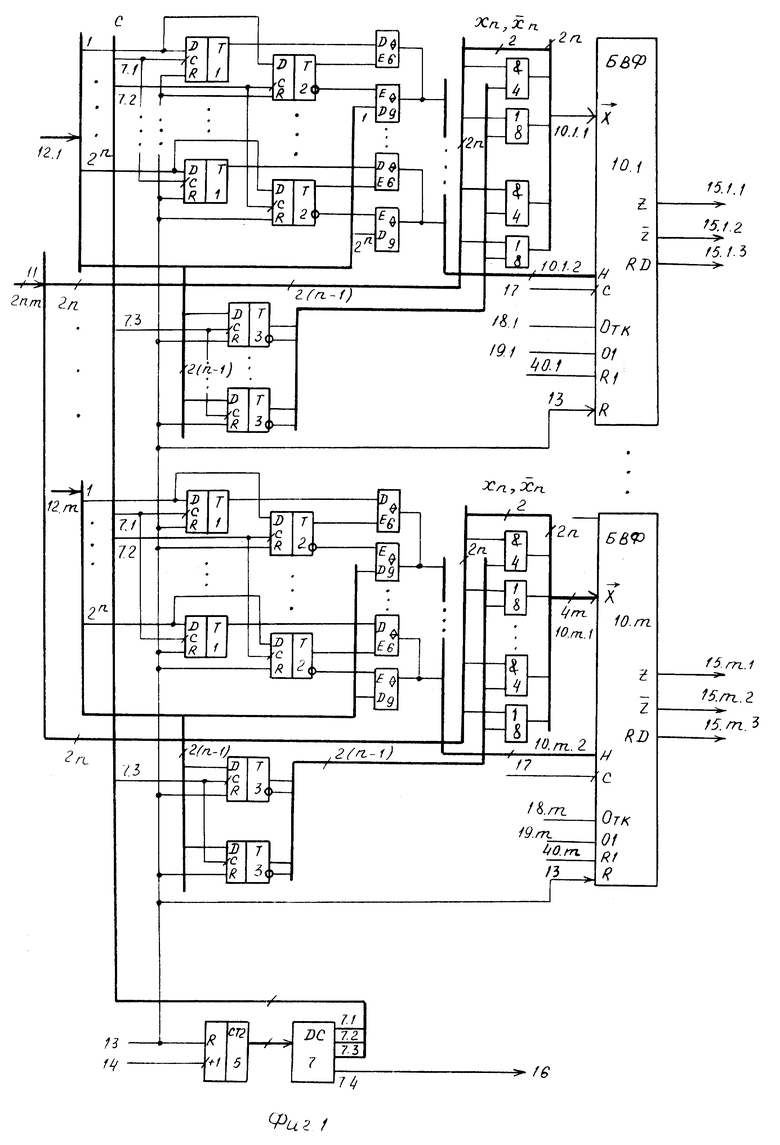

На фиг. 1 изображена функциональная электрическая схема предлагаемого программируемого логического устройства.

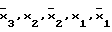

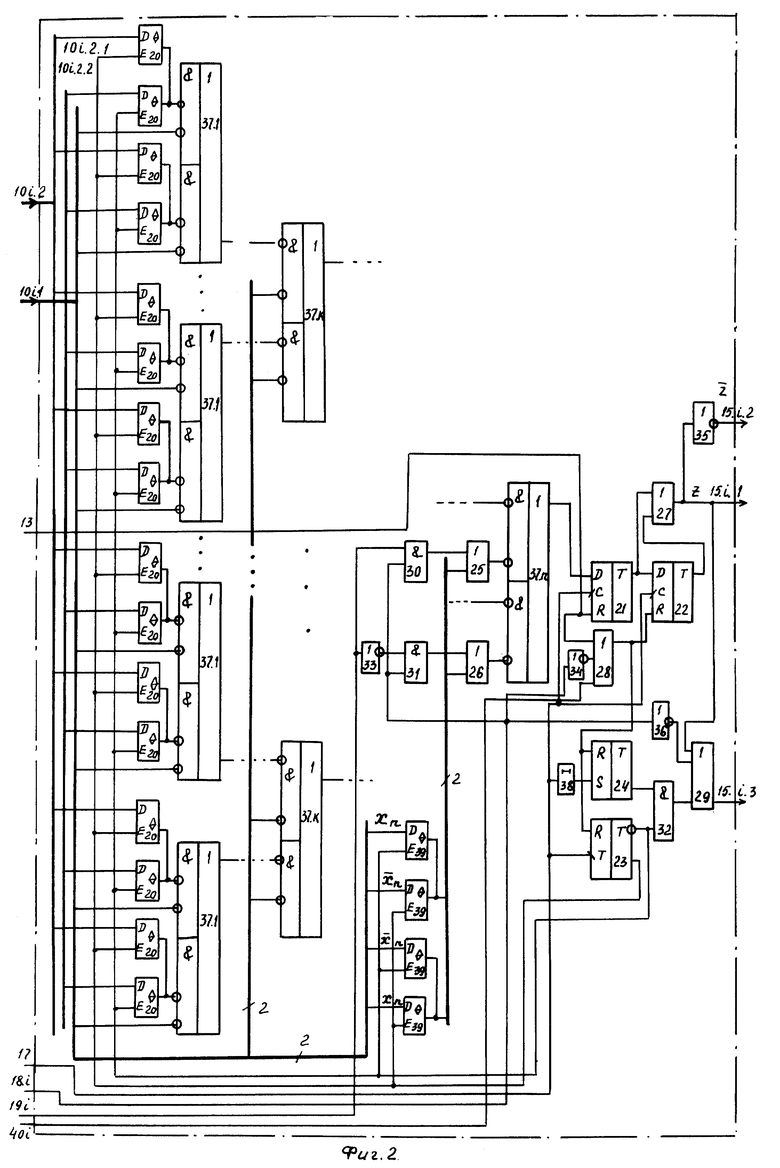

На фиг. 2 изображена функциональная электрическая схема i-го блока вычисления функций.

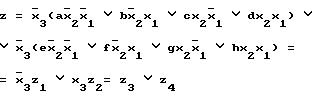

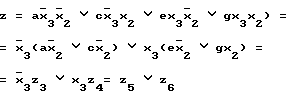

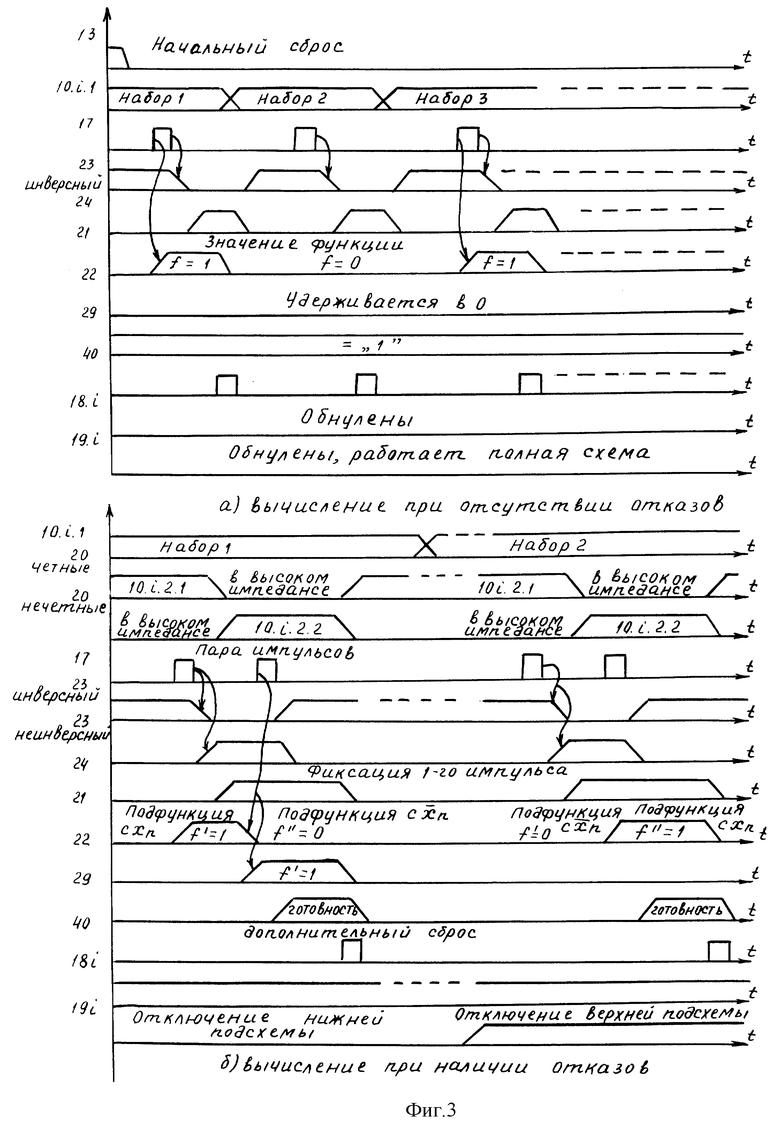

На фиг. 3 изображена временная диаграмма работы блока вычисления функций: а) в режиме вычисления при отсутствии отказов и б) в режиме вычисления при наличии отказов.

Программируемое логическое устройство содержит первую 1, вторую 2 и третью 3 группы D-триггеров, в первой и во второй группах m•2n D-триггеров, где n - число входных переменных, m - число выходных функций, в третьей группе 2(n-1)•m D-триггеров, группу m•(n-1) элементов И 4, счетчик 5, первую группу m•2n элементов И с тремя состояниями на выходе, дешифратор 7, группу m(n-1) элементов ИЛИ 8, вторую группу m•2n элементов И 9 с тремя состояниями на выходе, m блоков вычисления функций 10.1-10m, группу 2m•m входов парафазных входных переменных 11 по 2m разрядов на каждый из блоков 10.1-10.m, m групп входов расширения 12.1-12m, каждая из которых содержит 2n разрядов, вход сброса 13, вход программирования 14, группу m выходов значений функций 15, 1.1-15. m.1, группу m выходов инверсных значений функций 15.1.2-15.m.2, группу m выходов готовности результатов вычисления функций 15.1.3-15.m.3, выход окончания программирования 16, вход синхронизации 17, группу m входов реконфигурации блоков вычисления функций при отказах 18.1-18.m, группу m входов типа реконфигурации блоков вычисления функций при отказах 19.1-19.m.

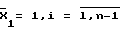

Каждый блок вычисления функций 10.1-10.m содержит группу 4•2n элементов И с тремя состояниями на выходе 20, первый 21 и второй 22 D-триггеры, T-триггер 23, RS-триггер фиксации импульса 24, первый 25, второй 26, третий 27, четвертый 28 и пятый 29 элементы ИЛИ, первый 30, второй 31 и третий 32 элемента И, первый 33, второй 34, третий 35 и четвертый 36 инверторы, n групп 37.1-37.n элементов 2•2 НЕ-И-ИЛИ, в каждую группу входит 2n-i элементов, где i - номер группы  ; элемент задержки 38, дополнительную группу элементов И с тремя состояниями на выходе 39, группу дополнительных входов сброса 40.1...10.m.

; элемент задержки 38, дополнительную группу элементов И с тремя состояниями на выходе 39, группу дополнительных входов сброса 40.1...10.m.

Входы сброса D-триггеров первой 1, второй 2, третьей 3 групп, счетчика 5 являются входом сброса 13 устройства. Счетный вход счетчика 5 является входом программирования 14 устройства. Информационные выходы счетчика 5 подключены к информационным входам дешифратора 7. Неинверсные выходы D-триггеров второй группы 2 подключены к управляющим входам соответствующих элементов И с тремя состояниями на выходе группы m•2n элементов И с тремя состояниями на выходе 6.

Неинверсные выходы D-триггеров третьей группы 3 подключены ко вторым входам соответствующих элементов И группы m•2n элементов И 4.

Управляющие входы элементов второй группы m•2n элементов И с тремя состояниями на выходе 9 подключены к инверсным выходам соответствующих D-триггеров второй группы D-триггеров 2. Информационные входы элементов второй группы m•2n элементов И с тремя состояниями на выходе 9 являются соответствующими входами расширения соответствующей группы из m групп входов расширения 12.1...12.m. Выходы элементов И с тремя состояниями на выходе групп 6, 9 объединены и подключены ко входам настройки 10.1.2...10.m.2 соответствующего из m блоков вычисления функций 10.1...10.m.

Первый выход 7.1 дешифратора 7 подключен ко входам синхронизации D-триггеров первой группы 1. Второй выход 7.2 дешифратора 7 подключен ко входам синхронизации D-триггеров второй группы 2. Третий выход 7.3 дешифратора 7 подключен ко входам синхронизации D-триггеров третьей группы 3. Четвертый выход 7.4 дешифратора 7 является выходом окончания программирования 16 устройства. Информационные входы D-триггеров первой 1 и второй групп 2 являются соответствующими входами расширения соответствующей из m групп входов расширения 12.1...12.m. Информационные входы D-триггеров третьей группы 3 являются 2(n-1) входами расширения соответствующей из m групп входов расширения 12.1. . .12.m. Первые входы элементов И группы m(n-1) элементов И 4 являются соответствующими из n-1 неинверсных входов групп 2n•m входов парафазных входных переменных 11 (по 2m разрядов на каждый блок вычисления функций). Первые входы элементов ИЛИ группы m(n-1) элементов ИЛИ 8 являются соответствующими из n-1 инверсных входов групп 2n•m входов парафазных входных переменных 11 (по 2m разрядов на каждый блок из m блоков вычисления функций). Выходы элементов И группы m(n-1) элементов И 4 подключены к соответствующим i-м неинверсным входам парафазных входных переменных 10.j.1 соответствующего j-го из m блоков вычисления функций 10.i-10.m  , а старший неинверсный разряд этих входов является соответствующим n-м неинверсным входом группы 2n•m входов парафазных входных переменных 11. Выходы элементов ИЛИ группы m(n-1) элементов ИЛИ 8 подключены к соответствующим i-м инверсным входам парафазных входных переменных 10.j.1 соответствующего j-го из m блоков вычисления функций 10.1...10.m

, а старший неинверсный разряд этих входов является соответствующим n-м неинверсным входом группы 2n•m входов парафазных входных переменных 11. Выходы элементов ИЛИ группы m(n-1) элементов ИЛИ 8 подключены к соответствующим i-м инверсным входам парафазных входных переменных 10.j.1 соответствующего j-го из m блоков вычисления функций 10.1...10.m  , а старший инверсный разряд этих входов является соответствующим n-м инверсным входом группы 2n•m входов парафазных входных переменных 11. Входы сброса блоков вычисления функций 10.1. . .10.m являются входом сброса 13 устройства. Входы синхронизации блоков вычисления функций 10.1...10.m являются входом синхронизации 17 устройства. Дополнительные входы сброса блоков вычисления функций 10.1...10. m являются группой m входов дополнительного сброса 40.1...40.m устройства. Входы реконфигурации m блоков вычисления функций 10.1...10.m являются группой m входов реконфигурации 18.1...18.m блоков вычисления функций при отказах. Входы типа реконфигурации m блоков вычисления функций 10.1...10.m при отказах являются группой m входов типа реконфигурации блоков вычисления функций при отказах 19.1...19.m. Выходы неинверсного значения функции блоков вычисления функций 10.1...10.m являются соответствующими разрядами группы m выходов значений функции 15.1.1...15.m.1 устройства. Выходы инверсного значения функции блоков вычисления функций 10.1...10.m являются соответствующими разрядами группы m выходов инверсных значений функций 15.1.2...15.m.2 устройства. Выходы готовности результатов вычислений блоков вычисления функций 10.1. . . 10. m являются группой m выходов готовности результатов вычисления функций 15.1.3...15.m.3 устройства.

, а старший инверсный разряд этих входов является соответствующим n-м инверсным входом группы 2n•m входов парафазных входных переменных 11. Входы сброса блоков вычисления функций 10.1. . .10.m являются входом сброса 13 устройства. Входы синхронизации блоков вычисления функций 10.1...10.m являются входом синхронизации 17 устройства. Дополнительные входы сброса блоков вычисления функций 10.1...10. m являются группой m входов дополнительного сброса 40.1...40.m устройства. Входы реконфигурации m блоков вычисления функций 10.1...10.m являются группой m входов реконфигурации 18.1...18.m блоков вычисления функций при отказах. Входы типа реконфигурации m блоков вычисления функций 10.1...10.m при отказах являются группой m входов типа реконфигурации блоков вычисления функций при отказах 19.1...19.m. Выходы неинверсного значения функции блоков вычисления функций 10.1...10.m являются соответствующими разрядами группы m выходов значений функции 15.1.1...15.m.1 устройства. Выходы инверсного значения функции блоков вычисления функций 10.1...10.m являются соответствующими разрядами группы m выходов инверсных значений функций 15.1.2...15.m.2 устройства. Выходы готовности результатов вычислений блоков вычисления функций 10.1. . . 10. m являются группой m выходов готовности результатов вычисления функций 15.1.3...15.m.3 устройства.

Входы управления нечетных элементов И с тремя состояниями на выходе из группы 4•2n элементов И с тремя состояниями на выходе 20 подключены к неинверсному выходу T-триггера 23. Инверсный выход T-триггера 23 подключен ко входам управления четных элементов И с тремя состояниями на выходе из группы 4•2n элементов И с тремя состояниями на выходе 20, информационные входы которых являются соответствующими разрядами входов настройки блока 10.i.2, где i - номер блока. Информационные входы нечетных элементов И с тремя состояниями на выходе из первой половины группы 4•2n элементов И с тремя состояниями на выходе 20 подключены к соответствующим j-м разрядам второй половины входов настройки 10. i. j.2,  . Информационные входы нечетных элементов И с тремя состояниями на выходе из второй половины 4•2n элементов И с тремя состояниями на выходе 20 подключены к соответствующим M-м разрядам первой половины входов настройки 10. i.2.1,

. Информационные входы нечетных элементов И с тремя состояниями на выходе из второй половины 4•2n элементов И с тремя состояниями на выходе 20 подключены к соответствующим M-м разрядам первой половины входов настройки 10. i.2.1,  . Выходы нечетных элементов И с тремя состояниями на выходе группы 4•2n элементов И с тремя состояниями на выходе 20 объединены с выходами соответствующих четных элементов И с тремя состояниями на выходе и подключены к соответствующим нечетным входам соответствующего элемента 2•2 НЕ-И-ИЛИ первой группы 37.1 из n групп элементов 2•2 НЕ-И-ИЛИ 37.1...37.n (по две пары нечетный-четный элемент И с тремя состояниями на выходе на каждый элемент 2•2 НЕ-И-ИЛИ группы 37.1). Четные входы элементов 2•2 НЕ-И-ИЛИ каждой S-й 37.5 S группы

. Выходы нечетных элементов И с тремя состояниями на выходе группы 4•2n элементов И с тремя состояниями на выходе 20 объединены с выходами соответствующих четных элементов И с тремя состояниями на выходе и подключены к соответствующим нечетным входам соответствующего элемента 2•2 НЕ-И-ИЛИ первой группы 37.1 из n групп элементов 2•2 НЕ-И-ИЛИ 37.1...37.n (по две пары нечетный-четный элемент И с тремя состояниями на выходе на каждый элемент 2•2 НЕ-И-ИЛИ группы 37.1). Четные входы элементов 2•2 НЕ-И-ИЛИ каждой S-й 37.5 S группы  элементов 2•2 НЕ-И-ИЛИ 37 являются соответствующими разрядами входов парафазных входных переменных 10.i.1 блока, где i - номер блока (второй вход каждого элемента 2•2 НЕ-И-ИЛИ S-й группы является входом XS, четвертый

элементов 2•2 НЕ-И-ИЛИ 37 являются соответствующими разрядами входов парафазных входных переменных 10.i.1 блока, где i - номер блока (второй вход каждого элемента 2•2 НЕ-И-ИЛИ S-й группы является входом XS, четвертый  ).

).

Выходы элементов 2•2 НЕ-И-ИЛИ S-й группы,  , где n - число входных переменных, подключены к соответствующим нечетным входам элементов 2•2 НЕ-И-ИЛИ S+1 группы 37.5+1, причем к каждому элементу 2•2 НЕ-И-ИЛИ l группы

, где n - число входных переменных, подключены к соответствующим нечетным входам элементов 2•2 НЕ-И-ИЛИ S+1 группы 37.5+1, причем к каждому элементу 2•2 НЕ-И-ИЛИ l группы  подключены выходы двух элементов l-1 группы. Выход единственного элемента 2•2 НЕ-И-ИЛИ 37.n последней n-ой группы из n групп элементов 2•2 НЕ-И-ИЛИ 37.1...37.n подключен к информационному входу D-триггера 21. Второй вход этого элемента подключен к выходу первого элемента ИЛИ 25, а четвертый вход этого элемента 2•2 НЕ-И-ИЛИ n-й группы 37.n подключен к выходу второго элемента 26. Первые выходы первого 25 и второго 26 элементов ИЛИ подключены к выходам первого 30 и второго 31 элементов И соответственно. Второй вход первого элемента ИЛИ 25 подключен к объединенным выходам первого и второго элементов И с тремя состояниями на выходе дополнительной группы элементов И с тремя состояниями на выходе 39. Второй вход второго элемента ИЛИ 26 подключен к объединенным выходам третьего и четвертого элементов И с тремя состояниями на выходе дополнительной группы элементов И с тремя состояниями на выходе 39. Вторые выходы первого 30 и второго 31 элементов И, входы второго 34 и четвертого 36 инвертора являются входом реконфигурации 18.i блока при отказах, i - номер блока. Первый вход первого элемента И 30 и вход первого инвертора 33 являются входом типа реконфигурации 19.i блока при отказах. Выход первого инвертора 33 подключен к первому входу второго элемента И 31. Вход обнуления первого D-триггера 21 и первый вход четвертого элемента ИЛИ 28 являются входом сброса 13 блока. Входы синхронизации первого 21 и второго 22 D-триггеров, счетный вход T-триггера 23, вход элемента задержки 38 являются входом синхронизации 17 блока. Выход второго инвертора подключен ко второму входу четвертого элемента ИЛИ 28, третий вход которого является входом дополнительного сброса 40.i блока (i - номер блока). Выход четвертого элемента ИЛИ 28 подключен ко входам обнуления второго D-триггера 22, RS-триггера фиксации импульса 24 и T-триггера 23. Выход первого D-триггера 21 подключен к информационному входу второго D-триггера 22 и первому входу третьего элемента ИЛИ 27, второй вход которого подключен к выходу второго D-триггера 22. Выход третьего элемента ИЛИ 27 является выходом значения функции 15.i.1 блока и подключен ко входу третьего инвертора 35 и первому входу пятого элемента ИЛИ 29. Выход третьего инвертора 35 является выходом инверсного значения функции 15.i.2 блока. Выход четвертого инвертора 36 подключен ко второму входу пятого элемента ИЛИ 29, третий вход которого подключен к выходу третьего элемента И 32. Выход пятого элемента ИЛИ 29 является выходом готовности результатов вычисления функции 15.i.3. Ппервый вход третьего элемента И 32 подключен к выходу RS-триггера фиксации импульса 24, а второй вход третьего элемента И 32 подключен к инверсному выходу T-триггера 23, который также подключен ко входам управления нечетных элементов И с тремя состояниями на выходе дополнительной группы элементов с тремя состояниями на выходе 39, ко входам управления четных элементов которой подключен неинверсный выход T-триггера 23. Информационные входы первого и четвертого элементов И с тремя состояниями на выходе группы 39 являются n-м неинверсным входом Xn парафазных входных переменных 10.i.1 блока. Информационные входы второго и третьего элементов И с тремя состояниями на выходе дополнительной группы элементов И с тремя состояниями на выходе 39 являются n-м инверсным входом

подключены выходы двух элементов l-1 группы. Выход единственного элемента 2•2 НЕ-И-ИЛИ 37.n последней n-ой группы из n групп элементов 2•2 НЕ-И-ИЛИ 37.1...37.n подключен к информационному входу D-триггера 21. Второй вход этого элемента подключен к выходу первого элемента ИЛИ 25, а четвертый вход этого элемента 2•2 НЕ-И-ИЛИ n-й группы 37.n подключен к выходу второго элемента 26. Первые выходы первого 25 и второго 26 элементов ИЛИ подключены к выходам первого 30 и второго 31 элементов И соответственно. Второй вход первого элемента ИЛИ 25 подключен к объединенным выходам первого и второго элементов И с тремя состояниями на выходе дополнительной группы элементов И с тремя состояниями на выходе 39. Второй вход второго элемента ИЛИ 26 подключен к объединенным выходам третьего и четвертого элементов И с тремя состояниями на выходе дополнительной группы элементов И с тремя состояниями на выходе 39. Вторые выходы первого 30 и второго 31 элементов И, входы второго 34 и четвертого 36 инвертора являются входом реконфигурации 18.i блока при отказах, i - номер блока. Первый вход первого элемента И 30 и вход первого инвертора 33 являются входом типа реконфигурации 19.i блока при отказах. Выход первого инвертора 33 подключен к первому входу второго элемента И 31. Вход обнуления первого D-триггера 21 и первый вход четвертого элемента ИЛИ 28 являются входом сброса 13 блока. Входы синхронизации первого 21 и второго 22 D-триггеров, счетный вход T-триггера 23, вход элемента задержки 38 являются входом синхронизации 17 блока. Выход второго инвертора подключен ко второму входу четвертого элемента ИЛИ 28, третий вход которого является входом дополнительного сброса 40.i блока (i - номер блока). Выход четвертого элемента ИЛИ 28 подключен ко входам обнуления второго D-триггера 22, RS-триггера фиксации импульса 24 и T-триггера 23. Выход первого D-триггера 21 подключен к информационному входу второго D-триггера 22 и первому входу третьего элемента ИЛИ 27, второй вход которого подключен к выходу второго D-триггера 22. Выход третьего элемента ИЛИ 27 является выходом значения функции 15.i.1 блока и подключен ко входу третьего инвертора 35 и первому входу пятого элемента ИЛИ 29. Выход третьего инвертора 35 является выходом инверсного значения функции 15.i.2 блока. Выход четвертого инвертора 36 подключен ко второму входу пятого элемента ИЛИ 29, третий вход которого подключен к выходу третьего элемента И 32. Выход пятого элемента ИЛИ 29 является выходом готовности результатов вычисления функции 15.i.3. Ппервый вход третьего элемента И 32 подключен к выходу RS-триггера фиксации импульса 24, а второй вход третьего элемента И 32 подключен к инверсному выходу T-триггера 23, который также подключен ко входам управления нечетных элементов И с тремя состояниями на выходе дополнительной группы элементов с тремя состояниями на выходе 39, ко входам управления четных элементов которой подключен неинверсный выход T-триггера 23. Информационные входы первого и четвертого элементов И с тремя состояниями на выходе группы 39 являются n-м неинверсным входом Xn парафазных входных переменных 10.i.1 блока. Информационные входы второго и третьего элементов И с тремя состояниями на выходе дополнительной группы элементов И с тремя состояниями на выходе 39 являются n-м инверсным входом  парафазных входных переменных 10.i.1 блока.

парафазных входных переменных 10.i.1 блока.

Первая группа D-триггеров 1 (фиг. 1) предназначена для записи и хранения информации настройки соответствующих блоков вычисления функций устройства с соответствующих входов расширения m групп входов расширения 12.1-12.m по переднему фронту сигнала "1" на выходе 7.1 дешифратора 7. Количество D-триггеров равно m•2n, где n - число входных переменных, а m - число выходных переменных. D-триггеры 1 обнуляются по входу обнуления 13. Настроечная информация, записанная в D-триггерах 1 через элементы первой группы m•2n элементов И с тремя состояниями на выходе 6, управляют входами настройки 10.1.2-10. m. 2 блоков вычисления функций 10.1-10.m и определяют реализуемую в них логическую (булеву) функцию. D-триггеры 1 могут быть реализованы, например, на интегральных микросхемах 155ТМ2 с дополнительными инверторами по входу R.

Вторая группа D-триггеров 2 предназначена для записи и хранения информации управления по соответствующим входам элементов первой 6 и второй 9 групп m•2n элементов И с тремя состояниями на выходе для обеспечения возможности расширения разрядности вычисляемых логических функций в блоках вычисления функций 10.1-10.m. Количество D-триггеров 2 равно m•2n, где n - число входных переменных, m - число выходных переменных. D-триггеры 2 обнуляются по входу обнуления 13. Информация в D-триггеры 2 записывается с соответствующих входов расширения m групп входов расширения 12.1-12.m по переднему фронту сигнала "1" на выходе 7.2 дешифратора 7. Настроечные сигналы, записанные в D-триггерах 2, управляют элементами И с тремя состояниями на выходе групп 6, 9 таким образом, что если в D-триггере группы 2 записана "1", то к соответствующему входу настройки блока вычисления функций подключается настроечная информация с выхода соответствующего D-триггера группы 1, иначе подключается соответствующий разряд входов расширения соответствующей из m групп входов расширения 12.1-12.m. Таким образом, можно подключить к любому разряду входов настройки 10.1.2-10.m.2 блоков вычисления функций 10.1...10.m или константу с D-триггеров группы 1, либо дополнительную переменную со входов расширения, либо выходы других блоков вычисления функций из блоков 10.1. ..10.m, либо другого программируемого логического устройства для обеспечения расширения разрядности вычисляемых логических функций, например, в соответствие с /Корнейчук В.И., Тарасенко В.П. Вычислительные устройства на микросхемах: Справочник. - Киев: Техника, 1988. - С. 34-36/.

D-триггеры второй группы D-триггеров 2 также могут быть реализованы на микросхемах типа 155ТМ2 с дополнительными инверторами по входу 12.

Третья группа D-триггеров 3, содержащая 2m(n-1) триггеров, предназначена для записи и хранения с части (с 2(n-1) разрядов) соответствующих входов расширения m групп входов расширения 12.1-12.m по переднему фронту сигнала на выходе 7.3 дешифратора 7 информации задания существенных переменных (всех, кроме последней "старшей"), управляющей группами m(n-1) элементов И 4, m(n-1) элементов ИЛИ 8.

Если переменная несущественна, то соответствующие ей разряды Xi, из 2(n-1),  разрядов входов парафазных входных переменных 10.1.1-10.m. 1 блоков вычисления функций 10.1-10.m с помощью элементов И 4 (на их входах) обнуляются, а разряды

разрядов входов парафазных входных переменных 10.1.1-10.m. 1 блоков вычисления функций 10.1-10.m с помощью элементов И 4 (на их входах) обнуляются, а разряды  с помощью элементов ИЛИ 8 устанавливаются в "1". D-триггеры 3 обнуляются по входу сброса 13 и также могут быть реализованы на микросхемах 155ТМ2 с дополнительными инверторами по входу R.

с помощью элементов ИЛИ 8 устанавливаются в "1". D-триггеры 3 обнуляются по входу сброса 13 и также могут быть реализованы на микросхемах 155ТМ2 с дополнительными инверторами по входу R.

Группа m(n-1) элементов И 4 предназначена для подключения входных неинверсных переменных со входов парафазных входных переменных 11 к группам входов переменных соответствующих из m блоков вычисления функций 10.1-10.m. При несущественности некоторых входных неинверсных переменных, кроме последней "старшей", соответствующие разряды Xi,  , входов парафазных входных переменных соответствующего блока вычисления функций 10.i обнуляется с помощью соответствующих элементов И группы 2n•m элементов И 4. Старшая переменная всегда должна быть существенна. Таким образом, сигнал "1" на выходе соответствующего нечетного D-триггера группы 3 через соответствующий i-й элемент И группы 4 обеспечивает существенность этой переменной Xi, т.е. они принимаются с соответствующего разряда входов 11, а сигнал "0" на выходе соответствующего D-триггера группы 3 обеспечивает несущественность этой переменной, т.е. на соответствующий вход переменных j-го блока вычисления функций подается "0".

, входов парафазных входных переменных соответствующего блока вычисления функций 10.i обнуляется с помощью соответствующих элементов И группы 2n•m элементов И 4. Старшая переменная всегда должна быть существенна. Таким образом, сигнал "1" на выходе соответствующего нечетного D-триггера группы 3 через соответствующий i-й элемент И группы 4 обеспечивает существенность этой переменной Xi, т.е. они принимаются с соответствующего разряда входов 11, а сигнал "0" на выходе соответствующего D-триггера группы 3 обеспечивает несущественность этой переменной, т.е. на соответствующий вход переменных j-го блока вычисления функций подается "0".

Счетчик 5 предназначен для управления дешифратором 7 в режиме программирования. Предварительно счетчик 5 обнуляется по входу сброса 13. Счетчик 5 принимает импульсы со входа программирования 14.

Счетчик 5 может быть реализован, например, на интегральной микросхеме 155ИЕ2.

Первая группа m•2n элементов И с тремя состояниями на выходе 6 предназначена для подключения к настроечным входам блоков вычисления функций 10.1.. . 10. m настроечной информации с выходов D-триггеров первой группы 1, в том случае если активизированы неинверсные выходы D-триггеров второй группы 2.

Первая группа m•2n элементов И с тремя состояниями на выходе 6 может быть реализована, например, на интегральных микросхемах 589АП16.

Дешифратор 7 предназначен для управления входами синхронизации D-триггеров групп D-триггеров 1, 2, 3 по информации со счетчика 5. По первому импульсу программирования на выходе счетчика 5 устанавливается информация, приводящая к установлению "1" на выходе 7.1 дешифратора 7, по второму - на выходе 7.2, по третьему - на выходе 7.3. При этом информация записывается в D-триггеры групп 1, 2, 3 соответственно. По четвертому импульсу программирования устанавливается "1" на выходе 7.4 дешифратора 7, что приводит к возбуждению выхода окончания программирования 16.

Дешифратор 7 может быть реализован, например, на интегральной микросхеме 155ИД3, причем ее входы управления необходимо подключить к "0" В.

Группа m(n-1) элементов ИЛИ 8 предназначена для подключения входных инверсных переменных со входов 11 парафазных входных переменных к группам входов переменных 10.1.1. . .10.m.1 соответствующих из m блоков вычисления функций 10.1-10.m.

При несущественности некоторых входных инверсных переменных, кроме последней "старшей", соответствующие разряды  входов парафазных входных переменных соответствующего блока вычисления функций 10.i сигналом "1" с выхода соответствующего четного D-триггера группы 3 через соответствующий элемент группы элементов ИЛИ 8 устанавливается в состояние "1", обеспечивая несущественность i-й переменной для данного j-го блока вычисления функций 10. j, причем одновременно с помощью соответствующего четного D-триггера группы 3 и соответствующего элемента И группы 4 обнулятся и разряд Xi, обеспечивая несущественность этой переменной. Таким образом, для несущественной переменной Xi = 0,

входов парафазных входных переменных соответствующего блока вычисления функций 10.i сигналом "1" с выхода соответствующего четного D-триггера группы 3 через соответствующий элемент группы элементов ИЛИ 8 устанавливается в состояние "1", обеспечивая несущественность i-й переменной для данного j-го блока вычисления функций 10. j, причем одновременно с помощью соответствующего четного D-триггера группы 3 и соответствующего элемента И группы 4 обнулятся и разряд Xi, обеспечивая несущественность этой переменной. Таким образом, для несущественной переменной Xi = 0,  . "Старшая" переменная всегда существенна и разряды Xn,

. "Старшая" переменная всегда существенна и разряды Xn,  непосредственно поступают на входы переменных блоков 10.1...10.m.

непосредственно поступают на входы переменных блоков 10.1...10.m.

Вторая группа m•2n элементов И 9 с тремя состояниями на выходе предназначена для подключения к настроечным входам 10.1.2...10.m.2 соответствующих блоков вычисления функций 10.1...10.m соответствующих входов расширения соответствующей группы из m групп 12.1-12.m в случае, если активированы инверсные выходы D-триггеров группы 2. Вторая группа m•2n элементов И с тремя состояниями на выходе может быть реализована, например, на интегральных микросхемах 589ПА16.

m блоков вычисления функций 10.1-10.m предназначены для вычисления логических функций, заданных настроечной информацией по настроечным входам i-го блока 10. i.1, причем количество существенных переменных определяется входами переменных 10.i.2. Вычисления производятся по импульсам синхронизации, поступающим на соответствующий вход 17 блоков 10.

Вычисления могут проводиться в нормальном режиме, когда вход реконфигурации 18.i блока 10.i обнулен, либо в режиме вычислений при наличии отказов, когда на входе реконфигурации 18.i установлена "1", а на входе типа реконфигурации i-го блока 10.i установлен тип реконфигурации. В случае отсутствия отказов, выявленных тестированием с помощью внешних по отношению к устройству технических средств, на выходе готовности 15.i.3 блока 10.i всегда установлена "1" и готовность результатов вычислений на выходе значения функции 15. i.1 и инверсного значения функции 15.i.2 результат можно использовать по окончании действия импульса синхронизации по входу 17 с учетом необходимости ожидания завершения переходных процессов внешними по отношению к устройству техническими средствами.

В случае наличия отказов в блоке 10.i готовность результатов определяется установкой на выходе 15.i.3 сигнала "1".

Внутренняя структура блоков вычисления функций 10.1-10.m будет описана ниже.

Группа 2•n•m входов парафазных входных переменных 11 предназначена для приема значений парафазных входных переменных, логические функции от n аргументов которой вычисляются в блоках вычисления функций 10.1-10.m, на каждый из которых поступает n разрядов группы. Значения парафазных входных переменных фиксируются на время вычислений внешними по отношению к устройству техническими средствами, например регистром, для исключения состязаний сигналов во время вычислений. Поступление импульса на вход синхронизации 17 организуется внешними техническими средствами только после завершения переходных процессов фиксации парафазных входных переменных во внешних технических средствах.

m групп входов расширения 12.1-12.m, каждая из которых содержит 2n разрядов, предназначена для обеспечения увеличения разрядности вычисляемых логических функций путем подключения к настроечным входам блоков вычисления функций дополнительных переменных или выходов аналогичных блоков данного или другого аналогичного программируемого логического устройства в режимах вычислений. В режиме программирования на входы расширения последовательно с помощью внешних технических средств подается информация программирования D-триггеров групп 1, 2, 3.

Вход сброса 13 предназначен для приема импульса обнуления устройства для обнуления D-триггеров групп 1, 2, 3, счетчика 5 и блоков вычисления функций 10.1-10.m.

Вход программирования 14 предназначен для приема импульсов программирования, управляющих счетчиком 5.

Группа m выходов значений функций 15.1.1-15.m.1 предназначена для выдачи значений логических функций, вычисленных в блоках вычисления функций 10.1-10.m.

Группа m выходов инверсных значений функций 15.1.2-15.m.2 предназначена для выдачи инверсных значений логических функций, вычисленных в блоках вычисления функций 10.1-10.m.

Группа m выходов готовности 15.1.3-15. m. 3 предназначена для выдачи внешним техническим средствам сигналов готовности результатов вычислений в блоках вычисления функций 10.1-10.m.

Выход окончания программирования 16 предназначен для выдачи сигнала окончания программирования с выхода 7.4 дешифратора 7, по которому разрешается начать вычисления.

Вход синхронизации 17 предназначен для приема сигналов синхронизации от внешних технических средств после окончания программирования и записи, например, во внешний регистр парафазных входных переменных.

Группа m входов реконфигурации блоков вычисления функций при отказах 18.1-18.m предназначена для приема от внешних по отношению к устройству технических средств сигналов необходимости реконфигурации, что выясняется внешними техническими средствами в результате тестирования устройства.

Группа m входов типа реконфигурации блоков вычисления функций при отказах 19.1-19.m предназначена для приема от внешних технических средств сигналов типа реконфигурации блоков вычисления функций, что выясняется в результате тестирования устройства.

После программирования устройства диагностической информацией производится вычисления (на входах 18, 19 установлены "0"). Если результаты вычислений не соответствуют эталону, то на входе 18.i соответствующего ненормового блока 10.i устанавливается "1". Затем вновь производятся вычисления и сравнение с эталоном (все это выполняется внешними по отношению к устройству техническими средствами). Если же вновь получается ненорма, то на входе 19.i устанавливается "1" внешними техническими средствами. Если после очередного тестирования получают ненорму блоки вычисления функций 10.i, то внешние технические средства делают вывод об отказе, неустраненном реконфигурацией, и требуемые вычисления производятся оставшимися блоками вычисления функций перепрограммированием.

Группа 4•2n элементов И с тремя состояниями на выходе 20 (фиг. 2) блоков вычисления функций 10. i предназначена для подключения к нечетным входам элементов 2•2 НЕ-И-ИЛИ настроечной информации с настроечных входов 10.i.2, причем четные элементы И группы 20 подключают исходную настроечную информацию, когда их входы управления активированы инверсным выходом обнуленного T-триггера 23, а нечетные элементы И группы 20 - "переставленную" настроечную информацию, когда первая и вторая половина информации со входов 10.i.2 меняется местами.

Это необходимо для реализации вычислений в режиме реконфигурации при отказах. Поэтому ко входам данных первой половины нечетных элементов И с тремя состояниями на выходе 20 подключена соответствующая настроечная информация второй половины настроечных входов 10.i.2, а ко входам данных второй половины нечетных элементов И группы 20 - соответствующая настроечная информация первой половины настроечных входов 10.i.2.

Таким образом, настроечная информация 10.i.2.1-10.i.2.2n-1 и информация 10.i.2.2n-1+1...10.i.2.2n меняется местами.

Элементы И с тремя состояниями на выходе группы 20 управляются инверсным и неинверсным выходами T-триггера 23, четная - инверсным, нечетная - неинверсным. Элементы И с тремя состояниями на выходе 20 могут быть, например, реализованы на микросхемах 589АП16.

Первый D-триггер 21 предназначен для приема значения сигнала с последней из n групп элементов 2•2 НЕ-И-ИЛИ, содержащей один элемент 37.n по импульсу синхронизации со входа 17. Первый D-триггер 21 обнуляется сигналом со входа сброса 13.

В первый D-триггер 21 записывается значение функции в режиме вычисления при отсутствии отказов, которое затем выдается через элемент ИЛИ 27 на выходе значений функций 15.i.1, 15.i.2. В режиме вычислений при наличии отказов в первый D-триггер 21 по первому импульсу синхронизации записывается значение первой подфункции, а по второму импульсу значение второй подфункции. Первый D-триггер 21 может быть реализован, например, на микросхемах 155ТМ2 с инвертором по входу R.

Второй D-триггер 22 предназначен для приема сигнала с выхода первого D-триггера 21 по импульсу синхронизации, поступающему на вход синхронизации 17. Второй D-триггер 22 обнуляется импульсом сброса, поступающим на вход сброса 13 через элемент ИЛИ 28, или импульсом дополнительного сброс со входа 40, поступающим в режиме вычислений при наличии отказов.

В режиме вычислений при отсутствии отказов на вход 18.i поступает "0", поэтому сигналом через элемент ИЛИ 28, поступающим с выхода инвертора 34, второй D-триггер 22 удерживается в состоянии "0" независимо от сигналов синхронизации.

В режиме вычислений при наличии отказов по первому импульсу синхронизации во второй D-триггер 22 записывается сигнал с выхода первого D-триггера 21, т. е. его исходное состояние "0". По второму импульсу синхронизации во второй D-триггер 22 записывается значение первой подфункции. После этого производится обнуление второго D-триггера 22 через элемент ИЛИ 28 по входу дополнительного сброса 40. Второй D-триггер 22 может быть реализован, например, на микросхемах 155ТМ2 с инвертором по входу R.

T-триггер 23 предназначен для управления группой 4•2n элементов И с тремя состояниями на выходе 20, причем четные элементы И группы 20 подключаются инверсным выходом T-триггера 23, когда T-триггер 23 обнулен, а нечетные элементы группы 20 - неинверсным выходом T-триггера 23, т.е. когда он установлен в состояние "1", причем изменение состояния T-триггера 23 производится по заднему фронту импульса синхронизации и гонок сигналов при переключениях не возникает, так как запись значений функции (подфункции) в D-триггеры 21, 22 производится по переднему фронту сигнала синхронизации.

Кроме того, T-триггер 23 управляет дополнительной группой элементов И с тремя состояниями на выходе 39 аналогично вышеописанному, управляя их четными и нечетными элементами для "перекрещивания" последней, старшей переменной при вычислениях в случае наличия отказов. При обнуленном T-триггере 23 подключаются нечетные элементы дополнительной группы элементов И с тремя состояниями на выходе 39, а при установленном T-триггере 23 подключаются четные элементы дополнительной группы элементов И с тремя состояниями на выходе 39, обеспечивая смену переменных первой и второй половины элемента 2•2 НЕ-И-ИЛИ 37.n.

T-триггер 23 управляет элементом И 32 для формирования сигнала готовности результатов вычислений при вычислениях в условиях отказов.

T-триггер 23 может быть реализован, например, на интегральной микросхеме 155ТВ1 с инвертором по входу сброса.

RS-триггер фиксации импульса 24 предназначен для управления элементов И 32 с целью формирования сигнала готовности при вычислениях в случае наличия отказов.

RS-триггер фиксации импульса 24 обнуляется сигналом с выхода элемента ИЛИ 28, а устанавливается сигналом с выхода элемента задержки 38 по первому импульсу синхронизации, причем задержка такова, что T-триггер 23 успевает установиться по заднему фронту первого импульса и обнуляется его инверсный выход, а после этого установится RS-триггер 24. Таким образом, сигнал "1" на выходе элемента И 32 формируется после каждого второго синхроимпульса, однако этот сигнал используется только в режиме вычислений при наличии отказов.

RS-триггер фиксации импульса 24 может быть реализован, например, на микросхемах 155ТМ2 с инверторами по входам R, S.

Первый элемент ИЛИ 25 предназначен для подключения ко второму входу элемента 37.n либо сигнала с объединенных входов первого и второго элементов И с тремя состояниями на выходе группы 39 либо сигнала с выхода элемента И 30 с целью обеспечения режимов вычислений при наличии отказов. В первом случае подключается самая старшая переменная Xn или ее инверсия  . Во втором случае - логическая единица для отключения верхней половины элемента 37.n.

. Во втором случае - логическая единица для отключения верхней половины элемента 37.n.

Второй элемент ИЛИ 26 предназначен для управления по четвертому входу элементом 37.n аналогично элементу ИЛИ 25. Второй элемент ИЛИ 26 подключает инверсию самой старшей переменной  или саму переменную Xn, поступающую с объединенных выходов третьего и четвертого элементов И с тремя состояниями на выходе дополнительной группы 39. В случае возбуждения выхода элемента И 31 на выходе второго элемента ИЛИ 26 устанавливается сигнал "1" и нижняя половина элемента 37. n отключается. Все это также обеспечивает реализацию режима вычислений при наличии отказов.

или саму переменную Xn, поступающую с объединенных выходов третьего и четвертого элементов И с тремя состояниями на выходе дополнительной группы 39. В случае возбуждения выхода элемента И 31 на выходе второго элемента ИЛИ 26 устанавливается сигнал "1" и нижняя половина элемента 37. n отключается. Все это также обеспечивает реализацию режима вычислений при наличии отказов.

Третий элемент ИЛИ 27 предназначен для формирования сигнала значения функции по сигналам на выходах первого 21 и второго 22 D-триггеров. При вычислениях в условиях отсутствия отказов выход второго D-триггера 22 всегда обнулен, поэтому значение функции определяется значением сигнала на выходе первого D-триггера 21 после поступления на него синхроимпульса.

Во время вычислений при наличии отказов значение функции определяется дизъюнкцией сигналов с выходов первого 21 и второго 22 D-триггеров после поступления второго синхроимпульса.

Четвертый элемент ИЛИ 28 предназначен для формирования сигнала сброса второго D-триггера 22, RS-триггера фиксации импульса 24, T-триггера 23, если поступает сигнал сброса на вход сброса 13, на вход дополнительного сброса 40 или если имеется сигнал логической единицы на выходе второго инвертора 34.

Пятый элемент ИЛИ 29 предназначен для формирования сигнала готовности на выход готовности 15.i.3 в том случае, если активирован выход элемента И 32, т. е. после окончания действия второго импульса синхронизации в режиме вычислений при наличии отказов, если активирован выход элемента ИЛИ 27, т.е. если выясняется, что логическая функция равна единице уже при вычислениях первой подфункции, наконец, если активирован выход инвертора 36, т.е. в случае вычислений при отсутствии отказов.

Первый элемент И 30 предназначен для формирования сигнала отключения верхней половины элемента 2•2 НЕ-И-ИЛИ 37.n ("логическая 1") в режиме вычисления при наличии отказов, если активирован вход 18.i и вход 19.i.

Второй элемент И 31 предназначен для формирования сигнала отключения нижней половины элемента 2•2 НЕ-И-ИЛИ 37.n ("логическая 1") в режиме вычисления при наличии отказов, если активирован вход 18.i и неактивирован вход 19.i (активируется выход инвертора 33).

Третий элемент И 32 предназначен для формирования сигнала готовности результатов вычисления в режиме вычислений при наличии отказов, если установлен RS-триггер 24 и обнулен T-триггер 23, т.е. после каждого второго импульса синхронизации.

Первый инвертор 33 предназначен для управления элементом И 31 с целью отключения им сигналом "1" нижней половины элемента 2•2 НЕ-И-ИЛИ 37.n, если неактивирован вход 19.i типа реконфигурации при отказах.

Второй инвертор 34 предназначен для формирования сигнала постоянного сброса D-тригггера 22 через элемент ИЛИ 28, RS-триггера 24 и T-триггера 23 в случае отсутствия отказов, т.е. когда неактивирован вход 18.i реконфигурации блока вычисления функций при отказах (на этом входе "0").

Третий инвертор 35 предназначен для формирования инверсного значения вычисленной логической функции на соответствующий выход 15.i.2.

Четвертый инвертор 36 предназначен для формирования сигнала готовности через элемент ИЛИ 29 в том случае, если неактивирован вход 18.i реконфигурации блока вычисления функции при отказах, т.е. при отсутствии отказов.

n групп элементов 2•2НЕ-И-ИЛИ 37.1-37.n предназначены для вычисления логических функций в соответствии с настроечными сигналами на входах 10.i.2 по n входным сигналам на входах 10.i.1.

Первая группа содержит 2n элементов, последняя - один элемент, т.е. каждая i-я группа содержит 2n-i элементов, i = 1, n и имеется "пирамидальное" соединение элементов.

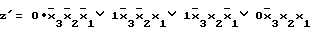

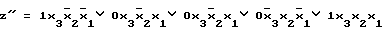

Элементы 37 реализуют функцию С.Тюрина  особенностью которой является то, что она сама и все ее модификации, полученные при однократной подстановке констант 0,1 или однократного инверсирования переменных, обладают функциональной полнотой.

особенностью которой является то, что она сама и все ее модификации, полученные при однократной подстановке констант 0,1 или однократного инверсирования переменных, обладают функциональной полнотой.

Поэтому однократный отказ входов даже последнего элемента в "пирамиде" не приводит к установлению константы на его выходе, что обеспечивает возможность вычислений за два такта на половине элементов.

Элемент задержки 38 предназначен для задержки установки RS-триггера 24 по входу S на время обнуления инверсного выхода T-триггера 23 после воздействия заднего фронта импульса синхронизации для исключения выдачи ложной готовности при вычислениях в случае отказов.

Дополнительная группа элементов И с высоким импендансом на выходе 39 предназначена для подключения к четным входам последней группы из n групп элементов 2•2 НЕ-И-ИЛИ 37.1-37.n, содержащей один элемент 37.n либо "своей" переменной, либо переменной с другого четного входа по сигналам управления с T-триггера 23, что необходимо для реализации режима вычислений при наличии отказов. Таким образом, происходит своего рода "перекрещивание переменных" т. е. вместе с заменой констант по входам элементов первой группы 37.1 происходит замена старшей переменной, обеспечивая вычисление логической функции по подфункциям на половине элементов 37.

Дополнительный вход сброса 40 предназначен для приема от внешних технических средств дополнительного сигнала сброса в режиме вычислений при наличии отказов для обнуления D-триггеров 21, 22 после выполнения вычислений (после поступления двух импульсов синхронизации) для исключения выдачи ложного сигнала готовности через элементы ИЛИ 27, 29 при сдвиге из D-триггера 21 в D-триггер 22 в новом цикле вычислений.

Программируемое логическое устройство работает в следующих режимах: 1) программирования (или запись); 2) вычисления при отсутствии отказов; 3) вычисления при наличии отказов.

В режиме программирования (или записи) устройство работает следующим образом. В исходном состоянии D-триггеры первой 1, второй 2 и 3 групп, счетчик 5 обнулены по входу 13 устройства, на входы управления первой группы элементов И с тремя состояниями на выходе 6 поданы сигналы "0" и их выходе находятся в высокоимпедансном состоянии, на входы управления второй группы элементов И с тремя состояниями на выходе 7 поданы сигналы "1" и на их выходе передается информация с соответствующих разрядов соответствующей группы входов расширения (фиг. 1).

По первому импульсу, поступающему на вход программирования 14 устройства, счетчик 5 переходит в первое состояние и на выходе 7.1 дешифратора 7 появляется сигнал "1". По этому сигналу информация программирования, предварительно поданная на соответствующие из m групп входов расширения 12.1-12. m также с помощью внешних по отношению к устройству технических средств записывается в D-триггеры группы 1.

Информация в D-триггеры заносится с их входов D по переднему фронту сигнала, поступающего с выхода 7.1 дешифратора 7. После этого с помощью внешних по отношению к устройству технических средств на соответствующие из m групп входов расширения 12.1-12.m подается информация программирования второй группы D-триггеров 2, в которые она и записывается по второму импульсу программирования, поступающему на вход 14 устройства, по переднему фронту сигнала "1", возникающему на выходе 7.2 дешифратора 7.

По третьему импульсу программирования активируется выход 7.3 дешифратора 7 и информация с 2(n-1) входов в каждой из m групп входов расширения 12.1-12. m, предварительно поданная внешними техническими средствами для указания разрядности вычисляемых логических функций в m блоках вычисления логических функций 10.1-10. m, записывается по D входам в соответствующие D-триггеры третьей группы. Выходы D-триггеров 3 группы управляют подключением входных переменных через группы m(n-1) элементов И 4, m(n-1) элементов ИЛИ 8. По четвертому импульсу программирования на выходе 7.4 дешифратора устанавливается "1"; и на выходе 16 окончания программирования появляется сигнал "1", свидетельствующий о завершении режима программирования. При очередном цикле программирования, если в этом есть необходимость, производится предварительное обнуление устройства по входу обнуления 13, вследствие чего счетчик 5 будет вновь установлен в нулевое, исходное состояние и на выходе 16 появится "0".

В D-триггеры 1 группы 1 в режиме программирования записываются m•2n констант настройки m блоков вычисления функций 10, в D-триггеры 2 группы 2 записываются m•2n сигналов управления И с тремя состояниями на выходе группы 6, 7 для подключения ко входам настройки 10.i.2-10.m.2 m блоков вычисления функций 10.1-10.m либо констант с выходов отдельных или всех D-триггеров 1 группы 1, либо отдельных или всех разрядов m групп входов расширения 12.1-12.m.

В D-триггеры 3 группы 3 в режиме программирования записываются сигналы управления группами m(n-1) элементов И 4 (нечетными D-триггерами), m(n-1) элементов ИЛИ 8 (четными D-триггерами) с целью указания разрядности входных переменных (за исключением самой старшей) на соответствующих входах переменных 10.i.1-10.m.1 m блоков вычисления функций 10.1-10.m. В случае неиспользования (несущественности) некоторых (кроме старшей) входных переменных в конкретном i-м блоке 10.i с помощью информации, записанной в соответствующих D-триггерах группы 3, обнуляются выходы соответствующих элементов И группы 4 и устанавливаются в "1" выходы соответствующих элементов ИЛИ группы 8, что приводит к "навязке" соответствующих констант на парафазных входах переменных 10.i.1-10.m.1.

В режиме вычисления при отсутствии отказов (отсутствие отказов устанавливается в процессе некоторых эталонных вычислений) на входах реконфигурации 18.1-18.m блоков вычисления функций 10.1-10.m с помощью технических средств, внешних по отношению к устройству, устанавливается сигнал "0", а на входах типа реконфигурации 19.1-19.m блоков вычисления функций 10.1-10.m информация в этом случае может быть любой.

Блоки вычисления функций 10.1-10.m вычисляют значения логических функций без расширения, задаваемые информацией на выходах соответствующих D-триггеров 1 группы 1, при этом соответствующие D-триггеры 2 группы D-триггеров 2 находятся в состоянии "1" и выходы соответствующих D-триггеров 1 группы 1 через соответствующие элементы И с тремя состояниями на выходе первой группы 6 поступают на входы настройки 10.i.2 соответствующего блока вычисления функций 10.i. Вычисления производятся по синхросигналу, поступаемому на вход 17 устройства, при этом на выходах готовности 15.1.3-15.m.3 по завершении вычисления в блоках вычисления функций появляется сигнал "1", а на группах m выходов значения функций 15.1.1-15. m. 1 и на группах m выходов инверсных значений функций 15.1.2-15. m. 2 появляются соответственно значение соответствующих функций и их инверсий. Предполагается, что для устранения состязаний входных сигналов на входах 11 они фиксируются на время вычислений внешними по отношению к устройству средствами.

Устройство предполагает возможность расширения разрядности вычисляемых функций (>n) при подключении выходов 15.i.1, 15.i.2 отдельных или нескольких блоков 10.1-10.m по отдельным или всех входам расширения в группах 12.1-12. m, кроме того, к этим входам возможно подключение отдельных переменных из входных m•n переменных 11, наконец, к отдельным входам парафазных переменных 11 возможно подключение выходов 15.i.1, 15.i.2 других аналогичных устройств, а также возможно подключение выходов 15.i.1, 15.i.2 других аналогичных устройств ко входам расширения 12.1-12.m данного устройства.

При вычислении логических функций с расширением устройство работает аналогично вычислениям без расширения, за исключением того, что сигнал общей готовности необходимо формировать с помощью внешних по отношению к устройству (устройствам) элементов И.

Расширение разрядности вычисляемых логических функций может быть осуществлено, например, с использованием методов, описанных в книге /Корнейчук В.И., Тарасенко В.П. Вычислительные устройства на микросхемах: Справочник. - Киев: Тэхника, 1988. - С. 34-36/.

В режиме вычислений при отсутствии отказов блоки вычисления функций работают следующим образом (фиг. 2, 3).

В исходном состоянии первый 21 и второй 22 D-триггеры, T-триггер 23, RS-триггер фиксации импульса 24 обнулены по входу сброса блоки вычисления функций сигналом со входа сброса 13.

На входах переменных 10.i.1 блока вычисления функций 10.i установлены значения парафазных входных переменных; на входах настройки 10.i.2 - информация настройки. Так как T-триггер 23 обнулен, то его инверсный выход активирует входы управления входов управления нечетных элементов И группы 4•2n элементов И с тремя состояниями на выходе 20, а неинверсный выход T-триггера 23 формирует сигнал "0" на входы управления четных элементов из группы 4•2n элементов И с тремя состояниями на выходе 20 и их выходы находятся в состоянии высокого импеданса. Вследствие этого к нечетным входам элементов 2•2 НЕ-И-ИЛИ из группы 37.1 (2n-1 элементов первого уровня) подключены соответствующие разряды из 2n разрядов входов настройки 10.i.2, настраивающих блок вычисления функций на требуемую логическую функцию, на четные входы элементов 37.1 поступают два разряда x1,  , соответствующие первой переменной из n входных переменных данного i-го блока 10.i, поданных на входы 10. i. 1 в парафазном коде (x1 - на вторые входы,

, соответствующие первой переменной из n входных переменных данного i-го блока 10.i, поданных на входы 10. i. 1 в парафазном коде (x1 - на вторые входы,  - на четвертые входы элементов 37.1). Аналогично на четные входы элементов других групп 37.j, где j = 2, n-1 поступают переменные xj,

- на четвертые входы элементов 37.1). Аналогично на четные входы элементов других групп 37.j, где j = 2, n-1 поступают переменные xj,  со входов 10.i.1. Группа 37.n из n групп 37.1-37. n элементов 2•2 НЕ-И-ИЛИ содержит один элемент, на второй и четвертый входы которого при отсутствии отказов поступают соответственно переменные xn,

со входов 10.i.1. Группа 37.n из n групп 37.1-37. n элементов 2•2 НЕ-И-ИЛИ содержит один элемент, на второй и четвертый входы которого при отсутствии отказов поступают соответственно переменные xn,  со входов 10.i.1, через дополнительную группу элементов И с высоким импедансом на выходе 39, нечетные элементы которой по входам управления подключены инверсным выходом T-триггера 23, а четные имеют на выходах высокий импеданс, так как их входы управления обнулены неинверсным выходом T-триггера 23, так как выходы элементов И 30, 31 обнулены вследствие наличия "0" на входе реконфигурации при отказе 18.i, в связи с этим же на выходе элемента ИЛИ 29 и на выходах 15.i.3 устройства установлен сигнал "1" готовности (сигнал отсутствия отказа со входа 18.i инвертируется в элементе 36 и поступает на второй вход элемента ИЛИ 29).

со входов 10.i.1, через дополнительную группу элементов И с высоким импедансом на выходе 39, нечетные элементы которой по входам управления подключены инверсным выходом T-триггера 23, а четные имеют на выходах высокий импеданс, так как их входы управления обнулены неинверсным выходом T-триггера 23, так как выходы элементов И 30, 31 обнулены вследствие наличия "0" на входе реконфигурации при отказе 18.i, в связи с этим же на выходе элемента ИЛИ 29 и на выходах 15.i.3 устройства установлен сигнал "1" готовности (сигнал отсутствия отказа со входа 18.i инвертируется в элементе 36 и поступает на второй вход элемента ИЛИ 29).

При вычислении логических функций в условиях отсутствия отказов, что определяется предварительным тестированием (сравнениям результатов вычислений с эталонными в процессе выполнения описываемых вычислений) по синхросигналу, поступающему со входа 17 в первый триггер 21 записывается значение вычисленной функции, которое через элемент ИЛИ 27, на второй вход которого поступает "0" со второго триггера 22, обнуленного в свою очередь выходом элемента ИЛИ 28, на который подана "1" с выхода инвертора 34, подключенного ко входу 18. i реконфигурации при отказах. Сигналом "1" с выхода элемента 29 триггеры 24, 23 удерживается в состоянии нуля и выходные сигналы T-триггера 23 не изменяются и не влияют на процесс вычислений в группе элементов 37.