Изобретение относится к вычислительной технике и может быть использовано для вычисления систем булевых функций, описывающих как комбинационные, так и по- следовзтельностные автоматы.

Известно устройство, содержащее gn- входовых элементов И (п - количество информационных входов устройства, ), t - элементов ИЛИ (t - количество информационных выходов устройства), три группы D-триггеров, группу элементов И с тремя состояниями на выходе, группу элементов И-НЕ с тремя состояниями на выходе, gt

двухвходовых элементов И, счетчик и дешифратор.

Недостатком устройства является низкое быстродействие в режиме записи.

Наиболее близким по технической сущности к изобретению является программируемое логическое устройство, содержащее g n-входовых элементов И (п - количество информационных входов устройства, iЈg 22n), t элементов ИЛИ (t - количество информационных выходов устройства), первую, вторую и третью группу D-триггеров, первую группу элементов И с тремя состоянияVJ XI

V4

GJ CJ

и выхода, группу элементов И-НЕ с тремя остояниями выхода, gt двухвходовых элеентов И, счетчик и дешифратор, три RS- риггера. дополнительный элемент ИЛИ, вторую группу элементов И с тремя состоя- 5 ниями на выходе, причем D-входы {I + (К - 1)х п}-х D-триггеров первой и второй групп, первые входы соответствующих элементов И с тремя состояниями выхода первой группы и первые входы элементов И-НЕ с тремя со- 10 стояниями выхода (1 1 п; 1 :Ј К д) являются 1-м информационным входом устройства, выходы D-триггеров первой группы соединены с вторыми входами соответствующих элементов И с тремя состоя- 15 ниями выхода первой группы, а выходы D-триггеров второй группы - с вторыми входами соответствующих элементов

И-НЕ с тремя состояниями выхода, выходы которых соединены с выходами соот- 20 ветствующих элементов И с тремя состояниями выхода первой группы, С-вхо- ды (К- 1)п + 1}тх D-триггеров первой группы соединены с К-м нечетным выходом дешифратора, а С-входы одноименных D-тригге- 25 ров второй группы - с К-м четным выходом дешифратора, выходы {(К - 1}п + элементов И с тремя состояниями выхода первой группы соединены с входами К-ro п-входо- вого элемента И, выход которого соединен 30 с первыми входами К + (j - 1)gJ-x двухвходовых элементов И (1 j t), вторые входы которых соединены с выходами соответствующих D-триггеров третьей группы, а выходы - с К-м входом |-х элементов ИЛИ, 35 информационные выходы счетчика соединены с входами дешифратора, а счетный вход счетчика является тактовым входом устройства, первые входы второй группы элементов И с тремя состояниями выхода 40 соединены с выходами соответствующих элементов ИЛИ, а вторые входы - с инверсным выходом третьего RS-триггера. 8-вход которого соединен с кулевым выходом дешифратора, а R-вход - с выходом допол- 45 нительного элемента ИЛИ, выход j-ro элемента И с тремя состояниями выхода второй группы соединен с D-входами К + (J - 1) D-триггеров третьей группы и является соответствующим информационным выходом 50 устройства, р-й выход дешифратора () соединен с С-входами {р - 1)t + D-триггеров третьей группы, S-входы первого и второго RS-триггеров соединены соответственно с g-м выходом дешифратора и с выхо- 55 дом переполнения счетчика, выход первого RS-триггера является выходом индикации программирования элементов ИЛИ устройства, выход второго RS-триггера соединен с

первым входом дополнительного элемента ИЛИ и является выходом индикации программирования элементов И устройства, R- входы D- и RS-триггеров и второй вход дополнительного элемента ИЛИ является входом сброса устройства.

Недостатком этого устройства является узкая область применения и отсутствие возможности наращивания рангов вычисляемых конъюнкций.

Эти недостатки обусловлены следующими обстоятельствами. Технические средства данного устройства ориентированы на вычисление логических функций, зависящих от текущего значения информационных входов, т.е. реализацию .комбинационного автомата. Реализация последовательностного автомата невозможна без применения дополнительных технических средств. Кроме того, в устройстве невозможно расширение рангов конъюнкций, что необходимо, например, в задачах вычисления многоразрядных логических функций.

Целью изобретения является расширение области применения за счет обеспечения возможности наращивания рангов вычисляемых конъюнкций.

Указанная цель достигается тем, что в программируемое логическое устройство, содержащее К групп по n+s элементов И с тремя состояниями выхода, где К - максимально возможное количество одновременно вычисляемых конъюнкций, п - максимальная разрядность входного сигнала, S - максимальная разрядность кода внутреннего состояния реализуемых автоматов, К групп по n+s элементов И-НЕ с тремя состояниями выхода, первую группу Кэлементов И, L групп по К элементов И, где L- максимально возможное количество одновременно вычисляемых булевых функций, группу элементов ИЛИ, причем выходы элементов И-НЕ стремя состояниями выхода каждый из К групп соединены с выходами соответствующих элементов И с тремя состояниями выхода соответствующей группы и с соответствующими входами соответствующего элемента И первой группы Кэлементов И, выходы которой соединены с первыми входами соответствующих элементов И каждой из L по К групп элементов И, выходы элементов И каждой из L групп по К элементов И подключены к соответствующим входам соответствующего элемента ИЛИ группы L элементов ИЛИ, введены блок оперативкой памяти констант, регистр, К групп по R элементов ИЛИ, где R - количество входов расширения, вторая группе К элементов И, два групповых мультиплексора, инвертор и шинный формирователь, причем выходы группы L элементов ИЛИ являются соответствующими информационными входами регистра, первая группа m разрядов выхода которого является информационным входом шинного формирователя, а вторая s-разрядная группа - выходом кода состояния устройства, где s+m L, и первым информационным входом второго группового мультиплексора, выход которого является первой группой адресных входов оперативной памяти, второй группой адресных входов которой является выход первого группового мультиплексора, первым, вторым информационным и адресным входами которого являются входы кода алгоритма, старших адресов записи и настройки устройства соответственно, вторым информационным, адресным и входом разрешения второго группового мультиплексора являются входы младших адресов записи, настройки и разрешения устройства соответственно, входами разрешения, данных и записи оперативной памяти являются входы разрешения, входы-выходы и записи устройства соответственно, вход синхронизации регистра является входом синхронизации устройства, вход настройки устройства подключен к входу инвертора, выход которого является входом разрешения шинного формирователя, выход которого является входом-выходом устройства, нечетные выходы каждой из К групп по n+s выходов настройки конъюнкций первой группы выходов блока оперативной памяти констант являются первыми входами соответствующих К групп элементов И с тремя состояниями выхода, а четные - первыми входами соответствующих К групп элементов И-НЕ с тремя состояниями выхода, KL выходов настройки функций оперативной памяти подключены к вторым входам соответствующих из L групп по К элементов И, К групп no R выходов расширения оперативной памяти являются первыми входами соответствующих из К групп no R элементов ИЛИ, вторыми входами которых являются соответствующие входы расширения устройства, а выходы каждой из К групп по R элементов ИЛИ подключены к соответствующим входам соответствующего элемента И второй группы элементов И. выходы которых являются (п+5+1)-ми входами соответствующих элементов И первой группы, вторая группа s выходов регистра а конкатенации с входными n-разрядными сигналами является входным ()-разрядним дискретным сигналом, который подключен к информационным входам соответствующей пары элементов И, И-НЕ каждой из К групп n+s элементов И, И-НЕ с тррмя состояниями

выхода, выходы элементов И первой ipynnw ((элементов И являются выходами расширения устройства.

Расширение области применения уст- 5 ройства достигается за счет обеспечения возможности наращивания рангов вычисляемых конъюнкций путем введения нового режима реализации последовательностно- го автомата с возможностью расширения 10 рангов вычисляемых конъюнкций.

Сущность введенного режима заключается в следующем:

а)часть вычисленных логических функций используется в качестве составляющей

5 входного сигнала, т.е. реализована обратная связь;

б)сигналы обратной связи (текущее состояние автомата) могут быть использованы для сокращения объема памяти констант на0 стройки, так как в каждом автомате реализуется меньшая система функций; это может быть полезно в задачах, требующих большой разрядности входного сигнала;

в)часть вектора значений конъюнкций 5 передается на выходы расширения устройства и может быть использована при вычислениях в других устройствах, при вычислении многоразрядных булевых функций;

0 г) сигналы, поступающие на входы расширения из других устройств, могут быть использованы для вычисления многоразрядных булевых функций;

д) учет результатов вычислений внеш5 них подконъюнкций производится специальной константой.

Введение блока оперативной памяти констант с соответствующими связями позволяет записывать, хранить и считывать

0 константы, используемые в новом введенном режиме для различных вариантов алгоритмов, а также обеспечивает возможность изменения констант по коду состояния автомата.

5 Введение регистра с соответствующими связями позволяет хранить полный выходной сигнал, содержащий и код текущего состояния автомата, что необходимо при реализации последовательностного автомата.

0 Введение К групп по R элементов ИЛИ (где К - число конъюнкций; R - число входов расширения) с соответствующими связями позволяет учитывать только те разряды входов расширения, которым соответству5 ют выходы третьей группы выходов блока оперативной памяти констант, находящиеся а состоянии логического нуля, иначе происходит маскирование входов расширения. Введение второй группы К элементов И с соответствующими связями и позволяет

вычислять значения конъюнкций с учетом информации на входах расширения и соответствующей константы на третьей группе выходов оперативной памяти путем вычисления значения внешних подконъюнкций.

Введение первого группового мультиплексора и соответствующих ему связей позволяет изменять информацию на второй группе адресных входов блока оперативной памяти констант в режиме настройки для реализации нового режима.

Введение второго группового мультиплексора с соответствующими связями позволяет изменять информацию на первой группе адресных входов оперативной памяти в режиме настройки для реализации нового режима, а также учитывать код текущего состояния автомата при считывании констант.

Введение инвертора с соответствующими связями позволяет отключить выходы шинного формирователя от входов-выходов в режиме настройки для реализации нового режима.

Введение шинного формирователя с соответствующими связями позволяет использовать выходы-входы устройства для записи информации в оперативную память в режиме настройки для реализации нового режима.

Введение выходов расширения позволяет передавать результаты вычислений части конъюнкций на другие устройства для увеличения рангов вычисляемых в них конъюнкций в новом режиме.

Введение входов расширения позволяет принимать результаты вычислений в других устройствах для увеличения рангов части вычисляемых конъюнкций в новом режиме.

Введение входа разрешения второго мультиплексора позволяет переводить выходы второго мультиплексора в нулевое со- стояние для исключения учета кода состояния автомата либо устанавливать на его выходах код состояния автомата в новом введенном режиме.

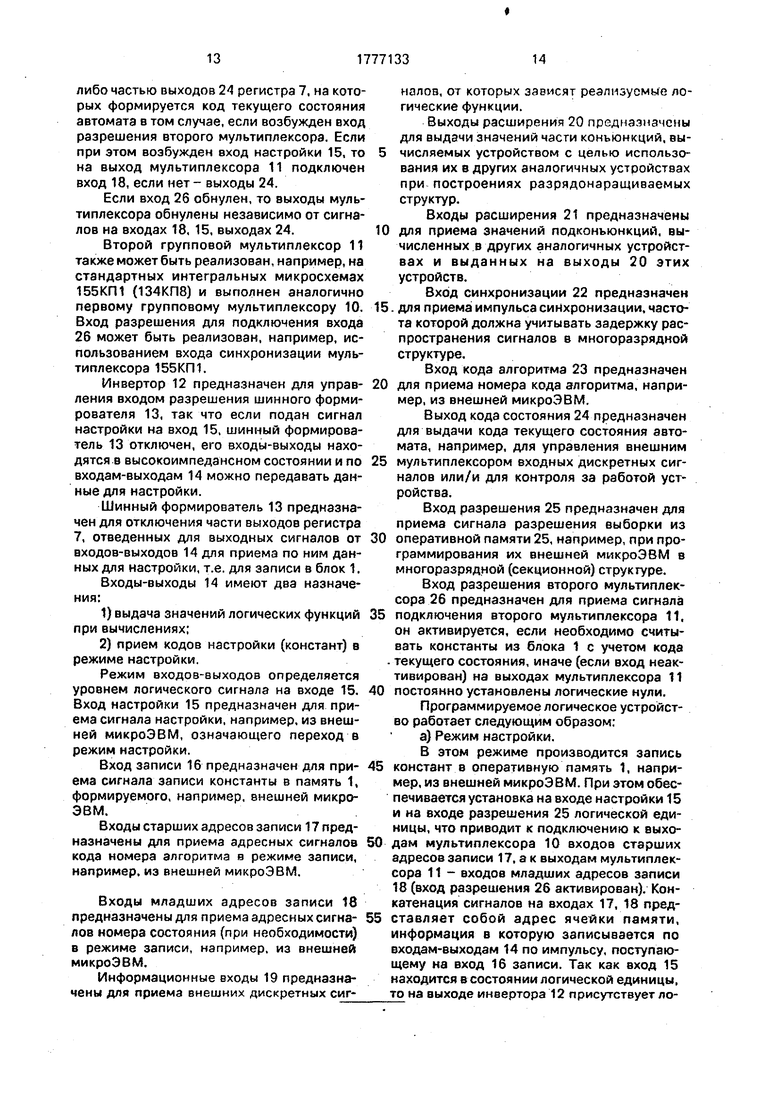

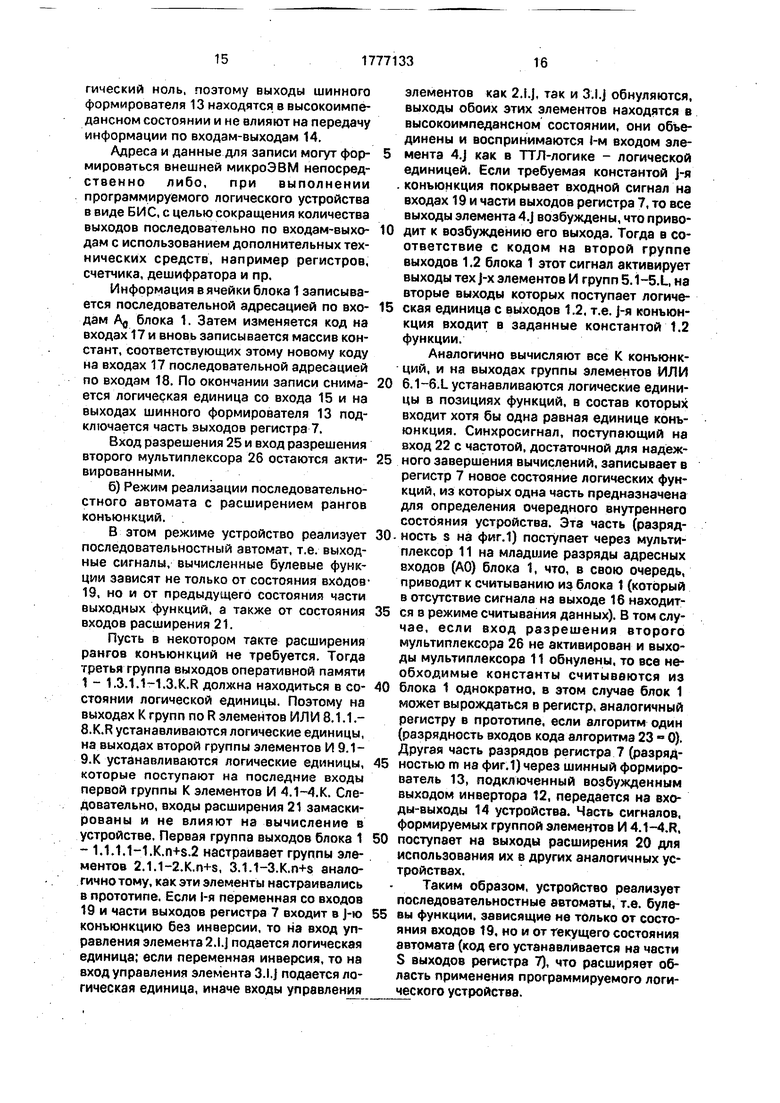

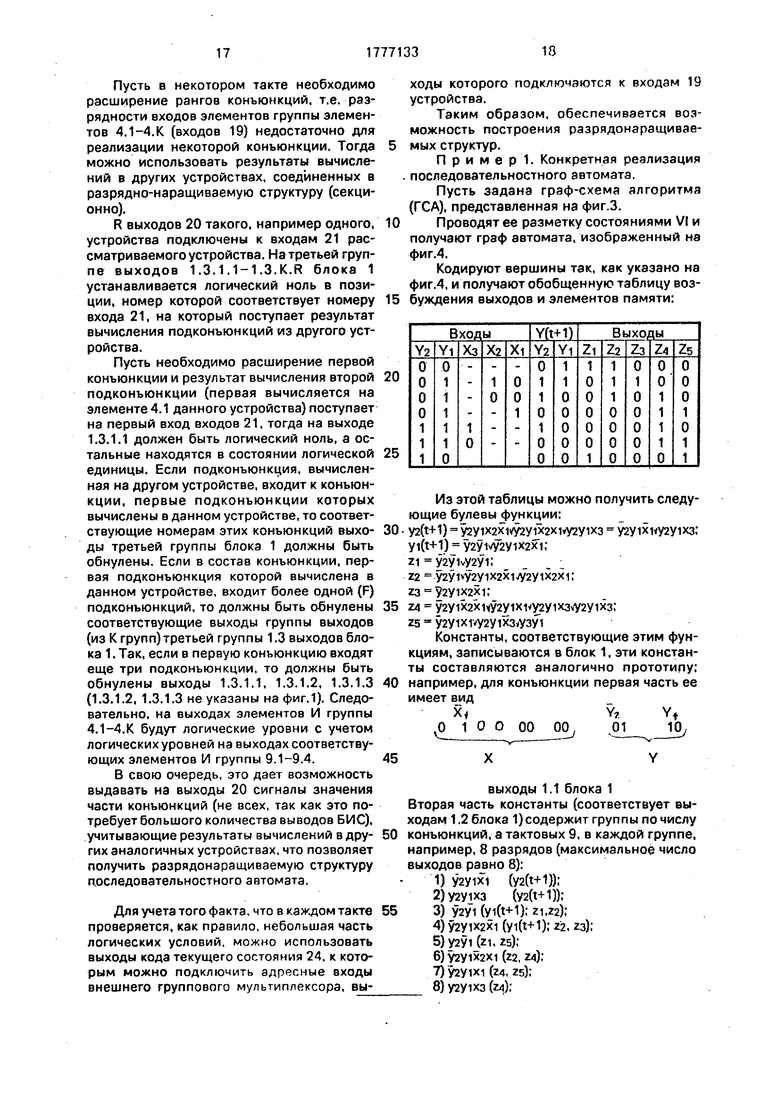

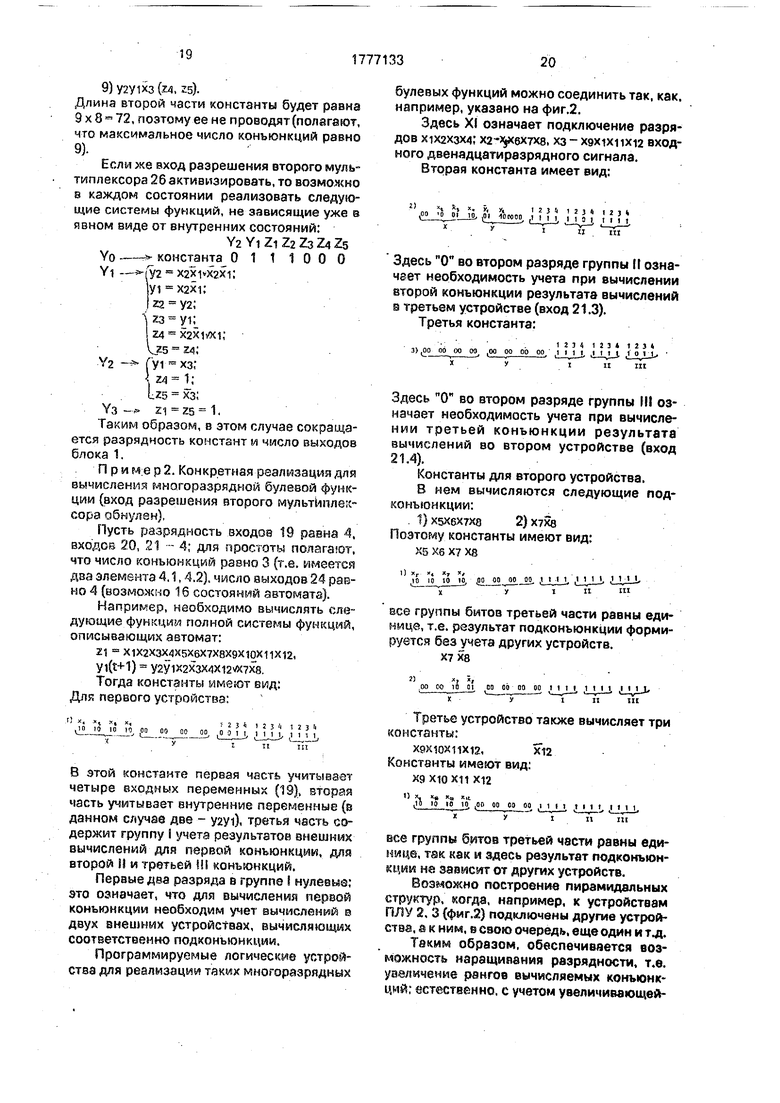

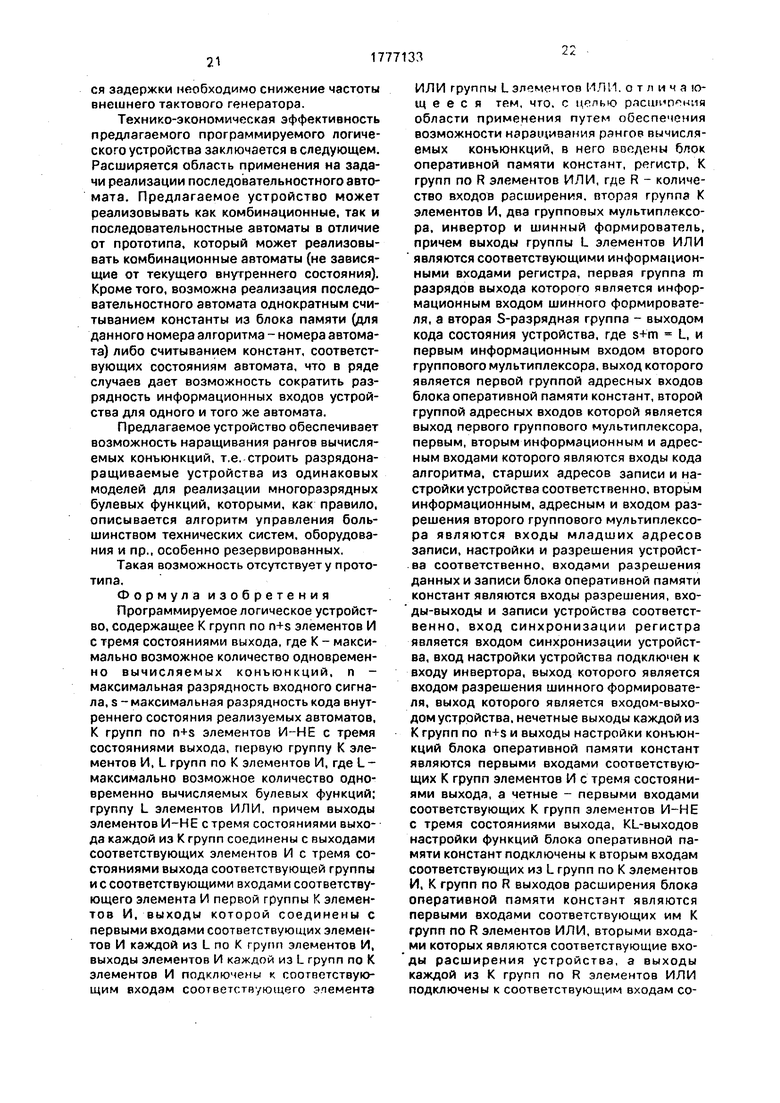

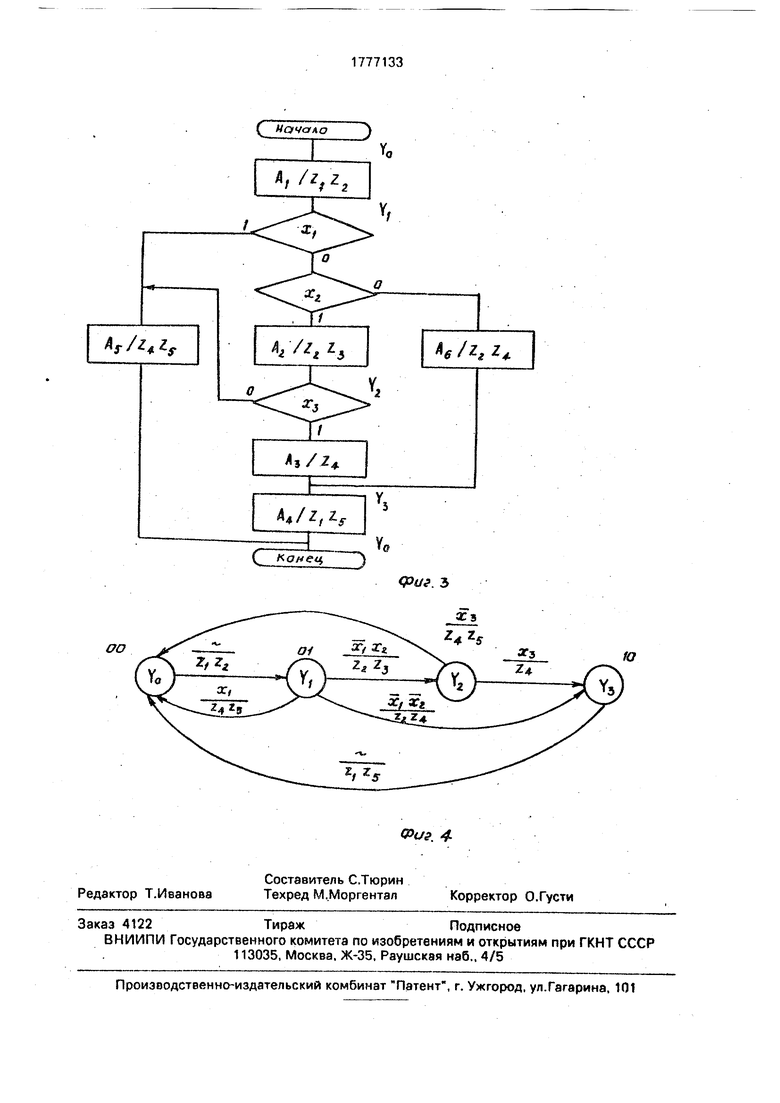

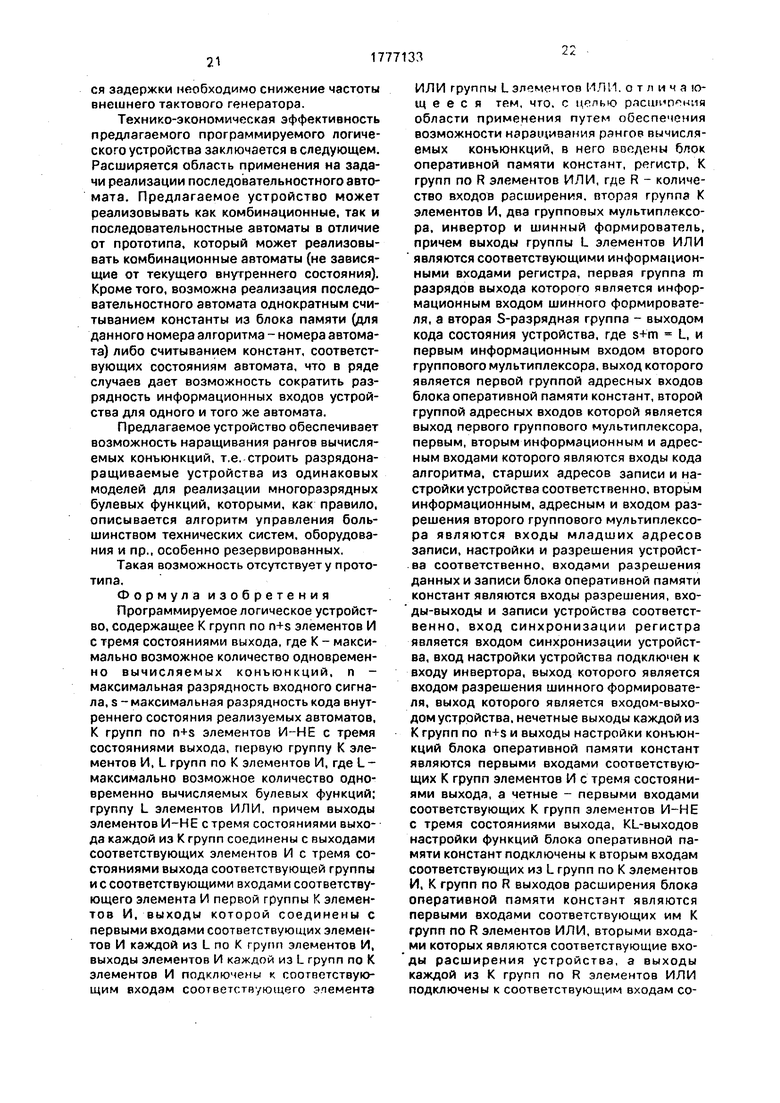

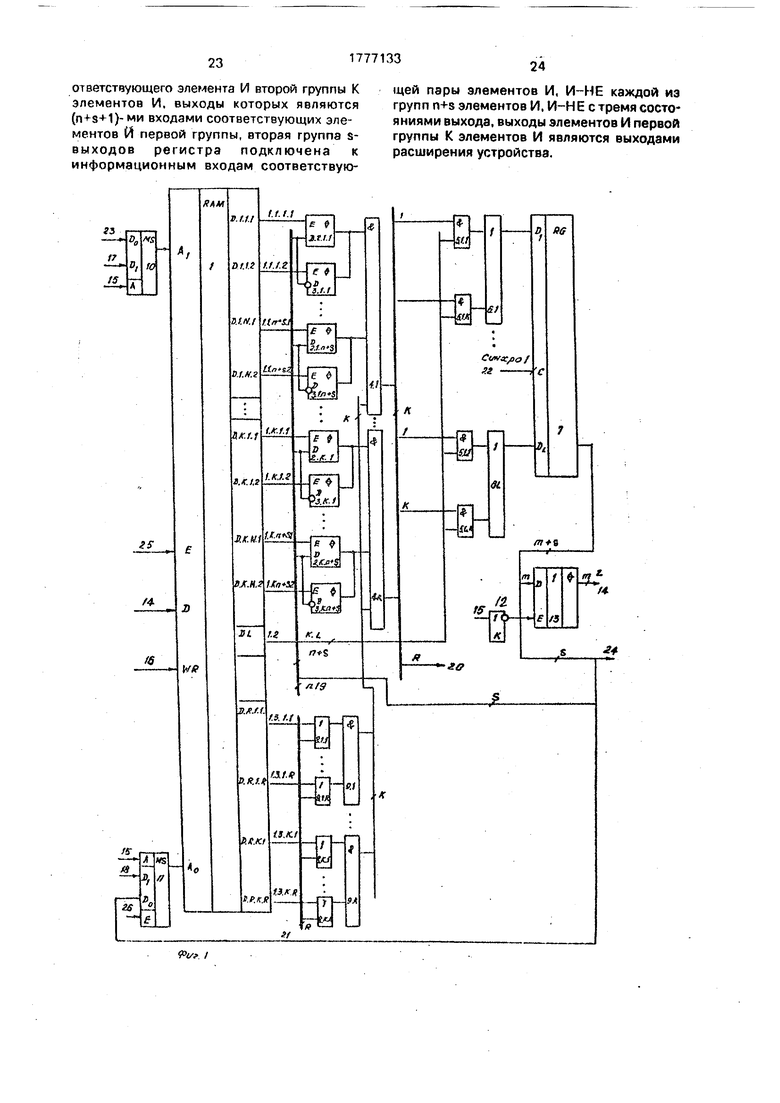

На фиг.1 изображена функциональная электрическая схема предлагаемого программируемого логического устройства; на фиг.2 - вариант соединения программируемых логических устройств для вычисления многоразрядных булевых функций; на фиг.З - граф-схема алгоритма для первого примера конкретной реализации последователь- постного автомата; на фиг.4 - граф автомата для первого примера конкретной реализации последовательностного автомата.

Программируемое логическое устройство содержит: блок оперативной памяти констант 1, К групп по n+s элементов И с тремя

состояниями на выходе 2.1.1-2.1. n+s

2,K.1-2,K.n+s, где К - максимально возможное количество одновременно вычисляемых

конъюнкций; s - максимальная разрядность кода внутреннего состояния реализуемых автоматов; п - максимальная разрядность входного сигнала; К групп по n+s элементов И-Н Ее тремя состояниями на выходе 3,1.10 3.1.n+s 3.K.1-3.K.n+s. первую группу К

элементов И 4.1-4. К, L групп по К элементов И 5.1.1-5.1.К..., 5.L.1-5.LK, где L - максимально возможное количество одновременно вычисляемых булевых функций, группу L

5 элементов ИЛИ 6.1-6.L, регистр 7, К групп

по R элементов ИЛИ 8.1.1-8.1.R8.К.1. 8.K.R, где R - количество входов расширения, вторую группу К элементов И 9.1-9.К, два групповых мультиплексора 10, 11, ин0 вертор 12, шинный формирователь 13, входы-выходы 14, вход настройки 15, вход записи 16, входы старших адресов записи 17, входы младших адресов записи 18, информационные входы 19, выходы расшире5 ния 20, входы расширения 21, вход синхронизации 22, входы кода алгоритма 23, выход кода состояния 24, вход разрешения 25, вход 26 разрешения второго группового мультиплексора.

0 Выходы элементов И-НЕ 3 с тремя состояниями выхода каждой из К групп соеди- нены с выходами соответствующих элементов И 2с тремя состояниями выхода соответствующей группы и с соответствую5 щими входами соответствующего элемента И первой группы К элементов И 4, выходы которой соединены с первыми входами соответствующих элементов И каждой из L по К групп элементов И 5. Выходы элементов И

0. каждой из L групп по К элементов И 5 подключены к соответствующим входам соответствующего элемента ИЛИ групп L элементов ИЛИ 6.

Выходы группы L элементов ИЛИ 6 яв5 ляются соответствующими информационными входами регистра 7, первая группа разрядов выхода которого является информационным входом шинного формирователя 13, а вторая S-разрядная группа 0 выходом 24 кода состояния устройства, где s+m - L, и первым информационным входом второго группового мультиплексора 11. выход которого является первой группой адресных входов блока оперативной памяти 1,

5 второй группой адресных входов которого является выход первого группового мультиплексора 10. первым, вторым информацион- ными и адресным входами которого являются вход 23 коде алгоритма, вход 17 старших адресов записи и вход 15 настройки устройства соответственно. Вторым информационным, адресным и входом разрешения второго группового мультиплексора 11 являются вход 18 младших адресов записи, вход 15 настройки и вход 26 разрешения устройства соответственно. Входами разрешения, данных и записи блока оперативной памяти 1 являются вход 25 разрешения, входы-выходы 14 и вход 16 записи устройства соответственно. Вход синхронизации реги- стра 7 является входом 22 синхронизации устройства. Вход 15 настройки устройства подключен к входу инвертора 12, выход ко- торого является входом разрешения шинного формирователя 13, выход которого является входом-выходом 14 устройства. Нечетные выходы каждой из К групп по n+s выходов настройки конъюнкций первой группы выходов блока оперативной памяти 1 являются первыми входами соответствую- щих К групп элементов И 2 с тремя состояниями выхода, а четные - первыми входами соответствующих К групп элементов И-НЕ 3 с тремя состояниями выхода. К L выходов настройки функций блока оперативной па- мяти 1 подключены к вторым входам соответствующих из L групп по К элементов И 5, К групп по R выходов расширения блока оперативной памяти являются первыми входами соответствующих из К групп по R элементов ИЛИ 8, вторыми входами которых являются соответствующие входы 21 расширения устройства, а выходы каждой из К групп по R элементов ИЛИ 8 подключены к соответствующим входам соответству- ющего элемента И второй группы элементов И 9, выходы которых являются (п+з+1)-ми входами соответствующих элементов И 4 первой группы.

Вторая группа s выходов регистра 7 в конкатенации с входными п-разрядными сигналами 19 является входным (n+sj-раз- рядным дискретным сигналом, который подключен к информационным входам соответствующей пары элементов И, И-НЕ каждой из К групп n+s элементов И 2, И-НЕ 3 с тремя состояниями выхода. Выходы элементов И первой группы К элементов И 4 являются выходами 20 расширения устройства.

Блок оперативной памяти 1 предназначен для записи, хранения и выдачи констант. Выходы настройки конъюнкций блока 1: 1.1.1.1.-1.K.n+s.2 имеют разрядность K.(n+s), где К - максимально возмож- нов количество одновременно выполняемых конъюнкций; п - максимальная разрядность информационных входов 19; s - максимальная разрядность кода нутреннего состояния.

Таким образом, имеется К подгрупп по n+s разрядов первой группы выходов. В каждой 1-й подгруппе пары сигналы имеют следующий смысл: 10 - необходимость учета прямого значения 1-й переменной; 01 - необходимость учета инверсного значения 1-й переменной; 00 - 1-я переменная не входит в конъюнкцию; 11 - запрещенное состояние.

Выходы настройки функции 1.2 опера- . тивной памяти 1 имеют разрядность K.L, где L- максимально возможное количество одновременно вычисляемых булевых функций (в том числе m - выходные сигналы, s - код состояния автомата). Она содержит единицы в тех из К позициях в L подгруппах, где соответствующие конъюнкции входят в соответствующие булевые функции. Выходы

расширения 1.3.1.1-1.3.1.R 1.3.К.11.3.K.R блока 1 имеют разрядность K.R. где R - количество входов расширения, и нули содержатся в тех из R позициях из К подгрупп, где соответствующие входы расширения необходимы при вычислениях соответствующих конъюнкций.

Оперативная память 1 адресуется по двумя группам адресных входов; первая группа адресных входов АО необходима при реализации последовательностного автомата системами функций, декомпозированными по состояниям автомата. В этом случае на выходе мультиплексора 11 установлен код текущего состояния, а в режиме записи информация поступает со входов 18. При отсутствии необходимости такой декомпозиции входы мультиплексора находятся в нулевом состоянии. Вторая группа адресных входов А1 блока 1 необходима для учета номера реализуемого алгоритма (номера автомата), причем при записи на эти входы передается информация со входов 17, а в режиме вычислений - со входов 23.

Данные в оперативную память 1 записываются со входов-выходов 14, если активированы вход разрешения 25 и вход записи 16.

Если вход записи 16 не активирован, а вход разрешения активирован, то блок 1 находится в режиме считывания информации.

Оперативная память 1 может быть реализована, например, на нескольких стандартных интегральных микросхемах 541РУ2.

К групп по n+s элементов И с тремя состояниями на выходе 2.1.1-2.n+s. 1, .... 3.K.1-2.K.n-s предназначены для подключения на свои выходы по разрешающему сигналу прямого (неинверсного) значения переменной, что необходимо, если она входит в соответствующую конъюнкцию без инверсии. Если вход разрешения неактивирован, то выходы элементов И находятся в высокоимпедэнсном состоянии и не влияют на передачу информации соответствующими элементами И-НЕ группы 3.

Элементы И группы 2 могут быть реализованы, например, на стандартных интегральных микросхемах 589АП16, причем информационный вход сопоставляется с двумя входами элемента И, объединенными вместе, и изображен на фиг.1 как единственный вход D. К групп по n+s элементов И-НЕ с тремя состояниями на выходе 3.1.13.n+s.13.K.1-3.K,n+s предназначены для

подключения по разрешающему сигналу на свои выходы инверсного значения переменной, что необходимо, если она входит в соответствующую конъюнкцию с инверсной. Если вход разрешения неактивирован, то выходы элементов И-НЕ находятся в высо- коимпедансном состоянии и не влияют на передачу информации соответствующими элементами И группы 2.

Элементы И-НЕ группы 3 могут быть реализованы, например, на стандартных интегральных микросхемах 589АЛ26, причем информационный вход сопоставляется с двумя входами элемента И, объединенными вместе, и изображен на фиг.1 как единственный вход D.

Первая группа К элементов И 4.1-4.К предназначена для вычисления К конъюнкций, причем выход каждого элемента И группы возбуждается в том случае, если выходы всех пар элементов групп 2, 3 активированы, что бывает в случае, если требуемые переменные входят в конъюнкцию с требуемым показателем инверсиро- вания либо если переменная вообще не входит в конъюнкцию: в этом случае выходы обоих элементов данной пары групп 2, 3 находятся в высокоимпедансном состоянии, выходы их объединены и это воспринимается соответствующим входом элемента И группы 4 как ТТЛ-логике - логической единицей.

L групп по К элементов И 5.1.1-5.1.К,.... 5.L.1-5.L.K предназначены для учета значений требуемых конъюнкций, определяемых константой на второй группе выходов 1.2 блока 1 таким образом, что если в соответствующем разряде данной константы присутствует логическая единица,, то учитывается значение соответствующей конъюнкции при формировании данной функции (в данную функцию входит соответствующая конъюнкция). Количество групп элементов равно количеству реализуемых булевых функций.

Группа L элементов ИЛИ 6.1-6.L предназначена для формирования значения логических функций, которые равны единице, если на выходе хотя бы одного элемента И

соответствующей группы групп элементов И 5 присутствует логическая единица, т.е элементы ИЛИ 6 формируют значение логической функции, заданной в дизъюнктивной нормальной форме (ДНФ).

0 Регистр 7 предназначен для записи по синхросигналу на входе 22 значений логических функций, формируемых группой элементов ИЛИ 6. Он может быть реализован, например, на стандартных интегральных

5. микросхемах 155ТР13.

Кгрупп по Rэлементов ИЛИ 8.1.1-8.1. R, ..., 8.K.1-8.K.R предназначены для учета значений сигналов на входах расширения при формировании значений К конъюнкций,

0 причем учитываются значения на тех входах расширения, которым соответствуют выходы третьей группы выходов оперативной памяти 1, находящиеся в состоянии логического нуля, иначе происходит маски5 рование данного входа расширения для данной конъюнкции.

Вторая группа К элементов И 9.1-9.К предназначена для вычисления значения внешних подконъюнкций, которые поступа0 ют на входы расширения 21 из других программируемых логических устройств, значения внешних подконъюнкций затем учитываются при вычислении всей подконъюнкций в данном устройстве на группе эле5 ментов И 4.

Первый групповой мультиплексор 10

предназначен для адресации второй группы

. адресных входов А1 оперативной памяти 1

либо входами старших адресов записи 17

0 при настройке, либо входами кода алгоритма 23 при вычислениях (в этом случае вход настройки 16 обнулен) и может быть реализован, например, на стандартных интегральных микросхемах 155КП1.

5 Групповой мультиплексор 10 представляет собой совокупность мультиплексоров, у которых все одноименные адресные входы объединены между собой, а одноименные входы различных мультиплексоров подклю0 чены к различным разрядам входов старших адресов записи (DO и входов D0 - входов номера алгоритма (используются два входа каналов во всех мультиплексорах).

С целью уменьшения количества обору5 дования желательна реализация на интегральных микросхемах 134КП8.

Второй групповой мультиплексор 11 предназначен для адресации первой группы адресных входов АО оперативной памяти 1 либо входами младших адресов записи 18,

либо частью выходов 24 регистра 7, на которых формируется код текущего состояния автомата в том случае, если возбужден вход разрешения второго мультиплексора. Если при этом возбужден вход настройки 15, то на выход мультиплексора 11 подключен вход 18, если нет - выходы 24.

Если вход 26 обнулен, то выходы мультиплексора обнулены независимо от сигналов на входах 18, 15, выходах 24.

Второй групповой мультиплексор 11 также может быть реализован, например, на стандартных интегральных микросхемах 155КП1 (134КП8) и выполнен аналогично первому групповому мультиплексору 10. Вход разрешения для подключения входа 26 может быть реализован, например, использованием входа синхронизации мультиплексора 155КП1.

Инвертор 12 предназначен для управления входом разрешения шинного формирователя 13, так что если подан сигнал настройки на вход 15, шинный формирователь 13 отключен, его входы-выходы находятся в высокоимпедансном состоянии и по входам-выходам 14 можно передавать данные для настройки.

Шинный формирователь 13 предназначен для отключения части выходов регистра 7, отведенных для выходных сигналов от входов-выходов 14 для приема по ним данных для настройки, т.е. для записи в блок 1.

Входы-выходы 14 имеют два назначения:

1)выдача значений логических функций при вычислениях;

2)прием кодов настройки (констант) в режиме настройки.

Режим входов-выходов определяется уровнем логического сигнала на входе 15. Вход настройки 15 предназначен для приема сигнала настройки, например, из внешней микроЭВМ, означающего переход в режим настройки.

Вход записи 16 предназначен для приема сигнала записи константы в память 1, формируемого, например, внешней микро- ЭВМ.

Входы старших адресов записи 17 предназначены для приема адресных сигналов кода номера алгоритма в режиме записи, например, из внешней микроЭВМ.

Входы младших адресов записи 18 предназначены для приема адресных сигналов номера состояния (при необходимости) в режиме записи, например, из внешней микроЭВМ.

Информационные входы 19 предназначены для приема внешних дискретных сигналов, от которых зависят реализуемые логические функции.

Выходы расширения 20 предназначены для выдачи значений части конъюнкций, вы- 5 числяемых устройством с целью использования их в других аналогичных устройствах при построениях разрядонаращиваемых структур.

Входы расширения 21 предназначены 10 для приема значений подконъюнкций. вычисленных в других аналогичных устройствах и выданных на выходы 20 этих устройств.

Вход синхронизации 22 предназначен 5. для приема импульса синхронизации, частота которой должна учитывать задержку распространения сигналов в многоразрядной структуре.

Вход кода алгоритма 23 предназначен 0 для приема номера кода алгоритма, например, из внешней микроЭВМ.

Выход кода состояния 24 предназначен для выдачи кода текущего состояния автомата, например, для управления внешним 5 мультиплексором входных дискретных сигналов или/и для контроля за работой устройства.

Вход разрешения 25 предназначен для приема сигнала разрешения выборки из 0 оперативной памяти 25, например, при программирования их внешней микроЭВМ в многоразрядной (секционной) структуре.

Вход разрешения второго мультиплексора 26 предназначен для приема сигнала 5 подключения второго мультиплексора 11. он активируется, если необходимо считывать константы из блока 1 с учетом кода . текущего состояния, иначе (если вход неактивирован) на выходах мультиплексора 11 0 постоянно установлены логические нули.

Программируемое логическое устройство работает следующим образом:

а) Режим настройки.

В этом режиме производится запись 5 констант в оперативную память 1, например, из внешней микроЭВМ. При этом обеспечивается установка на входе настройки 15 и на входе разрешения 25 логической единицы, что приводит к подключению к выхо- 0 дам мультиплексора 10 входов старших адресов записи 17, а к выходам мультиплексора 11 - входов младших адресов записи 18 (вход разрешения 26 активирован). Конкатенация сигналов на входах 17, 18 пред- 5 ставляет собой адрес ячейки памяти, информация в которую записывается по входам-выходам 14 по импульсу, поступающему на вход 16 записи. Так как вход 15 находится в состоянии логической единицы, то на выходе инвертора 12 присутствует логический ноль, поэтому выходы шинного формирователя 13 находятся в высокоимпе- дансном состоянии и не влияют на передачу информации по входам-выходам 14.

Адреса и данные для записи могут формироваться внешней микроЭВМ непосредственно либо, при выполнении программируемого логического устройства в виде БИС, с целью сокращения количества выходов последовательно по входам-выходам с использованием дополнительных технических средств, например регистров, счетчика, дешифратора и пр.

Информация в ячейки блока 1 записывается последовательной адресацией по входам А0 блока 1. Затем изменяется код на входах 17 и вновь записывается массив констант, соответствующих этому новому коду на входах 17 последовательной адресацией по входам 18. По окончании записи снимается логическая единица со входа 15 и на выходах шинного формирователя 13 подключается часть выходов регистра 7.

Вход разрешения 25 и вход разрешения второго мультиплексора 26 остаются активированными.

б) Режим реализации последовательно- стного автомата с расширением рангов конъюнкций.

В этом режиме устройство реализует последовательностный автомат, т.е. выходные сигналы, вычисленные булевые функции зависят не только от состояния входов- 19, но и от предыдущего состояния части выходных функций, а также от состояния входов расширения 21.

Пусть в некотором такте расширения рангов конъюнкций не требуется. Тогда третья группа выходов оперативной памяти 1 - 1.3.1.1-1.3.K.R должна находиться в состоянии логической единицы. Поэтому на выходах К групп по R элементов ИЛИ 8.1.1,- 8.K.R устанавливаются логические единицы, на выходах второй группы элементов И 9.1- 9.К устанавливаются логические единицы, которые поступают на последние входы первой группы К элементов И 4.1-4.К. Следовательно, входы расширения 21 замаскированы и не влияют на вычисление в устройстве. Первая группа выходов блока 1 - 1.1.1.1-1.K,n+s.2 настраивает группы элементов 2.1.1-2.K,n+s, 3,1.1-3.K.n+s аналогично тому, как эти элементы настраивались в прототипе. Если 1-я переменная со входов 19 и части выходов регистра 7 входит в j-ю конъюнкцию без инверсии, то на вход управления элемента 2.l.j подается логическая единица; если переменная инверсия, то на вход управления элемента 3.I. подается логическая единица, иначе входы управления

элементов как 2.I.J, так и 3.I.J обнуляются, выходы обоих этих элементов находятся в высокоимпедансном состоянии, они объединены и воспринимаются 1-м входом элемента 4.J как в ТТЛ-логике - логической

единицей. Если требуемая константой -я

. конъюнкция покрывает входной сигнал на

входах 19 и части выходов регистра 7, то все

выходы элемента 4.J возбуждены, что приво0 дит к возбуждению его выхода. Тогда в соответствие с кодом на второй группе выходов 1.2 блока 1 этот сигнал активирует выходы тех J-x элементов И групп 5.1-5.L, на вторые выходы которых поступает логиче5 екая единица с выходов 1.2, т.е. j-я конъюнкция входит в заданные константой 1.2 функции.

Аналогично вычисляют все К конъюнкций, и на выходах группы элементов ИЛИ

0 6.1-6.L устанавливаются логические единицы в позициях функций, в состав которых входит хотя бы одна равная единице конъюнкция. Синхросигнал, поступающий на вход 22 с частотой, достаточной для надеж5 ного завершения вычислений, записывает в регистр 7 новое состояние логических функций, из которых одна часть предназначена для определения очередного внутреннего состояния устройства. Эта часть (разряд0- ность s на фиг.1) поступает через мультиплексор 11 на младшие разряды адресных входов (АО) блока 1, что, в свою очередь, приводит к считыванию из блока 1 (который в отсутствие сигнала на выходе 16 находит5 ся в режиме считывания данных). В том случае, если вход разрешения второго мультиплексора 26 не активирован и выходы мультиплексора 11 обнулены, то все необходимые константы считываются из

0 блока 1 однократно, в этом случае блок 1 может вырождаться в регистр, аналогичный регистру в прототипе, если алгоритм один (разрядность входов кода алгоритма 23 0). Другая часть разрядов регистра 7 (разряд5 ностью m на фиг.1) через шинный формирователь 13, подключенный возбужденным выходом инвертора 12, передается на входы-выходы 14 устройства. Часть сигналов, формируемых группой элементов И 4.1-4.R,

0 поступает на выходы расширения 20 для использования их в других аналогичных устройствах.

Таким образом, устройство реализует последовательностные автоматы, т.е. буле5 вы функции, зависящие не только от состояния входов 19, но и от текущего состояния автомата (код его устанавливается на части S выходов регистра 7), что расширяет область применения программируемого логического устройстве.

Пусть в некотором такте необходимо расширение рангов конъюнкций, т.е. разрядности входов элементов группы элементов А. 1-4. К (входов 19) недостаточно для реализации некоторой конъюнкции. Тогда можно использовать результаты вычислений в других устройствах, соединенных в разрядно-наращиваемую структуру (секци- онно).

R выходов 20 такого, например одного, устройства подключены к входам 21 рассматриваемого устройства. На третьей группе выходов 1.3.1.1-1.3.K.R блока 1 устанавливается логический ноль в позиции, номер которой соответствует номеру входа 21, на который поступает результат вычисления подконьюнкций из другого устройства.

Пусть необходимо расширение первой конъюнкции и результат вычисления второй подконъюнкции (первая вычисляется на элементе 4.1 данного устройства) поступает на первый вход входов 21, тогда на выходе 1.3.1.1 должен быть логический ноль, а остальные находятся в состоянии логической единицы. Если подконъюнкция, вычисленная на другом устройстве, входит к конъюнкции, первые подконъюнкции которых вычислены в данном устройстве, то соответствующие номерам этих конъюнкций выхо- ды третьей группы блока 1 должны быть обнулены. Если в состав конъюнкции, первая подконъюнкция которой вычислена в данном устройстве, входит более одной (F) подконъюнкций, то должны быть обнулены соответствующие выходы группы выходов (из К групп) третьей группы 1.3 выходов блока 1. Так, если в первую конъюнкцию входят еще три подконъюнкции, то должны быть обнулены выходы 1.3.1.1. 1.3.1.2, 1.3.1.3 (1.3.1.2, 1.3.1.3 не указаны на фиг.1). Следовательно, на выходах элементов И группы 4.1-4.К будут логические уровни с учетом логических уровней на выходах соответствующих элементов И группы 9.1-9.4.

В свою очередь, это дает возможность выдавать на выходы 20 сигналы значения части конъюнкций (не всех, так как это потребует большого количества выводов БИС), учитывающие результаты вычислений в дру- гих аналогичных устройствах, что позволяет получить разрядонэращиваемую структуру п.оследовательностного автомата.

Для учета того факта, что в каждом такте проверяется, как правило, небольшая часть логических условий, можно использовать выходы кода текущего состояния 24, к которым можно подключить адресные входы внешнего группового мультиплексора, выходы которого подключаются к входам 19 устройства.

Таким образом, обеспечивается возможность построения разрядонарэщивае- мых структур.

П р и м е р 1. Конкретная реализация последовательностного автомата.

Пусть задана граф-схема алгоритма (ГСА), представленная на фиг.З.

Проводят ее разметку состояниями VI и получают граф автомата, изображенный на фиг.4.

Кодируют вершины так, как указано на фиг.4, и получают обобщенную таблицу возбуждения выходов и элементов памяти:

Из этой таблицы можно получить следующие булевы функции:

У2(1+1) yJ2yiX2X1Vy2yiX2X1 y2yiX3 У2У1ХЦУ2У1ХЗ,

yi(t+1) y2yivy 2V

Z1 У2УЬУ2У11

Z2 У2У1 У2У1Х2Хиу2У1Х2Х1;

23 У2У1Х2Х1,

Z4 y2yiX2X1iy2yiXvy2yiX3vy2yiX3;

Z5 У2У1Х1УУ2У1ХЗ УЗУ1

Константы, соответствующие этим функциям, записываются в блок 1, эти константы составляются аналогично прототипу; например, для конъюнкции первая часть ее имеет вид

.0 1 О О 00 00,0110,

С

X

выходы 1.1 блока 1

Вторая часть константы (соответствует выходам 1.2 блока 1) содержит группы по числу конъюнкций, а тактовых 9, в каждой группе, например, 8 разрядов (максимальное число выходов равно 8):

1) У2У1Х1 (y2(t+1));

2)у2У1хз (y2(t+1));

3)У2У1 (yi(t+1): 21.22);

4)У2У1Х2Х1 (yi(t+1); 22, 23);

5)У2У1(21, 25); 6)У2У1Х2Х1(22, 24); 7)У2У1Х1 (24,25);

8) у2У1хз (24):

9) У2У1ХЗ (Z4, 25).

Длина второй части константы будет равна 9 х 8 72, поэтому ее не проводят (полагают, что максимальное число конъюнкций равно

9).

Если же вход разрешения второго мультиплексора 26 активизировать, то возможно в каждом состоянии реализовать следующие системы функций, не зависящие уже в явном виде от внутренних состояний:

Y2YlZiZ2Z3Z4Z5

Yov константа 01 t 1000

Yl 2 Х2Х1 Х2Х1;

yi X2xi;

22 У2,

Z3 yi; Z4 x2Xivxi;

J-5 Z4.

fyi - хз;

Lz5 хз;

.

Таким образом, в этом случае сокращается разрядность констант и число выходов блока 1.

П р и м е р 2. Конкретная реализация для вычисления многоразрядной булевой функции {вход разрешения второго мультиплексора обнулен),

Пусть разрядность входов 19 равна 4, входов 20, 21 - 4; для простоты полагают, что число конъюнкций равно 3 (т.е. имеется два элемента 4.1, 4.2), число выходов 24 равно 4 (возможно 16 состояний автомата).

Например, необходимо вычислять следующие функции полной системы функций, описывающих автомат:

21 Х1Х2ХЗХ4Х5Х6Х7Х8Х9ХЮХ11Х12, yi(t+1) У2У1Х2ХЗХ4Х12 Х7Х8

Тогда константы имеют вид: Для первого устройства:

У2 Уз -

.10 10 10 10 00

-234 I 2 3 l 1 2 3 00 00ЈЈ, ,

У гипГ

В этой константе первая часть учитывает четыре входных переменных (19), вторая часть учитывает внутренние переменные (в данном случае две - yayi), третья часть содержит группу I учета результатов внешних вычислений для первой конъюнкции, для второй И и третьей III конъюнкций,

Первые два разряда в группе I нулевые; это означает, что для вычисления первой конъюнкции необходим учет вычислений в двух внешних устройствах, вычисляющих соответственно подконъюнкции.

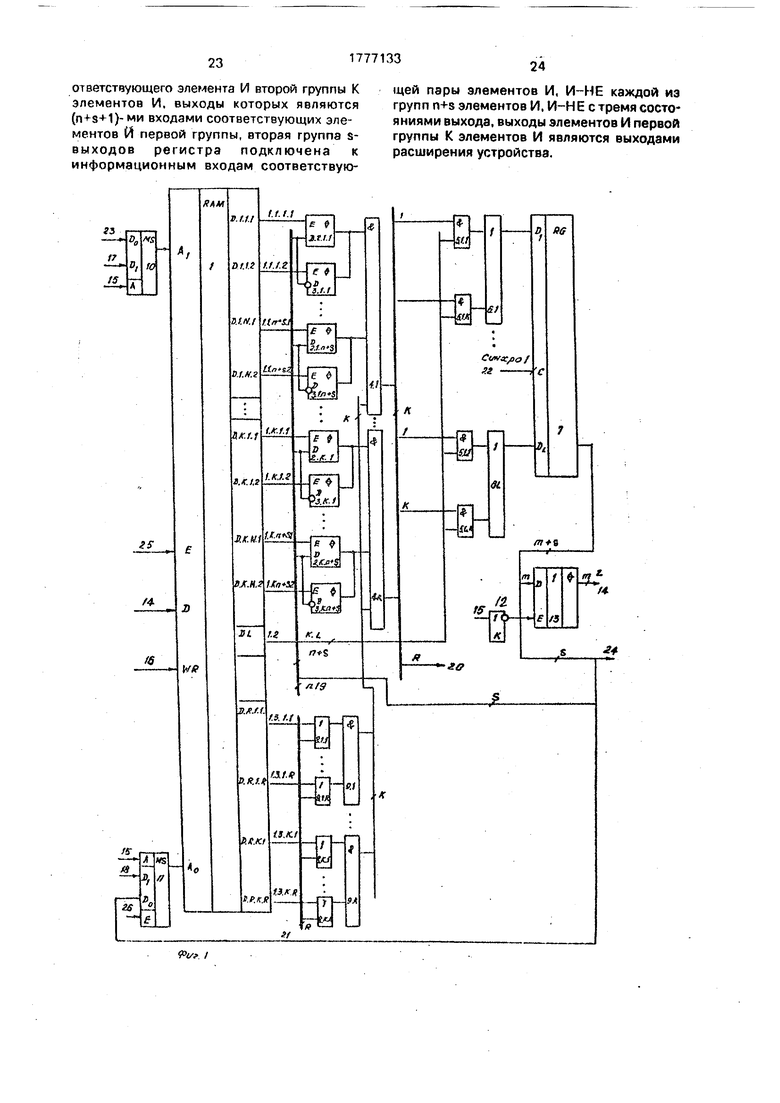

Программируемые логические устройства для реализации таких многоразрядных

булевых функций можно соединить так, как, например, указано на фиг.2.

Здесь XI означает подключение разрядов Х1Х2ХЗХ4, Х2-5$Х6Х7Х8, ХЗ - Х9Х1ХЦХ12 ВХОДНОГО двенадцатиразрядного сигнала.

Вторая константа имеет вид:

Здесь О во втором разряде группы II означает необходимость учета при вычислении второй конъюнкции результата вычислений э третьем устройстве (вход 21.3). Третья константа:

Здесь О во втором разряде группы III означает необходимость учета при вычислении третьей конъюнкции результата вычислений во втором устройстве (вход 21.4).

Константы для второго устройства.

В нем вычисляются следующие под- шныонкции:

1) Х5Х6Х7Х82) Х7Х8

Поэтому константы имеют вид:

Х5 Хб X Х8

11 5 „ И о Ј0 оо оо и. iJJJ, JJJJ. иД-Ь

1хТ i « га

все группы битов третьей части равны единице, т.е. результат подконъюнкции формируется без учета других устройств.

Х7Х8

х. ;,

10 01

00 00 00 00 lit

Третье устройство также вычисляет три

константы:

Х9ХЮХ11Х12,Х12

Константы имеют вид:

Х9Х10Х11Х12

х

ю

« «и

01J 00 00 00 1 | J til I, .Mil,

У IПIII

все группы битов третьей части равны единице, так как и здесь результат подконъюнкции не займет от других устройств.

Возможно построение пирамидальных структур, когда, например, к устройствам ПЛУ 2, 3 (фиг.2) подключены другие устройства, s к ним, в свою очередь, еще один и т л.

Таким образом, обеспечивается возможность наращивания разрядности, т.е. увеличение рангов вычисляемых конъюнкций: естественно, с учетом увеличивающейся задержки необходимо снижение частоты внешнего тактового генератора.

Технико-экономическая эффективность предлагаемого программируемого логического устройства заключается в следующем. Расширяется область применения на задачи реализации последовательностного автомата. Предлагаемое устройство может реализовывать как комбинационные, так и последовательностные автоматы в отличие от прототипа, который может реализовывать комбинационные автоматы (не зависящие от текущего внутреннего состояния). Кроме того, возможна реализация последовательностного автомата однократным считыванием константы из блока памяти (для данного номера алгоритма - номера автомата) либо считыванием констант, соответствующих состояниям автомата, что в ряде случаев дает возможность сократить разрядность информационных входов устройства для одного и того же автомата.

Предлагаемое устройство обеспечивает возможность наращивания рангов вычисляемых конъюнкций, т.е. строить разрядона- ращиваемые устройства из одинаковых моделей для реализации многоразрядных булевых функций, которыми, как правило, описывается алгоритм управления большинством технических систем, оборудования и пр., особенно резервированных,

Такая возможность отсутствует у прототипа.

Формула изобретения

Программируемое логическое устройство, содержащее К групп по n+s элементов И с тремя состояниями выхода, где К - максимально возможное количество одновременно вычисляемых конъюнкций, п - максимальная разрядность входного сигнала, s -максимальная разрядность кода внутреннего состояния реализуемых автоматов, К групп по n+s элементов И-НЕ с тремя состояниями выхода, первую группу К элементов И, L групп по К элементов И, где L- максимально возможное количество одновременно вычисляемых булевых функций; группу L элементов ИЛИ. причем выходы элементов И-НЕ с тремя состояниями выхода каждой из К групп соединены с выходами соответствующих элементов И с тремя состояниями выхода соответствующей группы и с соответствующими входами соответствующего элемента И первой группы К элементов И. выходы которой соединены с первыми входами соответствующих элементов И каждой из L по К групп элементов И, выходы элементов И каждой из L групп по К элементов И подключены к соответствующим входам соответствующего элемента

ИЛИ группы L элементов ИЛИ. о т л и ч а ю- щ е е с я тем, что. с целью расширения области применения путем обеспечения возможности наращивания рангов вычисляемых конъюнкций, в него воедены блок оперативной памяти констант, регистр, К групп по R элементов ИЛИ, где R - количество входов расширения, вторая группа К элементов И, два групповых мультиплексора, инвертор и шинный формирователь, причем выходы группы L элементов ИЛИ

являются соответствующими информационными входами регистра, первая группа m разрядов выхода которого является информационным входом шинного формирователя, а вторая S-разрядная группа - выходом кода состояния устройства, где s+m L, и первым информационным входом второго группового мультиплексора, выход которого является первой группой адресных входов блока оперативной памяти констант, второй группой адресных входов которой является выход первого группового мультиплексора, первым, вторым информационным и адресным входами которого являются входы кода алгоритма, старших адресов записи и настройки устройства соответственно, вторым информационным, адресным и входом разрешения второго группового мультиплексора являются входы младших адресов записи, настройки и разрешения устройства соответственно, входами разрешения данных и записи блока оперативной памяти констант являются входы разрешения, входы-выходы и записи устройства соответственно, вход синхронизации регистра является входом синхронизации устройства, вход настройки устройства подключен к входу инвертора, выход которого является входом разрешения шинного формирователя, выход которого является входом-выходом устройства, нечетные выходы каждой из К групп по n+s и выходы настройки конъюнкций блока оперативной памяти констант являются первыми входами соответствующих К групп элементов И с тремя состояниями выхода, а четные - первыми входами соответствующих К групп элементов И-НЕ с тремя состояниями выхода, KL-выходов настройки функций блока оперативной памяти констант подключены к вторым входам соответствующих из L групп по К элементов И, К групп по R выходов расширения блока оперативной памяти констант являются первыми входами соответствующих им К групп по R элементов ИЛИ, вторыми входами которых являются соответствующие входы расширения устройства, а выходы каждой из К групп по R элементов ИЛИ подключены к соответствующим входам соответствующего элемента И второй группы К элементов И, выходы которых являются (п+5-Н)-ми входами соответствующих элементов И первой группы, вторая группа s- выходов регистра подключена к информационным входам соответствующей пары элементов И, И-НЕ каждой из групп n+s элементов И. И-НЕ с тремя состояниями выхода, выходы элементов И первой группы К элементов И являются выходами расширения устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1751772A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА В МИКРОЭВМ ДИСКРЕТНЫХ СИГНАЛОВ | 1990 |

|

RU2007751C1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1688229A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2046396C1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1988 |

|

SU1608679A1 |

| Устройство для ввода-вывода дискретных сигналов микроЭВМ | 1989 |

|

SU1681306A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2049347C1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1786482A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1789975A1 |

Изобретение может быть использовано для вычисления систем булевых функций, описывающих как комбинационные, так и последовательностные автоматы, и позволяет наращивать ранги вычисляемых конъюнкций, что расширяет область применения устройства путем введения нового режима реализации последовательностного автомата. Устройство содержит блок оперативной памяти констант, К групп по n+s элементов И с тремя состояниями на выходе, где К - максимально возможное количество одновременно вычисляемых конъюнкций, п - максимальная разрядность входного сигнала, s - максимальная разрядность кода внутреннего состояния реализуемых автоматов, К групп по n+s элементов И-НЕ с тремя состояниями на выходе, первую группу К элементов И, L групп по К элементов И, где L- максимально возможное количество одновременно вычисляемых булевых функций, группу L элементов ИЛИ, регистр, К групп по R элементов ИЛИ, где R - количество входов расширения, вторую группу К элементов И, два групповых мультиплексора, инвертор, шинный формирователь, входы-выходы, вход настройки, вход записи, входы старших и младших адресов записи, информационные входы, выходы и входы расширения, вход синхронизации, входы кода алгоритма, выход кода состояния. 4 ил. (/) С

Фае. 2

{ Начало

Л, /z, z.

Z3

Л3/24

A4/Z,z,

С ко#еч }

00

6 /гг z

фиг Ъ

ХЗ

| Авторское свидетельство СССР Мг 1267964, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Программируемое логическое устройство | 1987 |

|

SU1444892A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-11-23—Публикация

1991-01-02—Подача