(П-2)-го и (n--l)-ro разрядов которого соединены с выходами элементов И одиннадцатой группы, первые входы которых соединены с выходом первого элемента И, выход второго элемента И соединен с первым входом третьего элемента И, выход которого соединен с входом h-ro раз. ряда регистра адр.еса микрокоманд, выходы элементов И восьмой и девятой групп соединены соответственно с первыми и вторыми входами соответ ствующих элементов ИЛИ третьей груп пы, выходы которых соединены с ад. ресными входами блока памяти, выход первого элемента И блока управления соединен с входом чтения-записи бло ка памяти, информационный вход и вы ход блока памяти соединены соответственно с выходом и информационным входом устройства, отличающийся тем, что, с целью сокращения аппаратурных затрат, каждьй многофункциональный модуль содержит два триггера, девять элементов И, пять элементов ИЛИ, причем в многофункциональном модуле вы ходы первого, второго и третьего элементов И соединены с соответствующими входами первого элемента ИЛИ, выход которого соединен с единичным входом первого триггера, прямой выход которого соединен с первым входом четвертого элемента выход пятого элемента И соединен с входом второго элемента ИЛИ, выход которого соединен с нулевым входом первого триггера, инверсный выход которого соединен с первьм входом шестого элемента И, выход которого и выход четвертого элемента И соеди нены соответственно с первьми вход ми третьего и четвертого элементов ИЛИ, второй вход четвертого эле мента ИЛИ соединен с выходом седьмо го элемента И, первый вход которого соединен с первыми входами первого, третьего и пятого элементов И, выхо ды четвертого и третьего элементов ИЛИ соединены соответственно с единичным и нулевым входами второго триггера, прямой и инверсный выходы которого соединены соответственно с первыми входами восьмого и девятого элементов И, выходы которых соединены соответственно с первым и вторым входами пятого элемента ИЛИ, вторые входы третьего и пятого элементов И объединены, третьи входы 44 третьего и пятого элементов И соединены соответственно с инверсньм и прямь1м выходами второго триггера, а также блок управления дополнительно содержит схему сравнения с нулем, два элемента ИЛИ, причем в блоке управления выход схемы сравнения с нулем соединен- с вторым входом третьего элеме нта И, выходы восьмого и девятого элементов И первой группы, выход второго элемента запрета группы соединены соответственно с первым, вторым и третьим входами первого элемента ИЛИ, выход пятого элемента: И первой группы и выход третьего элемента запрета группы соединены соответственно с первыми и вторым входами второго элемента ИЛИ, выходы первого, четвертого, пятого, восьмого и девято го элементов эапрета группы соединены соответственно с вторыми входами элементов И четвертой, девятой, восьмой, пятой и шестой групп, выходы третьего, шестого и седьмого элементов запрета группы соединены соответственно с первыми входами . элементов И седьмой группы, третьими входами элементов И третьей группы и счетным входом счетчика команд, выходы элементов И второй и четвертой групп соединены соответственно с третьими и четвёртыми входами соответствующих элементов ИЛИ третьей группы, выходы пятых элементов ИЛИ многофункциональных модулей соединены с соответствующими входами схемы сравнения с нулем и с вторыми входами соответствующих элементов И седьмой группы блока управления, выходы пятых эле|ментов ИЛИ двух старших многофункциональных модулей соединены с вторьми входами эли ентов И одиннадцатой группы блока управления, выход первого элемента ШШ которого соединен с входом разрешения блока памяти, выходы элем нтов И с первого по четвертый первой группы, выход второго элемента ШШ и выходы элементов И с шее- того по десятый первой группы блока управления соединены соответственно с вторыми входами четвертого элемента И, второго элемента ИЛИ, шесого элемента И, третьего элемента ИЛИ, седьмого элемента И, третьего элемента И, первым входом второго элемента И, вторыми входами восьмого элемента И, девятого элемента И и первого элемента И каждого многофункционального модуля, прямой выход второго триггера предьщущего многофункционального модуля соединен с вторым входом второго элемента И. последующего многофункционального

модуля, информационный вход устройства соединен с первыми входами первых элементов И многофункциональных модулей, выходы пятых элементов ИЛИ которых соединены с информационным входом блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления операцией записи | 1981 |

|

SU1003091A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Процессор с микропрограммным управлением | 1975 |

|

SU525956A1 |

| Устройство для выполнения команд реализации систем многоместных логических функций | 1981 |

|

SU999051A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство для табличной реализации многоместных логических функций | 1982 |

|

SU1019455A1 |

| Микро-ЭВМ | 1982 |

|

SU1124316A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для организации мультиветвления процессов в электронной вычислительной машине | 1980 |

|

SU922743A1 |

УНИВЕРСАЛЬНЫЙ ВЫЧИСЛИТЕЛЬНЫЙ АВТОМАТ, содержащий блок памяти, г многофункциональных модулей (п - разрядность операндов) и блок управления, содержащий регистр адреса микрокоманд, узел микропрограммной памяти, регистр микрокоманд, регистр команд, счетчик команд, группу элементов запрета, одиннадцать групп элементов И, . три элемента И, три группы элементов ИЛИ, причем в блоке управления выход узла микропрограммной памяти соединен с входом регистра микрокоманд, выход первого операционного поля которого соединен с первыми входами элементов И первой группы и первыми информационными входами элементов запрета группы, выход второго операционного поля регистра микрокоманд соединен с вторыми входами элементов И первой группы и .с управляющими входами элементов запрета группы, выходы третьего i операционного поля, четвертого опе рационного поля, первого и второго адресных полей регистра микрокоманд соединены соответственно с первым входом первого элемента И, первыми входами элементов И второй группы, первым входом второго элемента И и первыми входами элементов И третьей группы,третьи входы элементов И первой группы, вторые информационные входы элементов запрета группы, вторые входы первого и второго элементов И, вторые входы элементов И второй и третьей групп соединены , с первым тактовым входом автомата, выход счетчика команд соединен с первыми входами элементов И четвертой группы, выходы первого и второго полей адреса регистра коi манд соединены соответственно с первыми входами элементов И пятой (Л и шестой групп, выходы которых соединены соответственно с первыми и вторыми входами элементов ИЛИ первой группы, вьпсоды которых соединены с информационным входом, счетчика команд, выхода элементов И седьмой группьГ соединены с входом ср эо 4 регистра команд, выходы первого и второго полей адреса которого соединены соответственно с первыми входами элементов И восьмой и девятой tib групп, выход регистра адреса микрокоманд соединен с первыми входами элементов И десятой группы, вторые входы и выходы которых соединены соответственно с вторым тактовым входом автомата и .адресным входом узла микропрограммной памяти, выход операционного поля регистра команд и выходы элементов И третьей группы соединены через соответствующие элементы ИЛИ второй группы с входами разрядов с первого по (h-3) регистр адреса микрокоманд, входы

Изобретение относится к,автоматике и вычислительной технике и предназначено для реали:зации логических и арифметических операций и устройств.

Цель изобретения - сокращение ап1гаратурных затрат.

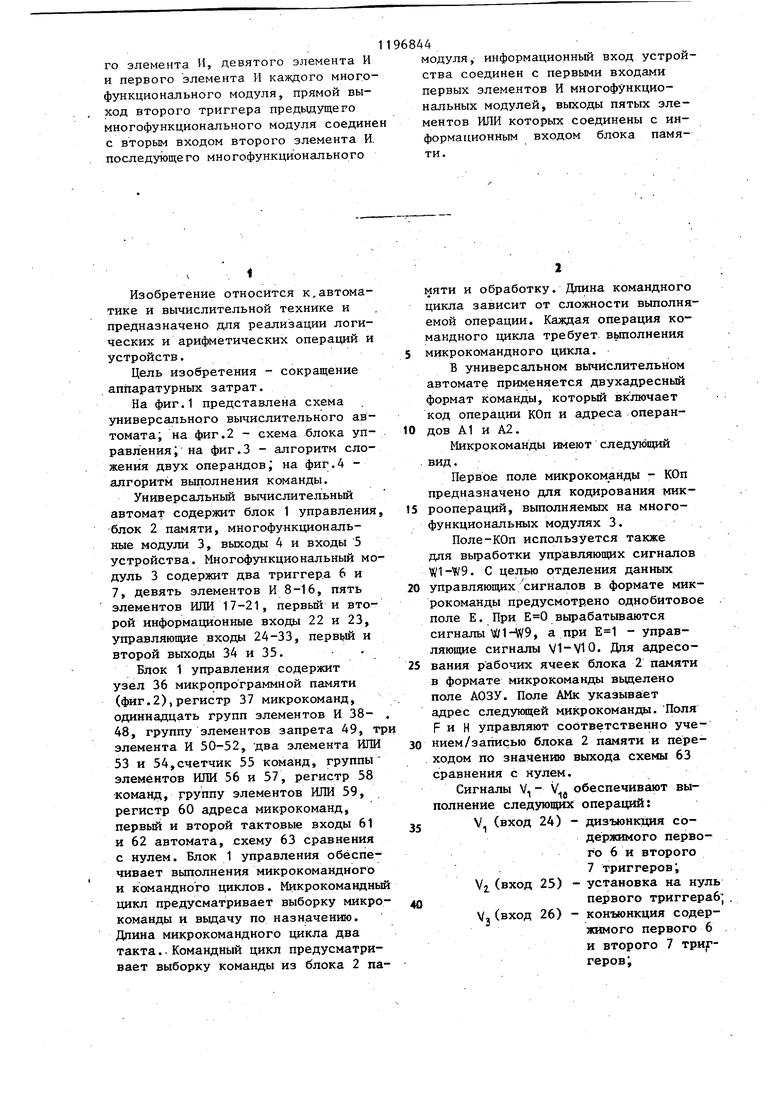

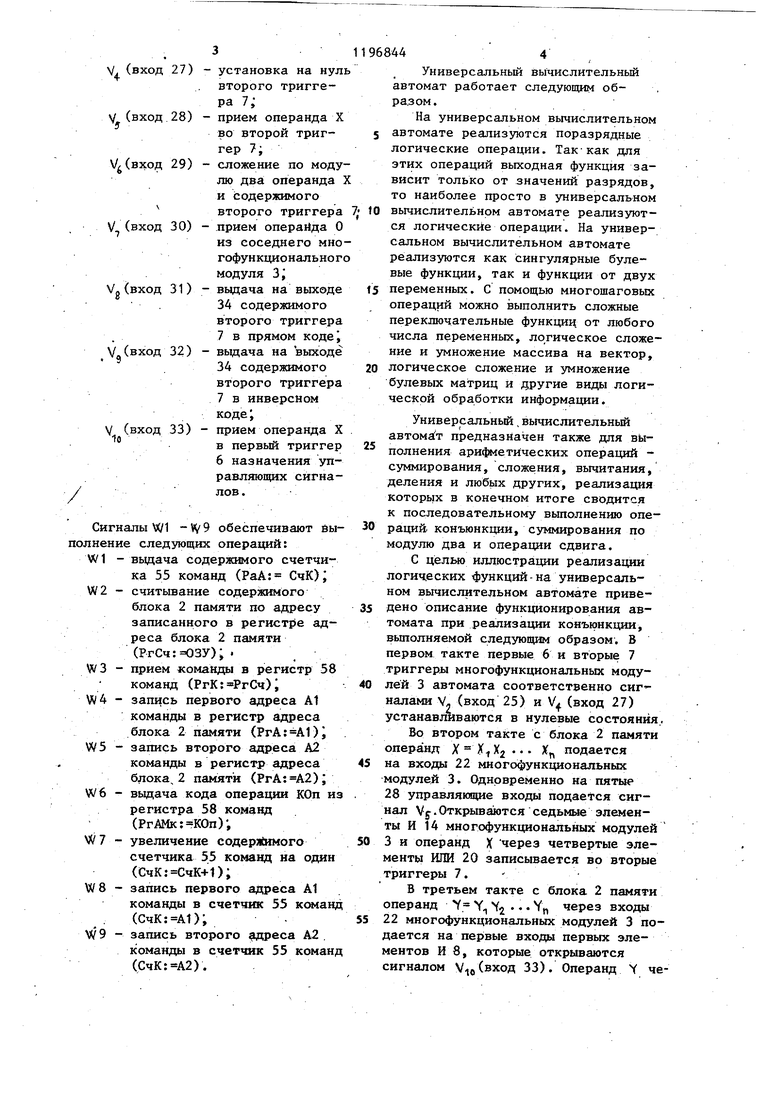

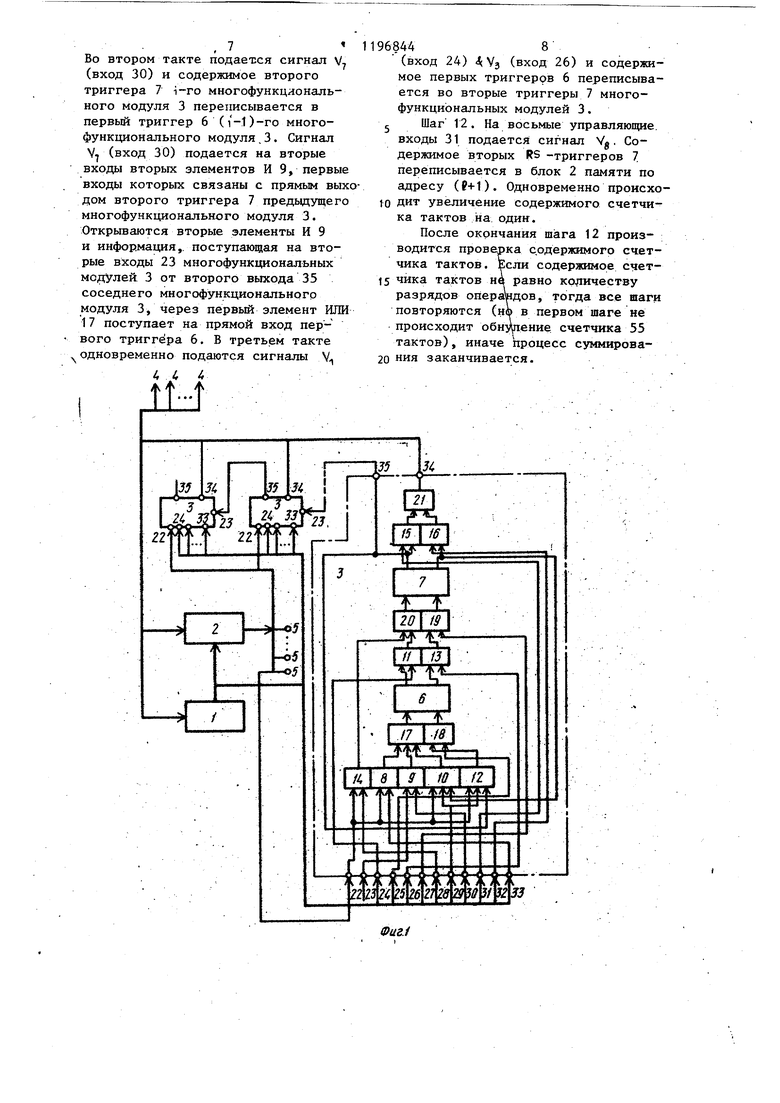

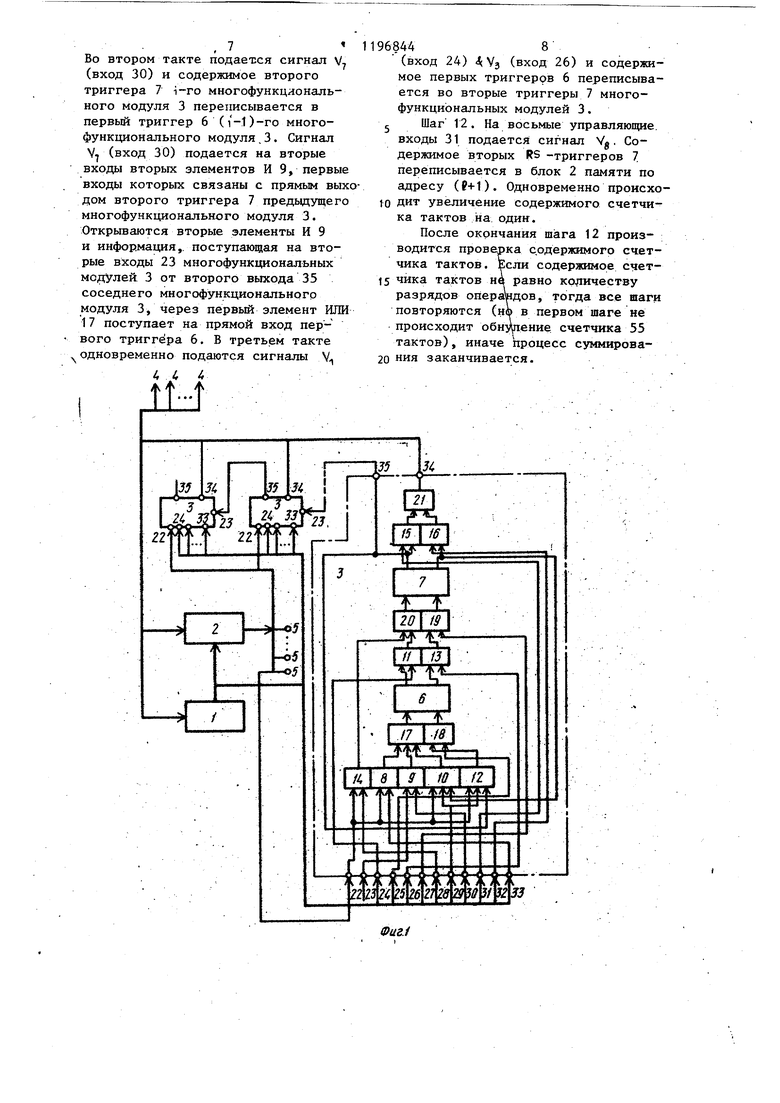

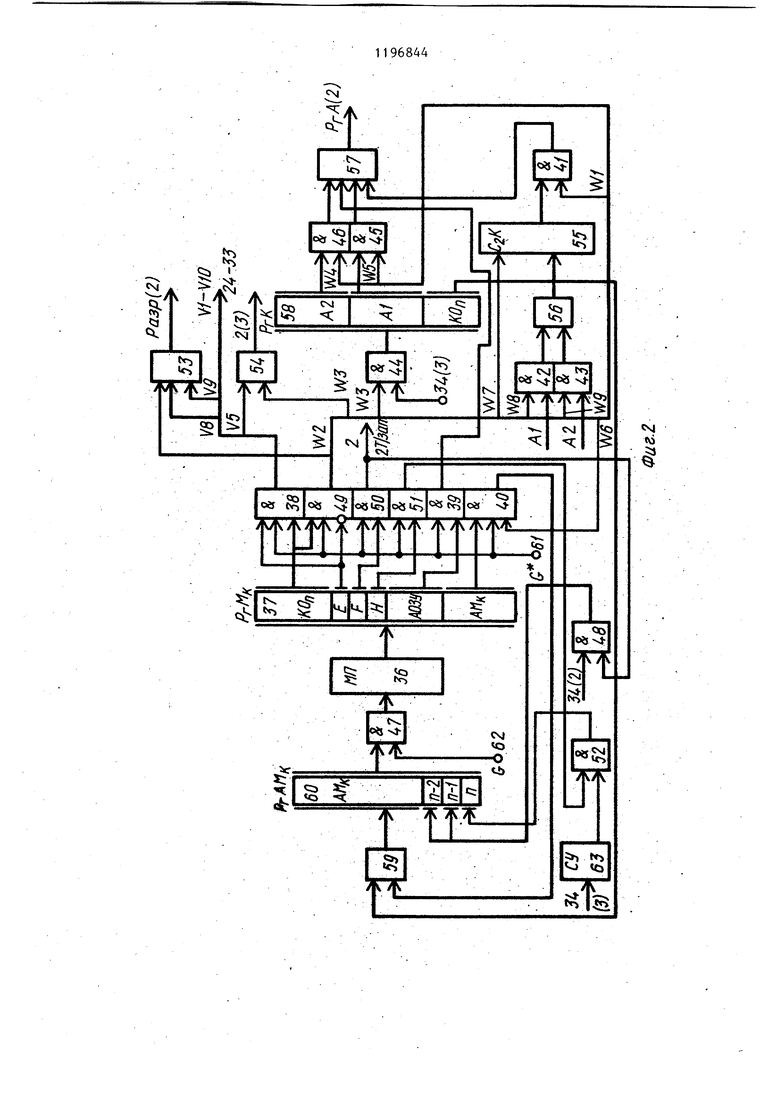

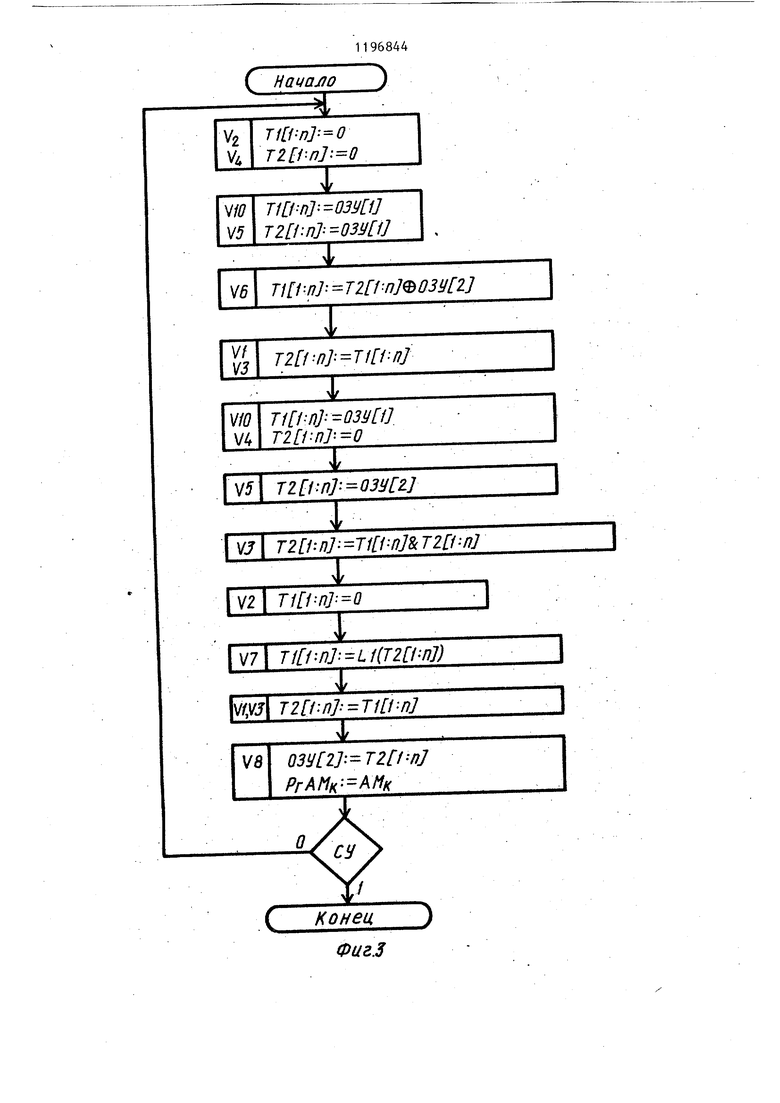

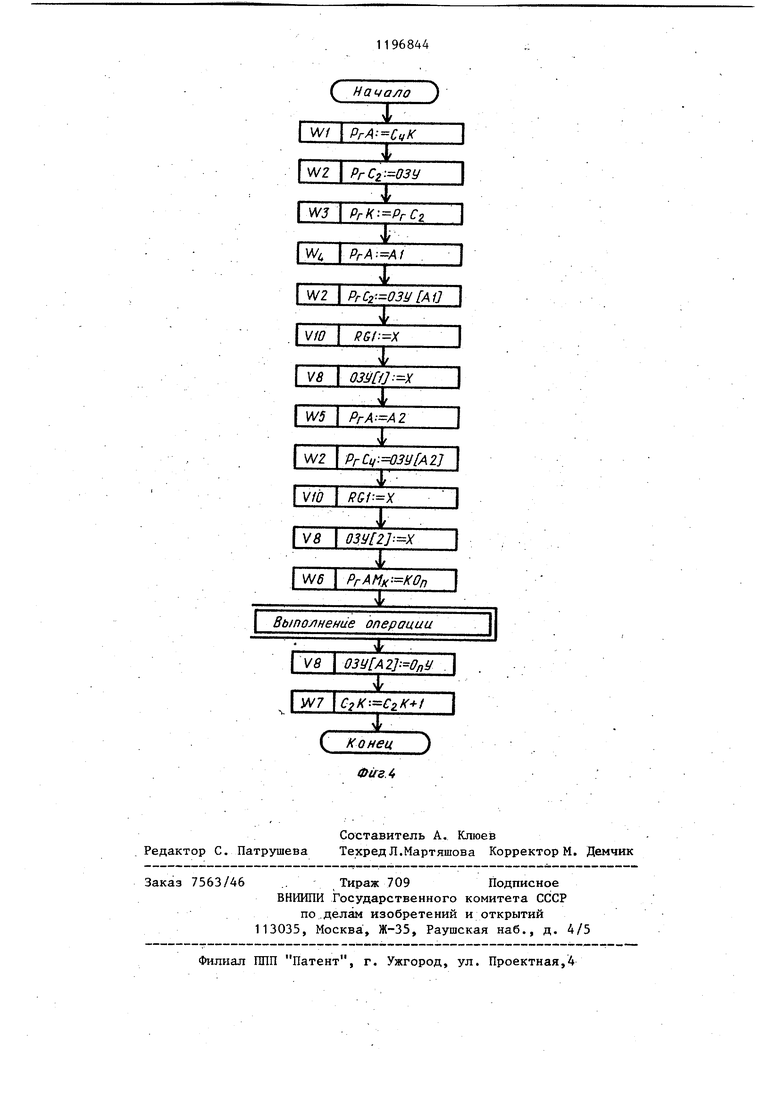

На фиг.1 представлена схема универсального вычислительного автомата; на фиг.2 - схема блока управления; на фиг.З - алгоритм сложения двух операндовj на фиг.4 алгоритм выполнения команды.

Универсальный вьшислительный автомат содержит блок 1 управления блок 2 памяти, многофункциональные модули 3, выходы 4 и входы 5 устройства. Многофункциональный модуль 3 содержит два триггера 6 и 7, девять элементов И 8-16, пять элементов ИЛИ 17-21, первый и второй информационные входы 22 и 23, управляющие входы 24-33, перв1 1й и второй выходы 34 и 35.

Блок 1 управления содержит узел 36 микропрограммной памяти (фиг.2), регистр 37 микрокоманд, одиннадцать групп элементов И 3848, группу элементов запрета 49, т элемента И 50-52, два элемента ИЛИ 53 и 54,счетчик 55 команд, группы элементов ИЛИ 56 и 57, регистр 58 команд, группу элементов ИЛИ 59, регистр 60 адреса микрокоманд, первый и второй тактовые входы 61 и 62 автомата, схему 63 сравнения с нулем. Блок 1 управления обеспечивает вьшолнения микрокомандного и командного циклов. Микрокомандны цикл предусматривает выборку микрокоманды и вьщачу по назначению. Длина микрокомандного цикла два такта.-Командньй цикл предусматривает выборку команды из блока 2 памяти и обработку. Длина командного цикла зависит от сложности выполняемой операции. Каждая операция командного цикла требует. В1,шолнения

микрокомандного цикла.

В универсальном вычислительном автомате применяется двухадресный формат команды, который включает код операции КОп и адреса операндов А1 и А2.

Микрокоманды имеют следунзщий вид.

Лервое поле микроком анды - КОп предназначено для кодирования микроопераций, выполняемых на многофункциональных модулях 3.

Поле-КОп используется также для выработки управляющих сигналов W1-W9. С целью отделения данных

управляющих сигналов в формате микрокоманды предусмотрено однобитовое поле Е. При вырабатываются сигналы M(/1-W9, а при - управляющие сигналы V1-V10. Для адресования рабочих ячеек блока 2 памяти в формате микрокоманды вьщелено поле АОЗУ. Поле АМк указывает адрес следующей микрокоманды. Поля F и Н управляют соответственно учением/записью блока 2 памяти и переходом по значению выхода схемы 63 сравнения с нулем.

Сигналы V, - V. обеспечивают вы1 1в

полнение следующих операций: V, (вход 24) - дизъюнкдая содержимого первого 6 и второго 7 триггеров;

Vj. (вход 25) - установка на нуль первого триггераб;

V-(вход 26) - конъюнкция содержимого первого 6 и второго 7 TPHJTгеров;J V(вход 27) установка на нул второго триггера 7; у, (вход. 28) прием операнда X во второй триггер 7; V(Bxofl 29) сложение по моду лю два операнда и содержимого второго триггера прием операнда О V (вход 30) из соседнего мно гофункциональног модуля 3; УО(ВХОД 31) выдача на выходе 34 содержимого второго триггера 7 в прямом коде Vg (вход 32) вьщача на вькоде 34 содержимого второго триггера 7 в инверсном коде; V (вход 33) прием операнда X fo в первый триггер 6 назначения управляющих сигна лов . Сигналы Wl -VV9 обеспечивают вы полнение следующих операций: W1 -выдача содержимого счетчика 55 команд (РаА: СчК) , W2 - считывание содержимого блока 2 памяти по адресу записанного в регистре адреса блока 2 памяти (РгСч: ОЗУ); . W3 - прием команды в регистр 58 команд ()i W4 - запись первого адреса А1 команды в регистр адреса блока 2 памяти () W5 - запись второго адреса А2 команды в регистр адреса блока, 2 памяти (); W6 - выдача кода операции КОп и регистра 58 команд (РгАМк: КОп); W 7 - увеличение содеря(имого счетчика 55 команд на один (СчК: СчК+1); W8 - запись первого адреса А1 команды в счетчик 55 коман (); . W9 - запись второго адреса А2 , команды в счетчик 55 коман (). 444 Универсальный вычислительный автомат работает следующим образом. На универсальном вычислительном автомате реализуются поразрядные логические операции. Таккак для этих операций выходная функция зависит только от значений разрядов, то наиболее просто в универсальном вычислительном автомате реализуются логические операции. На универсальном вычислительном автомате реализуются как сингулярные булевые функции, так и функции от двух переменных. С помощью многошаговых операций можно выполнить сложные переключательные функциц от любого числа переменных, логическое сложение и умножение массива на вектор, логическое сложение и умножение булевых матриц и другие виды логической обработки информации. Универсальный,вычислительный автома т предназначен также для выполнения ари етических операций суммирования, сложения, вычитания, деления и любых других, реализация которых в конечном итоге сводится к последовательному выполнению операций конъюнкции, суммирования по модулю два и операции сдвига. С целью иллюстрации реализации логических функций-на универсальном вычислительном автомате приведено описание функционирования автомата при реализации конъюнкции, вьтолняемой следующим образом. В первом такте первые 6 и вторые 7 триггеры многофункциональных модулей 3 автомата соответственно сигналами V, (вход 25) и V (вход 27) устанавливаются в нулевые состояния. Во втором такте с блока 2 памяти операнд X X Xj--- Х„ подается на входы 22 многофункциональных модулей 3. Одновременно на пятые 28 управляющие входы подается сигнал У.Открываются седьмые элементы И 14 многофункциональных модулей 3 и операнд через четвертые элементы ИЛИ 20 записывается во вторые триггеры 7. В третьем такте с блока 2 памяти операнд V Y Ч . Yf, через входы 22 многофункциональных Модулей 3 подается на перовые входы первых элементов И 8, которые открываются сигналом (вход, 33). Операнд Ч через первые элементы ИЛИ 17 заносится в первые триггеры 6 многофункциональных модулей 3.

Дпя осуществления операции конъюнкций подается сигнал у., (вход 26) и содержимое первых триггеров 6 d инверсных выходов через элементы И 11 и ИЛИ 20 переписывается во вторые триггеры 7. В результате во вторых триггерах 7 устанавливается логическое произведение Х(у

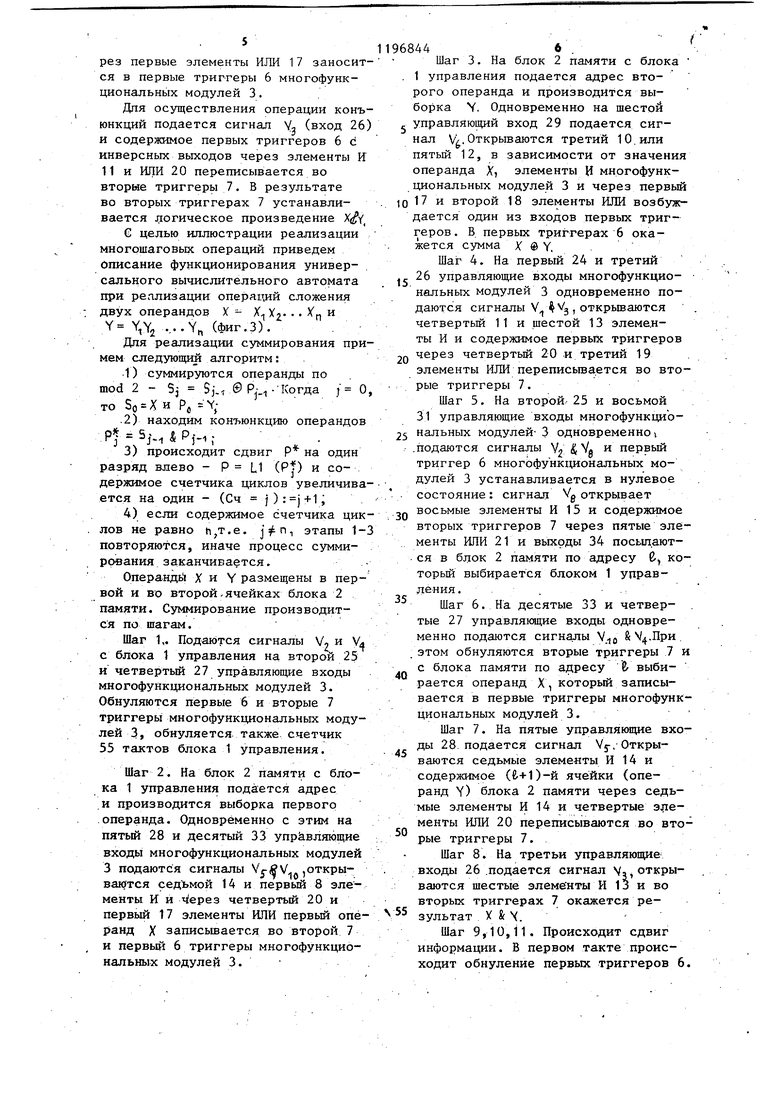

G целью иллюстрации реализации многошаговых операций приведем Описание функционирования универсального вычислительного автомата при реализации операций сложения двух операндов )( - Х Y Y.Yj ....Y, (фиг.З). .

Для реализации суммирования примем следующий алгоритм: .

1) суммируются операнды по mod 2 - Sj Sj., @ P-.i-Когда / О, то SO XH р ;

.2) находим конъюнкцию операндов

P

3)происходит сдвиг Р на один разряд влево - Р L1 (Рр и содержимое счетчика циклов увеличивается на один - (Сч j)

4)если содержимое счетчика циклов не равно я,т.е. (т этапы 1-3

повторяются, иначе процесс суммирования заканчивается.

Операндь X и Y размещены в первой и во второй-ячейках блока 2 памяти. Суммирование производится по шагам.

Шаг 1,. Подаются сигналы V, и V с блока 1 управления на второй 25 и четвертый 27 управляющие входы многофункциональных модулей 3. Обнуляются первые 6 и вторые 7 триггеры многофункциональных модулей 3, обнуляется также, счетчик 55 тактов блока 1 управления.

Шаг 2. На блок 2 памяти с блока 1 управления подается адрес и производится выборка первого операнда. Одновременно с этим на пятый 28 и десятый 33 управляющие входы многофункциональных модулей 3 подаются сигналы .. (Открываются седьмой 14 и первый 8 элементы И и четвертый 20 и первый 17 элементы ИЛИ первый операнд X записьшается во второй 7 и первый 6 триггеры многофункциональных модулей 3.

Г

Шаг 3. На блок 2 памяти с блока

. 1 управления подается адрес второго операнда и производится выборка . Одновременно на шестой управляющий вход 29 подается сигнал V. Открываются третий 10. или пятый 12, в зависимости от значения операнда X, элементы И многофункциональных модулей 3 и через первый -л второй 18 элементы ИЛИ возбуждается один из входов первых триггеров . В. первых триггерах 6 окажется сумма X ® Y.

Шаг 4. На первый 24 и третий 26 управляющие входы многофункциональных модулей 3 одновременно подаются сигналы V-Л YJ , открьшаются четвертый 11 и шестой 13 элеме.нты И и содержимое первых триггеров 2Q через четвертый 20 и третий 19

элементы ИЛИ переписьгеается во вторые триггеры 7.

Шаг 5. На второй 25 и восьмой 31 управляющие входы многофункциональных модулей- 3 одновременно .подаются сигналы Vo &V и первый триггер 6 многофункциональных модулей 3 устанавливается в нулевое . состояние: сигнал Vg открывает восьмые элементы И 15 и содержимое вторых триггеров 7 через пятые элементы ИЛИ 21 и выходы 34 посьш.ают.ся в блок 2 памяти по адресу В, который выбирается блоком 1 управления . . .

Шаг 6. На десятые 33 и четвер- . тые 27 управлякщие входы одновременно подаются сигналы V.j 6 У4.При . этом обнуляются вторые тр иггеры 7 и с блока памяти по адресу & выбирается операнд X, который записывается в пе:рвые триггеры многофункциональных модулей 3. Шаг 7. На пятые управляющие входы 28. подается сигнал Vy. Открываются седьмые элементы И 14 и содержимое (.+ 1)-й ячейки (операнд Y) блока 2 памяти через седьмые элементы И 14 и четвертые элементы ИЛИ 20 переписываются во вто50рые триггеры 7.

Шаг 8. На третьи управляющие входы 26 .подается сигнал /- открываются шестые элементы И 13 и во вторых триггерах 7 окажется результат X & Ч.

Шаг 9,10,11. Происходит сдвиг информации. В первом такте происходит обнуление первых триггеров 6. Во втором такте подается сигнал (вход 30) и содержимое второго триггера 7 i-ro многофункциональ ного модуля 3 переписывается в первый триггер 6 (i-1)-ro многоФункционального модуля.3. Сигнал V (вход 30) подается на вторые входы вторых элементов И 9, первы входы которых связаны с прямым вы дом второго триггера 7 предьщущег многофункционального модуля 3. Открьшаются вторые элементы И 9 и информация, поступающая на вторые входы 23 многофункциональных модулей 3 от второго выхода 35 соседнего многофункционального модуля 3, через первый элемент ИЛ 17 поступает на прямой вход первого триггера 6. В третьем такте одновременно подаются сигналы V 68448 (вход 24) «;Уз (вход 26) и содержимое первых триггеров 6 переписывается во вторые триггеры 7 многофункциональных модулей 3. 5 Шаг 12. На восьмые управляющие. входы 31 подается сигнал У«. Содержимое вторых RS -триггеров 7 переписывается в блок 2 памяти по адресу (Р+1). Одновременно происходит увеличение содержимого счетчика тактов на один. После окончания шага 12 производится проверка содержимого счетчика тактов. Если содержимое счетчика тактов не равно количеству разрядов операндов, тогда все шаги повторяются (но в первом шаге не происходит счетчика 55 тактов), иначе процесс суммирования заканчивается. У I/J-: J- J

Начало J

I Выполнение операции

i Уб I

I W7

С Конец )

| Устройство для реализации логических функций | 1981 |

|

SU1001080A1 |

| Универсальный вычислительный автомат | 1972 |

|

SU454547A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-12-07—Публикация

1983-12-02—Подача