ып

u-JT

6.1

ЈП j

1

t-s

/ i- к ;

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ локальной радиотелефонной связи и система для его осуществления | 1991 |

|

SU1831767A3 |

| Многоканальный формирователь одиночных импульсов | 1985 |

|

SU1243115A1 |

| Фазовый синхронизатор | 1987 |

|

SU1443147A1 |

| Одноканальное устройство для управления @ -фазным вентильным преобразователем | 1983 |

|

SU1320868A1 |

| Электронное музыкальное устройство | 1988 |

|

SU1793459A1 |

| Устройство для контроля газоразрядной индикаторной панели | 1983 |

|

SU1119067A1 |

| Устройство передачи сообщений | 1985 |

|

SU1506555A1 |

| Сенсорная панель | 1983 |

|

SU1192138A1 |

| Устройство для управления N - фазным импульсным преобразователем напряжения | 1989 |

|

SU1791925A1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

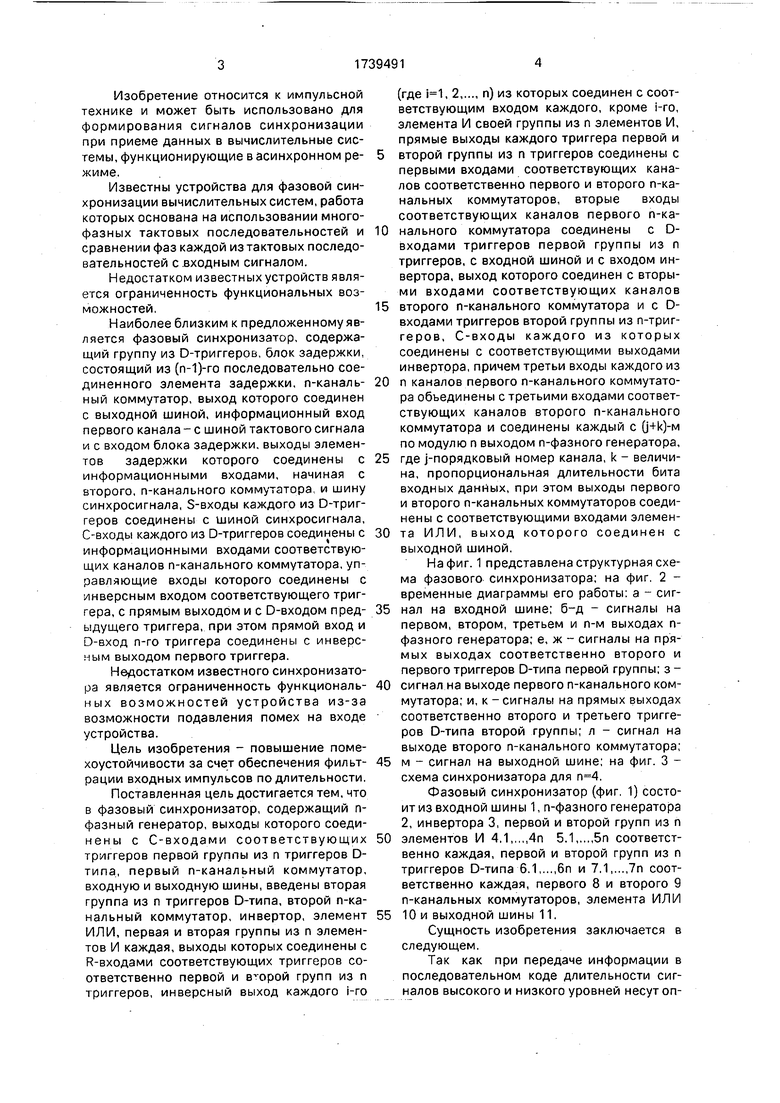

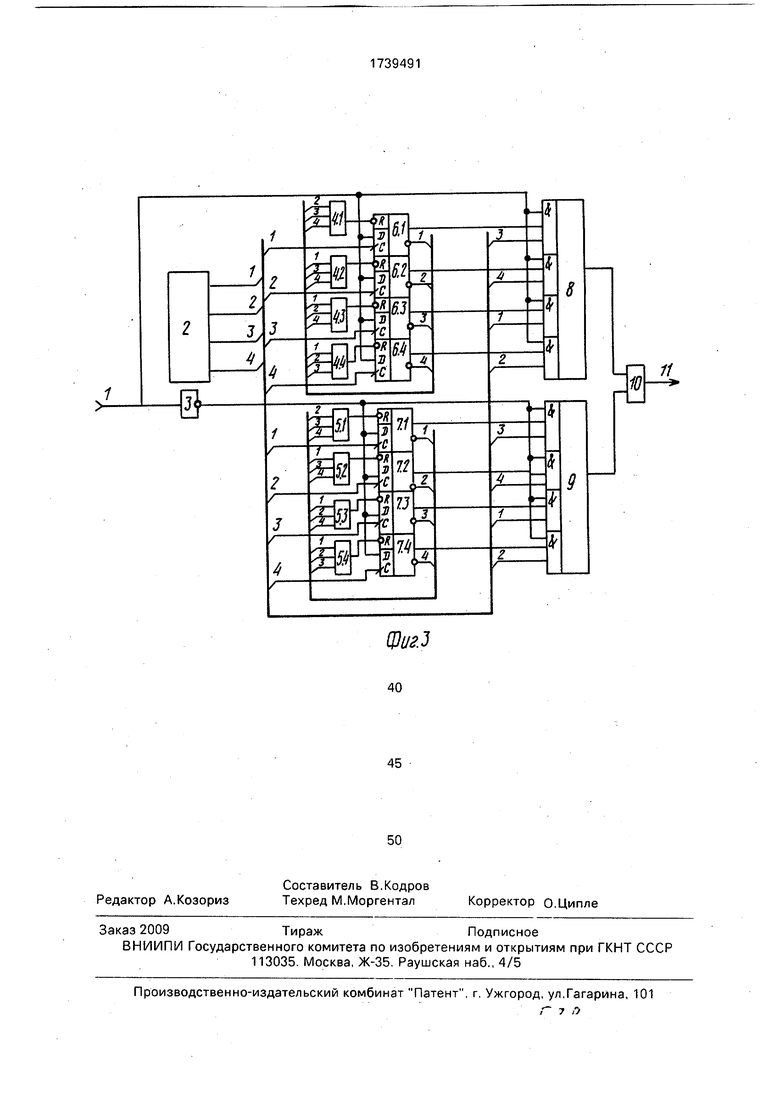

Сущность изобретения: устройство содержит входную шину 1, n-фазный генерта- тор 2,инвертор3,две группы из п элементов И 4.1-4.п, 5.1-5.п, две группы из п триггеров D-типа 6.1-б.п, 7.1-7.П, n-канальные коммутаторы 8, 9, выходную шину 11 с соответствующими связями. 3 ил.

(Л

С

FS10

11

4 iOO О

ю

Риг.1

Изобретение относится к импульсной технике и может быть использовано для формирования сигналов синхронизации при приеме данных в вычислительные системы, функционирующие в асинхронном ре- жиме.

Известны устройства для фазовой синхронизации вычислительных систем, работа которых основана на использовании многофазных тактовых последовательностей и сравнении фаз каждой из тактовых последовательностей с .входным сигналом.

Недостатком известных устройств является ограниченность функциональных возможностей,

Наиболее близким к предложенному является фазовый синхронизатор, содержащий группу из D-триггеров, блок задержки, состоящий из (п-1)-го последовательно соединенного элемента задержки, п-каналь- ный коммутатор, выход которого соединен с выходной шиной, информационный вход первого канала - с шиной тактового сигнала и с входом блока задержки, выходы элементов задержки которого соединены с информационными входами, начиная с второго, n-канального коммутатора и шину синхросигнала, S-входы каждого из D-триггеров соединены с шиной синхросигнала, С-входы каждого из D-триггеров соединены с информационными входами соответствующих каналов n-канального коммутатора, управляющие входы которого соединены с инверсным входом соответствующего триггера, с прямым выходом и с D-входом пред- ыдущего триггера, при этом прямой вход и D-вход п-го триггера соединены с инверсным выходом первого триггера.

Недостатком известного синхронизатора является ограниченность функциональ- ных возможностей устройства из-за возможности подавления помех на входе устройства.

Цель изобретения - повышение помехоустойчивости за счет обеспечения фильт- рации входных импульсов по длительности.

Поставленная цель достигается тем, что в фазовый синхронизатор, содержащий п- фазный генератор, выходы которого соединены с С-входами соответствующих триггеров первой группы из п триггеров D- типа, первый n-канальный коммутатор, входную и выходную шины, введены вторая группа из п триггеров D-типа, второй п-ка- нальный коммутатор, инвертор, элемент ИЛИ, первая и вторая группы из п элементов И каждая, выходы которых соединены с R-входами соответствующих триггеров соответственно первой и второй групп из п триггеров, инверсный выход каждого i-ro

(где , 2,..., п) из которых соединен с соответствующим входом каждого, кроме i-ro, элемента И своей группы из п элементов И, прямые выходы каждого триггера первой и второй группы из п триггеров соединены с первыми входами соответствующих каналов соответственно первого и второго п-ка- нальных коммутаторов, вторые входы соответствующих каналов первого п-ка- нального коммутатора соединены с D- входами триггеров первой группы из п триггеров, с входной шиной и с входом инвертора, выход которого соединен с вторыми входами соответствующих каналов второго n-канального коммутатора и с D- входами триггеров второй группы из п-триг- геров, С-входы каждого из которых соединены с соответствующими выходами инвертора, причем третьи входы каждого из п каналов первого n-канального коммутатора объединены с третьими входами соответствующих каналов второго п-канального коммутатора и соединены каждый с (j+k)M по модулю п выходом n-фазного генератора, где j-порядковый номер канала, к - величина, пропорциональная длительности бита входных данных, при этом выходы первого и второго n-канальных коммутаторов соединены с соответствующими входами элемента ИЛИ, выход которого соединен с выходной шиной.

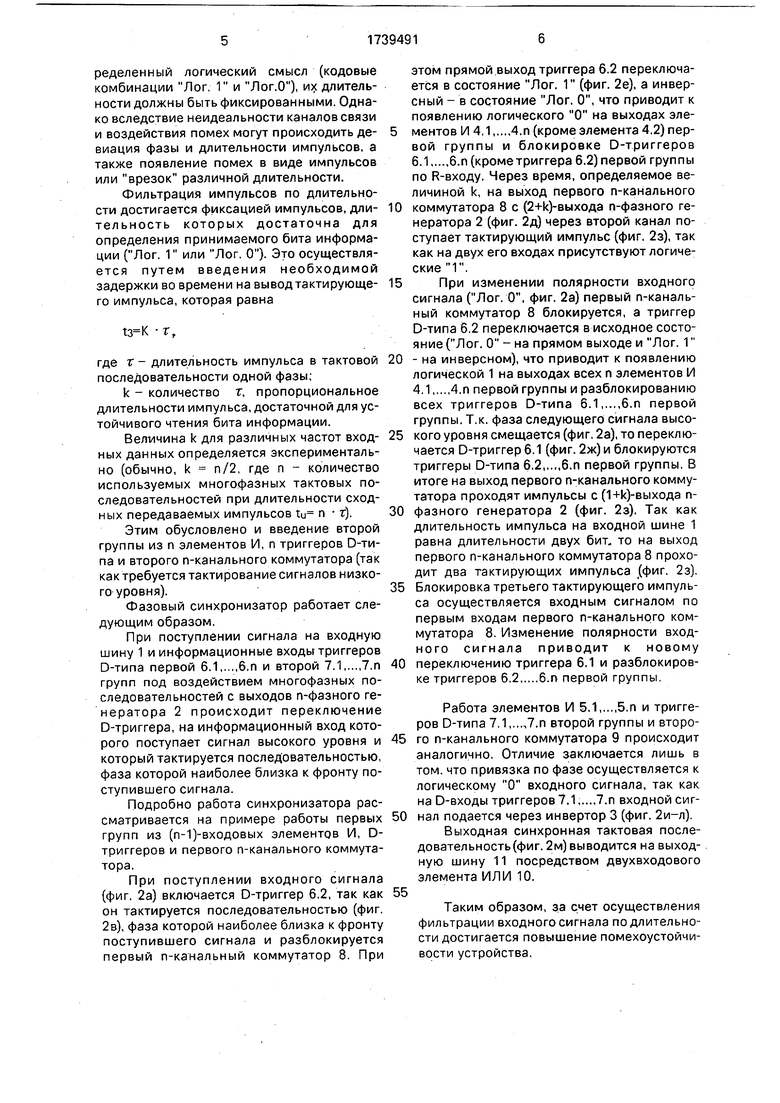

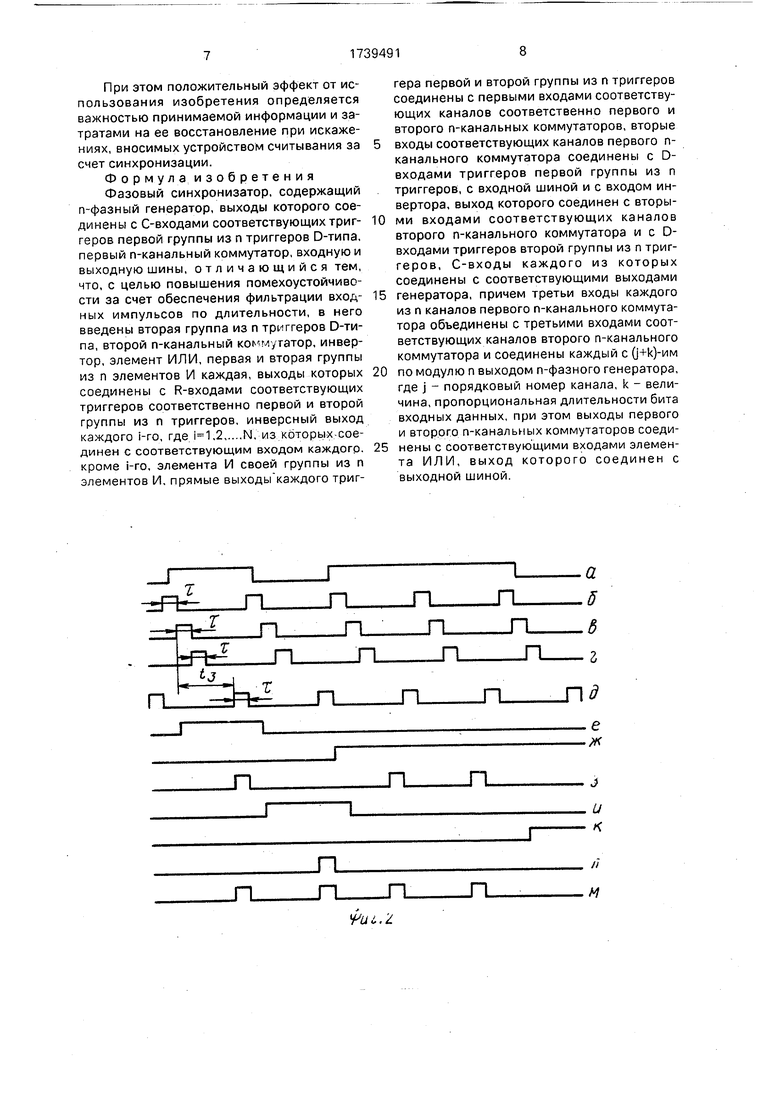

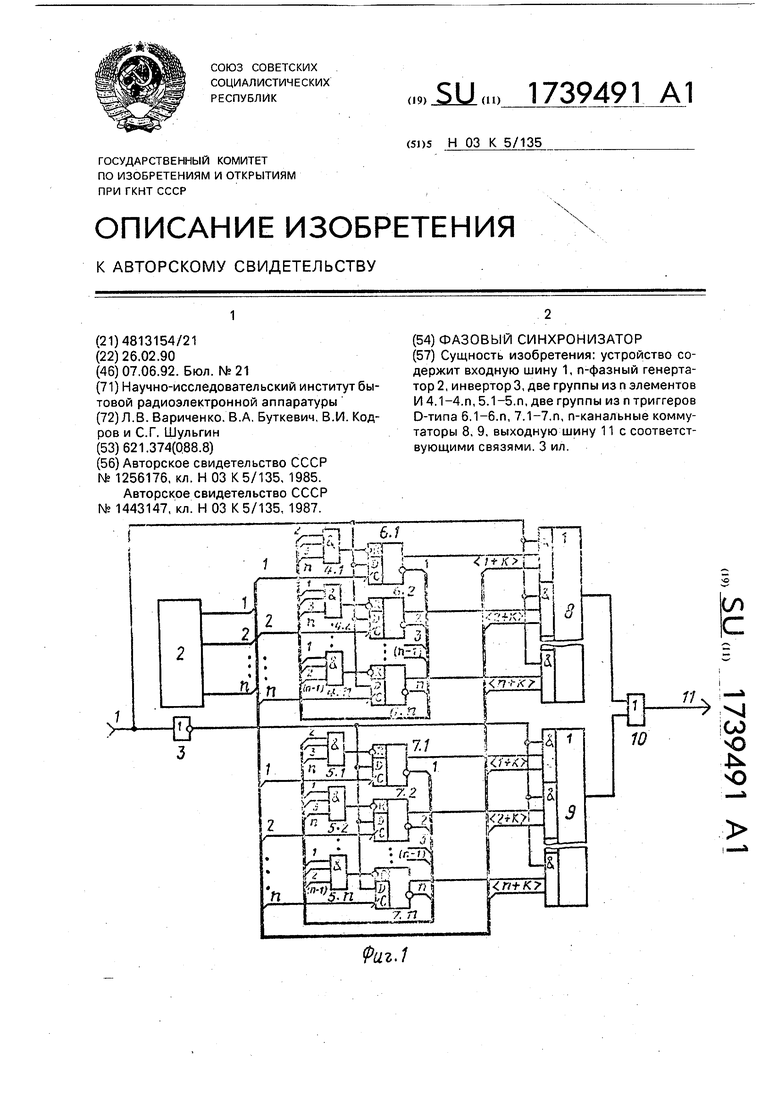

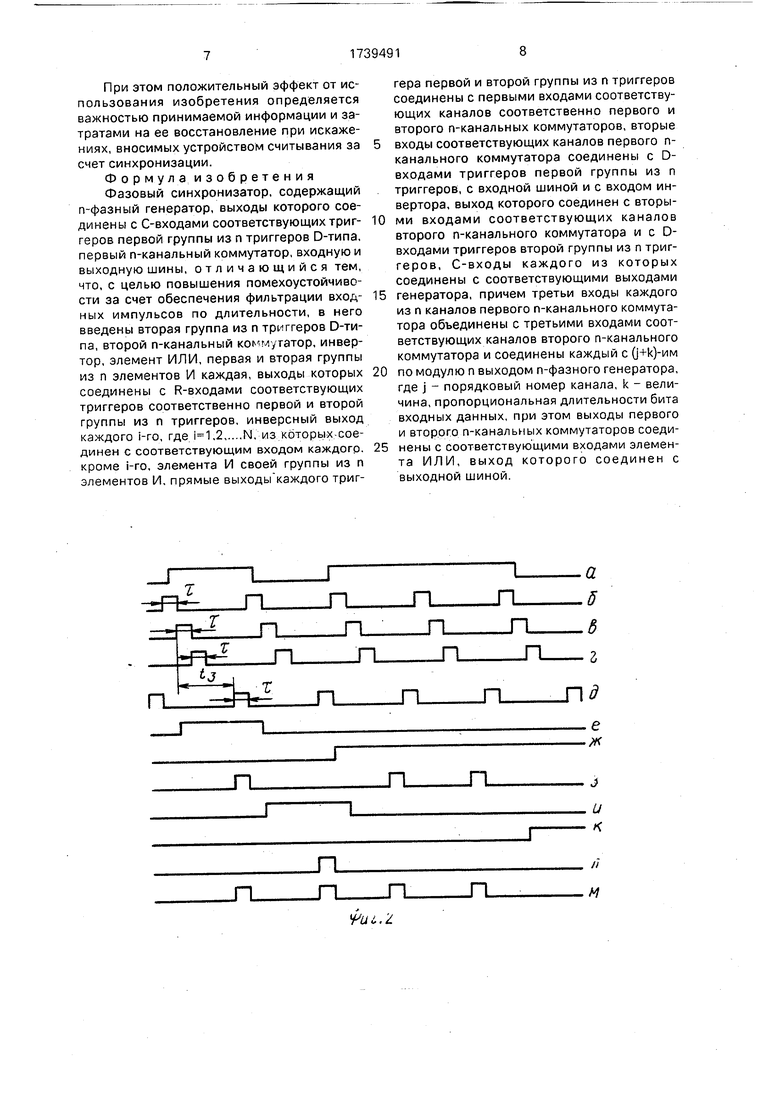

На фиг. 1 представлена структурная схема фазового синхронизатора; на фиг. 2 - временные диаграммы его работы: а - сигнал на входной шине; б-д - сигналы на первом, втором, третьем и n-м выходах п- фазного генератора; е, ж - сигналы на прямых выходах соответственно второго и первого триггеров D-типа первой группы; з - сигнал на выходе первого n-канального коммутатора; и, к - сигналы на прямых выходах соответственно второго и третьего триггеров D-типа второй группы; л - сигнал на выходе второго n-канального коммутатора; м - сигнал на выходной шине; на фиг. 3 - схема синхронизатора для .

Фазовый синхронизатор (фиг. 1) состоит из входной шины 1, n-фазного генератора 2, инвертора 3, первой и второй групп из п элементов И 4.14п 5.15п соответственно каждая, первой и второй групп из п триггеров D-типа 6.16п и 7,17п соответственно каждая, первого 8 и второго 9 n-канальных коммутаторов, элемента ИЛИ 10 и выходной шины 11.

Сущность изобретения заключается в следующем.

Так как при передаче информации в последовательном коде длительности сигналов высокого и низкого уровней несут определенный логический смысл (кодовые комбинации Лог. 1 и Лог.О), щ длительности должны быть фиксированными. Однако вследствие неидеальности каналов связи и воздействия помех могут происходить девиация фазы и длительности импульсов, а также появление помех в виде импульсов или врезок различной длительности.

Фильтрация импульсов по длительности достигается фиксацией импульсов, дли- тельность которых достаточна для определения принимаемого бита информации (Лог. 1 или Лог. О). Это осуществляется путем введения необходимой задержки во времени на вывод тактирующего импульса, которая равна

-т,

где т - длительность импульса в тактовой последовательности одной фазы;

k - количество т, пропорциональное длительности импульса, достаточной для устойчивого чтения бита информации.

Величина k для различных частот входных данных определяется экспериментально (обычно, k п/2, где п - количество используемых многофазных тактовых последовательностей при длительности сходных передаваемых импульсов tu n г).

Этим обусловлено и введение второй группы из п элементов И, п триггеров D-ти- па и второго n-канального коммутатора (так как требуется тактирование сигналов низкого уровня).

Фазовый синхронизатор работает следующим образом.

При поступлении сигнала на входную шину 1 и информационные входы триггеров

D-типа первой 6.1б.п и второй 7.17,п

групп под воздействием многофазных последовательностей с выходов n-фазного генератора 2 происходит переключение D-триггера, на информационный вход которого поступает сигнал высокого уровня и который тактируется последовательностью, фаза которой наиболее близка к фронту поступившего сигнала.

Подробно работа синхронизатора рассматривается на примере работы первых групп из (п-1)-входовых элементов И, D- триггеров и первого n-канального коммутатора.

При поступлении входного сигнала (фиг. 2а) включается D-триггер 6.2, так как он тактируется последовательностью (фиг. 2в), фаза которой наиболее близка к фронту поступившего сигнала и разблокируется первый n-канальный коммутатор 8. При

этом прямой выход триггера 6,2 переключается в состояние Лог. 1 (фиг. 2е), а инверсный - в состояние Лог. О, что приводит к появлению логического О на выходах элементов И 4,14.п (кроме элемента 4.2) первой группы и блокировке D-триггеров

по R-входу. Через время, определяемое величиной k, на выход первого п-канального

коммутатора 8 с (2+ -выхода n-фазного генератора 2 (фиг. 2д) через второй канал поступает тактирующий импульс (фиг. 2з), так как на двух его входах присутствуют логические 1.

При изменении полярности входного сигнала (Лог. О, фиг. 2а) первый п-каналь- ный коммутатор 8 блокируется, а триггер D-типа 6.2 переключается в исходное состояние (Лог. О - на прямом выходе и Лог. 1

- на инверсном), что приводит к появлению логической 1 на выходах всех п элементов И

всех триггеров D-типа 6.1б.п первой

группы. Т.к. фаза следующего сигнала высокого уровня смещается (фиг. 2а), то переключается D-триггер 6.1 (фиг. 2ж) и блокируются

триггеры D-типа 6,2б.п первой группы. В

итоге на выход первого n-канального коммутатора проходят импульсы с (1+k)-Bbixofla nфазного генератора 2 (фиг. 2з). Так как длительность импульса на входной шине 1 равна длительности двух бит, то на выход первого n-канального коммутатора 8 проходит два тактирующих импульса .(фиг. 2з).

Блокировка третьего тактирующего импульса осуществляется входным сигналом по первым входам первого n-канального коммутатора 8. Изменение полярности входного сигнала приводит к новому

переключению триггера 6.1 и разблокировке триггеров 6.2б.п первой группы.

Работа элементов И 5.1,...,5.п и триггеров D-типа 7.1,.,.,7.п второй группы и второго n-канального коммутатора 9 происходит аналогично. Отличие заключается лишь в том. что привязка по фазе осуществляется к логическому О входного сигнала, так как на D-входы триггеров 7.17.п входной сигнал подается через инвертор 3 (фиг. 2и-л).

Выходная синхронная тактовая последовательность (фиг. 2м) выводится на выходную шину 11 посредством двухвходового элемента ИЛИ 10.

Таким образом, за счет осуществления фильтрации входного сигнала по длительности достигается повышение помехоустойчивости устройства.

При этом положительный эффект от использования изобретения определяется важностью принимаемой информации и затратами на ее восстановление при искажениях, вносимых устройством считывания за счет синхронизации.

Формула изобретения Фазовый синхронизатор, содержащий n-фазный генератор, выходы которого соединены с С-входами соответствующих триг- геров первой группы из п триггеров D-типа, первый n-канальный коммутатор, входную и выходную шины, отличающийся тем, что, с целью повышения помехоустойчивости за счет обеспечения фильтрации вход- ных импульсов по длительности, в него введены вторая группа из п триггеров D-типа, второй n-канальный коммутатор, инвертор, элемент ИЛИ, первая и вторая группы из п элементов И каждая, выходы которых соединены с R-входами соответствующих триггеров соответственно первой и второй группы из п триггеров, инверсный выход

каждого 1-го, где ,2N. из которых-соединен с соответствующим входом каждогр. кроме 1-го, элемента И своей группы из п элементов И, прямые выходы каждого триггера первой и второй группы из п триггеров соединены с первыми входами соответствующих каналов соответственно первого и второго n-канальных коммутаторов, вторые входы соответствующих каналов первого п- канального коммутатора соединены с D- входами триггеров первой группы из п триггеров, с входной шиной и с входом инвертора, выход которого соединен с вторыми входами соответствующих каналов второго n-канального коммутатора и с D- входами триггеров второй группы из п триггеров, С-входы каждого из которых соединены с соответствующими выходами генератора, причем третьи входы каждого из п каналов первого n-канального коммутатора объединены с третьими входами соответствующих каналов второго п-канального коммутатора и соединены каждый с 0+к)-им по модулю п выходом n-фазного генератора, где j - порядковый номер канала, k - величина, пропорциональная длительности бита входных данных, при этом выходы первого и второго n-канальных коммутаторов соединены с соответствующими входами элемента ИЛИ, выход которого соединен с выходной шиной.

.2

teJ

| Фазовый синхронизатор | 1985 |

|

SU1256176A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Фазовый синхронизатор | 1987 |

|

SU1443147A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-06-07—Публикация

1990-02-26—Подача