I-л

Изобретение относится к импульсной технике и может быть использовано для формирования сигнала синхронизации вычислительных и измерительных систем, функционирующих в асинхронном режиме.

Цель изобретения - повышение точности фазовой синхронизации за счет повышения (практически на порядок) быстродействия.

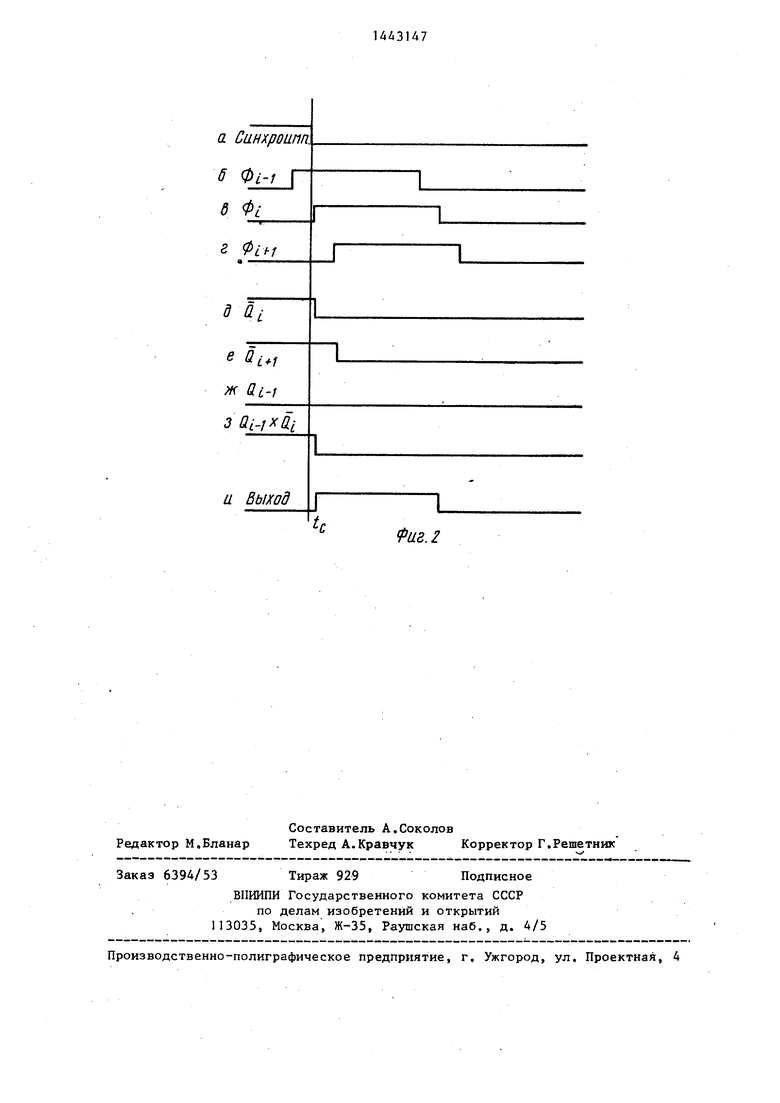

На фиг.1 приведена электрическая структурная схема синхронизатора; на фиг.2 - временные диаграммы, пЬясня- кицие его работу.

Фазовый синхронизатор содержит блок 1 задержки состояощй из (п-1)- го элемента задержки. Вход блока 1 задержки соединен с шиной 2 тактового сигнала, S-выходы каждого из п- триггеров D-типа группы 3 соединены с шиной 4 синхросигнала. Выход п-ка- нального коммутатора 5 соединен с выходной шиной 6.Информационный вход каждого канала п-канального коммута- тора 5 соединен с С-входом соответствующего триггера группы 3, при этом С-вход первого триггера группы 3 соединен с входом блока 1 задержки, выходы элементов задержки которого соединены с С-входами соответственно, начиная с второго, триггеров из группы 3.Управляющие входы каждого из каналов п-канального коммутатора 5 соединены с инверсными выходами соответствующих триггеров и с прямым выхо,- дом и D-ВХОДОМ предьщущего триггера группы 3, при этом инверсньй выход первого триггера соединен с прямым выходом и с D-ВХОДОМ п-го триггера группы 3.

Синхронизатор работает следующим образом.

До момента фазовой синхронизации все триггеры группы 3 по S-входу удерживаются в единичном состоянии. При этом на их инверсных выходах поддерживается уровень Лог.о, 1 оторый не пропускает на шину 6 через коммутатор 5 ни одну из фаз тактового сигнала, образованны блоком 1.

В момент синхронизации t (фиг.2) удерживающий сигнал снимается с S- входов триггеров (фиг.2а). Предполо- жим что сигналы фаз Ф ,, , Ф;, Ф ,, , приходящие на С-входы соответствующих триггеров, расположены относительно момента синхронизации t (Фиг.26,

г). Под воздействием рабочих фронтов фаз Ф|, , соответствующие триггеры последовательно переключаются в состояние Лог.О (фиг.2д и е). Далее переключаются остальнъш триггеры. В состоянии Лог.1 остается лишь (1-1)-й триггер .(Фиг.2ж), поскольку на его D-входе от сигнала Q ,4i Q; (фиг,2з) поддерживается уровень Лог. 1. Этот же сигнал пропускает через коммутатор 5 на шину 6 фазу Ф; (фиг.2и рабочийфронт которой наиболее близок к моменту синхронизации t,.

По сравнению с известным фазовым синхронизатором предлагаемый обладает большей по времени точностью фазовой синхронизации. Так в известном устройстве, реализованном на триггерах серии К500, мин1-1мально допустимое временное расстояние между соседними фазами синхросигнала составляет около 2 НС. В предлагаемом синхронизаторе минимальное расстояние между соседш ми фазами определяется эффектами второго порядка малости, оно, в частности, сравнимо с разбросом времени переключения триггеров фиксирующей цепи, ко- торьш для триггеров указанной серии не превышает ut, 0,2 не.

Формула изобретения

Фазовый синхронизатор, содержащий группу из п триггеров D-типа,блок задержки, состоящий из (n-l)-ro последовательно соединенного элемента задержки, п-канальный коммутатор, выход KOTOjioro соединен с выходной шиной, информационный вход первого канала - с шиной тактового сигнала и с входом блока задержки, выходы элементов задержки которого соединены с информационными входами, начиная с второго канала, п-канального коммутатора и ,шину синхросигнала, отличаю- щ и и с я тем,, что, с целью повьпие- ния точности фазовой синхронизации, S-входы каждого из п-триггеров соединены с шиной синхросигнала, С-входы каждого из п триггеров соединены с информационными входами соответствуют щих каналов п-канального коммутатора, управляющие входы которых соединены с инверсными выходом соответствующего триггера, с прямым выходом и с D-BXO- дом предыдущего триггера, при этом прямой выход и В-вход п-го триггера соединены с инверсным выходом первого триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Фазовый синхронизатор | 1990 |

|

SU1739491A1 |

| Фазовый синхронизатор | 1985 |

|

SU1256176A1 |

| Фазовый синхронизатор | 1987 |

|

SU1413708A2 |

| Фазовый синхронизатор | 1986 |

|

SU1309279A1 |

| Способ цикловой синхронизации при записи-воспроизведении цифровой информации | 1980 |

|

SU972568A1 |

| Устройство для передачи и приема многопозиционных широкополосных сигналов | 1989 |

|

SU1793551A1 |

| Генератор-анализатор псевдослучайной последовательности | 1990 |

|

SU1784978A1 |

| Устройство управления диаграммой направленности двумерных антенных решеток | 1990 |

|

SU1748215A1 |

| УСТРОЙСТВО ВОСПРОИЗВЕДЕНИЯ СИГНАЛОВ ЦИФРОВОЙ ИНФОРМАЦИИ С МАГНИТНОГО НОСИТЕЛЯ | 2001 |

|

RU2217817C2 |

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

Изобретение относится к импульсной технике и может быть использовано для формирования сигнала синхронизации вычислительных систем, функционирующих в асинхронном режиме. Цель изобретения - повьппение точности фазовой подстройки - достигается за счет повьшения (практически на один порядок) быстродействия. Устройство содержит блок 1 задержки, состоящий из п-1 злементов задержки, шину 2 тактового сигнала, группу 3 D- триггеров, шину 4 синхронизации, п- канальный коммутатор 5 и выходную ну 6. Положительный эффект заключается в том, что построение схемы последовательно по цепи триггеров не на- кладьюает принципиальных ограничений на временные расстояния меаду фазами. Это повыгаает надежность синхронизации ЭВМ и измерительных систем за ., , счет повьш1ения точности фазовой син- . хронизации. 2 ил. (Л

| Авторское свидетельство СССР 1285581, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Фазовый синхронизатор | 1985 |

|

SU1256176A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-12-07—Публикация

1987-05-11—Подача