Предлагаемое изобретение относится к области аналоговой микроэлектроники и может быть использовано в различных аналоговых и аналого-цифровых интерфейсах – активных RC-фильтрах, нормирующих преобразователях и т.п., в том числе работающих в условиях низких температур и воздействия радиации.

В современной микроэлектронике достаточно перспективны архитектуры операционных усилителей (ОУ), содержащие так называемый «перегнутый» каскод [1-28], который реализуется по BJT [1-18], JFET [19-24], а также по CMOS [25-28] технологиям. Это одно из перспективных направлений аналоговой схемотехники.

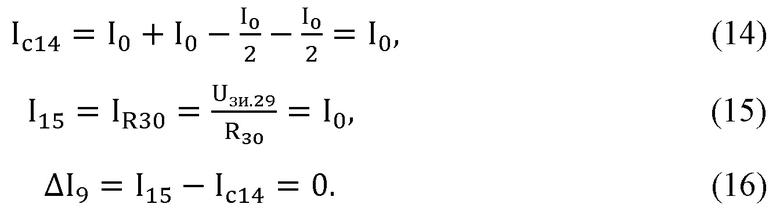

Ближайшим прототипом заявляемого устройства является операционный усилитель, представленный в статье [Assaad R. S., Silva-Martinez J. The recycling folded cascode: A general enhancement of the folded cascode amplifier // IEEE Journal of Solid-State Circuits. – 2009. – Т. 44. – №. 9. – С. 2535-2542, Fig. 1]. Кроме этого, данная архитектура ОУ используется в патенте US 7.510.113, 2009 г. Операционный усилитель – прототип содержит первый 1 и второй 2 входы входного дифференциального каскада 3 с первым 4 и вторым 5 токовыми выходами и токовым входом 6 общей истоковой цепи для установления статического режима, который связан с первой 7 шиной источника питания через вспомогательный источник опорного тока 8, токовый выход 9 устройства, вторую 10 шину источника питания, первый 11 вспомогательный полевой транзистор, сток которого соединен с истоком второго 12 вспомогательного полевого транзистора и подключен к первому 4 токовому выходу входного дифференциального каскада 3, третий 13 вспомогательный полевой транзистор, сток которого соединен с истоком четвертого 14 вспомогательного полевого транзистора и подключен ко второму 5 токовому выходу входного дифференциального каскада 3, цепь динамической нагрузки 15 на полевых транзисторах, включенную между стоком четвертого 14 вспомогательного полевого транзистора, связанным с токовым выходом 9 устройства и первой 7 шиной источника питания.

Существенный недостаток ОУ-прототипа состоит в том, что в нем не обеспечиваются малые значения систематической составляющей напряжения смещения нуля (Uсм) и повышенные значения коэффициента усиления по напряжению (Ку).

Основная задача предлагаемого изобретения состоит в создании радиационно-стойкого и низкотемпературного операционного усилителя, который за счет высокой самоустанавливающейся симметрии статического режима по токам стока и напряжениям затвор-сток применяемых полевых транзисторов обеспечивает малый уровень систематической составляющей напряжения смещения нуля и повышенные значения коэффициента усиления по напряжению.

Поставленная задача достигается тем, что в ОУ фиг. 1, содержащем первый 1 и второй 2 входы входного дифференциального каскада 3 с первым 4 и вторым 5 токовыми выходами и токовым входом 6 общей истоковой цепи для установления статического режима, который связан с первой 7 шиной источника питания через вспомогательный источник опорного тока 8, токовый выход 9 устройства, вторую 10 шину источника питания, первый 11 вспомогательный полевой транзистор, сток которого соединен с истоком второго 12 вспомогательного полевого транзистора и подключен к первому 4 токовому выходу входного дифференциального каскада 3, третий 13 вспомогательный полевой транзистор, сток которого соединен с истоком четвертого 14 вспомогательного полевого транзистора и подключен ко второму 5 токовому выходу входного дифференциального каскада 3, цепь динамической нагрузки 15 на полевых транзисторах, включенную между стоком четвертого 14 вспомогательного полевого транзистора, связанным с токовым выходом 9 устройства и первой 7 шиной источника питания, предусмотрены новые элементы и связи – затворы первого 11 и третьего 13 вспомогательных полевых транзисторов соединены со второй 10 шиной источника питания, исток первого 11 вспомогательного полевого транзистора связан со второй 10 шиной источника питания через первый 16 дополнительный резистор и соединен с затвором второго 12 вспомогательного полевого транзистора, исток третьего 13 вспомогательного полевого транзистора связан со второй 10 шиной источника питания через второй 17 дополнительный резистор и соединен с затвором четвертого 14 вспомогательного полевого транзистора, к первому 4 токовому выходу входного дифференциального каскада 3 подключен сток первого 18 дополнительного полевого транзистора, затвор которого соединен со второй 10 шиной источника питания, а исток связан со второй 10 шиной источника питания через третий 19 дополнительный резистор, ко второму 5 токовому выходу входного дифференциального каскада 3 подключен сток второго 20 дополнительного полевого транзистора, затвор которого соединен со второй 10 шиной источника питания, а исток связан со второй 10 шиной источника питания через четвертый 21 дополнительный резистор, источник опорного тока 8 выполнен на основе третьего 22, четвертого 23, пятого 24 и шестого 25 дополнительных полевых транзисторов, а также пятого 26 и шестого 27 дополнительных резисторов, причем стоки третьего 22 и пятого 24 дополнительных полевых транзисторов соединены с первой 7 шиной источника питания, затворы четвертого 23 и шестого 25 дополнительных полевых транзисторов связаны с токовым входом 6 общей истоковой цепи для установления статического режима входного дифференциального каскада 3, сток четвертого 23 дополнительного полевого транзистора соединен с истоком третьего 22 дополнительного полевого транзистора, затвор третьего 22 дополнительного полевого транзистора соединен с истоком четвертого 23 дополнительного полевого транзистора и через пятый 26 дополнительный резистор подключен к токовому входу 6 общей истоковой цепи для установления статического режима входного дифференциального каскада 3, затвор пятого 24 дополнительного полевого транзистора соединен с истоком шестого 25 дополнительного полевого транзистора и через шестой 27 дополнительный резистор подключен к токовому входу 6 общей истоковой цепи для установления статического режима входного дифференциального каскада 3.

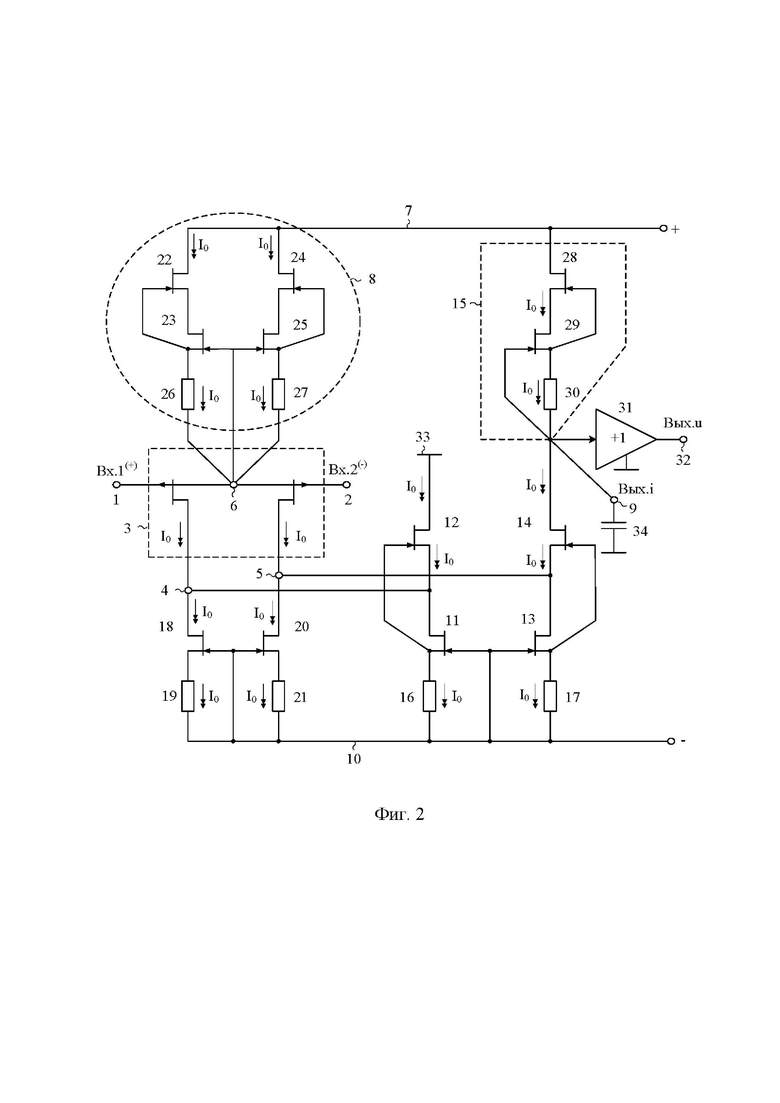

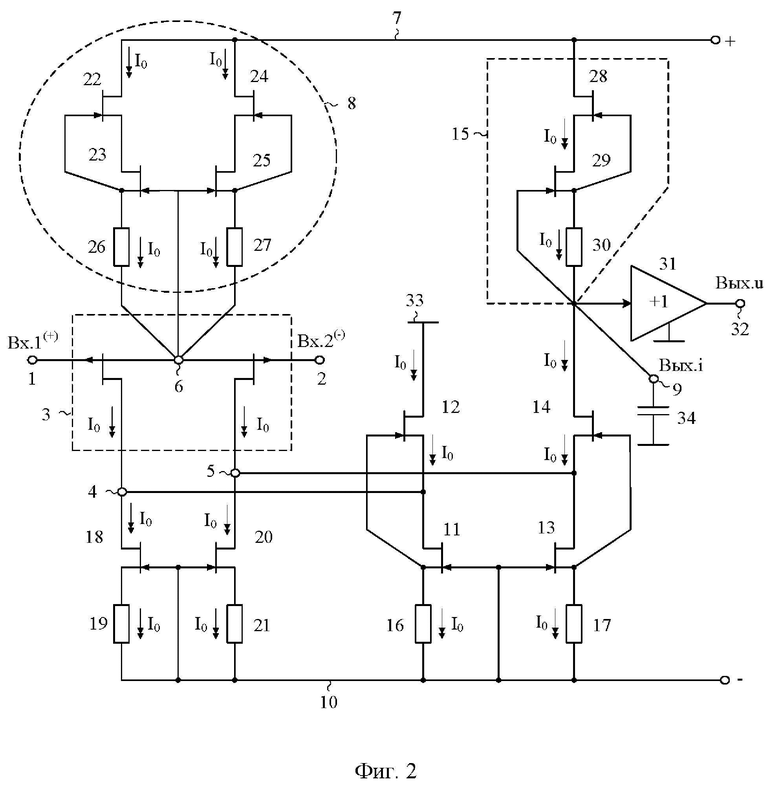

На фиг. 1 представлена схема ОУ-прототипа, а на фиг. 2 – схема заявляемого ОУ в соответствии с п. 1, п. 2, п. 3 и п. 4 формулы изобретения.

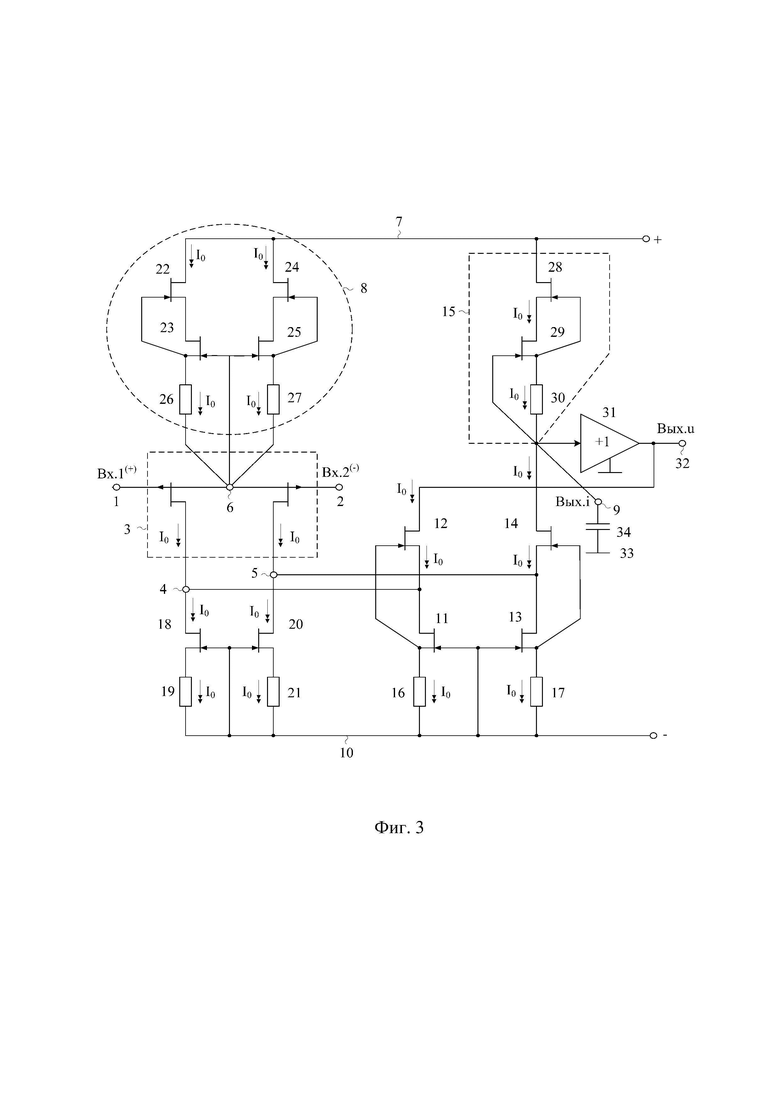

На фиг. 3 приведена схема заявляемого ОУ в соответствии с п. 5 формулы изобретения.

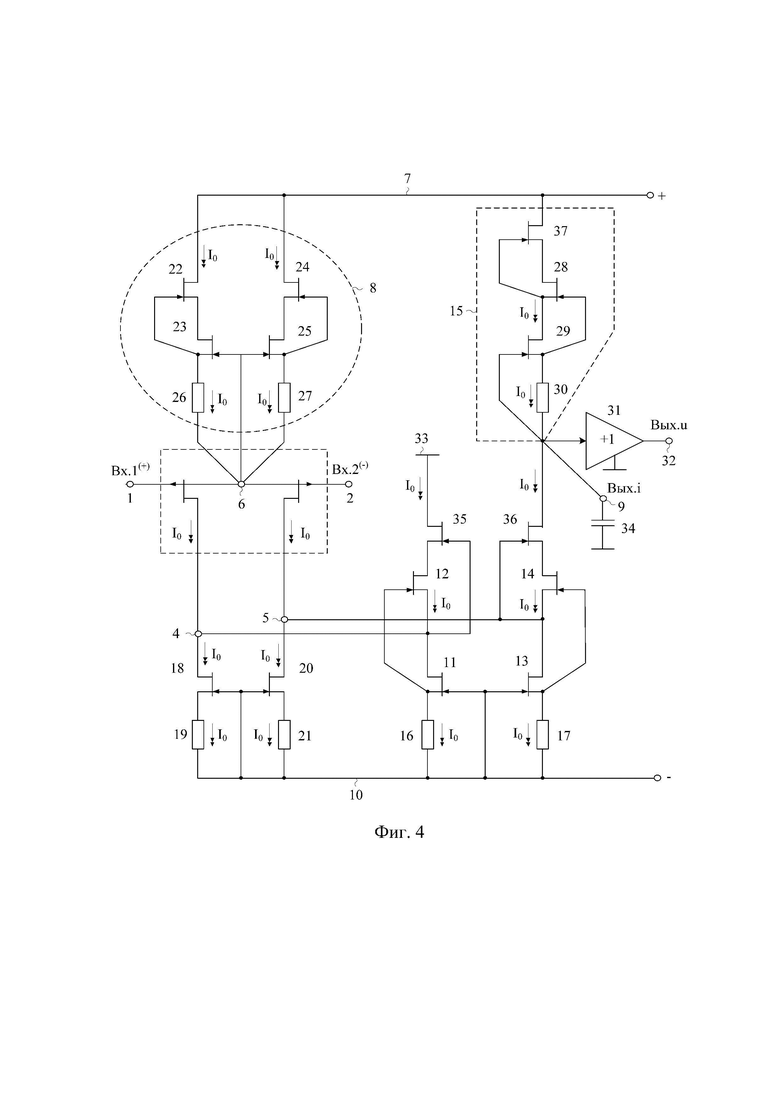

На фиг. 4 показана схема заявляемого ОУ фиг. 2 для случая, когда в качестве второго 12 и четвертого 14 вспомогательных полевых транзисторов, а также седьмого 28 дополнительного полевого транзистора используются каскодные составные транзисторы, образованные вторым 12 и пятым 35, четвертым 14 и шестым 36 вспомогательными полевыми транзисторами, а также седьмым 28 и девятым 37 дополнительными полевыми транзисторами.

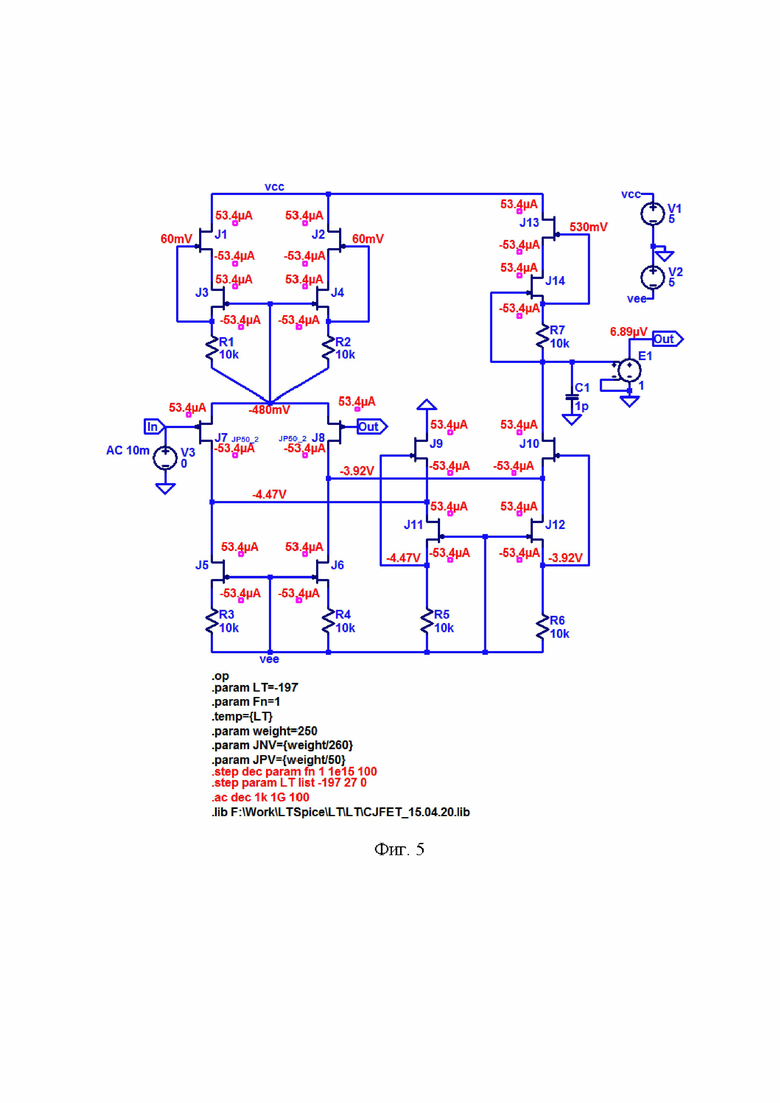

На фиг. 5 приведена схема заявляемого ОУ фиг. 2 в программной среде LTSpice (Analog Device, США) на комплементарных полевых транзисторах с управляющим pn-переходом (CJFET, «Интеграл», г. Минск, Беларусь) при напряжениях питания ± 5 В и температуре -197ºС.

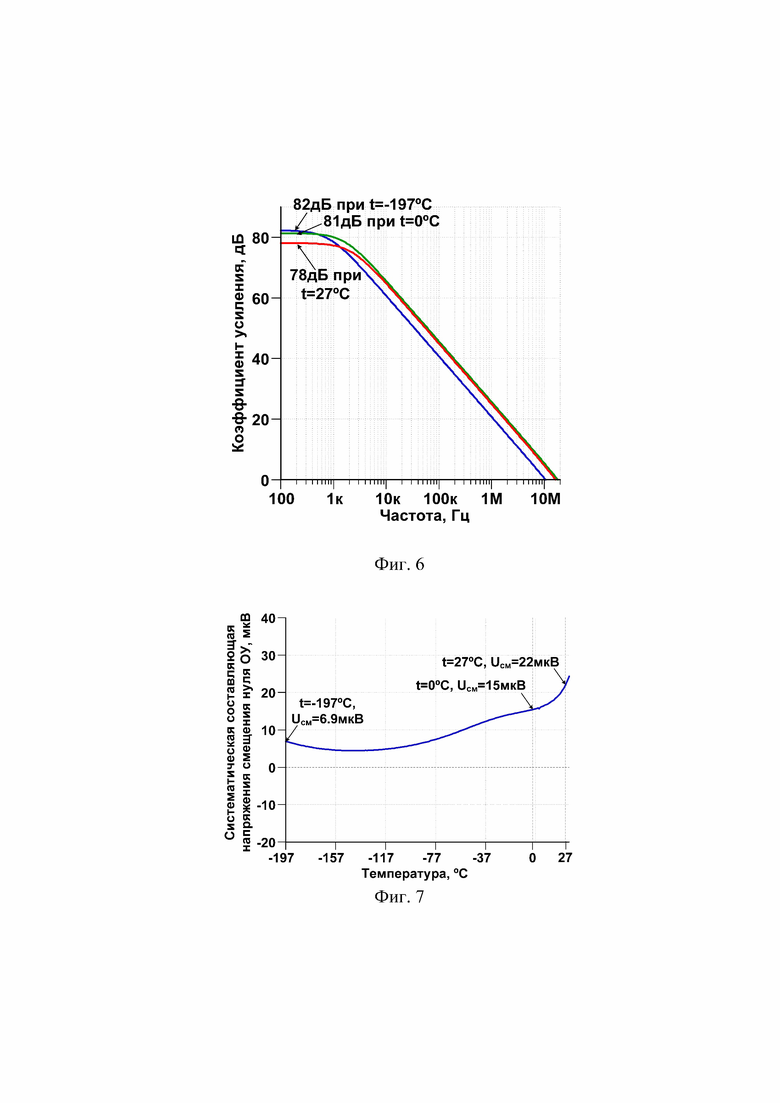

На фиг. 6 показаны результаты компьютерного моделирования логарифмической амплитудно-частотной характеристики (ЛАЧХ) ОУ фиг. 5, где разомкнутый коэффициент усиления (Ку) измерялся при t=0ºC; 27ºC; -197ºC.

На фиг. 7 приведена зависимость систематической составляющей напряжения смещения нуля ОУ фиг. 5 от температуры в диапазоне от -197°C до 30°C.

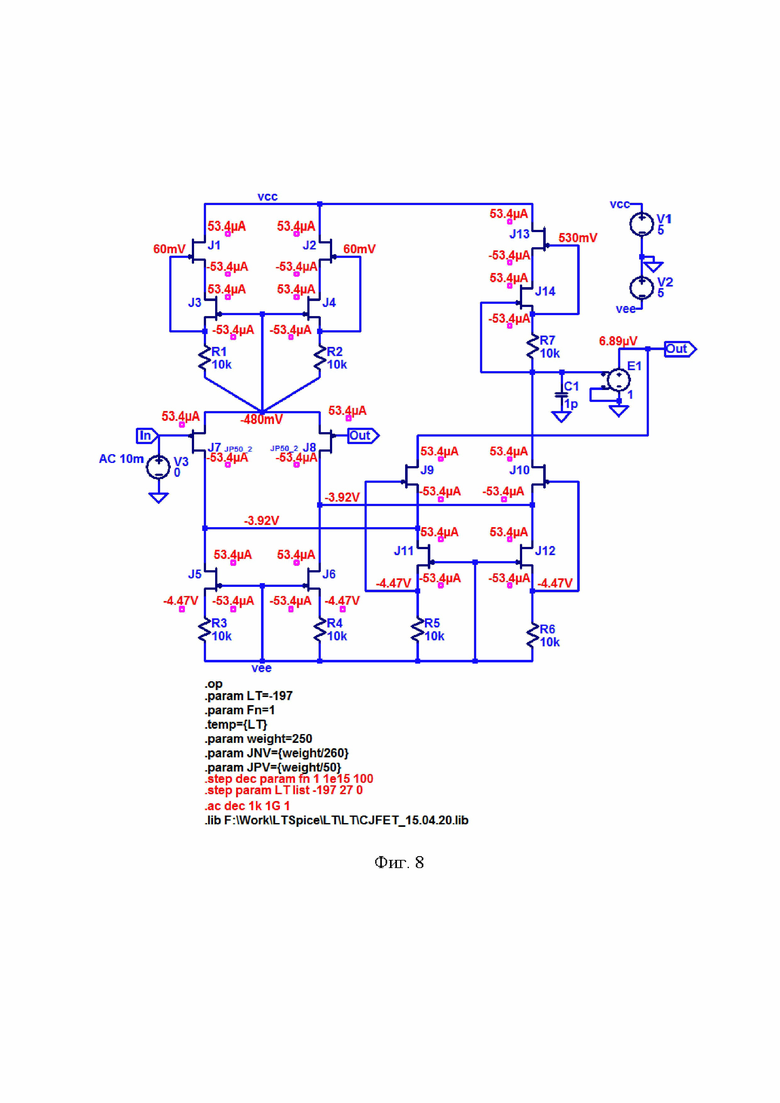

На фиг. 8 представлена схема заявляемого ОУ фиг. 3 в программной среде LTSpice (Analog Device, США) на CJFET («Интеграл», г. Минск, Беларусь) при напряжении питания ± 5 В и температуре -197ºС.

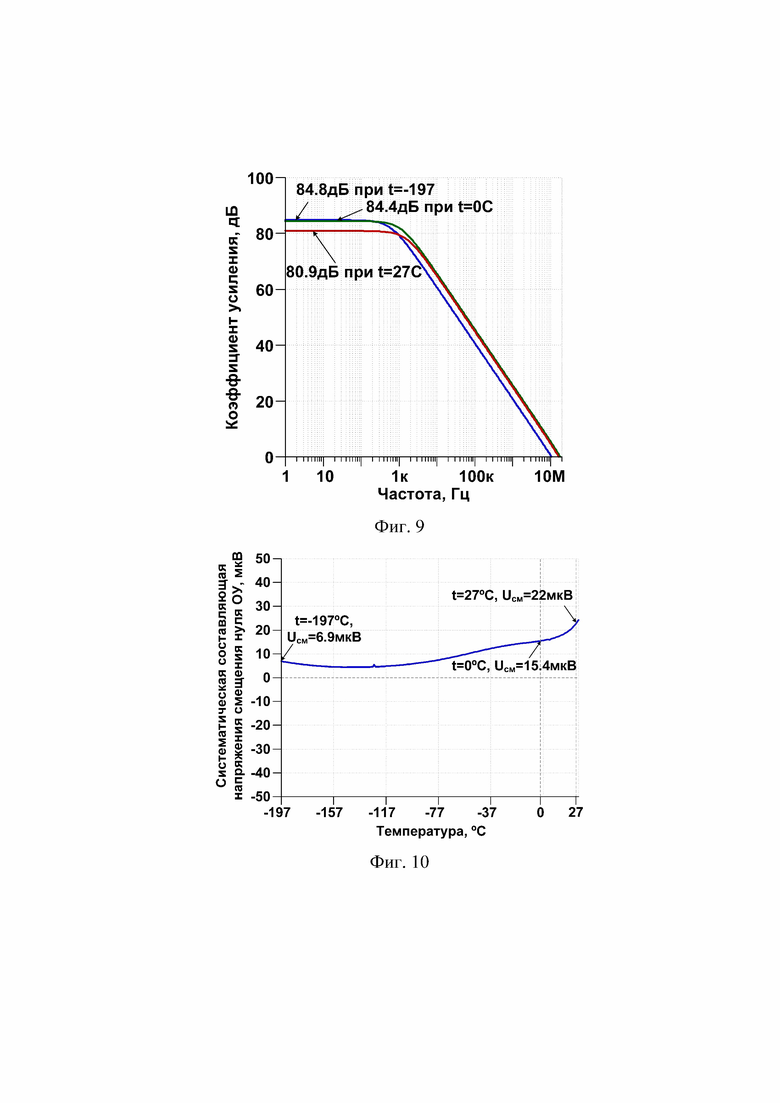

На фиг. 9 показана ЛАЧХ операционного усилителя фиг. 8, где разомкнутый Ку измерялся при t=0ºC; 27ºC; -197ºC.

На фиг. 10 приведена зависимость систематической составляющей напряжения смещения нуля ОУ фиг. 8 от температуры в диапазоне от -197°C до 30°C.

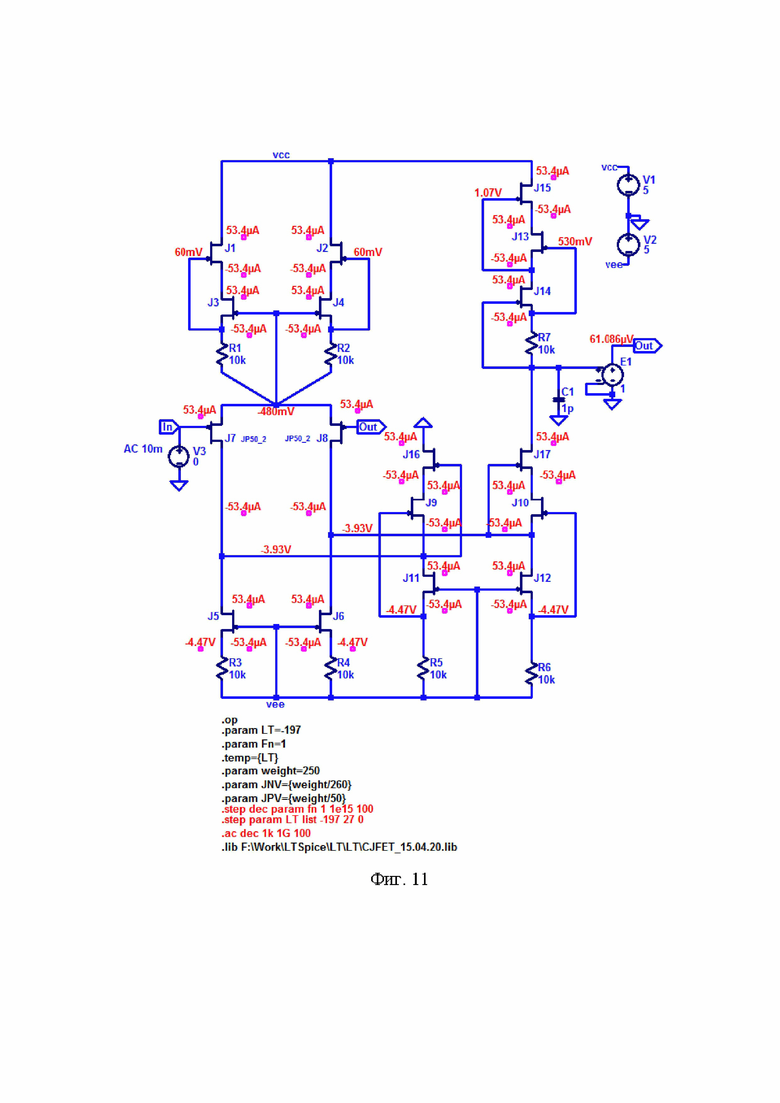

На фиг. 11 представлена схема ОУ фиг. 4 в программной среде LTSpice (Analog Device, США) на CJFET («Интеграл», г. Минск, Беларусь) при напряжении питания ± 5 В и температуре -197ºС.

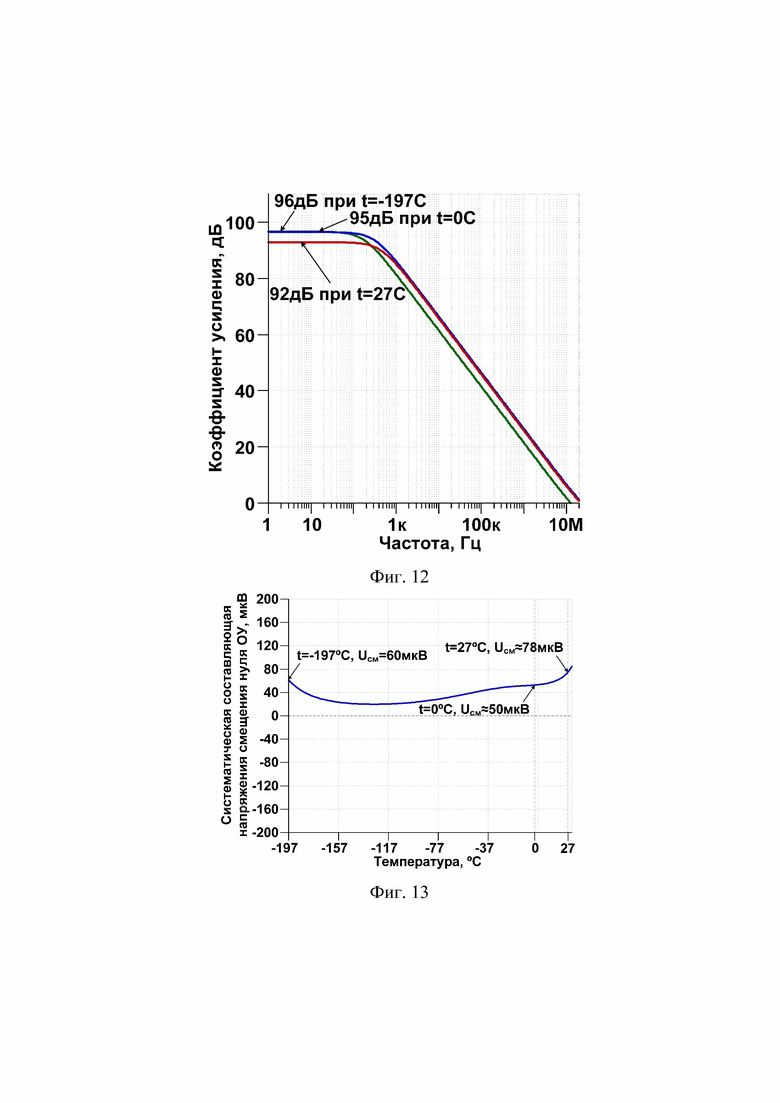

На фиг. 12 показаны результаты компьютерного моделирования ЛАЧХ ОУ фиг. 11, где разомкнутый Ку измерялся при t=0ºC; 27ºC; -197ºC.

На фиг. 13 приведена зависимость систематической составляющей напряжения смещения нуля ОУ фиг. 11 от температуры в диапазоне от -197°C до 30°C.

Операционный усилитель на комплементарных полевых транзисторах фиг. 2 содержит первый 1 и второй 2 входы входного дифференциального каскада 3 с первым 4 и вторым 5 токовыми выходами и токовым входом 6 общей истоковой цепи для установления статического режима, который связан с первой 7 шиной источника питания через вспомогательный источник опорного тока 8, токовый выход 9 устройства, вторую 10 шину источника питания, первый 11 вспомогательный полевой транзистор, сток которого соединен с истоком второго 12 вспомогательного полевого транзистора и подключен к первому 4 токовому выходу входного дифференциального каскада 3, третий 13 вспомогательный полевой транзистор, сток которого соединен с истоком четвертого 14 вспомогательного полевого транзистора и подключен ко второму 5 токовому выходу входного дифференциального каскада 3, цепь динамической нагрузки 15 на полевых транзисторах, включенную между стоком четвертого 14 вспомогательного полевого транзистора, связанным с токовым выходом 9 устройства и первой 7 шиной источника питания. Затворы первого 11 и третьего 13 вспомогательных полевых транзисторов соединены со второй 10 шиной источника питания, исток первого 11 вспомогательного полевого транзистора связан со второй 10 шиной источника питания через первый 16 дополнительный резистор и соединен с затвором второго 12 вспомогательного полевого транзистора, исток третьего 13 вспомогательного полевого транзистора связан со второй 10 шиной источника питания через второй 17 дополнительный резистор и соединен с затвором четвертого 14 вспомогательного полевого транзистора, к первому 4 токовому выходу входного дифференциального каскада 3 подключен сток первого 18 дополнительного полевого транзистора, затвор которого соединен со второй 10 шиной источника питания, а исток связан со второй 10 шиной источника питания через третий 19 дополнительный резистор, ко второму 5 токовому выходу входного дифференциального каскада 3 подключен сток второго 20 дополнительного полевого транзистора, затвор которого соединен со второй 10 шиной источника питания, а исток связан со второй 10 шиной источника питания через четвертый 21 дополнительный резистор, источник опорного тока 8 выполнен на основе третьего 22, четвертого 23, пятого 24 и шестого 25 дополнительных полевых транзисторов, а также пятого 26 и шестого 27 дополнительных резисторов, причем стоки третьего 22 и пятого 24 дополнительных полевых транзисторов соединены с первой 7 шиной источника питания, затворы четвертого 23 и шестого 25 дополнительных полевых транзисторов связаны с токовым входом 6 общей истоковой цепи для установления статического режима входного дифференциального каскада 3, сток четвертого 23 дополнительного полевого транзистора соединен с истоком третьего 22 дополнительного полевого транзистора, затвор третьего 22 дополнительного полевого транзистора соединен с истоком четвертого 23 дополнительного полевого транзистора и через пятый 26 дополнительный резистор подключен к токовому входу 6 общей истоковой цепи для установления статического режима входного дифференциального каскада 3, затвор пятого 24 дополнительного полевого транзистора соединен с истоком шестого 25 дополнительного полевого транзистора и через шестой 27 дополнительный резистор подключен к токовому входу 6 общей истоковой цепи для установления статического режима входного дифференциального каскада 3.

На фиг. 2, в соответствии с п. 2 формулы изобретения, цепь динамической нагрузки 15 на полевых транзисторах содержит седьмой 28 и восьмой 29 дополнительные полевые транзисторы, а также седьмой 30 дополнительный резистор, причем сток восьмого 29 дополнительного полевого транзистора соединен с истоком седьмого 28 дополнительного полевого транзистора, затвор восьмого 29 дополнительного полевого транзистора соединен с токовым выходом 9 устройства, исток восьмого 29 дополнительного полевого транзистора связан с затвором седьмого 28 дополнительного полевого транзистора и через седьмой 30 дополнительный резистор подключен к токовому выходу 9 устройства.

На фиг. 2, в соответствии с п. 3 формулы изобретения, токовый выход 9 устройства подключен ко входу дополнительного буферного усилителя 31, выход которого является потенциальным выходом 32 устройства.

На фиг. 2, в соответствии с п. 4 формулы изобретения, сток второго 12 вспомогательного полевого транзистора соединен с общей шиной 33 источников питания.

Устойчивость ОУ фиг. 2 обеспечивается корректирующим конденсатором 34.

На фиг. 3, в соответствии с п. 5 формулы изобретения, сток второго 12 вспомогательного полевого транзистора соединен с потенциальным выходом 32 устройства.

На фиг. 2, фиг. 3, фиг. 4, в соответствии с п. 6 формулы изобретения, в качестве упомянутых в п. в п.1, п.2, п.4, п.5 полевых транзисторов используются полевые транзисторы с управляющим p-n переходом.

На фиг. 2, фиг. 3, фиг. 4, в соответствии с п. 7 формулы изобретения, в качестве упомянутых в п. 1, п. 2, п.4, п.5 полевых транзисторов используются CMOS полевые транзисторы со встроенным каналом.

На фиг. 2, фиг. 3, фиг. 4, в соответствии с п. 8 формулы изобретения, сопротивления первого 16, второго 17, третьего 19, четвертого 21, пятого 26, шестого 27 и седьмого 30 дополнительных резисторов одинаковы и имеют идентичные зависимости сопротивлений от внешних воздействий, причем стоко-затворные характеристики всех упомянутых в п. 1, п. 2, п.4, п.5, п.6, п. 7 и на фиг. 2, фиг. 3, фиг. 4 полевых транзисторов в диапазоне внешних воздействий идентичны.

Рассмотрим работу ОУ фиг. 2.

Основная особенность схемы ОУ фиг. 2 состоит в создании условий, при которых на токовом выходе 9 устройства обеспечивается полная взаимная компенсация статического тока цепи динамической нагрузки 15 и стока четвертого 14 вспомогательного полевого транзистора. Данное условие выполняется путем специального построения вспомогательного источника опорного тока 8 на основе двух параллельно включенных элементарных источниках опорного тока на третьем 22, четвертом 23, пятом 24 и шестом 25 дополнительных полевых транзисторов, а также введения дополнительных источников опорного тока на первом 18 и втором 20 дополнительных полевых транзисторах.

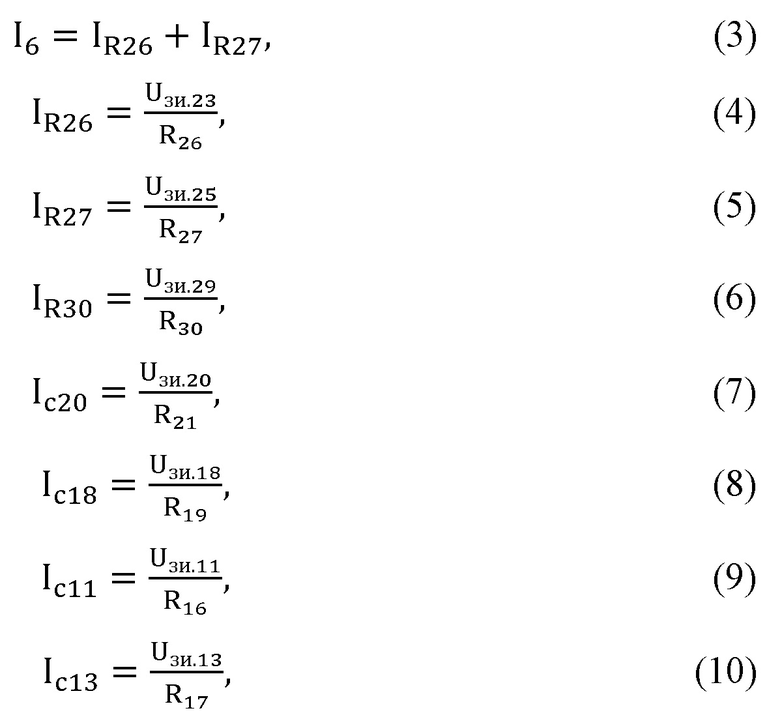

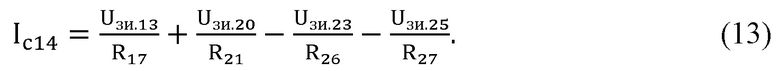

Систематическую составляющую напряжения нуля ОУ фиг. 2 по п. 1 формулы изобретения можно оценить по формуле

где ΔI9=I15-Ic14 – разность токов цепи динамической нагрузки 15 (двухполюсника 15) и тока стока четвертого 14 вспомогательного полевого транзистора при нулевом входном дифференциальном напряжении ud;

SΣ – крутизна преобразования входного дифференциального напряжения ud в выходной ток токового выхода 9.

Причем

где Sвх=Sa=Sb – крутизна стоко-затворной характеристики входных полевых транзисторов входного дифференциального каскада 3;

Ki14=1 – коэффициент передачи по току истока четвертого 14 вспомогательного полевого транзистора.

Ток I6 общей истоковой цепи входного дифференциального каскада 3, а также токи стоков первого 11 и третьего 13 вспомогательных полевых транзисторов, первого 18 и второго 20 дополнительных полевых транзисторов, определяются формулами:

где Uзи.ij – напряжение затвор-исток ij полевых транзисторов в рабочей точке I0.

Выходной ток токового выхода 9 равен разности

где I15=I30 = ток в седьмом 30 дополнительном резисторе;

Ic14 – ток стока четвертого 14 вспомогательного полевого транзистора

Причем

Если принять, что все полевые транзисторы работают при токе стока, равном I0, то можно найти

Таким образом, при идентичных резисторах и одинаковых стоко-затворных характеристиках применяемых полевых транзисторов выходной ток ошибки равен нулю (ΔI9=0). Как следствие, исходя из уравнения (1) систематическая составляющая напряжения смещения нуля предлагаемого ОУ близка к нулю.

Разомкнутый коэффициент усиления по напряжению ОУ фиг. 2 определяется следующим уравнением

где Ri9 – эквивалентное выходное сопротивление в цепи токового выхода 9.

Численные значения Ri9 определяются параллельным включением сопротивления цепи динамической нагрузки 15 и выходного сопротивления четвертого 14 вспомогательного полевого транзистора. За счет применения каскодных составных элементов на четвертом 14 и третьем 13 вспомогательных полевых транзисторах, восьмом 29 и седьмом 28 дополнительных полевых транзисторах токовый выход 9 оказывается высокоимпедансным, что при высоком входном сопротивлении дополнительного буферного усилителя 31 позволяет получить повышенные значения Kу (82-96 дБ). Данный вывод подтверждается моделированием ЛАЧХ на чертеже фиг. 6 для схемы ОУ фиг. 5, а также моделированием ЛАЧХ фиг. 12 для схемы ОУ фиг. 11.

В схеме фиг. 3, в соответствии с п. 5 формулы изобретения, за счет подключения стока второго 12 вспомогательного полевого транзистора к потенциальному выходу 32 устройства, обеспечивается идентичный статический режим по напряжению затвор-сток второго 12 и четвертого 14 вспомогательных полевых транзисторов, что уменьшает влияние эффекта модуляции длины канала на систематическую составляющую напряжения смещения нуля ОУ. Схема фиг. 3, в отличие от схемы фиг. 2, не требует общей шины источников питания 7 и 10. В этом ее преимущество.

Каскодное построение второго 12, четвертого 14 вспомогательных полевых транзисторов, а также седьмого 28 дополнительного полевого транзистора положительно сказывается на величине разомкнутого коэффициента усиления по напряжению в ОУ фиг. 4, который увеличивается (в сравнении со схемой фиг. 2) на 10-12 дБ и достигает при одном высокоимпедансном узле 96 дБ.

Таким образом, заявляемое устройство благодаря высокой симметрии статического режима по токам стока и напряжениям затвор-исток полевых транзисторов имеет (в сравнении с ОУ-прототипом) более высокие обобщенные показатели качества: улучшенные Uсм и Ку, а также малый ток потребления в статическом режиме (200мкА). При использовании СJFET транзисторов обеспечивается высокая радиационная стойкость, криогенный диапазон температур и экстремально низкий уровень шумов.

В частном случае, в соответствии с п. 7 формулы изобретения, заявляемая схема может быть выполнена на CMOS транзисторах со встроенным каналом. Для этого нужно показанные на чертежах фиг. 2, фиг. 3, фиг. 4 JFET транзисторы заменить на CMOS транзисторы со встроенным каналом. При этом все ранее описанные свойства схем JFET ОУ по Uсм, Ку сохраняются и для CMOS ОУ, при условии, что CMOS транзисторы имеют встроенный канал.

Таким образом, предлагаемый ОУ имеет существенные преимущества в сравнении с ОУ-прототипом и может быть рекомендован для практического использования в космическом приборостроении и физике высоких энергий.БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США № 5.420.540, 1995 г.

2. Патент США № 5.323.121, 1994 г.

3. Патент США № 4.293.824, 1981 г.

4. Патент США № 4.406.990, 1983 г.

5. Патент РФ 2592429, 2016 г.

6. Патент США 4.390.850, 1983 г.

7. Патент США № 5.952.882, 1999 г.

8. Патент США № 5.323.121, 1994 г.

9. Патент РФ № 2615070, 2017 г.

10. Патент США № 4.406.990, 1983 г., Fig.

11. Патент США № 7.215.200, 2007 г. Fig.

12. Патент США № 5.963.085, 1999 г.

13. Патент РФ № 2513482, 2014 г.

14. Патент РФ № 2595926, 2016 г.

15. Патент РФ № 2668968, 2018 г.

16. Патент РФ № 2684500, 2019 г., Fig. 1, Fig.

17. Патент РФ № 2319291, 2008 г.

18. Close J. P., Santos F. A JFET input single supply operational amplifier with rail-to-rail output //IEEE Bipolar Circuits and Technology Meeting. – 1993. – pp. 149-150.

19. Dimitri Danyuk "Linear Integrated Systems Headphone Amplifier Evaluation Board", Linear Integrated Systems, p. 1-17. URL: http://www.linearsystems.com/lsdata/others/Headphone_Amplifier_Evaluation_Board.pdf

20. Патент США № 6.750.715, 2004 г.

21. Патент США № 6.714.076, 2004 г.

22. Патент РФ № 2624565, 2017 г.

23. Патент РФ № 2621286, 2017 г.

24. Prokopenko N. N., Pakhomov I. V., Zhuk A. A. Low temperature and radiation resistant JFET differential amplifiers circuits synthesis with increased common-mode rejection ratio //IOP Conference Series: Materials Science and Engineering. – IOP Publishing, 2020. – Т. 862. – №. 3. – С. 032109.

25. Патент США № 6.825.721, 2004 г.

26. Патент США № 6.788.143, 2004 г.

27. Патент США № 7.570.113, 2009 г.

28. Shor J. S., Luria K. Miniaturized BJT-based thermal sensor for microprocessors in 32-and 22-nm technologies //IEEE journal of solid-state circuits. – 2013. – Т. 48. – №. 11. – С. 2860-2867.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННОЙ КРУТИЗНОЙ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2770915C1 |

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2770913C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ «ПЕРЕГНУТОГО» КАСКОДА И КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ | 2022 |

|

RU2773907C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2022 |

|

RU2784666C1 |

| ПРОМЕЖУТОЧНЫЙ КАСКАД CJFET ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С ПАРАФАЗНЫМ ТОКОВЫМ ВЫХОДОМ | 2019 |

|

RU2712411C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2021 |

|

RU2766861C1 |

| Арсенид-галлиевый операционный усилитель с малым напряжением смещения нуля | 2023 |

|

RU2812914C1 |

| Прецизионный арсенид-галлиевый операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля и повышенным коэффициентом усиления | 2023 |

|

RU2813370C1 |

| Арсенид-галлиевый операционный усилитель для работы в широком диапазоне температур | 2023 |

|

RU2814685C1 |

Изобретение относится к области аналоговой микроэлектроники и может быть использовано в различных аналоговых и аналого-цифровых интерфейсах – активных RC-фильтрах, нормирующих преобразователях и т.п., в том числе работающих в условиях низких температур и воздействия радиации. Технический результат: создание радиационно-стойкого и низкотемпературного операционного усилителя, который за счет высокой самоустанавливающейся симметрии статического режима по токам стока и напряжениям затвор-сток применяемых полевых транзисторов обеспечивает малый уровень систематической составляющей напряжения смещения нуля и повышенные значения коэффициента усиления по напряжению. Технический результат достигается за счет создания условий, при которых на токовом выходе (9) устройства обеспечивается полная взаимная компенсация статического тока цепи динамической нагрузки (15) и стока четвертого (14) вспомогательного полевого транзистора. Данное условие выполняется путем специального построения вспомогательного источника опорного тока (8) на основе двух параллельно включенных элементарных источников опорного тока на третьем (22), четвертом (23), пятом (24) и шестом (25) дополнительных полевых транзисторах, а также введения дополнительных источников опорного тока на первом (18) и втором (20) дополнительных полевых транзисторах. 7 з.п. ф-лы, 13 ил.

1. Операционный усилитель на комплементарных полевых транзисторах, содержащий первый (1) и второй (2) входы входного дифференциального каскада (3) с первым (4) и вторым (5) токовыми выходами и токовым входом (6) общей истоковой цепи для установления статического режима, который связан с первой (7) шиной источника питания через вспомогательный источник опорного тока (8), токовый выход (9) устройства, вторую (10) шину источника питания, первый (11) вспомогательный полевой транзистор, сток которого соединен с истоком второго (12) вспомогательного полевого транзистора и подключен к первому (4) токовому выходу входного дифференциального каскада (3), третий (13) вспомогательный полевой транзистор, сток которого соединен с истоком четвертого (14) вспомогательного полевого транзистора и подключен ко второму (5) токовому выходу входного дифференциального каскада (3), цепь динамической нагрузки (15) на полевых транзисторах, включенную между стоком четвертого (14) вспомогательного полевого транзистора, связанным с токовым выходом (9) устройства и первой (7) шиной источника питания, отличающийся тем, что затворы первого (11) и третьего (13) вспомогательных полевых транзисторов соединены со второй (10) шиной источника питания, исток первого (11) вспомогательного полевого транзистора связан со второй (10) шиной источника питания через первый (16) дополнительный резистор и соединен с затвором второго (12) вспомогательного полевого транзистора, исток третьего (13) вспомогательного полевого транзистора связан со второй (10) шиной источника питания через второй (17) дополнительный резистор и соединен с затвором четвертого (14) вспомогательного полевого транзистора, к первому (4) токовому выходу входного дифференциального каскада (3) подключен сток первого (18) дополнительного полевого транзистора, затвор которого соединен со второй (10) шиной источника питания, а исток связан со второй (10) шиной источника питания через третий (19) дополнительный резистор, ко второму (5) токовому выходу входного дифференциального каскада (3) подключен сток второго (20) дополнительного полевого транзистора, затвор которого соединен со второй (10) шиной источника питания, а исток связан со второй (10) шиной источника питания через четвертый (21) дополнительный резистор, источник опорного тока (8) выполнен на основе третьего (22), четвертого (23), пятого (24) и шестого (25) дополнительных полевых транзисторов, а также пятого (26) и шестого (27) дополнительных резисторов, причем стоки третьего (22) и пятого (24) дополнительных полевых транзисторов соединены с первой (7) шиной источника питания, затворы четвертого (23) и шестого (25) дополнительных полевых транзисторов связаны с токовым входом (6) общей истоковой цепи для установления статического режима входного дифференциального каскада (3), сток четвертого (23) дополнительного полевого транзистора соединен с истоком третьего (22) дополнительного полевого транзистора, затвор третьего (22) дополнительного полевого транзистора соединен с истоком четвертого (23) дополнительного полевого транзистора и через пятый (26) дополнительный резистор подключен к токовому входу (6) общей истоковой цепи для установления статического режима входного дифференциального каскада (3), затвор пятого (24) дополнительного полевого транзистора соединен с истоком шестого (25) дополнительного полевого транзистора и через шестой (27) дополнительный резистор подключен к токовому входу (6) общей истоковой цепи для установления статического режима входного дифференциального каскада (3).

2. Операционный усилитель на комплементарных полевых транзисторах по п. 1, отличающийся тем, что цепь динамической нагрузки (15) на полевых транзисторах содержит седьмой (28) и восьмой (29) дополнительные полевые транзисторы, а также седьмой (30) дополнительный резистор, причем сток восьмого (29) дополнительного полевого транзистора соединен с истоком седьмого (28) дополнительного полевого транзистора, затвор восьмого (29) дополнительного полевого транзистора соединен с токовым выходом (9) устройства, исток восьмого (29) дополнительного полевого транзистора связан с затвором седьмого (28) дополнительного полевого транзистора и через седьмой (30) дополнительный резистор подключен к токовому выходу (9) устройства.

3. Операционный усилитель на комплементарных полевых транзисторах по п. 1, отличающийся тем, что токовый выход (9) устройства подключен ко входу дополнительного буферного усилителя (31), выход которого является потенциальным выходом (32) устройства.

4. Операционный усилитель на комплементарных полевых транзисторах по п. 1, отличающийся тем, что сток второго (12) вспомогательного полевого транзистора соединен с общей шиной (33) источников питания.

5. Операционный усилитель на комплементарных полевых транзисторах по п. 3, отличающийся тем, что сток второго (12) вспомогательного полевого транзистора соединен с потенциальным выходом (32) устройства.

6. Операционный усилитель на комплементарных полевых транзисторах по пп. 1, 2, 4, 5, отличающийся тем, что в качестве упомянутых в пп. 1, 2, 4, 5 полевых транзисторов используются полевые транзисторы с управляющим p-n-переходом.

7. Операционный усилитель на комплементарных полевых транзисторах по пп. 1, 2, 4, 5, отличающийся тем, что в качестве упомянутых в пп. 1, 2, 4, 5 полевых транзисторов используются CMOS полевые транзисторы со встроенным каналом.

8. Операционный усилитель на комплементарных полевых транзисторах по пп. 1-7, отличающийся тем, что сопротивления первого (16), второго (17), третьего (19), четвертого (21), пятого (26), шестого (27) и седьмого (30) дополнительных резисторов одинаковы и имеют идентичные зависимости сопротивлений от внешних воздействий температуры, причем стоко-затворные характеристики всех упомянутых в пп. 1-7 полевых транзисторов в диапазоне внешних воздействий идентичны.

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С «ПЛАВАЮЩИМ» ВХОДНЫМ ДИФФЕРЕНЦИАЛЬНЫМ КАСКАДОМ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2741055C1 |

| НИЗКОТЕМПЕРАТУРНЫЙ ДВУХКАСКАДНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2721942C1 |

| US 7570113 B2, 04.08.2009 | |||

| US 6825721 B2, 30.11.2004 | |||

| ИНСТРУМЕНТАЛЬНЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2016 |

|

RU2624565C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2017 |

|

RU2668968C1 |

| ПРЕЦИЗИОННЫЙ ДВУХКАСКАДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2615070C1 |

Авторы

Даты

2022-03-16—Публикация

2021-09-08—Подача