.

LA

ты

fe

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения чисел в системе остаточных классов | 1982 |

|

SU1037244A1 |

| Устройство для сравнения чисел в системе остаточных классов | 1984 |

|

SU1160394A1 |

| Сумматор в системе остаточных классов | 1983 |

|

SU1111170A1 |

| Устройство для сравнения чисел в системе остаточных классов | 1984 |

|

SU1224803A1 |

| Устройство для сравнения чисел в системе остаточных классов | 1983 |

|

SU1145338A1 |

| Устройство для обнаружения ошибок в системе остаточных классов | 1980 |

|

SU878061A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Арифметическое устройство по модулю | 1983 |

|

SU1120325A1 |

| Устройство для сравнения чисел в системе остаточных классов | 1983 |

|

SU1121670A1 |

| Устройство для исправления ошибок в системе остаточных классов | 1980 |

|

SU932499A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах связи и обработки информации, оперирующих с модулярными кодами. Целью изобретения является расширение области применения за счет обнаружения и коррекции ошибок. Устройство содержит блоки 3 и 10 хранения констант, вычитатели 4 и 11, группу вычитателей 5, схему 6 сравнения, группу элементов И 8 и шифратор 9. 1 ил., 3 табл.

5

о-С1

п

#

/

0х

пз

о

пЙВ

X

:

Ч

Јь CJ О О Ю

Изобретение относится к вычислительной технике и может быть использовано в системах связи, оперирующих с модулярны- ми кодами (кодами в системе остаточных классов).

Известно устройство для коррекции ошибок, содержащее блоки памяти констант нулевизации и ошибок сумматора.

Недостатком устройства является низкое быстродействие обнаружения и коррекции ошибки.

Наиболее близким к предлагаемому является устройство для сравнения чисел в системе остаточных классов, содержащее первый и второй выходные регистры, состоящее из п подрегистров, входы которых являются входами первого и второго чисел соответственно, первый и второй сумматоры, первую и вторую группы элементов ИЛИ, схему сравнения, первую и вторую группы элементов ИЛИ, схему сравнения, первую и вторую группы элементов И, первую и вторую группы по N сумматоров (N

п +1

П PI, п-количество оснований системы

I 1

остаточных классов; Pi - основание), третью и четвертую, пятую и шестую группы элементов И, первый и второй выходные регистры, первый и второй блоки хранения констант нулевизации по n-му основанию, причем первые входы первого и второго сумматоров подключены соответственно к выходам первого и второго регистров, адресные входы блока хранения констант нулевизации по n-му основанию подключены к выходам n-х подрегистров соответственно первого и второго входных регистров, а выходы - к вторым входам соответственно первого и второго сумматоров, выходы которых подключены соответственно к первым входам сумматоров первой и второй групп, вторые входы которых соответственно попарно объединены и являются группой входов констант устройства, а выходы подключены соответственно к первой и второй группам входов схемы сравнения, выход Равно которой подключен к первым входам элементов И первой и второй групп, вторые входы которых подключены соответственно к входам первого и второго регистров, первые входы элементов И третьей и пятой, четвертой и шестой групп соответственно попарно объединены и подключены соответственно к выходам элементов И первой и второй групп, вторые входы элементов И треть.ей и четвертой, пятой и шестой групп соответственно объединены и подключены к выходам Меньше и Больше схемы сравнения, выходы элементов И третьей и

шестой, четвертой и пятой групп подключены попарно к входам соответствующих элементов ИЛИ первой и второй групп, выходы которых подключены к соответствующим

входам соответственно первого и второго выходных регистров, выходы которых являются соответственно выходами Макс и Мин устройства.

Недостатком данного устройства является невозможность обнаружения и коррекция ошибок.

Цель изобретения - расширение области применения за счет обнаружения и коррекции ошибок.

Цель достигается тем, что в устройство для обработки информации, представленной в системе остаточных классов, содержащее первый и второй блоки хранения констант, первый и второй вычислители,

группу вычитателей, схему сравнения и группу элементов И, причем информационные входы группы устройства соединены с соответствующими входами уменьшаемого группы первого вычитателя, входы вычитаемого группы которого соединены с соответствующими выходами группы первого блока хранения констант, адресный вход которого соединен со старшим информационным входом группы устройства, входы констант

группы которого соединены с входами вычитаемых соответствующих вычитателей груп- пы, входы уменьшаемых которых соединены с выходом первого вычитателя, выходы вычитателей группы соединены с

соответствующими входами первой группы схемы сравнения, выход Больше которой соединен с первыми входами элементов И группы, выходы группы второго блока хранения констант соединены с соответствующими входами вычитаемого группы второго вычитателя, введен шифратор, причем входы задания унитарного кода максимального числа группы.устройства соединены с соответствующими входами второй группы схемы

5 сравнения, выходы вычитателей группы - с вторыми входами соответствующих элементов И группы, выходы которых соединены с соответствующими входами группы шифратора, выход которого соединен с адресным

0 входом второго блока хранения констант, информационные входы группы устройства соединены с соответствующими входами уменьшаемого второго вычитателя, выход которого является выходом устройства.

5 В основу работы предлагаемого устройства положен следующий принцип.

Наибольшее число в СОК с основаниями Pit Ра, РзPn, Pn+i, Рп+2 можно представить следующим образом:

В-Р-1.гдеР П Pi . (1) 1 1

ЧислаА-( си tcs,...,0h.ah + i....ah+r) и В можно представить в виде однорядово- го кода

KN {ZNZN-i..,Z2Zi} (2)

(пв) // /

KN {ZNZN-i...Z2Zi} (3)

n+r

где N П Pk. K 1 7

(Zi 1, ,М,), ( , N,).

Алгоритм поступления однорядового кода Ami - 0 Zi Ami - mi Z2

Ami - 2 mi Zsи т.д.,

где

Am, A-ai (a(),aЈ),... t

apli,0.aM.,f...,afl affi-г);

Bmi В -# ($ ) ,fЈ), ... ,/$L i , 0 ,

/й-i/,... Ж,

r r

где ai (ai. 32aian +r);

,# ....#,...Ј n+r), .

ZOA - 0, если Am) - пд mi 0;

ZnA -1,если Ami ПА mi, и для Zne тоже.

Тогда, используя (1) и сравнивая (2) и (3),

(ПА) (пв) можно сказать, что если KN KN

(ПА) (пв) число правильное, если KN KN

число неправильное.

Провели обнаружение ошибки. Если рассмотреть однорядовый код, то можно заметить, что положение ZnA 0 показывает интервал, в котором находится число. Тогда, используя теорему о однозначности

определения местоположения и величины ошибки при выполнении соотношения

Рп+1 2РпРп-1

(4)

при одном проверочном символе или

P|Pj Pn+1 Pn+2

(5)

для двух оснований проверочных.

Таким образом, используя выражения (1), (2), (3). (4). (5), возможно путем сравнения обнаружить и исправить ошибку.

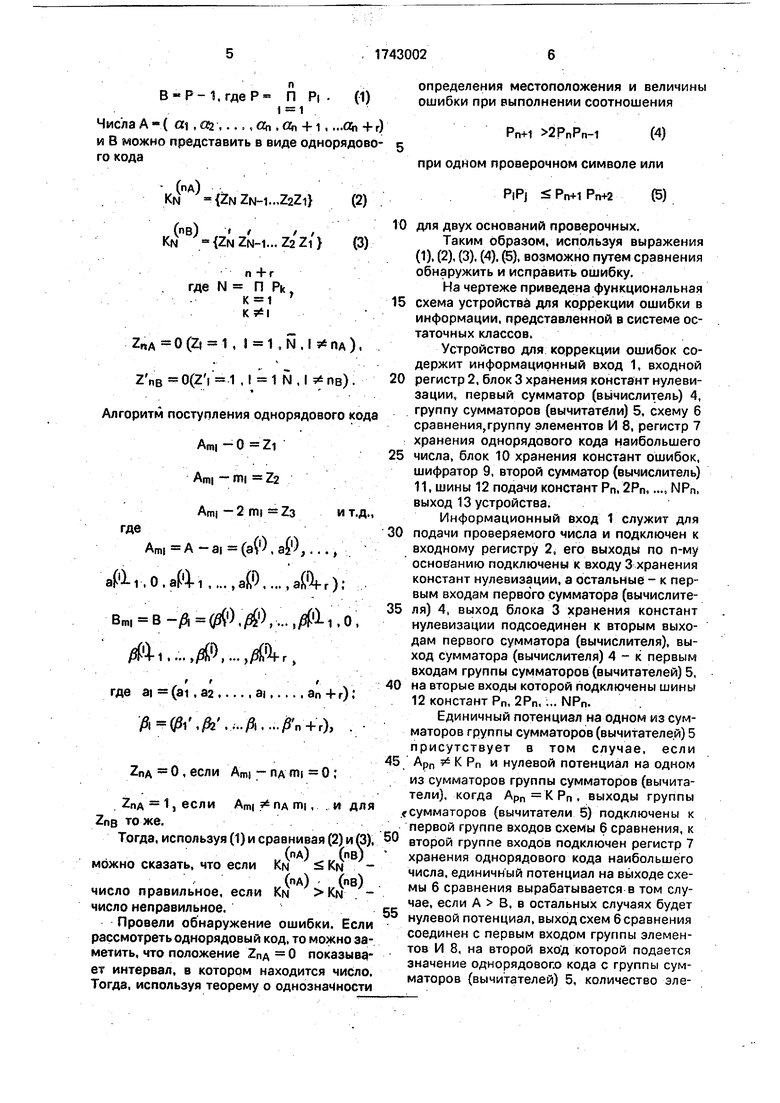

На чертеже приведена функциональная

схема устройства для коррекции ошибки в информации, представленной в системе остаточных классов.

Устройство для коррекции ошибок содержит информационный вход 1, входной

регистр 2, блок 3 хранения констант нулеви- зации, первый сумматор (вычислитель) 4, группу сумматоров (вычитатбли) 5, схему 6 сравнения группу элементов И 8, регистр 7 хранения однорядового кода наибольшего

числа, блок 10 хранения констант ошибок, шифратор 9, второй сумматор (вычислитель) 11, шины 12 подачи констант Pn, 2Pn, ...t NPn, выход 13 устройства.

Информационный вход 1 служит для

подачи проверяемого числа и подключен к входному регистру 2, его выходы по п-му основанию подключены к входу 3 хранения констант нулевизации, а остальные - к первым входам первого сумматора (вычислителя) 4, выход блока 3 хранения констант нулевизации подсоединен к вторым выходам первого сумматора (вычислителя), выход сумматора (вычислителя) 4 - к первым входам группы сумматоров (вычитателей) 5,

на вторые входы которой подключены шины 12 констант Р„, 2РП,... NPn.

Единичный потенциал на одном из сумматоров группы сумматоров (вычитателей) 5 присутствует в том случае, если

Арп & К Рп и нулевой потенциал на одном

из сумматоров группы сумматоров (вычитатели), когда Арп К Рп , выходы группы

сумматоров (вычитатели 5) подключены к

первой группе входов схемы б сравнения, к

второй группе входов подключен регистр 7 хранения однорядового кода наибольшего числа, единичный потенциал на выходе схемы 6 сравнения вырабатывается в том случае, если А В. в остальных случаях будет

нулевой потенциал, выход схем 6 сравнения соединен с первым входом группы элементов И 8, на второй вход которой подается значение однорядового кода с группы сумматоров {вычитателей) 5, количество элементов И определяется величиной N, выход схем И подключен к шифратору 9, преобразующему унитарный код в код интервала, по которому произошла ошибка, что позволяет реализовать блок 10 хранения констант ошибок на меньшем количестве ПЗУ, так как количество входов шифратора числа равно N, а выходов будет L logaN.

Блок 10 хранения констант ошибок может .быть реализован на ПЗУ, их количество будет зависеть от количества разрядов од- норядового кода и количества оснований системы СОВ, Количество выходов блока 10 соответствует количеству разрядов входного регистра, и они подключены к вторым входам второго сумматора (вычислители), потенциал на выходных шинах, соответствующий ошибке, появляется только в случае единичного потенциала схемы 6 сравнения, соответствующего сигналу Больше. На первые входы второго сумматора (вычислителя) II подается значение проверяемого числа с входного регистра 2, выход сумматора 11 является выходом устройства.

Устройство работает следующим образом.

В исходном состоянии на второй вход группы 5 сумматоров (вычитателей) подаются значения констант Рп, 2РПпРп и по

шинам 12 на вторую группу входов схемы б сравнения подается однорядовый код наибольшего числа, записанного в регистре 7.

Устройство готово к работе, проверяемое число по входу 1 поступает в регистр 2, значение по основанию п поступает на вход блока 3 хранения констант нулевизации. Сумматор (вычислитель) 4 производит операцию вычитания А - an и на его выходе появится число Арп -числу А, приведенному по основанию. На выходе группы 5 сумматоров (вычитателей), производящих также операцию вычитания Арп - Рп, Арп - 2Рп, .... Арп - пРп, образуется однорядовой код, который подается на схему 6 сравнения. Результат сравнения подается на выход схемы 6 сравнения в том случае, когда число А будет меньше либо равно В, на выходе схемы 6 сравнения будет нулевой потенциал, и на сумматор (вычислитель) 11 подается ну- левая кодовая комбинация в том случае, если произошла о.шибка, т.е. А В, единичный потенциал открывает группу И, и однорядовый код поступает на шифратор. Шифратор преобразует данный код, и на выходе образуется кодовая комбинация, соответствующая определенному интервалу, блок 10 хранения констант ошибок согласно данного номера на сумматор (вычислитель) 11 выдает кодовую комбинацию ошибки, на

выходе сумматора (вычислителя) 11 образуется правильное число.

Таким образом, через время окончания переходных процессов на выходе 13 выда- ется правильное проверяемое число.

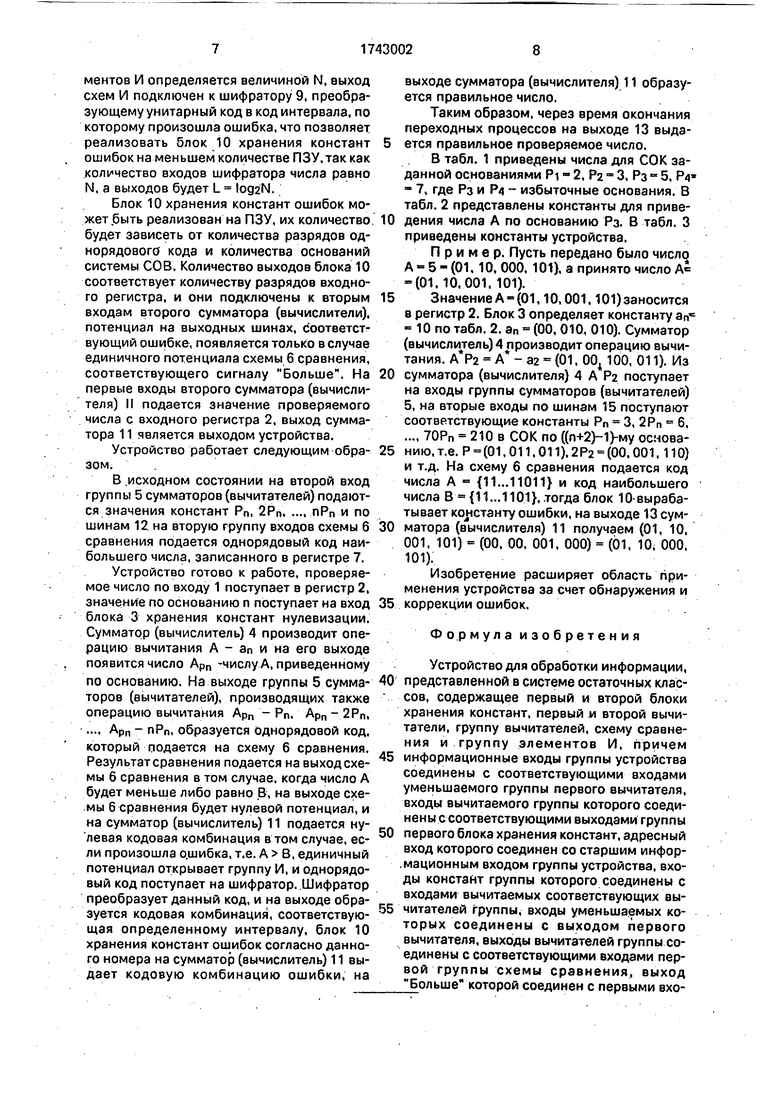

В табл. 1 приведены числа для СОК заданной основаниями Pi - 2, Р2 3, Рз 5, Р«

-7, где Рз и Р4 - избыточные основания. В табл. 2 представлены константы для приведения числа А по основанию Рз. В табл. 3

приведены константы устройства.

Пример. Пусть передано было число

А - 5 - (01, 10, 000, 101), а принято число А

(01.10,001, 101). Значение А (01,10,001.101) заносится

в регистр 2. Блок 3 определяет константу апв

-10 по табл. 2. ап - (00, 010, 010). Сумматор (вычислитель) 4 производит операцию вычитания. - А - 32 - (01, OOj, 100, 011). Из

сумматора (вычислителя) 4 А Рг поступает на входы группы сумматоров (вычитателей) 5, на вторые входы по шинам 15 поступают соответствующие константы Рп 3, 2РП 6, ,.., 70РП 210 в СОК по ((п+2Н)-му основанию.т.е. Р-(01.011.011).2Р2-(00.001,110) и т.д. На схему 6 сравнения подается код числа А {11...11011} и код наибольшего числа В {11... 1101}. .тогда блок 10-выраба- тывает константу ошибки, на выходе 13 сумматора (вычислителя) 11 получаем (01, 10, 001, 101) (00, 00, 001, 000) - (01, 10. 000. 101).

Изобретение расширяет область применения устройства за счет обнаружения и

коррекции ошибок.

Формула изобретения

Устройство для обработки информации,

представленной в системе остаточных классов, содержащее первый и второй блоки хранения констант, первый и второй вычи- татели, группу вычитателей, схему сравнения и группу элементов И. причем

информационные входы группы устройства соединены с соответствующими входами уменьшаемого группы первого вычитателя, входы вычитаемого группы которого соединены с соответствующими выходами группы

первого блока хранения констант, адресный вход которого соединен со старшим инфор- .мационным входом группы устройства, входы констант группы которого соединены с входами вычитаемых соответствующих вычитателей группы, входы уменьшаемых которых соединены с выходом первого вычитателя, выходы вычитателей группы соединены с соответствующими входами первой группы схемы сравнения, выход Чэольше которой соединен с первыми входами элементов И группы, выходы группы второго блока хранения констант соединены с соответствующими входами вычитаемого группы второго вычитателя, отличающееся тем, что, с целью расширения области применения за счет обнаружения и коррекции ошибок, оно содержит шифратор, причём входы задания унитарного кода максимального числа группы устройства соединены с соответствующими входами второй группы схемы сравнения, выходы

вычитателей группы соединены с вторыми входами соответствующих элементов И группы, выходы которых соединены с соответствующими входами группы шифратора, выход которого соединен с адресным входом второго блока хранения констант, информационные входы группы устройства соединены с соответствующими входами уменьшаемого второго вычитателя, выход которого является выходом устройства.

Таблица 1

Таблица 2

Таблица 3

| Устройство для сравнения чисел в системе остаточных классов | 1984 |

|

SU1160394A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| Устройство для сравнения чисел в системе остаточных классов | 1982 |

|

SU1037244A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-06-23—Публикация

1990-06-12—Подача