Изобретение относится к автоматике и вычислительной технике и может быть использовано для обработки данных в схемах автоматики и специализированных ЭВМ, работающих в системе остаточных классов (СОК).

Цель изобретения - упрощение точности сравнения операндов в СОК.

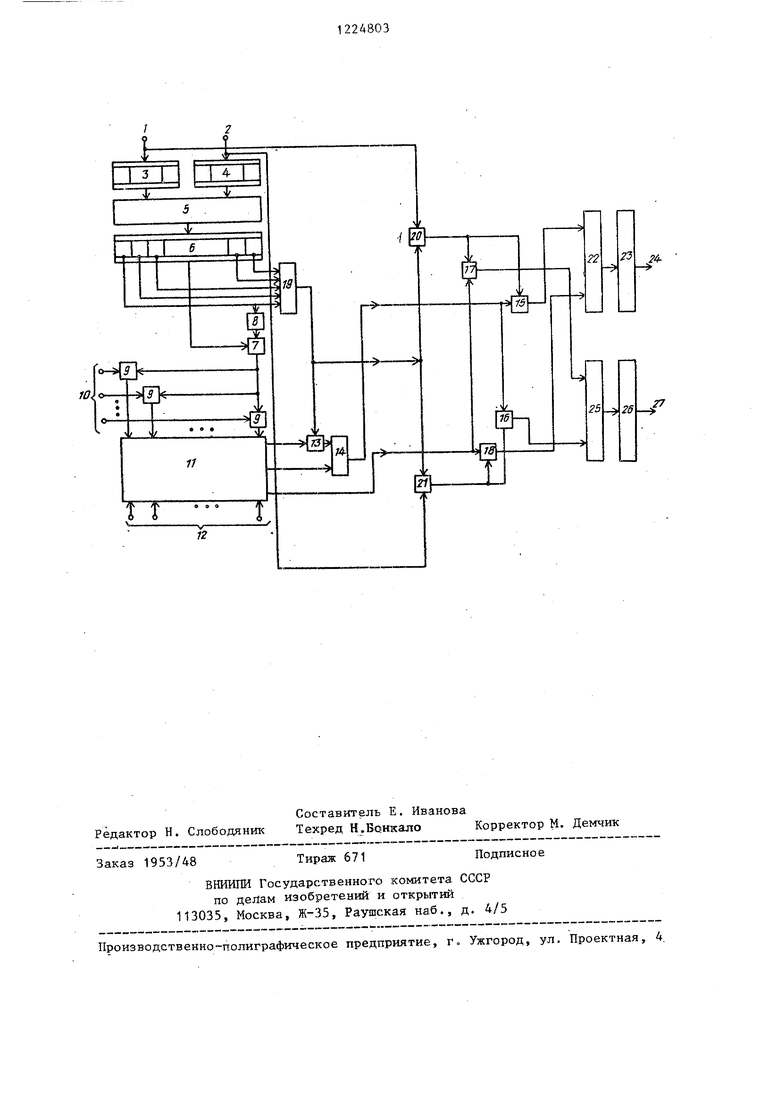

На чертеже представлена структурная схема устройства.-.

Устройство содержит входы первого и второго сравниваемых чисел соответственно 1 и 2, входные регистры 3 и А, сумматор 5, регистр 6, состоящий из п подрегистров, сумматор 7, элементы ИЛИ 25 поступает на вход блок 8 .хранения констант нулевизацин, регистра 26 наименьшего числа, а группу сумматоров 9, входы 10 конс10

ное однорядовым кодом, в котором н к-ом (на (к + 1)-м справа) месте дет ноль, а на остальных - единицы поступает на первую группу входов схемы 11 сравнения. На группу вход схемы 11 поступает также слово дли N (соответствующее числу Р, ), в к ром на первом месте (второе справа будет ноль (Р -т Р, 0, при m а на остальных - единицы. Если к (и Р( ) то с выхода Больше сх мы 11 сигнал открывает элементы И и 18, и с входа 1 устройства опе ранд А через элементы И 20 и 17,

операнд В с входа 2 устройства че элементы И 21 и 18, элементы ИЛИ поступает на вход регистра 23 наи

тант , схему 11 сравнения, входы 12 кода заданного интервала, элемент 13

операнд В с входа 2 устройства чер элементы И 21 и 18, элементы ИЛИ 2 поступает на вход регистра 23 наизапрета, элемент ИЛИ 14, группы эле- большего числа. Если к 1, то с

ментов И 15, 16, 17 и 18 элемент НЕ-И 19, группы элементов И 20 и 21, группу элементов ИЛИ 22, регистр 23 наибольшего числа, выход 24 максимального числа, группу элементов ИЛИ 25, регистр 26 наименьшего числа, выход 27 минимального числа.

Устройство работает следующим . образом.

По входам 1 и 2 соответственно первое А (а,, а , ..., а,) и второе В (Ь , Ь , .., bf,) сравниваемые числа заносятся соответственно во входные регистры 3 и 4, с которых они

выхода Равно схемы 11 сигнал чер элемент ИЛИ 14 открывает элементы И 15 и 16, и с входа 1 операнд А рез элементы И 20 и 15, элементы

ИЛИ 22 поступает на вход регистра наибольшего числа, а операнд 8 с входа 2 ч ерез элементы И 21, 16, элементы ИЛИ -25 поступает на вход регистра 26 наименьшего числа. Есл

30 к О и (А-В jmod Р т О, то с выхо Меньше схемы 11 сигнал через открытый элемент 13 запрета (отсут ствует сигнал с выхода элемента НЕ-И 19, так как (А-В) mod Р 0)

одновременно поступают на сумматор 5, 35 элемент ИЛИ 14 открывает элементы

И 15, 16 и в дальнейшем работа уст ройства идентична режиму Равно, описанному вьпце.

с выхода которого значение и

п

(А-В) mod Р (где Р П Р;), зано1 1

сится в регистр 6. Блок хранения констант нулевизации по значению у, (А - В) mod Р (,, , ..., „ ) определяет соответствующую константу в виде J, (у,, У, , Уг , ..., у, ). Сумматор 7 выполняет операцию вычитания в СОК л (и - ( ) mod Р, , и это значение поступает на первые входы сумматоров 9, на вторые входы .которых по шинам 10 поступают соответствующие константы О, Р,, 2Р(, ..., 50 нули, что свидетельствует о равен- (N-1)P, , представленные в СОК с осно- стве .операндов-А и В с точностью

ваниями 12, Р, ..., Р. В результате

на выходе только одного сумматора 9

появится ноль, т.е. и

кР, О. В

этом случае с выходов сумматоров 9

fi слово длиной N Пр. представленЬ2

элементы ИЛИ 25 поступает на вход регистра 26 наименьшего числа, а

ное однорядовым кодом, в котором на к-ом (на (к + 1)-м справа) месте будет ноль, а на остальных - единицы, поступает на первую группу входов схемы 11 сравнения. На группу входов схемы 11 поступает также слово длиной N (соответствующее числу Р, ), в котором на первом месте (второе справа) будет ноль (Р -т Р, 0, при m 1), а на остальных - единицы. Если к 1 (и Р( ) то с выхода Больше схемы 11 сигнал открывает элементы И 17 и 18, и с входа 1 устройства операнд А через элементы И 20 и 17,

элементы ИЛИ 25 поступает на вход регистра 26 наименьшего числа, а

операнд В с входа 2 устройства через элементы И 21 и 18, элементы ИЛИ 22 поступает на вход регистра 23 наибольшего числа. Если к 1, то с

выхода Равно схемы 11 сигнал через элемент ИЛИ 14 открывает элементы И 15 и 16, и с входа 1 операнд А через элементы И 20 и 15, элементы

ИЛИ 22 поступает на вход регистра 23 наибольшего числа, а операнд 8 с входа 2 ч ерез элементы И 21, 16, элементы ИЛИ -25 поступает на вход регистра 26 наименьшего числа. Если

к О и (А-В jmod Р т О, то с выхода Меньше схемы 11 сигнал через открытый элемент 13 запрета (отсутствует сигнал с выхода элемента НЕ-И 19, так как (А-В) mod Р 0),

И 15, 16 и в дальнейшем работа устройства идентична режиму Равно, описанному вьпце.

Пусть k )т.е. А-В

40 О(mod Р) ), в этом случае на выходе элемента НЕ-И 19 (на входе элемента НЕ-И 19 присутствует сигнал лишь тогда, когда на всех его входах сигналы отсутствуют, т.е. когда в

45 регистр 6 записан нулевой операнд с СОК) присутствует сигнал, который закрывает элемент 13 запрета и закрывает элементы И 20 и 21. В этом случае в регистрах 23 и 26 содержатся

до единицы.

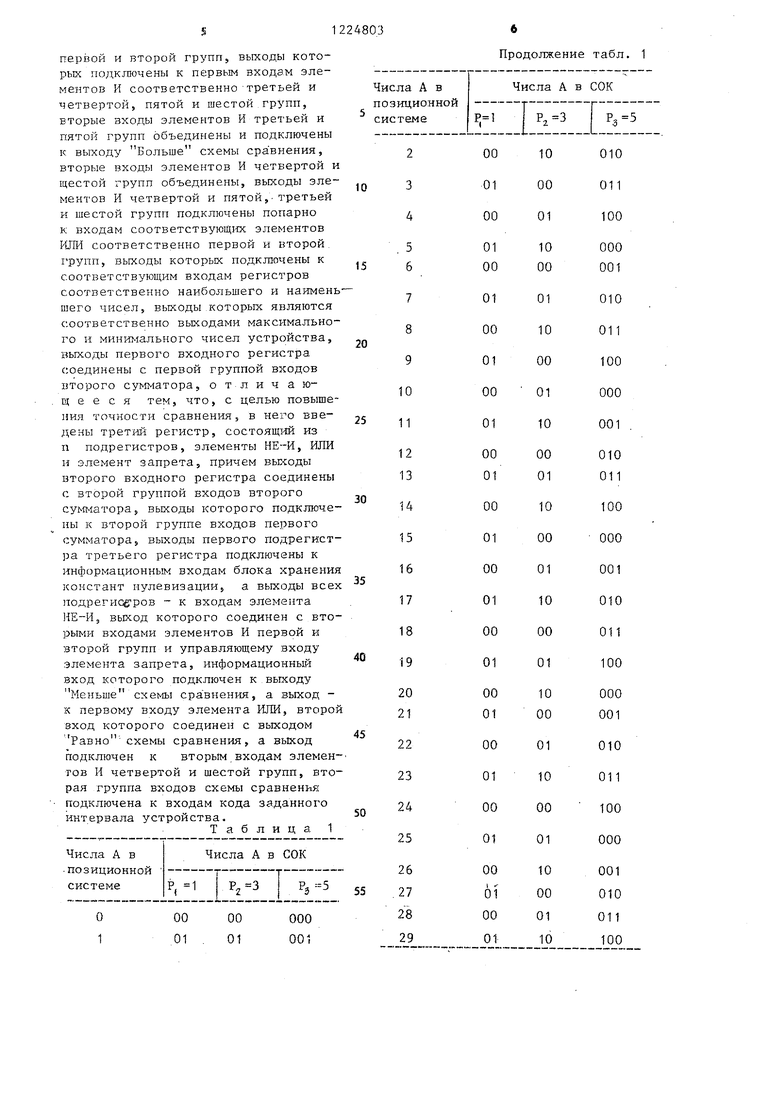

Рассмотрим пример конкретного выполнения операции сравнения чисел 515 А и и для СОК, заданной основаниями Р, 2, Р2 3, Р, 5 (см. табл. 1).

Пример 1 . А2 (00, 01 , 010), Ъ,, (01, 10, 011). Операнды

Аи В. заносятся соответственно в регистры 3 и 4. Сумматор 5 определяет значение 4 (А , - В,,) mod 30

производит операцию вычи- Д - 5 в СОК и операнд

4 (А, - В,,

(01, 10, 100, которое поступает на вход регистра 6. Блок 8 по значению

, 01 определяет константу в виде

У, (01, 01, 001) (см. табл. 2). Сумматор 7 танин д

л (00, 01, 011), кратньй Р, 2 поступает на первые входы сумматоров 9, на вторые входы которых по шинам 10 поступают константы О, Р , 2P , ..., 1А Р, (см. табл. 3). Так как

А - 14-Р, О, то на первую группу входов схемы 11 поступает однорядо- вый код длиной в N 15 (от нулевого до четырнадцатого) двоичных разрядов 011111111111111, где на четырнадцато (k 14)месте (k + 1 15) ноль, а на остальных местах - единицы. На вторую группу входов схемы 11 (по шинам 12) подается код в виде 111111111111101 (, О, m 1). Так как к 14 1, то с выхода Больше схемы 11 сигнал открывает

элементы И 17 и 18. Операнд А через элементы И 20 и 17 и элементы ИЛИ 25 поступает в регистр 26 наименьшего числа, а операнд В через элементы И 21 и 18 и элементы ИЖ 22 поступает в регистр 23 наибольшего числа. Соответствие между выходными сигналами схемы 12, элемента НЕ-И 19 и соотношением между сравниваемыми операндами А и В приведены ниже, схемы 12

Выходы

Меньше ( й Р, ) Равно ( й р )

Больше (д Р, )

Выход элемента НЕ-И 19

Л О

Проверка: А 2 В Пример 2,

24

гэ

Для А, В

Для А, .В А В

(01, 10,

011), В22 (00, 01, 010). В этом случае с выхода сумматора 5 значение Л (А23 - Bjj ) mod 30 (01 , О, 1 , 001) поступает на второй вход сумматора 7, на первьй вход которого поступает константа из блока 8 у, (01, 01, 001) см. табл. 2). С выхода сумматора 7 значение д Д-у (00, 00, 000) поступает на первые

1224803

входы сумматора 9. Так как д О PJ О (см. табл. 3), то на первую группу входов поступает слово вида 111111111111110 (k 0). В этом слу- i чае ,Toc выхода

Меньше схемы 11 сигнал через откры

тый элемент 13 запрета, элемент ИЛИ 14 открывает элементы И 15 и 16. Операнд Агэ через элементы И 20 и 15 и элементы ИЛИ 22 поступает в регистр 23 наибольшего числа, а операнд В через элементы И 21 и 16 и элементы ИЛИ 25 поступает на вход регистра 26 наименьшего числа.

Проверка: 22

Пример 3. Агэ (01, 10, 011), В2 (01, 10, 011).

Сумматор 5-определяет результат Д (mod 30), который заносится в регистр 6, так как все остатки операнда Д (00, 00, 000) равны нулю, то на выходе элемента НЕ-И 19 присутствует сигнал, который закрывает элемент 13 запрета и закрьтает элементы И 20 и 21. В регистрах 23 и 26 содержатся нули, что свидетельствует о равенстве сравниваемых операндов.

Проверка: В

30

Формула изобретения

Устройство для сравнения чисел в системе остаточных классов, содержащее первый и второй входные регистры, входы которых являются входами первого и второго сравниваемых чисел устройства соответственно, блок хранения констант нулевизации, сумматоры, группу из N сумматоров ( где

Т1

N -D Р; 1 количество оснований

системы остаточньпс классов (СОК) , Р; - L е - основание СОК), схему

сравнения, группу элементов И, груп- пу элементов ИЛИ, регистры наибольшего и наименьшего чисел, причем выходы блока хранения констант нулевизации подключены к первой группе входов первого сумматора, выходы которого подключены к первым группам входов сумматоров группы, вторые группы входов которых являются группой входов констант устройства, а выходы подключены к первой группе входов схемы сравнения, входы первого и второго сравниваемых чисел устройства подключены к первым входам элементов И соответственно

12248038

Таблица 2

22

2Ъ2 ii

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения чисел в системе остаточных классов | 1984 |

|

SU1160394A1 |

| Устройство для сравнения чисел в системе остаточных классов | 1983 |

|

SU1121670A1 |

| Устройство для сравнения чисел в системе остаточных классов | 1983 |

|

SU1145338A1 |

| Устройство для обнаружения и исправления ошибок в системе остаточных классов | 1980 |

|

SU888124A1 |

| Сумматор в системе остаточных классов | 1983 |

|

SU1111170A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Устройство для обработки информации, представленной в системе остаточных классов | 1990 |

|

SU1743002A1 |

| Арифметическое устройство по модулю | 1983 |

|

SU1120325A1 |

| Устройство для сравнения чисел в системе остаточных классов | 1987 |

|

SU1427358A1 |

| Устройство для возведения чисел в квадрат по модулю @ | 1982 |

|

SU1096641A2 |

Изобретение относится к области автоматики и вычислительной техники. Изобретение предназначено для обработки данных в схемах автоматики и специализированных ЭВМ, функционирующих в. системе остаточных классов. Цель изобретения - увеличение точности сравнения операндов в системе остаточных классов(СОК) . Устройство со- дерлит регистры первого и второго сравниваемых чисел ,сумматор для определения их разности, регистр, состоящий из п подрегистров, блок хранения констант нулевизации , сумматор для вычисления констант нулевизации, схему сравнения с кодом заданного интервала по выбранному основанию СОК, элемент запрета, злемент ШШ, элемент НЕ-И, группы элементов И и ИЛИ переписи и регистры наибольшего и наименьшего чисел. Сущность изобретения заключается в том, что сравнения операндов М и В заменяется сравнением операндов с (A-B)modP и Р, 2 (где Р. 1т Р.), что позволяет сравнивать операнды Л и В с точностью до единицы интервала. 1 ил,,3 табл. (Л 1чэ го 4; 00

25

.

Составитель E. Иванова Редактор Н. Слободяник Техред Н.Вонкало Корректор М. Демчик

Заказ 1953/48

Тираж 671

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г о Ужгород, ул. Проектная, 4,

Подписное

| Устройство для сравнения чисел в системе остаточных классов | 1982 |

|

SU1037244A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сравнения чисел в системе остаточных классов | 1983 |

|

SU1145338A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-04-15—Публикация

1984-09-03—Подача