выход элемента запрета подключен к первым входам десятого, одиннадцатого и двенадцатого элементов И, а выход первого элемента И - к первым входам тринадцатого, четырнадцатого и пятнадцатого элементов И, вторые входы четвертого, седьмого, десятого и тринадцатого элементов И соединены с выходом Равно схемы сравнения, выход Больше которой подключен к вторым входам пятого восьмого, одиннадцатого и четырнадцатого элементов И, а выход Меньше - к вторым входам шестого, девятого, двенадцатого и пятнсщцатого элементов И, выходы четвертого и десятого элементов И подключены к входам первого элемента И-ЛИ, выход которого соедин с управляющими .входами элементов И первой и второй групп, выходы шестого, седьмого, восьмого,девятого и одиннадцатого элементов И подключены к входам второго элемента ИЛИ, выход которого соединен с управляющими входами элементов И третьей и пятой групп, выходы пятого, двенадцатого, тринадцатого, четырнадцатого и пятнадцатого элементов И подключены к входам третьего элемента И, выход которого соединен с управлякмцими входами элементов И четвертой и пятой групп.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения чисел в системе остаточных классов | 1983 |

|

SU1145338A1 |

| Устройство для сравнения чисел в системе остаточных классов | 1984 |

|

SU1160394A1 |

| Устройство для сравнения чисел в системе остаточных классов | 1982 |

|

SU1037244A1 |

| Устройство для сравнения чисел в системе остаточных классов | 1984 |

|

SU1224803A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Сумматор в системе остаточных классов | 1983 |

|

SU1111170A1 |

| Устройство для обработки информации, представленной в системе остаточных классов | 1990 |

|

SU1743002A1 |

| Устройство для сравнения чисел в системе остаточных классов | 1987 |

|

SU1427358A1 |

| Арифметическое устройство в системе остаточных классов | 1985 |

|

SU1290315A1 |

| Устройство для обнаружения и исправления ошибок в системе остаточных классов | 1980 |

|

SU888124A1 |

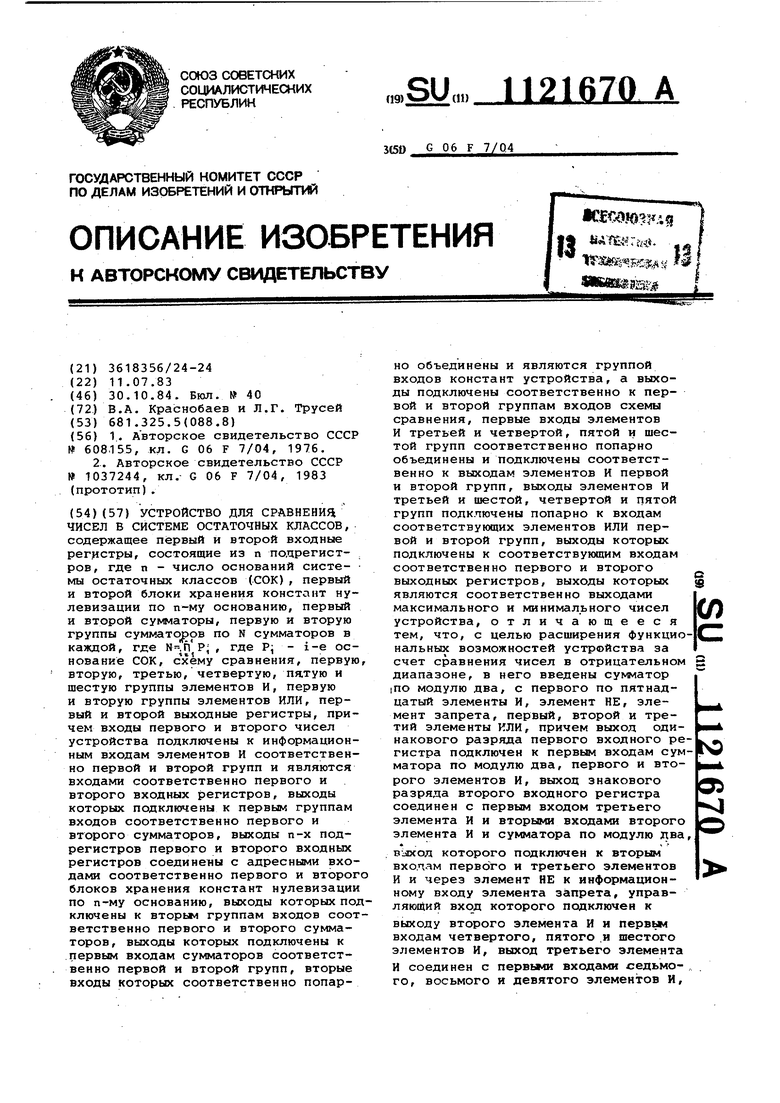

УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ЧИСЕЛ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ, содержащее первый и второй входные регистры, состоящие из п подрегистров, где п - число оснований системы остаточных классов (СОК), первый и второй блоки хранения констант нулевиэации по п-му основанию, первый и второй сумматоры, первую и вторую группы сумматоров по N сумматоров в каждой, где N. , где Р; - i-e основание СОК, схему сравнения, первую, вторую, третью, четвертую, пятую и шестую группы элементов И, первую и вторую группы элементов ИЛИ, первый и второй выходные регистры, причем входы первого и второго чисел устройства подключены к информационным входам элементов И соответственно первой и второй групп и являются входами соответственно первого и второго входных регистров, выходы которых подключены к первым группам входов соответственно первого и второго сумматоров, выходы п-х подрегистров первого и второго входных регистров соединехы с адресными входами соответственно первого и второго блоков хранения констант нулевизации по п-му основанию, выходы которых подключены к вторым группам входов соответственно первого и второго сумматоров, выходы которых подключены к первым входам сумматоров соответственно первой и второй групп, вторые входы которых соответственно попарно объединены и являются группой входов констант устройства, а выходы подключены соответственно к первой и второй группам входов схемы сравнения, первые входы элементов И третьей и четвертой, пятой и шестой групп соответственно попарно объединены и подключены соответственно к выходам элементов И первой и второй групп, выходы элементов И третьей и шестой, четвертой и пятой групп подключены попарно к входам соответствующих элементов ИЛИ первой и второй групп, выходы которых подключены к соответствующим входам соответственно первого и второго выходных регистров, выходы которых являются соответственно выходами (Л максимального и минимального чисел устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет сравнения чисел в отрицательном диапазоне, в него введены сумматор |ПО модулю два, с первого по пятнадцатый элементы И, элемент НЕ, элемент запрета, первый, второй и третий элементы ИЛИ, причем выход одинакового разряда первого входного регистра подключен к первым входам сумматора по модулю два, первого и второго элементов И, выход знакового разряда второго входного регистра соединен с первым входом третьего элемента И и вторыми входами второго элемента И и сумматора по модулю два, вdкoд которого подключен к вторым входам первого и третьего элементов И и через элемент НЕ к информационному входу элемента запрета, управляюйий вход которого псщключен к выходу второго элемента И и первьм входам четвертого, пятого .и шестого элементов И, выход третьего элемента И соединен с первьми входами седьмо- , го, восьмого и девятого элементов И,

Изобретение относится к автоматике и вычислительной технике и может быть использовано для обработки данных в схемах автоматики и ЭВМ, работающих в системе остаточных классов (СОК) .

Известно устройство для сравнения чисел в системе остаточных классов, содержащее два блока преобразования, каждый из которых содержит регистр, сумматор, узел деления, группы элементов И, ИЛИ l .

Недостатком устройства является низкое быстродействие.

Наиболее близким к предлагаемому по технической сущности .является устройство для сравнения чисел в системе остаточных классов, содержащее первый и второй входные регистры состоящие из п подрегистров, вхЬды которых являются входами первого и второго чисел соответственно, первый и второй сумматоры, первую и вторую группы элементов ИЛИ, схему сравнения, первую и вторую группы элементов И, причем первые входы первого |И второго сумматоров подключены соответственно к выходам первого и второго входных регистров. Кроме того, устройство содержит первую и вторую группы по N сумматоров (N .fl Р; , п количество оснований системй остаточных классов, Р; - основание), третью четвертую, пятую и шестую группы элементов И, первый и второй выходные регистры, первый и второй блоки хранения констант нулевизации пи n-sMy основанию, адресные входы которых подключены к выходам п-х подрегистров соответственно, первого и второго входных регистров, а выходы подключены к вторым входам соответственно первого и второго сумматоров, выходы которых подключены соответственно к первым входам сумматоров первой и .второй групп, вторые входы которых соответственно попарно объединены и являются группой входов , 5 констант устройства, а выходы подключены соответственно к первой и второй группам входов схемы сравнения, выход Равно которой подклю- чен к первым входам элементов И пер0 вой и второй Групп, вторые входы которых подключены соответственно к входам первого и второго входных регистров, первые входы элементов И третьей и пятой, четвертой и шестой

5 групп соответственно попарно объединены и подключены соответственно к выходам элементов И первой и второй групп, вторые входы элементов И третьей и четвертой, пятой и шестой групп соответственно объединены, и подключены к выходам Меньше и Больше схемы сравнения, выходы элементов И третьей и шестой, четвертой и пятой групп подключены попарно к входам соответственно эле5 ментов ИЛИ первой и второй групп, выходы которых подключены к соответствующим входам соответственно первого и второго выходных регистров, выходы которых являются соот0 ветственно выходами max и min устройства 2 .

Недостаток устройства - низкие функциональные возможности.

Цель изобретения - расширение

5 функциональных возможностей за счет сравнения чисел в отрицательном диапазоне.

Поставленная цель достигается тем, что в устройство для сравнения чисел 0 в системе остаточных классов, содержащее первый и второй входные регистры, состоящие из п подрегистров, где

n - ЧИСЛО оснований СОК, первый и второй блоки хранения констант нулевизации по п-му основанию, первый и второй сумматоры, первую и вторую группы сумматорр в по N сумматоров в каждой, где N п Р; , где Р- - i-e основание СОК, схему сравнения, первую, вторую; третью, четвертую, пятую и шестую группы элементов И, первую и вторую группы элементов ИЛИ, первый я второй выходные регистры, причем входы первого и второго чисел устройства подключены к информационHfc iвходам элементов И соответственно первой и второй групп и являются входами соответственно первого и второго входных регистров ;, выходы которых подключены к первым группам . , входом соответственно первого и вто,рого сумматоров, выходы п-х подрегистров первого и второго входных регистров соединены с адресными входами -соответственно первого и второго блоков хранения констант нулевиэации по п-му основанию, выходы которых подключены к вторым группам входов

соответственно- первого .и второго сумматоров,выходы которых подключены к первым входам сумматоров соответственно первой и второй групп, вторые ; входы которых соответственно попарно объединены и являются группой входов констант устройства, а выходы подключены соответственно к первой и второй группам входсз схемы сравнения, первые входы элементов И третьей и четвертой, пятой и шестой групп соответственно попарно объединены и подключены соответственно к выходам элементом И первой и второй групп, |Выходы элементов И третьей и шестой, четвертой и пятой групп подключены попарно к входам соответствующих элементов ИЛИ первой и второй групп, выходы которых подключены к соответствующим входам соответственно первого и второго выходных регистров, выходы KOTdt bix являются .соответственно выходами максимального и минимального чисел устройства, введены сумматор по модулю два, с первого по пятнадцатый элементы И, элемент НЕ, элемент запрета, первый, второй и третий элементы ИЛИ, причем выход одинакового разряда первого входного регистра подключен к первым входам сумматора по модулю два, первого и второго элементов И, выход знакового разряда второго входного регистра соединен с первым входом третьего элемента И и вторыми входами второго элемента И и сумматора по модулю два, выход которого подключен к вторым входам первого и третьего элементов И и через элемент НЕ к информационному входу элемента запрета, управляющий вход которого подключен к выходу второго элемента И и

первым входам четвертого, пятого и шестого элементов И, выход третьего элемента И соединен.с первыми входами седьмого, восьмого и девятого элементов И, выход элемента запрета подключен к первым входам деЬятого, одиннадцатого и двенадцатого элементов И, а выход первого элемента И - к первым входам тринадцатого, четырнадцатого и пятнадцатого элементов И, вторые входы четвертого, седьмого, десятого и тринадцатого элементов И соединены с выходом Равно схемы сравнения, выход Больше которой подключен к вторым входам пятого, восьмого, одиннадцатого и четырнадцатого элементов И, а выход Меньше - к вторьм входам шестого, девятого, двенгщцатого и пятнадцатого элементов И, выходы четвертого и десятого элементов И подключены к входам первого элемента ИЛИ, выход которого соединен с управлякяцими входами элементов И первой « второй групп, уаходы шестого, седьмого, восьмого, девятого и одиннадцатого элементов И подключены к входам второго элемента ИЛИ, выход которого соединен с управляющими входами элементов И третьей и пятой групп, выходы пятого, двенгщ:цат,ого, тринадцатого, четьфнадцатого и пятнадцатого элементов И подключены к входам третьего элемента И, выход которого соединен с управляющими входами элементов И четвертой и пятой групп.

Функциональные возможности пред- лагаемого устройства расширяются за счет выполнения операции сравнения чисел в отрицательном диапазоне. При этом сравниваемые операнды , а, ..., а;) и В(в|, Bj, .... в„) имеют по одному дополнительному знаковому разряду, т.е. число сопровождается признаком 5 {9j) знака signACsignB) , где

если А(В)0 если )0

В этом случае сравниваемые операнды представляются в виде

A( А) (9д; (а,, а,, ...,а„)) В (5 В) №gj (В.а, , ... , В„)).

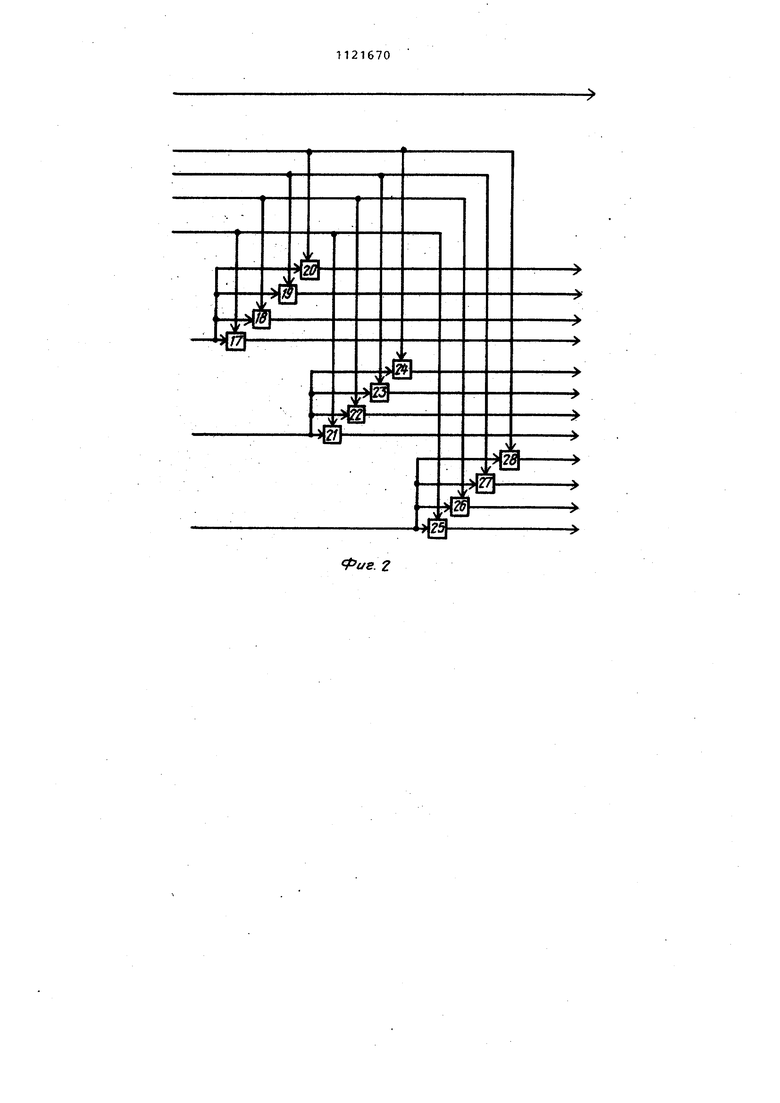

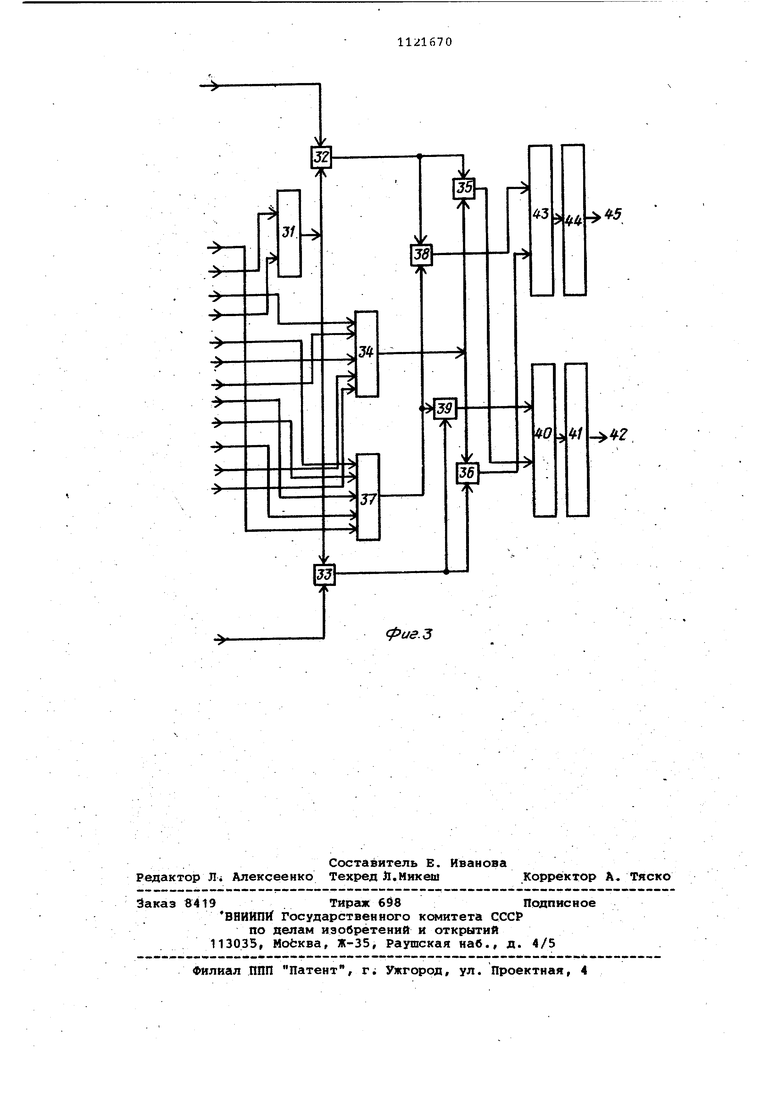

На фиг. 1, 2 и 3 представлена структурная схема предлагаемого устройства.

Устройство первый и рой входы 1 и 2 устройства, первый и второй входные регистры 3 и 4, пер- вый блок 5 хранения констант нулевизации, по сюнованию, первый сумматор б, первую группу 7 сумматоров, схему 8 сравнения чисел А и В, блок

9 хранения констант нулевиэации, второй сумглатор 10, вторую группу сумматоров 11, шины 12 подачи констант Р„ , 2Рп, NPi, (N ft Рр , сумматор 13 по модулю два, первый - пятнадцатый элементы И 14-28, элемент 29, элемент 30 запрета, первый элемент ИЛИ 31, первую и вторую группы элементов 32 и 33, второй элемент ИЛИ 34, третью и четвертую группы элементов И 35 и 36, третий элемент ИЛИ 37, пятую и шестую группы элементов И 38 и 39, первую группу элементов ИЛИ 40, первый выходной регистр 41 (регистр наибольшего числа)} первый выход 42 устройства (выход max), вторую группу элементов ИЛИ 43, второй выходной регистр 44 (регистр наименьшего числа), второй выход 45 устройства (выход min).

.Устройство работает следующим образом.

По первой 1 и второй 2 входным шинам устройства соответственно первое А (Пд; Л) (97д; (а, , .. ., а) и второе В(вг В) (aef (й.в, .. . . , й„) сравниваемые числа, записанные в СОК с учетом знаков операндов д и Я в, заносятся -соответственно в первый 3 и второй 4 входные регистры. Блоки 5 и 9 хранения констант по значениям а и в„ соответственно определяют константы нулевизации по основаниям СОК в виде

a, (a U;а„)и

..., в„).

Первый б и второй 10 сумматоры выполняют операцию вычитания соответственно А {А-а„-(aj.a, , ....а-) , . а.) li .В„ (В,. и, . .... (5«)-(, QJ ., ..., В„). Из сумма(торов 6 и 10 числа А и В в СОК, кратные основанию, поступают на первые входы соответственно сумматоров 7 и 11, на вторые входы которых по шинам 12 поступают ,константы Р,,2Р,, ... ,NPn в СОК (-N.10, Р;) .., В результате на выходе одного из сумматоров 7 и 11 появляется ноль, т.е. A-an-kP( 0, . В этом случае с выходов сумматоров 7 и 11 два слова длины N, представленные однорядовым кодом, в каждом из которых только на k-M и ш-м местах нули, а на остальHfejx - единицы, поступают на схему, 8 сравнения. Если Од РВ D (т.е. А,) то сигнал присутствует только на выходе элемента 30 (так как 0+00/mod2/), на выходе сумматора 13 отс утствует сигнал, на выходе элемента НЕ 29 присутствует, а запрещающий сигнал с выхода элемента И 15 отсутствует. Если Од 1 (AVO) () то сигнал присутстйует только на выходе элемента И 14, Если () и Пр 1(), то сигнал присутствует только на выходе третьего элемента И 16. Если s 9в 1 (А , 0) , то

сигнал присутствует на выходе только второго элемента И 15. При сигнал Больше с выхода схемы 8 сранения поступает на первые входы элементов И 21-24. При сигнал Меньше с выхода схемы 8 сравнения поступает на первые входы элементов И 25-28. При сигнал Равно с выхода схемы 8 сравнения поступает на первые входы элементов И 17-20. Если и одновременно.Яд или57я то выходной сигнал элемента И 19 или 17 через элемент ИЛИ 31 закрывает элементы И 32, и 33, и в выходных регистрах 41 и 44 числа отсутствуют, т.е. там нули, что и является признаком равенства операндов А и В . В остальных случаях ( и при ) сигнал с выхода одного из элементов И 14-16 иЛи элемента 30 открывает только один из элементов И 18, 20-28, выходной сигнал которого через соответствующие элементы ИЛИ 34 или 37 открывает соответственно элементы И 35, 36 или 38, 39 и выходные операнды А и В через соответственно открытые элементы И 32, и 33, через соответствующие элементы И 35, 36, 38 и 39, через соответствующие элементы ИЛИ 40 и 43 поступают в соответствующие выходные регистры 41 и 44 наибольшего и наименьшего чисел.

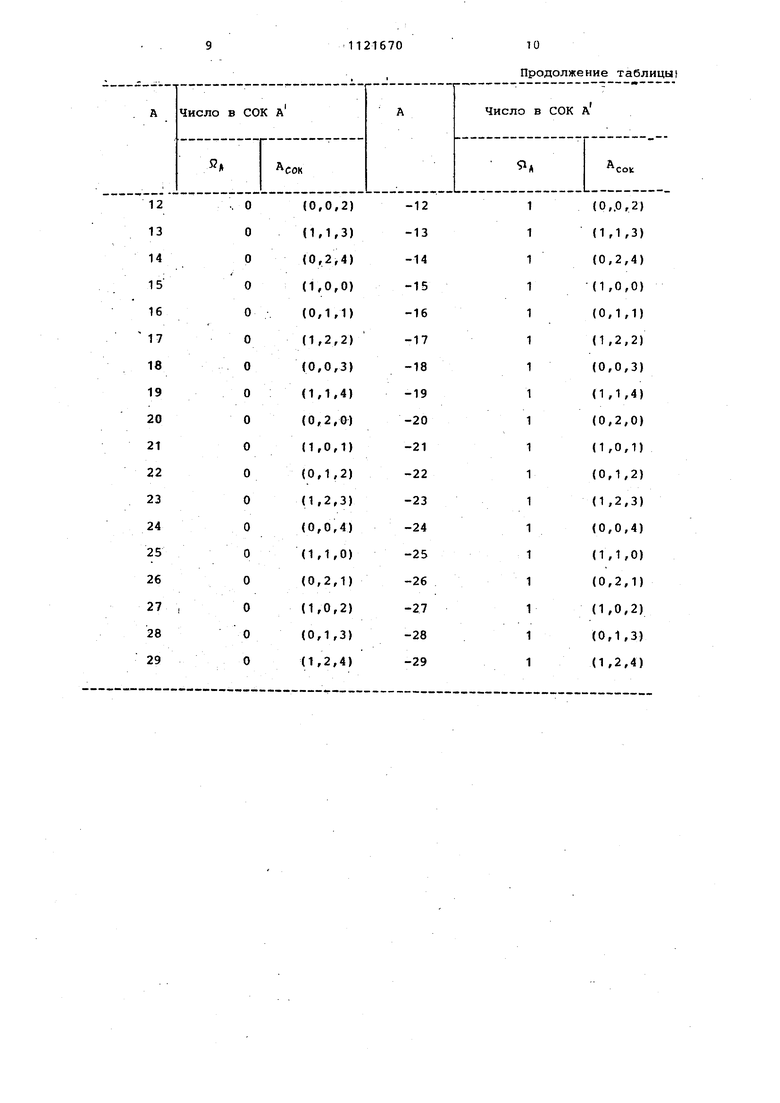

Рассмотрим примеры конкретного выполнения операции сравнения чисел для СОК, заданной.основаниями Р 2, , (таблица).

, Пример 1. (0; (010) и В,(0; (О, 1, 0)). Операнд А заносится в регистр 3, а операнд В в регистр 4. По значению и в блоках 5 и 9 выбираются константы аэ(0,0,0) и В,(0,0,0). Сумматоры 6 и 10 производят операцию вычитания А-а и В-В„, .е. получаем (О, 1 ,0) . Это значение поступает на входы сумматоров 7 и 11, на вторые входы которых по шинам 12 поступают значения констант , 2Р,10, ..., в СОК. Таким образом, на первые и вторые входы схемы 8 сравнения поступает код длиной в двоичных разрядов вида (1111015, так как ( В-В„-а5 0)

Сигнал выходной шины Равно схемы 8 сравнения поступает на первые входы элементов И 17-20. Так как ° выходе сумматора 13 отсутствует сигнал (0+0)0(mod 2) ) , значит на выходе элемента НЕ 29 присутствует сигнал, который через открытый элемент 30 открывает элемент И 19, выходной сигнал которого через элемент ИЛИ 31 закрывает элементы И 32 и 33. В регистрах 41 и 44 содержатся нули, что свидетельствует о ра венстве чисел . Проверка:. Пример 2. А,о (0; (0,1,0)) и в (1; (0,1,0)). В ЭТОМ случае вы ходной сигнал элемента И 16 (., ,) открывает элемент И 18, выходной сигнал которого через элемент ИЛИ 34 открывает элементы И 35 и 36. Операнд А с выхода 1 через элементы И 32 и ., элемент ИЛИ 40 поступает в регистр 41 наибольшего числа, а операнд В с выхода 2 через элементы И 33, 36, элемент ИЛИ 43 поступает в регистр 44наименьшего числа, т.е. . Проверка: . I П р и м е р 3. А.(1 ; (0,1 ,0)) , Bjj (0; (1,2,3)). Операнд В заносит ся в регистр 4. По значению в блоке 9 выбирается константа 8j(1, 0,3). Сумматор 10 производит операцию , (1,2,3)-(1,0,3)(0,2,0) , это значение поступает на первые входы сумматоров 11. В этом случае на вторую группу входов схемы 8 срав нения поступает код вида fllOlll, так как В-8„-45 0. Так как (, , т.е. ), на выходе Меньше схемы 8 сравнения присутствует сигнал, который поступает на первые входы элементов И 25-28. При., выходной сигнал элемента И 14 открывает элемент И28, выходной сиг нал которого через элемент ИЛИ 37 от крывает элементы И 38 и 39. В этом случае операнд А через элементы И 32 и 38 поступает в регистр 44 наи-, меньшего числа, а операнд в через элементы И 33 и 39 поступает в регистр 41 наибольшего числа, т.е. . Проверка: . Пример 4. (1 ()) и в-(1} (1,2;3)). в этом случае открыт второй элемент И 15 (.Йд в 1), выходной сигнал которого закрывает элемент 30 и открывает элемент И 25 (), выходной сигнал которого через элемент ИЛИ 34 открывает элементы И 35 и 36. Операнд А через элементы И 32 и 35 и .элемент ИЛИ 40 поступает в регистр 41 наибольшего числа, а операнд В через .элементы И 33, 36 и элемент ИЛИ 43 - в регистр 44 наименьшего числа, т.е. . Проверка: . Техническое преимущество изобретения по сравнению g базовым объектом - прототипом сострит в существенном расширении функциональных возможностей за счет сравнения чисел в отрицательном диапазоне. Экономический эффект заключается в уменьшении количества оборудования за счет совмещения в одцст устройстве выполнения операции сравнения чисел как в положительном, так и в отрицательном диапазонах.

(0,0,2)

. О О О (М,3) (0,)

/

О О (1,0,0) (0,1,1)

о о о о о о о о о о о о о (1,2,2) (0,0,3) (1,1,4) (0,2,0) (1,0,1) (0,1,2) (1,2,3) (0,0,4) (1,1,0) (0,2,1) (1,0,2) (0,1,3) (1,2,4)

Продолжение таблицы

(О,.0,2)

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 (1,1,3) (0,2,4) (1,0,0) (0,1,1) (1,2,2) (0,0,3) (1,1,4) (0,2,0) (1,0,1) (0,1,2) (1,2,3) (0,0,4) (1,1,0) (0,2,1) (1,0,2) (0,1,3) (1,2,4)

I It I i f

f 6 фие1

Фиг 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| АППАРАТ ДЛЯ РАСПРЕДЕЛЕНИЯ ТОРФА НА СУШИЛЬНОМ ПОЛЕ | 1922 |

|

SU608A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для сравнения чисел в системе остаточных классов | 1982 |

|

SU1037244A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

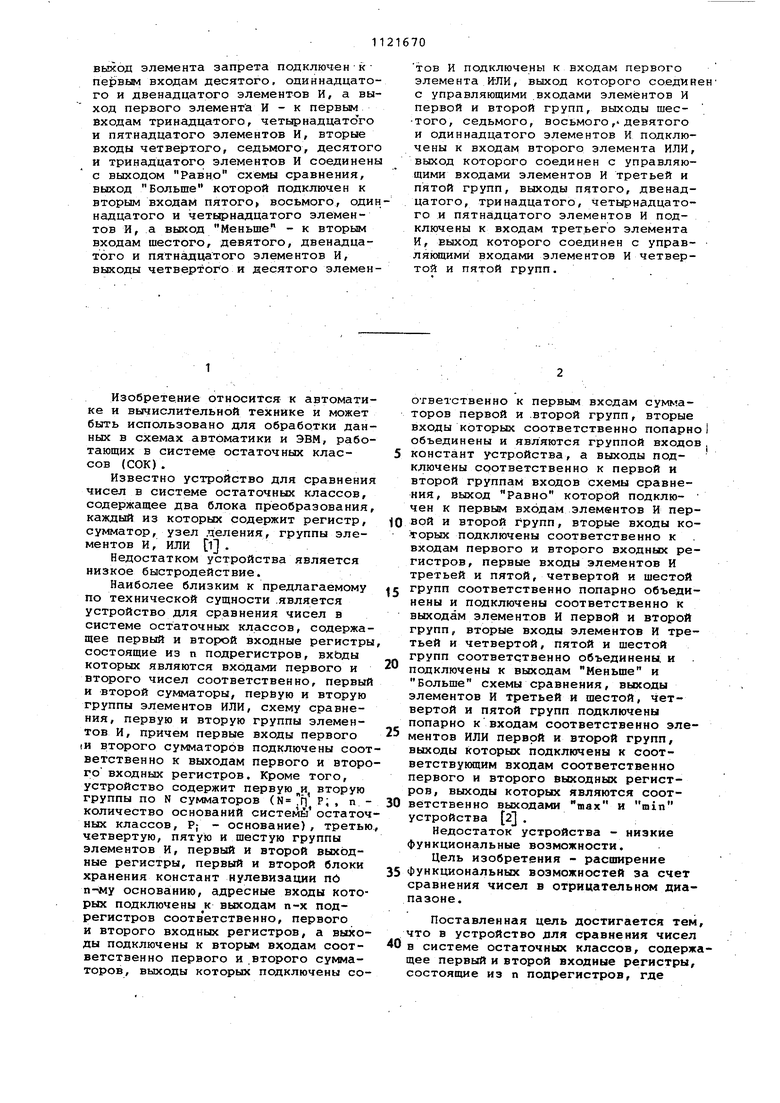

Авторы

Даты

1984-10-30—Публикация

1983-07-11—Подача