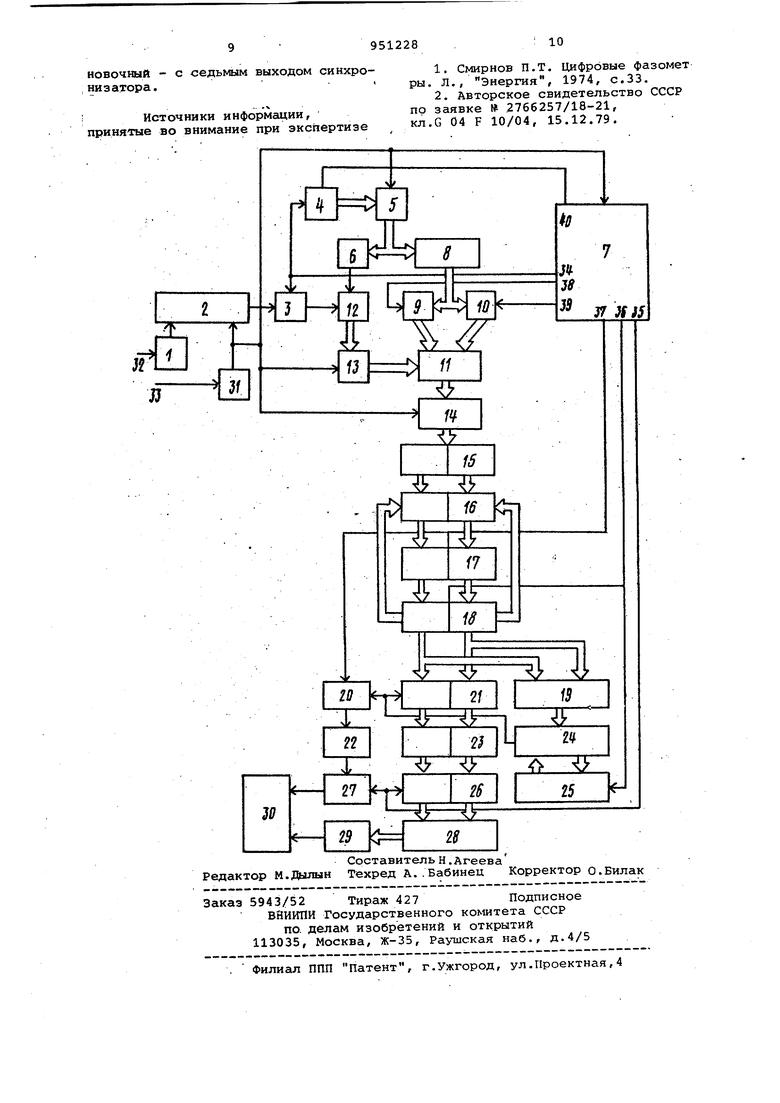

t - очередное нуль-пересечение первого из процессов; t - последующее во времени (за tn).нуль-пересечение второго из процессов. Можно показать, что алгоритм (1) является оптимальным лишь в случае, если измеряемый параметр-задержка не изменяется на интервале наблюдения (или же эти изменения очень малы) . В практике пеленгования источников неизвестных сигналов указанно условие практически никогда не выполняется - обычно цель перемещает ся со значительной угловой скоростью по отношению к пеленгатору, что при водит к непостоянству задержки на измерительном интервале. Для исполь зования известного устройства прихоpiTCH значительно сокращать величину :измерительного интервала (чтобы из.менения задержки не чувствовешись при измерении), чтонеизбежно ведет к ухудшению достижимой точности измерений. Цель изобретения - повышение точности измерений взаимной задержки между сигналами (за счет увеличения величины измерительного интервала) . Поставленная цель д ;остигается тем, что в цифровой измеритель задержки , содержащий два формирователя нуль-пересечений, входы которых подключены ко входам триггера, подключенные к выходу триггера последовательно соединенные первый ключ, первый счетчик, второй ключ и второй элемент ИЛИ, ко второму входу первог ключа подключен первый выход синхронизатора , последовательно соединенные третий ключ, делитель,первый постоянный запоминающий блок и индикатор, управляющий вход третьего ключа подключен ко BTOpiDMy выходу синхронизатора, накапливающий сумматор и второй постоянный запоминающий блок, введены последовательно соединенный сумматор, оперативный запоминающий блок, распределитель, квадратор, блок сравнения и первый регистр, вход сумматора подключен к выходу второго постоянного запоминающего блока,управляющие входы первого регистра и распределителя объединены и подключены к третьему выходу синхронизатора, выход первого регистра подключен ко второму входу блока сравнения,, а также последовательно соединенные четвертый ключ, второй,,регистр и пятый ключ, выход которого подключен ко второму входу индикатора, управляющие входы третьего и пятого ключей объединены, также последовательно соединенные шестой ключ и третий регистр, выход которого соединен со входом третьего ключа, информационные входы шестого ключа объединены со входами квадратора и подключены к выходу распределителя, а управляющие входы четвертого и шестого ключей объединены и соединены со вторым .выходом блока сравнения, сигнальные входы четвертого ключа и адресные шины оперативного запоминающего блока объединены и подключены к Четвертому выходу синхронизатора, вторые выходы распределителя подключены ко вторым входам сумматораf а также последовательно соединенные второй счетчик, седьмой ключ, четвертый регистр и восьмой ключ, выход которого через второй элемент ИЛИ подключен ко входу накапливающего сумматора, вторые входы второго элемента ИЛИ через девятый ключ подключены к соответствующим выходам четвертого регистра, управляющие входа восьмого и девятого ключей подключены соответственно к пятому и -шестому выходам синхронизатора, установочный вход накапливающего сумматора объединен с управляющими входами второго и седьмого ключей и синхронизатора и подключен к выходу первого формирователя нульпересечений, выход седьмого через первый элемент ИЛИ подключен к установочному входу первого счетчика, выходы накапливающего сумматора соединены с .адресными входами второго постоянного запоминающего блока, при этом вход второго счетчика соединен с первым, а установочный - с седьмым выходом синхронизатора. На чертеже показана блок-схема устройства задержки. Цифровой измеритель задержки содержит формирователь 1 нуль-перёсег чений, триггер 2, первый ключ 3, второй счетчик 4, седьмой ключ 5, первый элемент б ИЛИ, синхронизатор 7, четвертый регистр 8, восьмой 9 и девятый 10 ключи, второй элемент 11 ИЛИ, первый счетчик 12, второй ключ 13, накапливающий сумматор 14, второй постоянный запоминающий блок 15 (ПЗБ), сумматор 16, оперативный запоминающий блок 17 (ОЗБ), распределитель 18, квадратор 19, четвертый ключ 20, шестой ключ 21, второй регистр 22, третий регистр 3, блок 24 сравнения, первый регистр 25, третий ключ 26, пятый ключ 27, делитель 28, первый постоянный запоминающий , индик:атор 30 и второй формирователь 31 нуль-пересечений. Узкополосные сигналы, взаимную задержку между которыми необходимо измерить,подаются на входы 32 и 33 формирователей 1 и 31 нуль-пересечений; 34-40 выходы синхронизатора 7. Цифровой измеритель задержки работает следующим образом.

Сигналы, взаимную задержку между которыми необходимо измерить, подаются на входы 32 и 33 формирователей 1 и 31 нуль-пересечений. Импульсы, соответствующие передним кронтам прямоугольных напряжений, сформированных из входных сигналов, опрокидывают триггер 2. На выходе триггера 2 формируются импульсы положительной полярности, длительность которых равна временному расстоянию между соседними (последующими) нуль-пересечениями . двух узкополосных сигналов Эти импульсы, поступая на вход первого ключа -3, разрешают прохождение импульсов высокочастотного заполнения с первого выхода синхронизатора 7 в первый счетчик 12. Таким образом происходит измерение длительности (положительного) -импульса на выходе триггера 2 - временного расстояния (tf, -tp) между очередной парой нуль-пересечений двух узкополрсных сигналов. В момент начала измерения сигналом с выхода 40 синхронизатора 7 устанавливается в нуль содержимое второго счетчика 4. Далее этот счетчик 4 начинает заполняться импульсаМи высокочастотного заполнения с выхода 34 синхронизатора 7- В моменты времени формирования импульсов нульпересечений одним из формирователей 1 или 32 нуль-пересечений производится .считывание числа, накопленного в счетчике 4, через седьмой ключ 5 в четвертый регистр В, Таким образом производится измерение времени от , момента начала измерения до момента формирования очередного из нуль-пересечения (одного из информационных узкополосных сигналов) t. В момент формирования импульса нуль-пересечения на выходе 32 формирователя (в этот момент заканчивается, очевидно, положительный импульс на выходе триггера) устанавливается в нулевое состояние содержимое накапливающего сумматора 14, после чего (с аппара.турной задержкой) в сумматор 14 через ключ 13 и элемент ИЛИ 11 переписывается число с выхода счетчика 12. Указанное число (многоразрядный двоичный код) воздействует на адресные шины второго ПЗБ 15. Два числа с выхода ПЗБ 15 суммируются сумматором 16 с содержимым первой (очередной) строки оперативного запоминающего блока 17 - также двумя числами, которые представляют собой соответственно действительную и мнимую часть комплексного числа. Результат сложения записывается в ту же самую строку ОЗБ 17 откуда взята (через распределитель 18) упомянутая пара чисел. Далее под воздействием управляющего импульса с выхода 38 синхронизатора 7 открывается ключ 9, и к содерхсимому накапливающего сумматора 14 добавляется число, хранящееся в регистре 8, умноженное на константу 2 (что достигается соответствующей распайкой выходных шин ключа 9 ко входным шинам элемента ИЛИ 11 - со сдвигом на п разрядов). Результат суммирования опять воздействует на адресные шины второго ПЗБ 15, и очередная пара чисел суммируется сумматором 16 с содержимьдм очередной строки ОЗВ 17. Результат сложения опять записывается в ту строку ОЗБ 17, откуда взята пара чисел. После этоoго синхронизатор 7 формирует на выходе серию М-2 импульсов, которые от срывают ключ 10 (М - число отсчетов выходного эффекта). При каждом открывании ключа содержимое сумматора

5 14 возрастает на величину числа,хранящегося в регистре 8. Аналогично описанному происходит обновление содержимого М-1 очередных строк ОЗБ 17. На этом отработка информации,

0 содержащейся в очередных данных временном расстоянии (t - t), между нуль-пересечениями двух сигналов (хранится в счетчике 12) и недь-пересечением 1„ первого из сигналов (хранится в регистре 8) закан5чивается. С приходом очередного импульса нуль-пересечения с выхода второго формирователя 31 нуль-пересечений триггер опрокидывается, в результате чего открывается ключ 3.

0 Производится заполнение счетчика 12 импульсами высокочастотного заполнения до тех пор, пока триггер не опрокидывается импульсом с выхода первого формирователя 1 нуль-пересече5ний, таким путем производится измерение временного интервала между очередной парой нуль-пересечений двух информационных узкополосных сигналов. Снова (путем открывания клю0ча 5) производится регистрация мо мента формирования очередного нульпересечения. После этого повторяется процедура обработки информации, соI держащейся в очередной паре Ч1аселданных. Процесс обработки пар данных

5

продолжается до конца измерительного интервала. В момент времени t Т на управляющий вход распределителя 18 подается управляющий си-: гнал с выхода 36 синхронизатора 7,

O в результате чего выход ОЗБ 17 подключается к объединенным входам квад ратора 19 и ключа 21.- Этим же импуль;сом с выхода синхронизатора обнуляется регистр 25. Начинается этап

5 обработки статистик, накопленных в ОЗВ 17 в течение измерительного интервала. Синхрбнизатор 7 подает на адресные шины ОЗБ 17 и ключа 20 код, соответствующий чтению первой

0 строки. Два числа с выхода ОЗБ 18 с помощью квадратора 19 возводятся в квадрат и складываются - формируется квадрат модуля комплексного числа. Этот квадрат модуля с помощью блока

5 24 сравнения сравнивается с числом.

хранящимся в регистре 25. Если новое число больше, вырабатывается управляющий сигнал для ключей 20 и 21, в результате чего в регистры 22 и 23 переписываются соответственно номер строки ОЗБ 17, в котором хранилось новое число, и самсз комплексное число (действительная и мнимая часть). В регистр 25 переписывается через блок 24 сравнение новое, большее из двух сравниваемых число. Путем возведения в квадрат и порчередного сравнения всех чисел, хранящихся в М строках ОЗБ 17, выбигЗается та пара чисел, которая обеспечивает наибольший квадрат модуля (соответствует наибольшему подавлению мешающего параметра), и записывается в регистр 23. В регистре 22 при этом оказывается записанным номер строки ОЗБ 17, в котором хранится упомянутая пара чисел. После обработки информации всех строк ОЗБ 17 под воздействием управляющего сигнала с выхода 35 синхронизатора 7 открываются ключи 26 и 27. Число, соответствующее номеру кнала цифровой обработки, в котором обеспечено наилучшее подавление мешающего параметра, через ключ 27 выводится на индикатор. Числа с выхода регистра 23 (соответственно действительная и мнимая составляющие наибольшего отсчета выходного эффекта) поступают на соответствующие входы делителя 28. По результату деления из первого ПЗБ 29 выбирается числовременная задержка между информационными сигналами (измеренная в соответствующих единицах). Этот результат измерения также поступает на индикатор 30. Обнуление ОЗБ 17 производится в процессе обработки статистик (строк данных) с помощью совокупности блоков 19-30, поскольку на входные ШИВЫ сумматора 16 поступают .числа, равные нулю.

Данное устройство также реализует Е цифровом виде алгоритм измерения взаимной задержки между узкополосными сигналами неизвестной формы по (1) . Благодаря тому, что в данном устройстве осуществляется совместное оптимальное измерение задержки и скорости ее изменения,здесь

;удается существенно увеличить время накопления (обработки) сигнала, а значит повысить к точность измерения задержки по сравнению d известным

устройством.

Формула изобретения

Цифровой измеритель задержки, содержащий два формирователя, нуль-перечесенкй, выходы которых подключены к входам триггера, подключенные к выходу триггера последовательно соединенные первый ключ, первый счетчик, второй ключ и второй элемент ИЛИ, к второму входу первого ключа подключен первый выход синхронизатора, последовательно соединенные третий ключ, делитель, первый постоянкый запоминающий блок и индикатор, управляющий вход третьего ключа подключен к второму выходу синхронизатора, накапливающий сумматор и второй постоянный запоминающий блок, от л и ч а ющи и ся тем, что, с целью повышения точности измерения задержки, введены последовательно соединенные сумматор, оперативный запоминающий блок, распределитель, квадратор, блок сравнения и первый регистр, вход сумматора подключен к выходу второго постоянного запоминающего блока, управляющие входы первого регистра и распределителя объединены и подключены к третьему выходу синхронизатора, выход первого регистра подключен к второму входу блока сравнения, а также последовательно соединенные четвертый ключ, второй регистр и пятый ключ, выход которого подключен к второму входу ин,цикатора, управляющие входы третьего и пятого ключей объединены, также последовательно соединенные шестой ключ и третий регистр, выход которого соединен с входом третьего ключа, информационные входы шестого ключа объединены с входами квадратора и подключены к выходу распределителя, а управляющие входы четвертого к шестого ключей объединены и соединены с вторым выходом блока сравнения, сигнальные входы четвёртого ключа и адресные шины оперативного запоминающего блока объединены и подключены к четвертому выходу синхронизатора, вторые выходы распределителя подключены к вторым входам сумматора, а также последовательно соединенные второй счетчик, Седьмой ключ, четвертый регистр и восьмой ключ, выход которого через второй элемент ИЛИ подключен к входу накапливающего сумматора, вторые входы второго элемента ИЛИ через девятый ключ подключены к соответствующим выходам четвертого регистра, управляющие входы восьмого и девятого ключей подключены соответственно к пятому и шестому выходам синхронизатора, установочный вход накапливающего сумматора объединен с управляющими входаг«1 второго и седьмого ключей и синхронизатора и подключен к выходу первого формирователя нульпересечений, выход седьмого ключа через первый элемент ИЛИ лодключен к установочному входу первого счетчика, выходы Накапливающего сумматора соединены с адресными входами второго постоянного запоминающего блот ка, при этом счетный вход второго счетчика соединен с первым, а установочный - с седьмым выходом синхронизатора.

; Источники информации, принятые во внимание при экспертизе

1.Смирнов П.Т. Цифровые фазомет ры. Л., энергия, 1974, с.33.

2.Авторское свидетельство СССР по заявке № 2766257/18-21,

кл.С 04 F 10/04, 15.12.79.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой обработки сигналов | 1979 |

|

SU879494A1 |

| Устройство для измерения мощности | 1990 |

|

SU1751685A1 |

| Цифровой измеритель задержки | 1980 |

|

SU930219A2 |

| Система передачи сообщений | 1986 |

|

SU1356268A1 |

| Устройство асинхронного приема импульсных сигналов | 1988 |

|

SU1684930A1 |

| Устройство для цифровой обработкиСигНАлОВ | 1979 |

|

SU834559A1 |

| УСТРОЙСТВО ДЛЯ ИМИТАЦИИ РАДИОЛОКАЦИОННОГО ИЗОБРАЖЕНИЯ МЕСТНОСТИ | 1988 |

|

SU1841035A1 |

| Цифровой измеритель задержки | 1979 |

|

SU822063A1 |

| Адаптивное устройство компенсации помех в речевом сигнале | 1988 |

|

SU1660188A1 |

| Устройство для регистрации телевизионного изображения | 1989 |

|

SU1720168A1 |

Авторы

Даты

1982-08-15—Публикация

1981-01-04—Подача