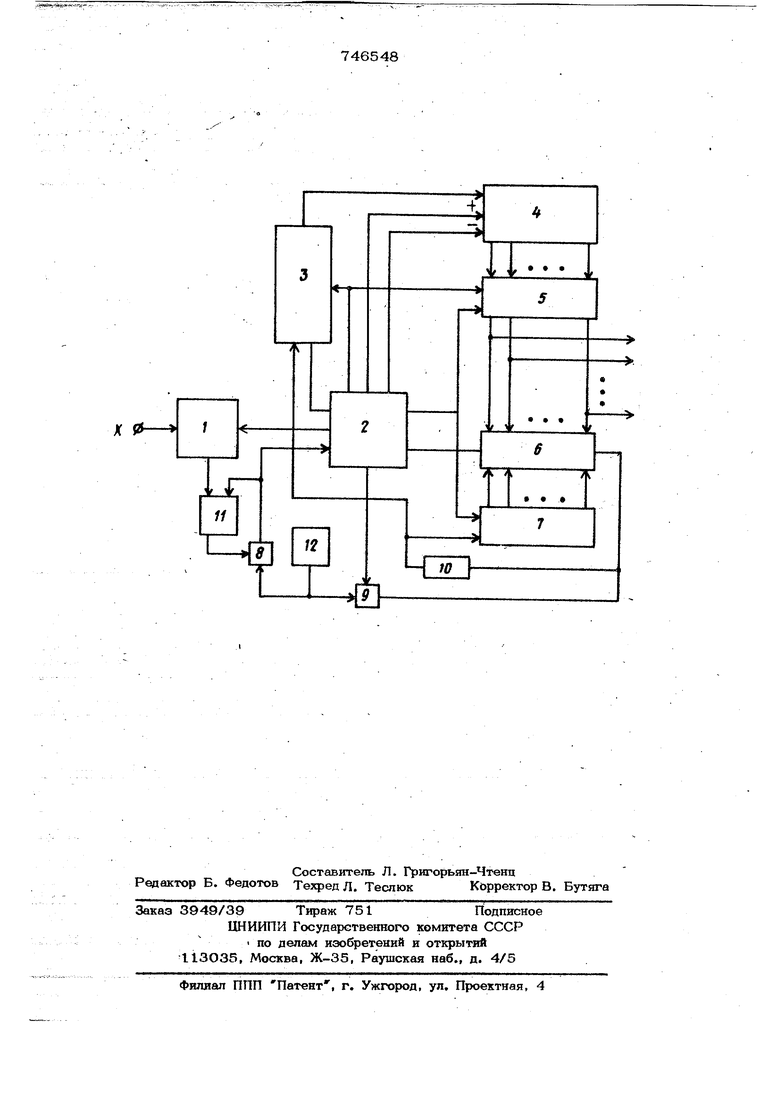

(54) РЕКУРРЕНТНЫЙ ВЫЧИСЛИТЕЛЬ ОЦЕНКИ МАТЕМАТИЧЕСКОГО ОЖИДАНИЯ Изобретение относится к вычислительной технике, может быть использов но для текущего статистического анализа случайных процессов. Известно устройство для оценки математического ожидания i, реализующее рекуррентный алгоритм, содержащее аналого-цифровой преобразователь, блок управления, сумматор-вычитатель, регистр, триггер, реверсивный счетчик, вычитатель. Существенным недостатком устройства является его сложность. Наиболее близким но технической реализацииявляется вычислитель оценки математического ожидания ТрП, содержащий счетчик, генератор импульсов, триггер, элемент задержки, уттрашляемы делитель частоты, первый выход которо го подключен к счетному входу реверсивного счетчика, блок сравнения. Недостатки прототипа эактеочаются в малой скорости сходш-юсти, что обусловлено свойствами реализуемого им алгоритма вычисления среднего, и, как следствие, - в малой точности оценки. Цель изобретения состоит в ускорении сходимости и повышении точности оценки математического ожидания. С этой целью в вычислитель для оценки математического ожидания бведены регистр, ключи, блок управления и время-импульсный преобразователь. Первый выход ; блока управления подключен к управляющему входу вро яимпульсного тфеобразователя, и }юрмационный вход которого является входом вычислителя, выход время-импульснотх) преобразователя соединен со входом установки в нуль триггера, нулевой выход которого подключен к утфавляющему входу ключа, информационный вход которого объединен с информационным входом второго ключа и соединен с выходом генератора импульсов; выход первого тслюча подключен ко входу установки в единицу триггера и к первому входу блока управления, второй выход которого соединен с управляющим входом второго ключа, выход которого соединен с управляющим входом блока сравнения и через элемент задержки - со счетным входами управляемого делителя частоты и счетчика, выходы которого подключены к первой группе информационных входов блока сравнения; вторая группа ин. формационных входов блока сравнения соединена с соответствуюши- ми выходами регистра, вход ухзтановки в нуль которого соединен со входом установки в нуль счетчика и с третьшу выходом блока управления, четвертый выход которого соединен с управляюшиМи входами регистра и управ гаемого де лителя частоты, первый выход которого соединен со счетным входом реверсивного счетчика. Входы сложение и вы читание реверсивного счетчика подклю чШы соответственно к пятому и шестому выходам блока управления, третий вход которого соединен со вторым вы Ходом управляемого делителя частоты, а инфЬрйационныевходы регистра подклю чёны к соответствующим выходам ревер сивного счетчика. Структурная электрическая схема вы числителя представлена на чертеже. Вычислитель содержит время-импульс ный преобразователь 1, блок 2 управле ния, управляемый делитель ч ютоты 3, реверсивный счетчик 4, регистр 5, блок сравнения, счетчик 7, ключи 8, 9, элемент задержки 1О, триггер 11, генера;уор импульсов 12. Вычислитель реализует следующий ре куррентный алгоритм оценки математического ожидания: о -QlJci п rv п-. п , V-O. Перед началом работы реверсивный счетчик 4, регистр 5 и счетчик 7 установлены в нуль, триггер 11 - в единицу, а блок управления 2 - в исходное состояние; коэффициент деления угфавпясмого делителя частоты 3 равен едйнипё. Реверсивный счетчик 4 служит для формирования величины Зщ регистр - д :1фанення величины S.. После запуска блока управления 2 о иййгуШс«з « 1с Шр1ШРГ время-лмпульсвый преобразователь 1, также открывает ключ 9; Первый же импульс с ключа проходит через блок сравнения 6 «а второй вход блока управления 2, в результате чего реверсивный счетчик 4 устанавливается в режим сложения. Спустя время т: , пропорциональное величине х, , на выходе время-импуЛьсного преобразователя 1 появляется импульс, опрокидывающий в нуль триггер 11. Очередной импульс с ; генератора импульсов 12 проходит через открывшийся ключ-8 на первый вход блока управления 2, а также возвращает триггер 11 в единичное состояние. Блок управления 2 закрывает ключ 9 и отключает реверсивный счетчик 4, на котором, как и на счетчике 7, будет зафиксировано число,, представляющее в некотором масштабевеличину . После этого импульс с третьего выхода блока управления возвращает счетчик 7 и регистр 5 в нулевое состояние а импульс с четвертого выхода передает содержимое реверсивного счетчика 4 в регистр 5 и, кроме того, увелкчшает на единицу коэффициент деления управляемого делителя частоты 3. Так осуществляется первая итерация. Импульс блока управления начинает выполнение очередной итерации, в процессе которой возможны случаи x,j-5j9 и Xg 5 . В первом случае по достижении равенства Xg S/J возникает импульс на втором входе блока управления 2; с этого момента и до появления импульса на первом входе блока управления реверсивный счетчик 4 складывает импульсы, поступающие на его счетный вход с управляемого делителя частоты 3, число этих импул1 ов равно {x2-s;V2. Таким образом, на счетчике 4 фор-: мируется число S,+ ( 5, ) /2. Во втором случае после появления импульса на первом входе блок управления устанавливает реверсивный .счетчик 4 в режим вычитания; ключ 9 продолжает оставаться открытым, и на счетчик 7 продолжают поступать импульсы, пока их число не достигает з1а||иксированного на регистре значенияЗ,. После этого блок сравнения б пропускает импульс на второй вход блока управления, дальнейшие действия которого идентичны описанным в предыдущем случае. Таким образом, в течение времени, пропорпионального величине (х - S ), импульсы с управляемого делителя частоты 3 поступают на вычитающий вход реверсивного счетчика 4, в результате чего его содержимое, передаваемое затем в регистр 5, составляет ( ч - U 2 В дальнейшем описанная последовательность действий циклически повторяется, отличие очередного цикла от предыдущего состоит в том, что коэффициент деления управляемого делителя частоты на единицу больше. Когда .этот коэффициент достигает заданного значения, появляется единичн потенциал на втором выходе унравляемого делителя частоты, соединенного с третьим входом блока управления 2. Этот потенциал запрещает появление оч редного импульса на выходе блока упра ления, прекращая работу схемы и включая, при необходимости, соответствующу индикацию. Выходом схемы может служить выхо регистра 5 либо выход реверсивного сч чика 4. Обеспечиваемое вычислителетл повьшен скорости сходимости и точности оценки, а также его простота позволяют повысить эффективность функционирования систем, управление которыми требует определения текущего значения математического ожидания процессов в систем Формула изо б р е т е н и Рекуррентный вьгаислитель оценки математического ожидания, содержащий счетчик, генератор импульсов, триггер, -элемент задержки, управляемый делител частоты, первый выход которого подклю чен к счетному входу реверсивного счет чика, блок сравнения, о т л и ч а ющ и и с я тем, что, с целью повышени точности оценки математического ожида ния, в него введены регистр, ключи, блок управления и время-импульсный преобразователь, при этом первый выход блока управления подключен к управляющему входу время-нмпульсного преобразователя, информационный вход которого является входом вычислителя, выход время-импульсного преобразователя соединен со входом установки в нуль триггера, нулевой выход которого подключен к управляющ.ему входу первого ключа, информационный вход которого объеди- нен с информационным входом второго ключа и соединен с выходом генератора импульсов, выход первого ключа подключен ко входу установки в единицу триггера и к первому входу блока управления, второй выход которого соединен с управляющим входом второго ключа, выход которого соединен с управлякетим входом блока сравнения и через элемент задержки - со счетными входами управляемого делителя частоты и счетчика, выходы которого подключены к первой группе информационных входов блока сравнени5, вторая группа информационных входов которого соединена с соответствующими выходами регистра, вход установки в нуль которого соединен со входом установки в нуль счетчика и с третьим выходом блока управления, четвертый выход которого соединен с управляющими входами регистра и управляемого делителя частоты, первый выход которого соединен со счетным входом реверсивного счетчика, входы сложение и вычитание реверсивного счетчика . подключены соответственно к пятому и шестому выходам блока управления, третий вход .которого соединен со вторым выходом управляемого делителя частоты, а информационные входы регистра подключены к соответствующим выходам реверсивного счетчика. Источники информации, принятые BU внимание при экспертизе 1.Автсфское свидетельство СССР I 428388, кл.а06 F 15/36, 1972. 2,Авторское свидетельство СССР № 485455, кл. G Об 15/36. 1974 прототип).

X 0

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислитель оценки математического ожидания случайного процесса | 1980 |

|

SU932502A1 |

| Устройство для вычисления дисперсии случайного процесса | 1981 |

|

SU1029183A1 |

| Вероятностный интегрирующий преобразователь аналог-код | 1987 |

|

SU1441476A1 |

| Адаптивный вычислитель оценки математического ожидания | 1981 |

|

SU982014A1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

| Устройство для определения вероятностных характеристик фазы случайного сигнала | 1982 |

|

SU1112377A1 |

| Устройство для определения стационарности случайного процесса | 1981 |

|

SU1109761A1 |

| Генератор случайного импульсного процесса | 1982 |

|

SU1094032A1 |

| Устройство для вычисления математического ожидания | 1986 |

|

SU1383398A1 |

| ВЫЧИСЛИТЕЛЬ ОЦЕНКИ МАТЕМАТИЧЕСКОГО ОЖИДАНИЯ | 2002 |

|

RU2229158C1 |

Авторы

Даты

1980-07-05—Публикация

1978-03-20—Подача