VJ

ел

vj СО О

| название | год | авторы | номер документа |

|---|---|---|---|

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

| Генератор функций | 1979 |

|

SU842765A1 |

| Устройство для воспроизведения запаздывающих функций | 1983 |

|

SU1173424A1 |

| Аналого-цифровой логарифмический преобразователь | 1984 |

|

SU1236511A1 |

| Цифровой генератор функций | 1980 |

|

SU894692A1 |

| Цифровой генератор функций | 1980 |

|

SU980083A1 |

| Цифровой кусочно-линейный аппроксиматор | 1988 |

|

SU1615743A1 |

| Функциональный преобразователь | 1984 |

|

SU1241257A1 |

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

| Функциональный преобразователь нескольких переменных | 1986 |

|

SU1387022A1 |

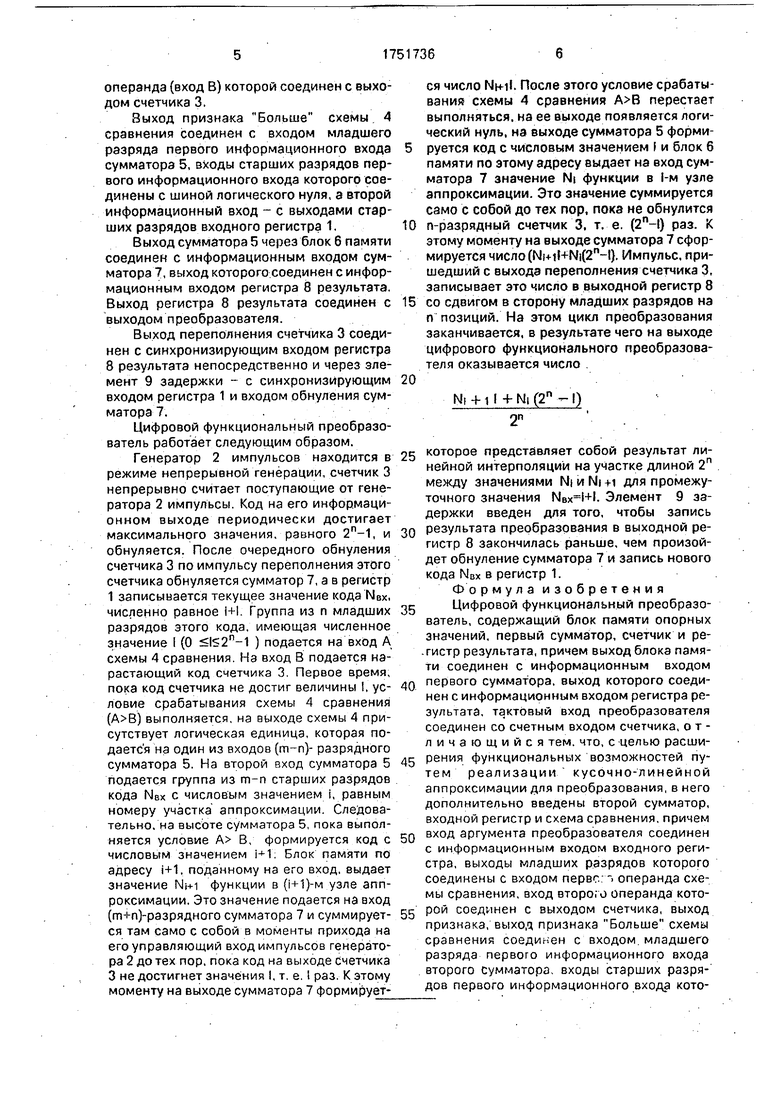

Изобретение относится к информационно-измерительной технике и может быть использовано для воспроизведения заданных функций, коррекции амплитудных характеристик датчиков, а также аппаратурной реализации специализированных арифметических устройств. Цель изобретения - расширение функциональных возможностей за счет возможности реализации кусочно-линейной аппроксимации для преобразования. Преобразователь содержит входной регистр 1, генератор 2 импульсов, соединенный с тактовым входом преобразователя, n-разрядный счетчик 3, схему 4 сравнения, сумматоры 5, 7, блок 6 памяти опорных значений, регистр 8 результата, элемент 9 задержки Преобразователь производит кусочно-линейную аппроксимацию заданной функции и при этом позволяет реализовать математическую зависимость, лежащую в основе линейной интерполяции, за один цикл заполнения счетчика с помощью небольшого количества функциональных узлов. 1 ил. in С

А

Изобретение относится к информационно-измерительной технике и может быть использовано для воспроизведения заданных функций, коррекции (в том числе линеаризации) амплитудных характеристик датчиков, аппаратурной реализации специализированных арифметических устройств. Известны преобразователи, производящие кусочно-линейную аппроксимацию заданной функции, значения которой в узлах аппроксимации, а также значения углов наклона аппроксимирующей ломаной хранятся в блоке памяти. Промежуточные значения заданной функции определяются линейной интерполяцией с помощью мно- жительно-суммирующего устройства.

Недостатками таких преобразователей являются большой объем и сложность блока памяти, в котором приходится хранить не только значения заданной функции, но и значения углов наклона аппроксимирующей ломаной

Известен также функциональный преобразователь, содержащий входной и буферный регистры, дешифратор, блок памяти, два блока вычитания, реверсивный и вычитающий счетчики, два делителя частоты, три элемента И, два элемента ИЛИ, генератор, формирователь импульсов, и триггер

Недостатком указанного преобразователя является сложность конструкции

Наиболее близким к предлагаемому по технической сущности является цифровой функциональный преобразователь, содержащий блок памяти опорных значений, первый сумматор, счетчик и регистр результата, причем выход блока памяти соединен с информационным входом первого сумматора, выход которого соединен с информационным входом регистра результата, тактовый вход преобразователя соединен со счетным входом счетчика.

Недостатком известного устройства является ограниченность функциональных возможностей (известное устройство воспроизводит лишь такие функции, которые можно представить в виде суммы экспонент).

Цель изобретения - расширение функциональных возможностей за счет возможности реализации кусочно-линейной аппроксимации заданных функций.

Поставленная цель достигается тем, что в цифровой функциональный преобразователь, содержащий блок памяти опорных значений, первый сумматор, счетчик и регистр результата, причем выход блока памяти соединен с информационным входом первого сумматора, выход которого соединен с информационным входом регистра результата, тактовый вход преобразователя соединен со счетным входом счетчика, дополнительно введены второй сумматор,

входной регистр и схема сравнения, причем вход аргумента преобразователя соединен с информационным входом входного регистра, выходы младших разрядов которого соединены с входом первого операнда

схемы сравнения, вход второго операнда которой соединен с выходом счетчика, выход признака Больше схемы сравнения соединен с входом младшего разряда первого информационного входа второго сумматора, входы старших разрядов первого информационного входа которого соединены с шиной логического нуля, второй информационный вход второго сумматора соединен с выходами старших разрядов

входного регистра, выход второго сумматора соединен с адресным входом блока памяти опорных значений, выход регистра результата соединен с выходом результата преобразователя, тактовый вход которого

соединен с синхронизирующим входом первого сумматора, выход переполнения счетчика соединен с синхронизирующим входом регистра результата непосредственно и через элемент задержки -с синхронизирующим входом входного регистра и входом обнуления первого сумматора.

Введение второго сумматора, входного регистра, схемы сравнения и связей между ними обеспечивает то, что преобразователь

производит кусочно-линейную аппроксимацию заданной функции и при этом позволяет реализовать математическую зависимость, лежащую в основе линейной интерполяции, за один цикл заполнения

счетчика с помощью небольшого количества функциональных узлов.

На чертеже приведена структурная схема цифрового функционального преобразователя.

Устройство содержит входной регистр 1, генератор 2 импульсов, соединенный с тактовым входом преобразователя, п-раз- рядный счетчик 3, схему 4 сравнения, которая может быть выполнена на цифровом

компараторе, сумматор 5, блок 6 памяти опорных значений, сумматор 7, регистр 8 результата и элемент 9 задержки.

Тактовый вход преобразователя соединен со счетным входом счетчика 3 и с синхронизирующим входом сумматора 7,

Вход аргумента преобразователя соединен с информационным входом входного регистра 1, выходы младших разрядов кото рого соединены с входом первого операнда

схемы 4 сравнения (вход А), вход второго

операнда (вход В) которой соединен с выходом счетчика 3.

Выход признака Больше схемы 4 сравнения соединен с входом младшего разряда первого информационного входа сумматора 5, входы старших разрядов первого информационного входа которого соединены с шиной логического нуля, а второй информационный вход - с выходами старших разрядов входного регистра 1.

Выход сумматора 5 через блок 6 памяти соединен с информационным входом сумматора 7, выход которого соединен с информационным входом регистра 8 результата. Выход регистра 8 результата соединен с выходом преобразователя.

Выход переполнения счетчика 3 соединен с синхронизирующим входом регистра 8 результата непосредственно и через элемент 9 задержки - с синхронизирующим входом регистра 1 и входом обнуления сумматора 7.

Цифровой функциональный преобразователь работает следующим образом.

Генератор 2 импульсов находится в режиме непрерывной генерации, счетчик 3 непрерывно считает поступающие от генератора 2 импульсы. Код на его информационном выходе периодически достигает максимального значения, равного 2п-1, и обнуляется. После очередного обнуления счетчика 3 по импульсу переполнения этого счетчика обнуляется сумматор 7, а в регистр 1 записывается текущее значение кода NBx, численно равное i+l. Группа из п младших разрядов этого кода, имеющая численное значение I (0 lS2n-1 ) подается на вход А схемы 4 сравнения. На вход В подается нарастающий код счетчика 3. Первое время, пока код счетчика не достиг величины 1, условие срабатывания схемы 4 сравнения () выполняется, на выходе схемы 4 присутствует логическая единица, которая подается на один из входов (m-n)- разрядного сумматора 5. На второй вход сумматора 5 подается группа из m-n старших разрядов кода NBX с числовым значением i, равным номеру участка аппроксимации. Следовательно, на высоте сумматора 5, пока выполняется условие А В, формируется код с числовым значением i+1. Блок памяти по адресу i+1, поданному на его вход, выдает значение Nj+i функции в (1+1)-м узле аппроксимации. Это значение подается на вход (т+п)-разрядного сумматора 7 и суммируется там само с собой в моменты прихода на его управляющий вход импульсов генератора 2 до тех пор, пока код на выходе счетчика 3 не достигнет значения I, т. е. I раз. К этому моменту на выходе сумматора 7 формируется число Мьн1. После этого условие срабатывания схемы 4 сравнения перестает выполняться, на ее выходе появляется логический нуль, на выходе сумматора 5 форми5 руется код с числовым значением I и блок 6 памяти по этому адресу выдает на вход сумматора 7 значение NI функции в i-м узле аппроксимации. Это значение суммируется само с собой до тех пор, пока не обнулится

0 n-разрядный счетчик 3. т. е. (2n-l) раз. К этому моменту на выходе сумматора 7 сформируется число (Ni+il+Ni(2n-l). Импульс, пришедший с выхода переполнения счетчика 3, записывает это число в выходной регистр 8

5 со сдвигом в сторону младших разрядов на п позиций. На этом цикл преобразования заканчивается, в результате чего на выходе цифрового функционального преобразователя оказывается число

0

NI +11 + Nt (2П - I) 2П

5 которое представляет собой результат линейной интерполяции на участке длиной 2 между значениями NI и NI +1 для промежуточного значения . Элемент 9 задержки введен для того, чтобы запись

о результата преобразования в выходной регистр 8 закончилась раньше, чем произойдет обнуление сумматора 7 и запись нового кода NBX в регистр 1.

Формула изобретения

5 Цифровой функциональный преобразователь, содержащий блок памяти опорных значений, первый сумматор, счетчик и ре- .гистр результата, причем выход блока памяти соединен с информационным входом

Q первого сумматора, выход которого соединен с информационным входом регистра результата, тактовый вход преобразователя соединен со счетным входом счетчика, отличающийся тем. что, с целью расши5 рения функциональных возможностей путем реализации кусочно-линейной аппроксимации для преобразования, в него дополнительно введены второй сумматор, входной регистр и схема сравнения, причем

Q вход аргумента преобразователя соединен с информационным входом входного регистра, выходы младших разрядов которого соединены с входом первс операнда схемы сравнения, вход второго операнда кото5 рой соединен с выходом счетчика, выход признака, выход признака Больше схемы сравнения соедиг-.ен с входом младшего разряда первого информационного входа второго сумматора, входы старших разрядов первого информационного входа кото

рого соединены с шиной логического нуля,которого соединен с синхронизирующим

второй информационный вход второго сум-входом первого сумматора, выход переполматоря соединен с выходами старших раз-нения счетчика соединен ссинхронизируюрядов входного регистра, выход второгощим входом регистра результата

сумматора соединен с адресным входом5 непосредственно, а через элемент задержблока памяти опорных значений, выход ре-ки - с синхронизирующим входом входного

гистрз результата соединен с одноименнымрегистра и входом обнуления первого сумвыходом преобразователя, тактовый входматора.

| Смолов В | |||

| Б | |||

| Функциональные преобразователи информации | |||

| Л.: Энергоиздат, 1981, с | |||

| Веникодробильный станок | 1921 |

|

SU53A1 |

| Способ сопряжения брусьев в срубах | 1921 |

|

SU33A1 |

| Цифровой генератор функций | 1986 |

|

SU1324092A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

Авторы

Даты

1992-07-30—Публикация

1990-07-18—Подача