(5) ЦИФРОВОЙ ГЕНЕРАТОР ФУНКЦИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь | 1977 |

|

SU742947A1 |

| Цифровой преобразователь координат | 1980 |

|

SU942004A1 |

| Генератор функций | 1979 |

|

SU842765A1 |

| Устройство для воспроизведения функций | 1984 |

|

SU1182539A1 |

| Аппроксимирующий функциональный преобразователь | 1984 |

|

SU1205153A1 |

| Цифровой кусочно-линейный аппроксиматор | 1988 |

|

SU1615743A1 |

| Устройство для воспроизведения переменных во времени коэффициентов | 1981 |

|

SU1005087A1 |

| Генератор функций | 1990 |

|

SU1758641A1 |

| Вычислительное устройство | 1982 |

|

SU1040493A1 |

| Устройство для вычисления функций синуса и косинуса | 1980 |

|

SU907546A1 |

I

Изобретение относится к автоматике и вычислительной технике и может быть использовано в специализированных вычислительных устройствах для воспроизведения функциональных зависимостей при жестких требованиях к объему запоминающего устройства.

Известен цифровой генератор функций, содержащий блоки памяти, регистры, коммутаторы, блок сдвига l Недостатком известного генератора является большой объем аппаратурных затрат.

Наиболее близким к предлагаемому является цифровой генератор функций, содержащий два регистра, дешифратор, два блока памяти, блок умножения, сумматор, два коммутатора, состоящие из элементов И, .

Однако в известном генераторе в цифровой форме воспроизводится кусочно-линейная функция, интерполирующая исходную функцию на системе двоичнорациональных узлов , ,1 ,...2 .

Для этого требуется хранить 2N значений функции в узловых точках и 2 значений производной функции в этих же точках. В общей сложности данный метод требует 2 ячеек памяти в двух запоминающих устройствах.

Цель изобретения - упрощение цифрового генератора функций.

Поставленная цель достигается тем, что цифровой генератор функций, соtoдержащий регистр старших и регистр младших разрядов аргумента, дешифратор, блок памяти, блок умножения, сумматор, коммутатор, элементы И, причем выходы регистра младших разрядов арISгумента подключены к первой группе входов блока умножения, выходы которого подключены к первой группе входов сумматора, выходы сумматора являются выходами цифрового генератора

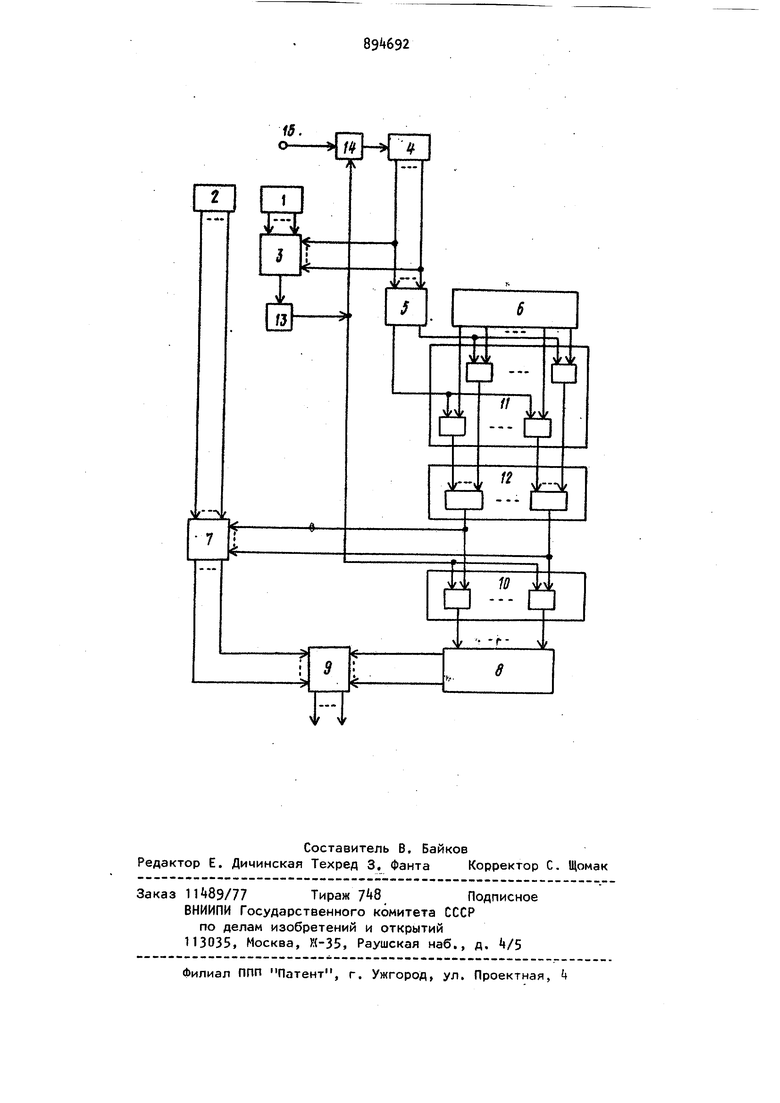

20 функций, выходы дешифратора подключены к управляющим, а выходы блока памяти - к информационным входам коммутатора, выходы которого подключены 3 . ко второй группе входов блока умножения, содержит схему сравнения, счетчик, накапливающий сумматор, элемент НЕ и дополнительнв|й элемент И, причем выходы регистра старших разрядов аргумента подключены к лервой группе входов схемы сравнения, а выходы счетчика - ко второй группе входов схемы сравнения и входам дешифратора, выход схемы сравнения через элемент НЕ подключен к первым входам элементов И и первому входу дополнительного элемента И, вторые входы эле ментов И подключены к выходам коммутатора, выходы элементов И подключены ко входам накапливающего сумматора, выходы которого подключены ко второй группе входов сумматора, второй вход дополнительного элемента И подключен тактовому входу цифрового генератора функций, а выход дополнительного элемента И - ко входу счетчика. На чертеже представлен цифровой генерат@р функций, функциональная схема. Цифровой генератор функций содержит регистр 1 старших и регистр 2 млад ших разрщов аргумента, схему 3 сравнения, счетчик 4, дешифратор 5, бЛок 6 памяти, блок 7 умножения, накапливающий сумматор 8, сумматор 9 овлементы И 10, коммутатор, состоящий из элементов И 11, ИЛИ 12, элемент НЕ 13 дополнительный элемент И 1А, тактовый вход 15. В генераторе в цифровой форме вычисляется значение кусочно-линейной функции у(х), интерполирующей заданную к воспроизведению функцию f(x) по системе двоичйо-рациональных узлов j/2 при ,1,...,2,когда значение аргумента фиксируется в двух регистрах так, что старшие разряды располагаются в первом регистре, а младшиево втором. Значение генерируемой кусочно-линейной функции при фиксированном аргументе X вычисляется в соответствии с формулой fCx V-iHCxj) vu)-fCV3bU-Xj) , где f(x) является значением исходной функции f(x)B yзлoвoйтoчкexl J/2 . Это значение вычисляется в устрой стве следующим образом. (((х,-,,)-Пх,(хо)( 2 Принимая обозначение (x-)-f (х-), получаем (X)-- &i 24x-X5)j;Xj Х5Х.,чГ Таким образом, при фиксированном значении аргумента х на регистрах устройства содержимое счетчика npo6eraet значения от О до J, т.е. номера yMactков аппроксимации от первого до текущего. При этом накапливаются значения л, хранящиеся в блоке 6 памяти, и затем вычисляется искомое значение аппроксимирующей функции у(х) в соответствии с 2 .путем одного умножения и.одного сложения о Выполнение операции 2 (x-xj) при $ х. автоматически реализуете интерпретацией кода аргумента ejO; Ц в виде правильной двоичной дроби в которой запятая фиксируется перед старшим разрядом. В исходном положении на накапливающем сумйаторе 8 устанавливается кой значения f{xQ), счетчик устанавливается в положение О. В блоке 6 памяти находятся значения первых разностей д , j 0,1,2,... 1. На регистры 1 и 2 принижается код значения аргумента. Так как содержимое регистра 1 не равно содержимому счетчика 4, то на выходе схемы 3 сравнения кодов имеется сигнал О. Следовательно, сигнал 1 с выхода элемента НЕ 13 открывает элемент И Н и группу элементов И 10. На счетчик.:4 через элемент И 14 поступают тактовые импульсы, заполняющие cчetчик k. Содержимое счетчика 4 постоянно дешифрируется дешифратором 5 из блока памяти 6 через коммутатор {элементы И 11, ИЛИ 12) и группу элементов И 10 значения первых разностей поступают на накапливающйй сумматор 8, где суммируются в соответствии с (1). На J-OM такте содержимое счетчика Ц оказывается равным содержимому регистра 1 (старшим разрядам аргумента). Срабатывает схема 3 сравнения кодов на ее выходе появляется сигнал 1. Прекращается заполнение счетчика тактовыми импульсами и закрываются элементы И 10. Последней разностью, поступившей на накапливающий сумматор 8, оказывается разность Однако на вторые входы блока 7 умножения из блока 6 памяти поступает значение разности j, соответствующее устаноаленмому на счетчике номеру участка аппроксимации.

Производится переменожение по 2 ) младших разрядов аргумента х и разнсх:ти д j, и затем в сумматоре 9 образуется искомое значение аппроксимирующей кусочно-линейной функции у(х),

Таким о бразом, в предлагаемом устройстве по сравнению с известным объемом памяти уменьшается ровмо.в два раза.

.Формула изобретения

Цифровой генератор функций, содержащий регистр старших и регистр младших разрядов аргумента, дешифратор, блок памяти, блок умножения, сумматор KOMMyTaTojf), элементы И, причем выходы регистра младших разрядов аргумента подключены к первой группе входов бло ка умножения, выходы которого подключены к первой группе входов сумматора выходы сумматора являются выходами цифрового генератора функций, выходы дешифратора подключены к управляющим, а выходы блока памяти - к информационным входам коммутатора, В1ыходы которого подключены ко втором группе входов блока умножения, о т л и чающийся тем, что, с целью упрощения цифрового генератора функций, он содержит схему сравнения,счетчик, накалливающий сумматор, элемент НЕ и дополнительный элемент И, причем выходы регистра старших разрядов аргумента подключены к первой группе входов схемы сравнения, а выходы счетчика - ко второй группе входов схемы сравнения и ко входам дешифратора, выход схемы сравнения через элемент НЕ подключен :к первым входам элементов И и первому входу дополнительного элемента И, вторые входы элементов И подключены к выходам коммутатора, выходы элементов И подключены ко входам накапливающего сумматора, выходы которого подкш)чены ко второй группе входов сумматора, второй вход дополнительного элемента И подкш)чен к тактовому входу цифрового генератора функций, а выход дополнительного элемента И - ко входу счетчика. Источники информации, принятые во внимание при экспертизе

№ , кл. G Об F 1/02, IS (прототип) .

н

Авторы

Даты

1981-12-30—Публикация

1980-04-28—Подача