Изобретение относится к вычислительной технике и может быть использовано при аппаратной реализации устройств нормализации (денормализации) мантисс числа в высокопроизводительных вычислительных системах, реализующих операции с плавающей запятой.

Цель изобретения - повышение быстродействия ,

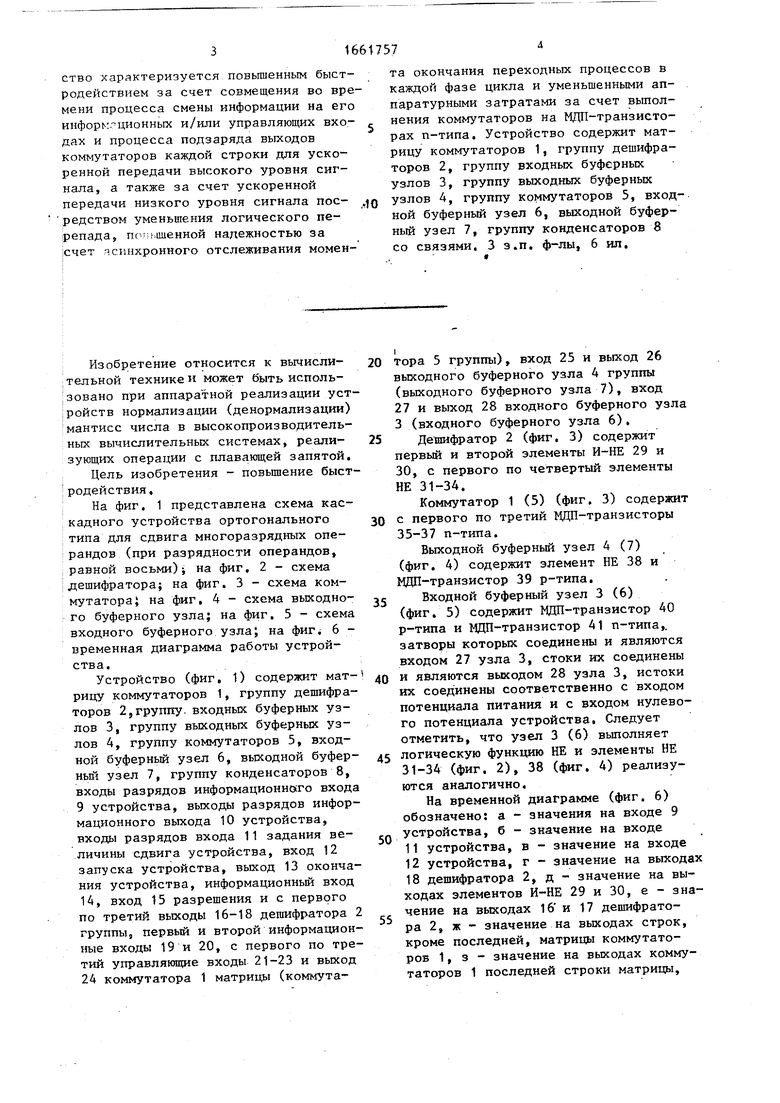

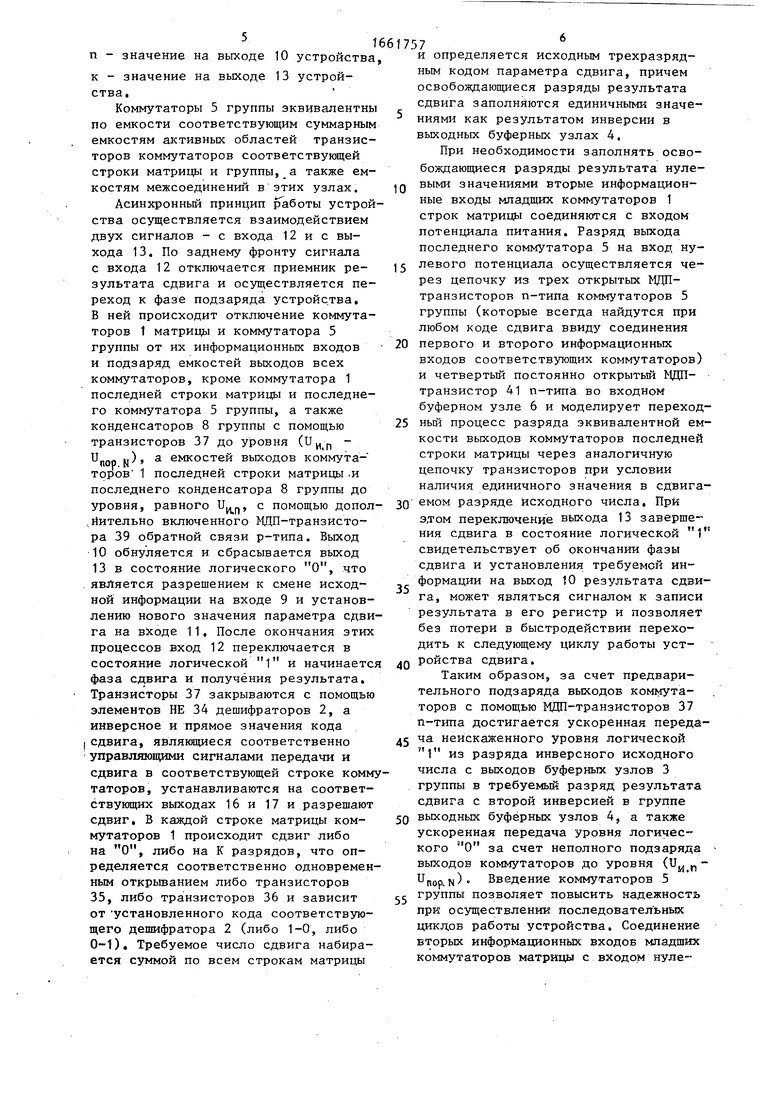

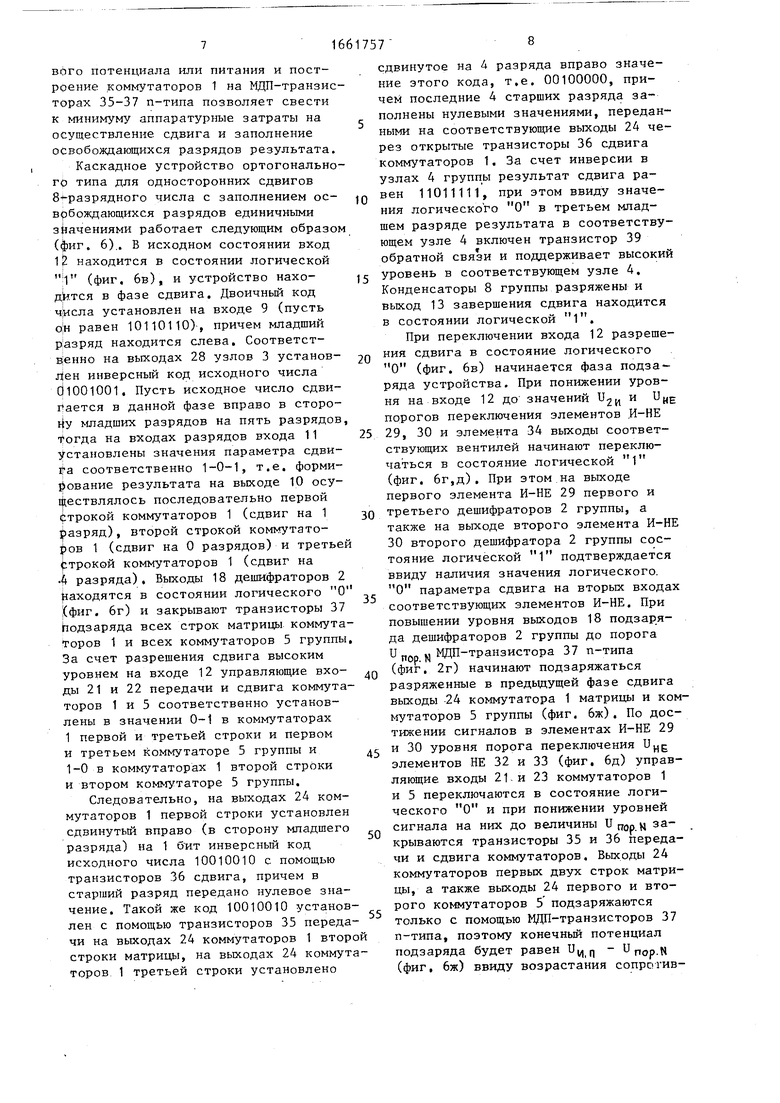

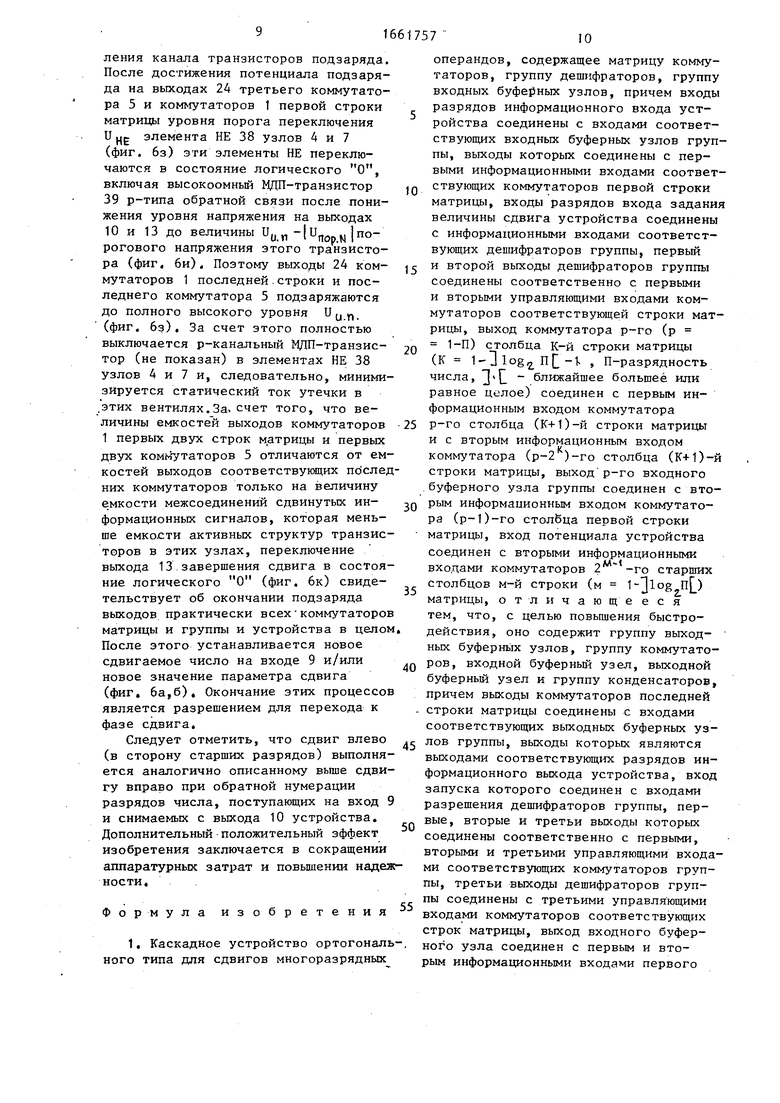

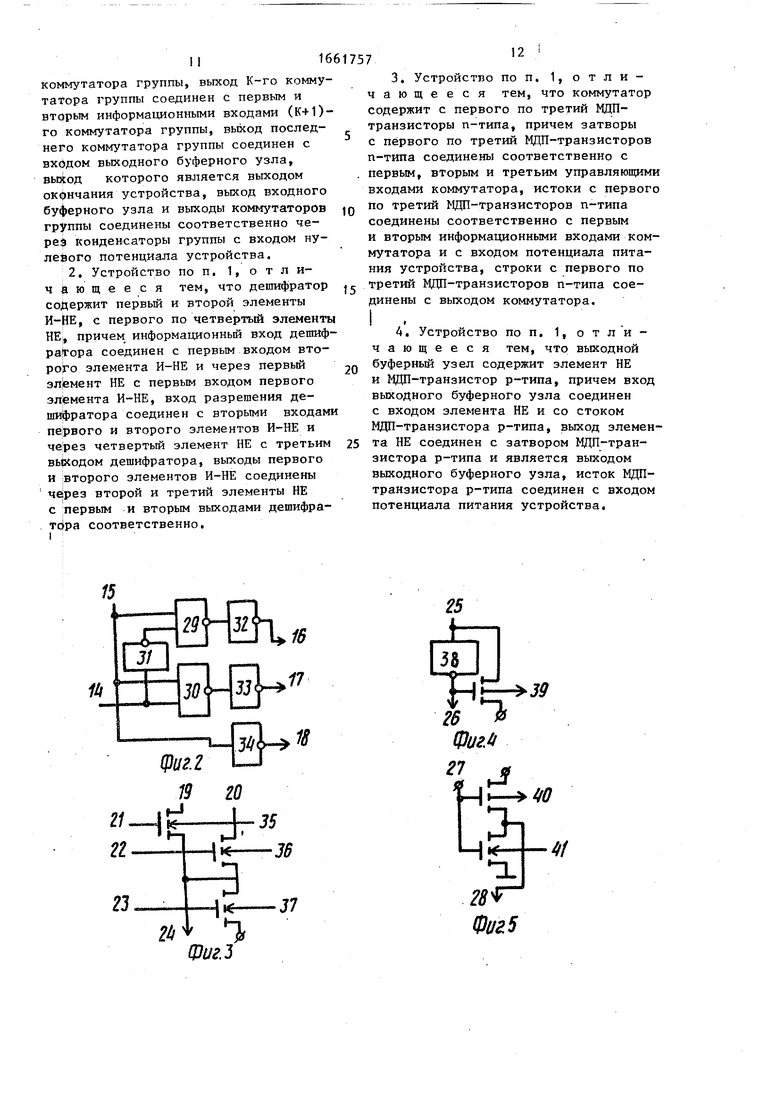

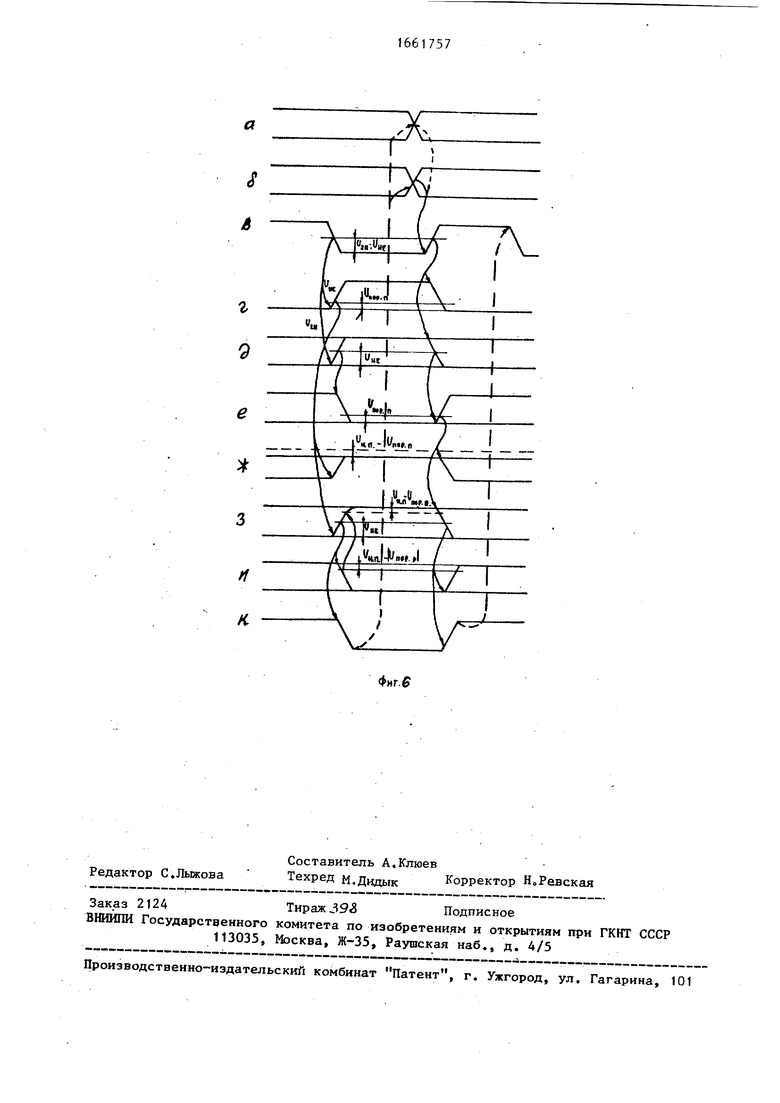

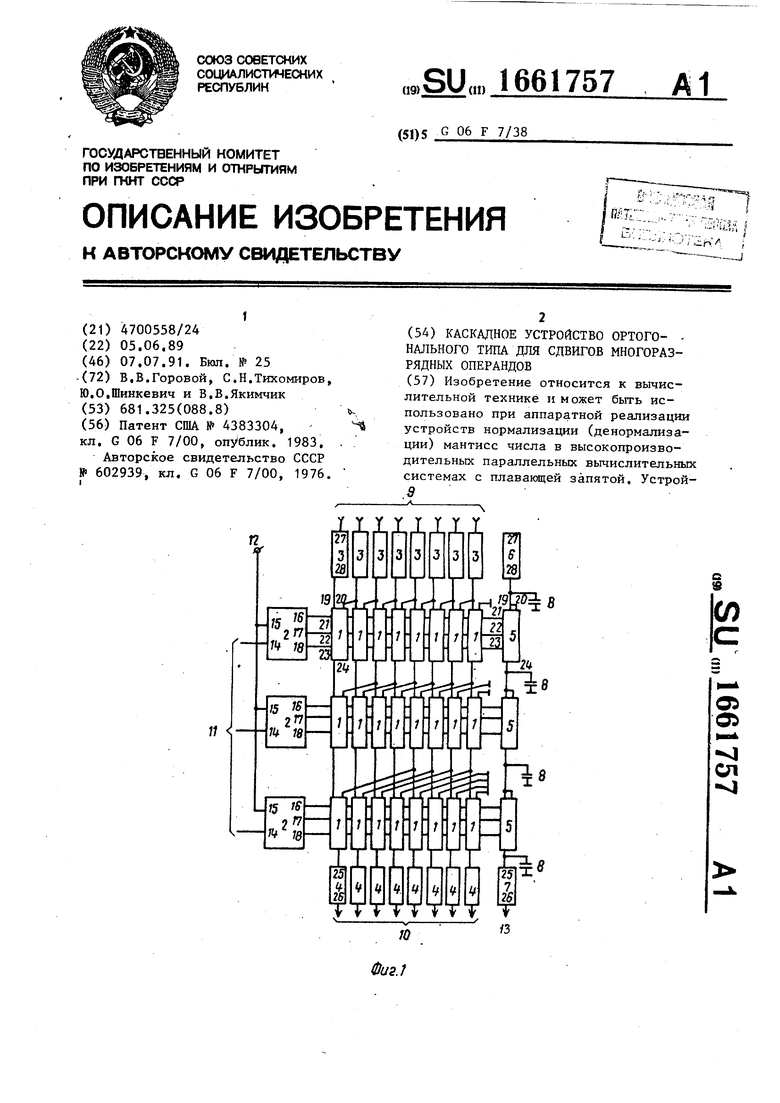

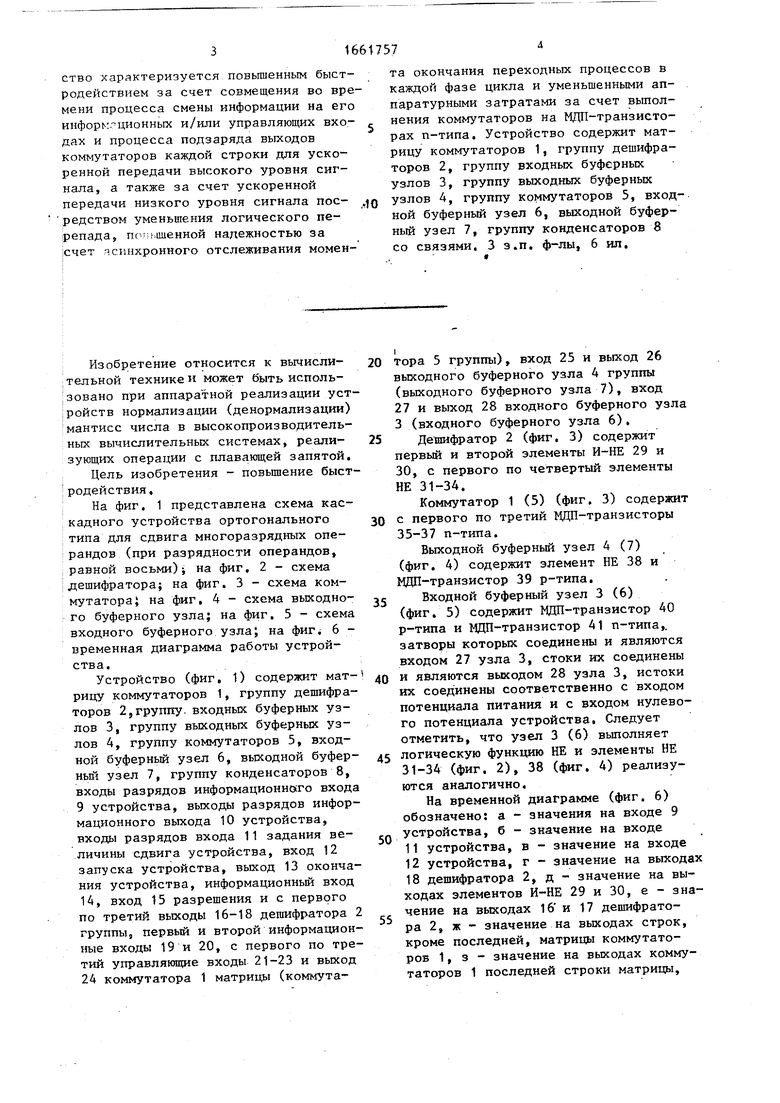

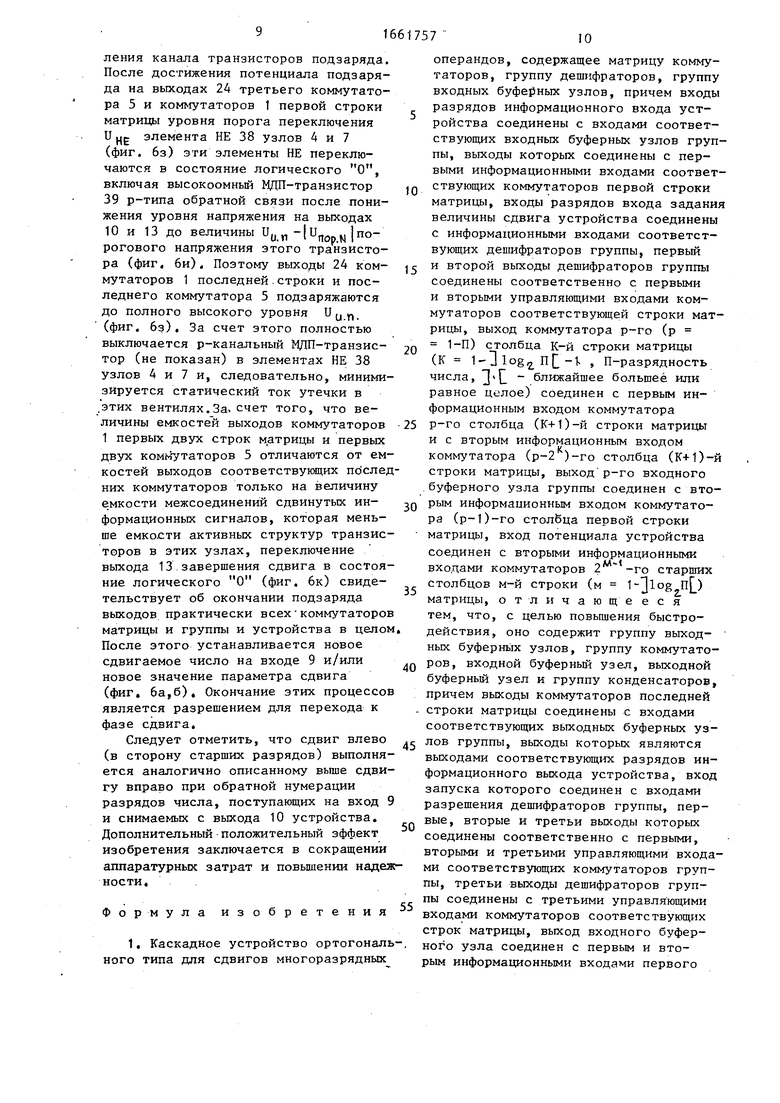

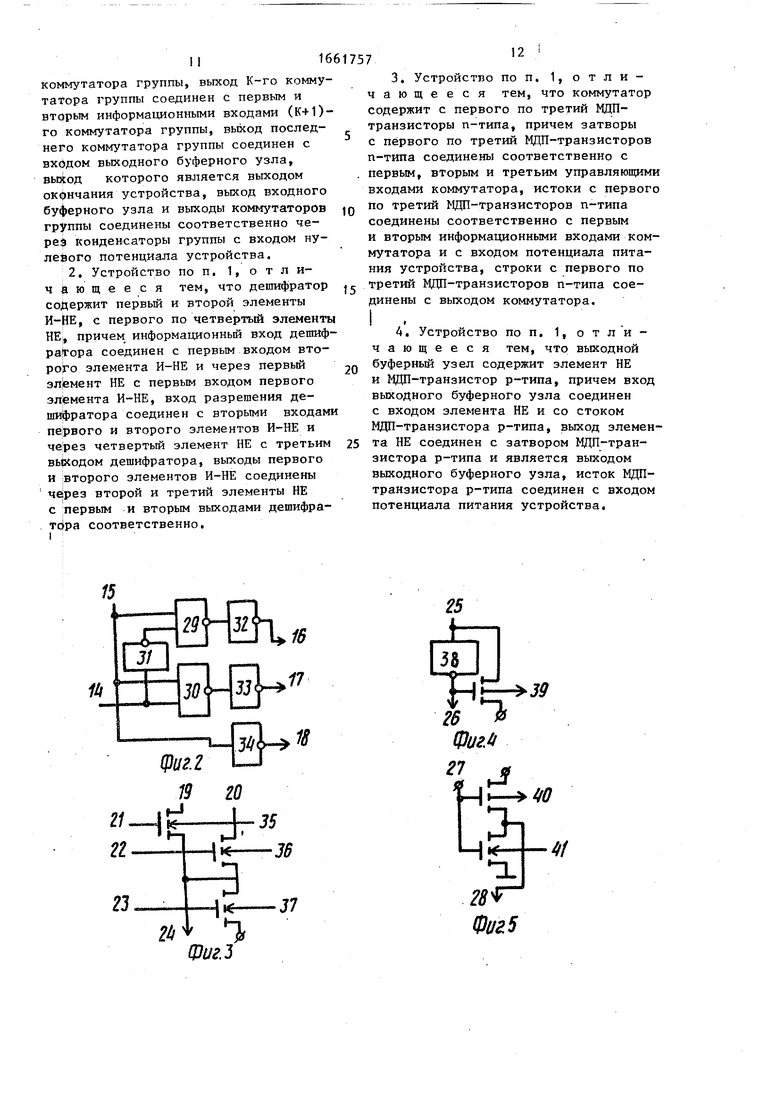

На фиг. 1 представлена схема каскадного устройства ортогонального типа для сдвига многоразрядных операндов (при разрядности операндов, равной восьми); на фиг. 2 - схема дешифратора; на фиг. 3 - схема коммутатора} на фиг, 4 - схема выходного буферного узла; на фиг. 5 - схема входного буферного узла; на фиг. 6 - временная диаграмма работы устройства.

Устройство (фиг. 1) содержит матрицу коммутаторов 1, группу дешифраторов 2,группу входных буферных узлов 3, группу выходных буферных узлов 4, группу коммутаторов 5, входной буферный узел 6, выходной буферный узел 7, группу конденсаторов 8, входы разрядов информационного входа 9 устройства, выходы разрядов информационного выхода 10 устройства, входы разрядов входа 11 задания величины сдвига устройства, вход 12 запуска устройства, выход 13 окончания устройства, информационный вход 14, вход 15 разрешения и с первого по третий выходы 16-18 дешифратора 2 группы, первый и второй информационные входы 19 и 20, с первого по третий управляющие входы 21-23 и выход 24 коммутатора 1 матрицы (коммутатора 5 группы), вход 25 и выход 26 выходного буферного узла 4 группы (выходного буферного узла 7), вход 27 и выход 28 входного буферного узла 3 (входного буферного узла 6).

Дешифратор 2 (фиг. 3) содержит первый и второй элементы И-НЕ 29 и 30, с первого по четвертый элементы НЕ 31-34.

Коммутатор 1 (5) (фиг. 3) содержит

с первого по третий МДП-транзисторы 35-37 п-типа.

Выходной буферный узел 4 (7) (фиг. 4) содержит элемент НЕ 38 и МДП-транзистор 39 р-типа.

Входной буферный узел 3 (6)

(фиг. 5) содержит МДП-транзистор 40 р-типа и МДП-транзистор 41 п-типа,. затворы которых соединены и являются входом 27 узла 3, стоки их соединены

и являются выходом 28 узла 3, истоки их соединены соответственно с входом потенциала питания и с входом нулевого потенциала устройства. Следует отметить, что узел 3 (6) выполняет

логическую функцию НЕ и элементы НЕ 31-34 (фиг. 2), 38 (фиг. 4) реализуются аналогично.

На временной диаграмме (фиг. 6) обозначено: а - значения на входе 9 устройства, 6 - значение на входе

11устройства, в - значение на входе

12устройства, г - значение на выходах 18 дешифратора 2, д - значение на выходах элементов И-НЕ 29 и 30, е - значение на выходах 16 и 17 дешифратора 2, ж - значение на выходах строк, кроме последней, матрицы коммутаторов 1,з- значение на выходах коммутаторов 1 последней строки матрицы,

- значение на выходе 10 устройства, к - значение на выходе 13 устройства.

Коммутаторы 5 группы эквивалентны по емкости соответствующим суммарным емкостям активных областей транзисторов коммутаторов соответствующей строки матрицы и группы, а также емкостям межсоединений в этих узлах.

Асинхронный принцип работы устройства осуществляется взаимодействием двух сигналов - с входа 12 и с выхода 13. По заднему фронту сигнала с входа 12 отключается приемник результата сдвига и осуществляется переход к фазе подзаряда устройства. В ней происходит отключение коммутаторов 1 матрицы и коммутатора 5 группы от их информационных входов и подзаряд емкостей выходов всех коммутаторов, кроме коммутатора 1 последней строки матрицы и последнего коммутатора 5 группы, а также конденсаторов 8 группы с помощью транзисторов 37 до уровня ( U

пор. ц

), а емкостей выходов коммута-

торов 1 последней строки матрицы .и последнего конденсатора 8 группы до уровня, равного илп, с помощью дополнительно включенного МДП-транзисто- ра 39 обратной связи р-типа. Выход 10 обнуляется и сбрасывается выход 13 в состояние логического О, что является разрешением к смене исходной информации на входе 9 и установению нового значения параметра сдвига на входе 11. После окончания этих процессов вход 12 переключается в состояние логической 1 и начинается аза сдвига и получения результата. ранзисторы 37 закрываются с помощью элементов НЕ 34 дешифраторов 2, а нверсное и прямое значения кода сдвига, являющиеся соответственно правляющими сигналами передачи и сдвига в соответствующей строке коммутаторов, устанавливаются на соответствующих выходах 16 и 17 и разрешают двиг. В каждой строке матрицы комутаторов 1 происходит сдвиг либо а О, либо на К разрядов, что оп166

ределяется соответственно одновременным открыванием либо транзисторов 35, либо транзисторов 36 и зависит от установленного кода соответствующего дешифратора 2 (либо 1-0, либо 0-1). Требуемое число сдвига набирается суммой по всем строкам матрицы

10

15

20

25

661757°

и определяется исходным трехразрядным кодом параметра сдвига, причем освобождающиеся разряды результата сдвига заполняются единичными значениями как результатом инверсии в выходных буферных узлах 4.

При необходимости заполнять освобождающиеся разряды результата нулевыми значениями вторые информационные входы младщих коммутаторов 1 строк матрицы соединяются с входом потенциала питания. Разряд выхода последнего коммутатора 5 на вход нулевого потенциала осуществляется через цепочку из трех открытых МДП- транзисторов n-типа коммутаторов 5 группы (которые всегда найдутся при любом коде сдвига ввиду соединения первого и второго информационных входов соответствующих коммутаторов) и четвертый постоянно открытый МДП- транзистор 41 n-типа во входном буферном узле 6 и моделирует переходный процесс разряда эквивалентной емкости выходов коммутаторов последней строки матрицы через аналогичную цепочку транзисторов при условии наличия единичного значения в сдвигаемом разряде исходного числа. При э,том переключение выхода 13 завершения сдвига в состояние логической 1 свидетельствует об окончании фазы сдвига и установления требуемой информации на выход 10 результата сдвига, может являться сигналом к записи результата в его регистр и позволяет без потери в быстродействии переходить к следующему циклу работы устройства сдвига.

Таким образом, за счет предварительного подзаряда выходов коммутаторов с помощью МДП-транзисторов 37 n-типа достигается ускоренная переда45 ча неискаженного уровня логической 1 из разряда инверсного исходного числа с выходов буферных узлов 3 группы в требуемый разряд результата сдвига с второй инверсией в группе

50 выходных буферных узлов 4, а также ускоренная передача уровня логического О за счет неполного подзаряда - выходов коммутаторов до уровня (UM R- пор. Введение коммутаторов 5 группы позволяет повысить надежность при осуществлении последовательных цикдов работы устройства. Соединение вторых информационных входов младших коммутаторов матрицы с входом нуле30

35

40

55

Brtro потенциала или питания и построение коммутаторов 1 на МДП-транзис- торах 35-37 n-типа позволяет свести к минимуму аппаратурные затраты на осуществление сдвига и заполнение освобождающихся разрядов результата.

Каскадное устройство ортогонального типа для односторонних сдвигов 8+-разрядного числа с заполнением ос- врбождающихся разрядов единичными значениями работает следующим образом (фиг. 6). В исходном состоянии вход 12 находится в состоянии логической 1 (фиг. 6в), и устройство находится в фазе сдвига. Двоичный код числа установлен на входе 9 (пусть он равен 10110110), причем младший разряд находится слева. Соответственно на выходах 28 узлов 3 установ- Л;ен инверсный код исходного числа d1001001. Пусть исходное число сдвигается в данной фазе вправо в сторо- йу младших разрядов на пять разрядов, Тогда на входах разрядов входа 11 установлены значения параметра сдви- Га соответственно 1-0-1, т.е. формирование результата на выходе 10 осуществлялось последовательно первой Строкой коммутаторов 1 (сдвиг на 1 разряд), второй строкой коммутаторов 1 (сдвиг на 0 разрядов) и третьей трокой коммутаторов 1 (сдвиг на 4 разряда). Выходы 18 дешифраторов 2 (находятся в состоянии логического О (фиг. 6г) и закрывают транзисторы 37 Иодзаряда всех строк матрицы коммутаторов 1 и всех коммутаторов 5 группы. За счет разрешения сдвига высоким уровнем на входе 12 управляющие входы 21 и 22 передачи и сдвига коммутаторов 1 и 5 соответственно установлены в значении 0-1 в коммутаторах 1 первой и третьей строки и первом и третьем коммутаторе 5 группы и 1-0 в коммутаторах 1 второй строки и втором коммутаторе 5 группы.

Следовательно, на выходах 24 коммутаторов 1 первой строки установлен сдвинутый вправо (в сторону младшего разряда) на 1 бит инверсный код исходного числа 10010010 с помощью транзисторов 36 сдвига, причем в старший разряд передано нулевое значение. Такой же код 10010010 установлен с помощью транзисторов 35 передачи на выходах 24 коммутаторов 1 второ строки матрицы, на выходах 24 коммутаторов 1 третьей строки установлено

0

5

0

5

0

5

0

5

сдвинутое на 4 разряда вправо значение этого кода, т.е. 00100000, причем последние 4 старших разряда заполнены нулевыми значениями, переданными на соответствующие выходы 24 через открытые транзисторы 36 сдвига коммутаторов 1, За счет инверсии в узлах 4 группы результат сдвига равен 11011111, при этом ввиду значения логического О в третьем младшем разряде результата в соответствующем узле 4 включен транзистор 39 обратной связи и поддерживает высокий уровень в соответствующем узле 4. Конденсаторы 8 группы разряжены и выход 13 завершения сдвига находится в состоянии логической 1.

При переключении входа 12 разрешения сдвига в состояние логического О (фиг. 6в) начинается фаза подза- ряда устройства. При понижении уровня на входе 12 до значений U2(1 и UHE порогов переключения элементов И-НЕ 29, 30 и элемента 34 выходы соответствующих вентилей начинают переключаться в состояние логической 1 (фиг. 6г,д). При этом на выходе первого элемента И-НЕ 29 первого и третьего дешифраторов 2 группы, а также на выходе второго элемента И-НЕ 30 второго дешифратора 2 группы состояние логической 1 подтверждается ввиду наличия значения логического. О параметра сдвига на вторых входах соответствующих элементов И-НЕ. При повышении уровня выходов 18 подзаря- да дешифраторов 2 группы до порога U пор МДП-транзистора 37 п-типа (фиг, 2г) начинают подзаряжаться разряженные в предыдущей фазе сдвига выходы 24 коммутатора 1 матрицы и коммутаторов 5 группы (фиг. 6ж). По достижении сигналов в элементах И-НЕ 29 и 30 уровня порога переключения UHE элементов НЕ 32 и 33 (фиг. 6д) управляющие входы 21 и 23 коммутаторов 1 и 5 переключаются в состояние логического О и при понижении уровней сигнала на них до величины U П0р закрываются транзисторы 35 и 36 передачи и сдвига коммутаторов. Выходы 24 коммутаторов первых двух строк матрицы, а также выходы 24 первого и второго коммутаторов 5 подзаряжаются только с помощью МДП-транзисторов 37 n-типа, поэтому конечный потенциал подзаряда будет равен ии п - U пор (фиг, 6ж) ввиду возрастания сопрогивления канала транзисторов подзаряда. После достижения потенциала подэаря- да на выходах 24 третьего коммутатора 5 и коммутаторов 1 первой строки матрицы уровня порога переключения U НЕ элемента НЕ 38 узлов 4 и 7 (фиг. 6з) эти элементы НЕ переключаются в состояние логического О, включая высокоомный МДП-транзистор 39 р-типа обратной связи после понижения уровня напряжения на выходах 10 и 13 до величины Uun -|UnopW{порогового напряжения этого транзистора (фиг. 6и). Поэтому выходы 24 ком- мутаторов 1 последней строки и последнего коммутатора 5 подзаряжаются до полного высокого уровня Uy.n. (фиг. 6з), За счет этого полностью выключается р-канальный МДП-транзис- тор (не показан) в элементах НЕ 38 узлов 4 и 7 и, следовательно, минимизируется статический ток утечки в .этих вентилях.За- счет того, что величины емкостей выходов коммутаторов 1 первых двух строк матрицы и первых двух коммутаторов 5 отличаются от емкостей выходов соответствующих последних коммутаторов только на величину емкости межсоединений сдвинутых ин- формационных сигналов, которая меньше емкости активных структур транзисторов в этих узлах, переключение выхода 13 завершения сдвига в состояние логического О (фиг. 6к) свидетельствует об окончании подзаряда выходов практически всех коммутаторов матрицы и группы и устройства в целом После этого устанавливается новое сдвигаемое число на входе 9 и/или новое значение параметра сдвига (фиг. 6а,б). Окончание этих процессов является разрешением для перехода к фазе сдвига.

Следует отметить, что сдвиг влево (в сторону старших разрядов) выполняется аналогично описанному выше сдвигу вправо при обратной нумерации разрядов числа, поступающих на вход 9 и снимаемых с выхода 10 устройства. Дополнительный положительный эффект изобретения заключается в сокращении аппаратурных затрат и повышении надежности.

Формула изобретения

1. Каскадное устройство ортогональ-. ного типа для сдвигов многоразрядных

Q 0 5 о

. 35

50

5

.

операндов, содержащее матрицу коммутаторов, группу дешифраторов, группу входных буферных узлов, причем входы разрядов информационного входа устройства соединены с входами соответствующих входных буферных узлов группы, выходы которых соединены с первыми информационными входами соответствующих коммутаторов первой строки матрицы, входы разрядов входа задания величины сдвига устройства соединены с информационными входами соответствующих дешифраторов группы, первый и второй выходы дешифраторов группы соединены соответственно с первыми и вторыми управляющими входами коммутаторов соответствующей строки матрицы, выход коммутатора р-го (р 1-П) столбца К-й строки матрицы (К 1- J log пЈ -1 , П-разрядность числа, Ј. ближайшее большее или равное целое) соединен с первым информационным входом коммутатора р-го столбца (К+1)-и строки матрицы и с вторым информационным входом коммутатора (р-2 )-го столбца (К+1)-й строки матрицы, выход р-го входного буферного узла группы соединен с вторым информационным входом коммутатора (р-1)-го столбца первой строки матрицы, вход потенциала устройства соединен с вторыми информационными входами коммутаторов 2 -го старших столбцов м-й строки (м 1 31°87П.) матрицы, отличающе еся тем, что, с целью повышения быстродействия, оно содержит группу выходных буферных узлов, группу коммутаторов, входной буферный узел, выходной буферный узел к группу конденсаторов, причем выходы коммутаторов последней строки матрицы соединены с входами соответствующих выходных буферных узлов группы, выходы которых являются выходами соответствующих разрядов информационного выхода устройства, вход запуска которого соединен с входами разрешения дешифраторов группы, первые, вторые и третьи выходы которых соединены соответственно с первыми, вторыми и третьими управляющими входами соответствующих коммутаторов группы, третьи выходы дешифраторов группы соединены с третьими управляющими входами коммутаторов соответствующих строк матрицы, выход входного буферного узла соединен с первым и вторым информационными входами первого

11

коммутатора группы, выход К-го коммутатора группы соединен с первым и вторым информационными входами (К+1)- го коммутатора группы, выход последнего коммутатора группы соединен с входом выходного буферного узла, выход которого является выходом окончания устройства, выход входного буферного узла и выходы коммутаторов группы соединены соответственно че- реЈ конденсаторы группы с входом нулевого потенциала устройства,

2, Устройство по п. 1, о т л и- чающееся тем, что дешифратор содержит первый и второй элементы И-НЕ, с первого по четвертый элементы НЕ, причем информационный вход дешифратора соединен с первым входом второго элемента И-НЕ и через первый элемент НЕ с первым входом первого элемента И-НЕ, вход разрешения дешифратора соединен с вторыми входами первого и второго элементов И-НЕ и через четвертый элемент НЕ с третьим выходом дешифратора, выходы первого и второго элементов И-НЕ соединены через второй и третий элементы НЕ с первым и вторым выходами дешифратора соответственно.

166175712

3. Устройство по п. отличающееся тем, что коммутатор содержит с первого по третий МДП- транзисторы n-типа, причем затворы с первого по третий МДП-транзисторов n-типа соединены соответственно с первым, вторым и третьим управляющими входами коммутатора, истоки с первого по третий МДП-транзисторов п-типа соединены соответственно с первым и вторым информационными входами коммутатора и с входом потенциала питания устройства, строки с первого по третий МДП-транзисторов n-типа соединены с выходом коммутатора.

10

15

20

25

4. Устройство по п. 1, отличающееся тем, что выходной буферный узел содержит элемент НЕ и МДП-транзистор р-типа, причем вход выходного буферного узла соединен с входом элемента НЕ и со стоком МДП-транзистора р-типа, выход элемента НЕ соединен с затвором МДП-транзистора р-типа и является выходом выходного буферного узла, исток МДП- транзистора р-типа соединен с входом потенциала питания устройства.

4. Устройство по п. 1, отличающееся тем, что выходной буферный узел содержит элемент НЕ и МДП-транзистор р-типа, причем вход выходного буферного узла соединен с входом элемента НЕ и со стоком МДП-транзистора р-типа, выход элемента НЕ соединен с затвором МДП-транзистора р-типа и является выходом выходного буферного узла, исток МДП- транзистора р-типа соединен с входом потенциала питания устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемая логическая матрица | 1989 |

|

SU1695387A1 |

| Программируемая логическая матрица | 1989 |

|

SU1695383A1 |

| Постоянное запоминающее устройство | 1987 |

|

SU1443030A1 |

| Универсальный цифровой преобразователь координат | 1980 |

|

SU924701A1 |

| Ассоциативный параллельный процессор | 1980 |

|

SU955078A1 |

| Буферное запоминающее устройство с произвольной выборкой двумерного фрагмента | 1986 |

|

SU1444784A1 |

| Устройство для умножения @ -разрядных чисел | 1986 |

|

SU1374217A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| УСТРОЙСТВО ДЛЯ СЕЛЕКЦИИ ЭЛЕМЕНТОВ КОНТУРНОГО ИЗОБРАЖЕНИЯ | 1991 |

|

RU2015560C1 |

Изобретение относится к вычислительной технике и может быть использовано при аппаратной реализации устройств нормализации (денормализации) мантисс числа в высокопроизводительных параллельных вычислительных системах с плавающей запятой. Устройство характеризуется повышенным быстродействием за счет совмещения во времени процесса смены информации на его информационных и/или управляющих входах и процесса подзаряда выходов коммутаторов каждой строки для ускоренной передачи высокого уровня сигнала, а также за счет ускоренной передачи низкого уровня сигнала посредством уменьшения логического перепада, повышенной надежностью за счет асинхронного отслеживания момента окончания переходных процессов в каждой фазе цикла и уменьшенными аппаратурными затратами за счет выполнения коммутаторов на МДП-транзисторах N-типа. Устройство содержит матрицу коммутаторов 1, группу дешифраторов 2, группу входных буферных узлов 3, группу выходных буферных узлов 4, группу коммутаторов 5, входной буферный узел 6, выходной буферный узел 7, группу конденсаторов 8 со связями. 3 з.п.ф-лы, 6 ил.

фиг. 2

19 го

2/-1Ј 1-4 .

-36

37

фиг.З

tHj-

| Патент США № 4383304, кл, G 06 F 7/00, опУблик | |||

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Устройство сдвига информации | 1976 |

|

SU602939A1 |

| , | |||

Авторы

Даты

1991-07-07—Публикация

1989-06-05—Подача