Изобретение относится к области преобразования кодов и может быть использовано в системах обработки информации многоканальных измерителей.

Известен шифратор позиционного кода, содержащий генератор тактовых импульсов, элемент И, счетчик импульсов, блок ввода информации, коммутаторы и мультиплексор [1].

Известен также шифратор, содержащий блок мультиплексирования, генератор тактовых импульсов, три регистра, формирователь импульсов, триггер, элементы ИЛИ, элемент И, элемент задержки и дешифратор. Шифратор осуществляет шифрацию положения разряда, имеющего единичное значение, во входном n-разрядном коде [2].

Недостатком известных шифраторов являются ограниченные функциональные возможности, в частности отсутствие возможности шифрации положения во входном n-разрядном коде группы разрядов, имеющих единичное значение. Необходимость выполнения этой функции возникает при обработке информации, поступающей от многоканальных измерителей, например, в многоканальных системах определения пеленга и частоты радиотехнических сигналов. Коды на выходе таких измерителей характеризуются наличием единиц в одном или нескольких разрядах из совокупности соседних разрядов, соответствующих возбужденным каналам измерителя параметра входного сигнала. Количество разрядов, в пределах которых находится эта совокупность единиц, зависит, в частности, от уровня входного сигнала измерителя и пороговых уровней в каждом из его каналов. Важнейшей информацией, характеризующей значение измеряемого параметра, является положение этой группы в n-разрядном коде, а именно положение центра этой группы. Отсюда следует, что обеспечение возможности шифрации положения во входном n-разрядном коде группы разрядов, имеющих единичное значение, является необходимой функцией устройства для шифрации кода, поступающего от многоканальных измерителей.

Техническая задача, решаемая изобретением, заключается в обеспечении возможности шифрации кода от многоканальных измерителей, в частности шифрации положения группы разрядов, имеющих единичное значение.

Для решения поставленной задачи в устройство, содержащее блок мультиплексирования, введены М шифраторов, блок формирования адреса мультиплексирования и блок преобразования кода, причем каждый из М шифраторов выполнен в виде постоянного запоминающего устройства (ПЗУ), у которого выходы являются выходами шифратора, а адресные входы - входами шифратора. При этом входы i-го шифратора (i = 0,1...M-1) соединены с i-й группой входов устройства, первая группа выходов i-го шифратора соединена с i-й группой информационных входов блока мультиплексирования, адресные входы которого соединены с первой группой входов блока преобразования кода и с выходами блока формирования адреса мультиплексирования, i-я группа входов которого соединена с второй группой выходов i-го шифратора, причем выходы блока мультиплексирования подключены к второй группе входов блока преобразования кода, выходы которого являются выходами устройства.

В одном из частных случаев выполнения устройства i-я и (i+1)-я группы входов устройства перекрываются между собой, а блок мультиплексирования выполнен в виде мультиплексора, у которого i-я группа информационных входов является i-й группой информационных входов блока мультиплексирования, выходы мультиплексора являются выходами блока мультиплексирования, а адресные входы мультиплексора являются адресными входами блока мультиплексирования. При этом ПЗУ, на котором выполнен i-й шифратор, запрограммировано таким образом, что на первой группе выходов i-го шифратора формируется код положения центра группы логических "1" во входном коде i-го шифратора относительно младшего разряда этого кода, а на второй группе выходов i-го шифратора, содержащей один выход, формируется сигнал di, значение которого равно логической "1", если на тех входах i-го шифратора, которые не являются входами (i+1)-го шифратора, имеется хотя бы одна логическая "1", и логическому "0" в противном случае. Блок формирования адреса мультиплексирования выполнен в виде ПЗУ, у которого адресные входы являются входами блока формирования адреса мультиплексирования, а выходы - выходами блока формирования адреса мультиплексирования, при этом ПЗУ, на котором выполнен блок формирования адреса мультиплексирования, запрограммировано таким образом, что на его выходах формируется код номера младшего из тех сигналов di, значения которых равны логической "1".

Блок преобразования кода выполнен в виде ПЗУ, у которого адресные входы являются входами блока преобразования кода, а выходы - выходами блока преобразования кода, при этом ПЗУ, на котором выполнен блок преобразования кода, запрограммировано таким образом, что на его выходах формируется код, значение которого

R = rN + 2kN, где rN - значение кода на выходах блока мультиплексирования;

k - количество входов i-го шифратора, не являющихся входами (i+1)-го шифратора;

N - значение кода на выходах блока формирования адреса мультиплексирования.

В другом частном случае выполнения устройства группы его входов не перекрываются между собой, блок мультиплексирования состоит из двух мультиплексоров, а выходы блока мультиплексирования состоят из двух групп выходов, причем i-я группа информационных входов первого мультиплексора (i = 0,1, . ..,M-1) соединена с i-й группой информационных входов блока мультиплексирования, а выходы первого мультиплексора являются первой группой выходов блока мультиплексирования, j-я группа информационных входов второго мультиплексора (j = 0,1,...,M-2) соединена с (j+1)-й группой информационных входов блока мультиплексирования, а выходы второго мультиплексора являются второй группой выходов блока мультиплексирования, при этом адресные входы первого и второго мультиплексоров соединены между собой и с адресными входами блока мультиплексирования. При этом ПЗУ, на котором выполнен i-й шифратор, запрограммировано таким образом, что на первой группе выходов i-го шифратора формируется код положения центра группы логических "1" во входном коде i-го шифратора относительно младшего разряда этого кода, а на второй группе выходов i-го шифратора, содержащей один выход, формируется сигнал di, значение которого равно логической "1", если на входах i-го шифратора имеется хотя бы одна логическая "1", и логическому "0" в противном случае. Блок формирования адреса мультиплексирования выполнен в виде ПЗУ, у которого адресные входы являются входами блока формирования адреса мультиплексирования, а выходы - выходами блока формирования адреса мультиплексирования, при этом ПЗУ, на котором выполнен блок формирования адреса мультиплексирования, запрограммировано таким образом, что на его выходах формируется код номера младшего из тех сигналов di, значения которых равны логической "1".

При этом блок преобразования кода выполнен в виде ПЗУ, у которого адресные входы являются входами блока преобразования кода, а выходы - выходами блока преобразования кода. ПЗУ, на котором выполнен блок преобразования кода, запрограммировано таким образом, что на его выходах формируется код, значение которого

R = rN + rN+1 + 2mN, где rN - значение кода на первой группе выходов блока мультиплексирования;

rN+1 - значение кода на второй группе выходов блока мультиплексирования;

m - количество входов шифратора.

Неизвестно устройство для обработки многоразрядного кода, в котором содержалась бы вся совокупность существенных признаков изобретения. Это подтверждает, что оно является новым.

Неизвестны устройства для обработки многоразрядного кода, в которых бы дополнительно использовались M шифраторов, блок формирования адреса мультиплексирования и блок преобразования кода, при этом входы i-го шифратора (i = 0,1,...М-1) были бы соединены с i-й группой входов устройства, а первая группа выходов i-го шифратора соединена с i-й группой информационных входов блока мультиплексирования, адресные входы которого соединены с первой группой входов блока преобразования кода и с выходами блока формирования адреса мультиплексирования, i-я группа входов которого соединена с второй группой выходов i-го шифратора, причем выходы блока мультиплексирования подключены к второй группе входов блока преобразования кода, выходы которого являются выходами устройства. Это подтверждает, что изобретение не вытекает явным образом из уровня техники.

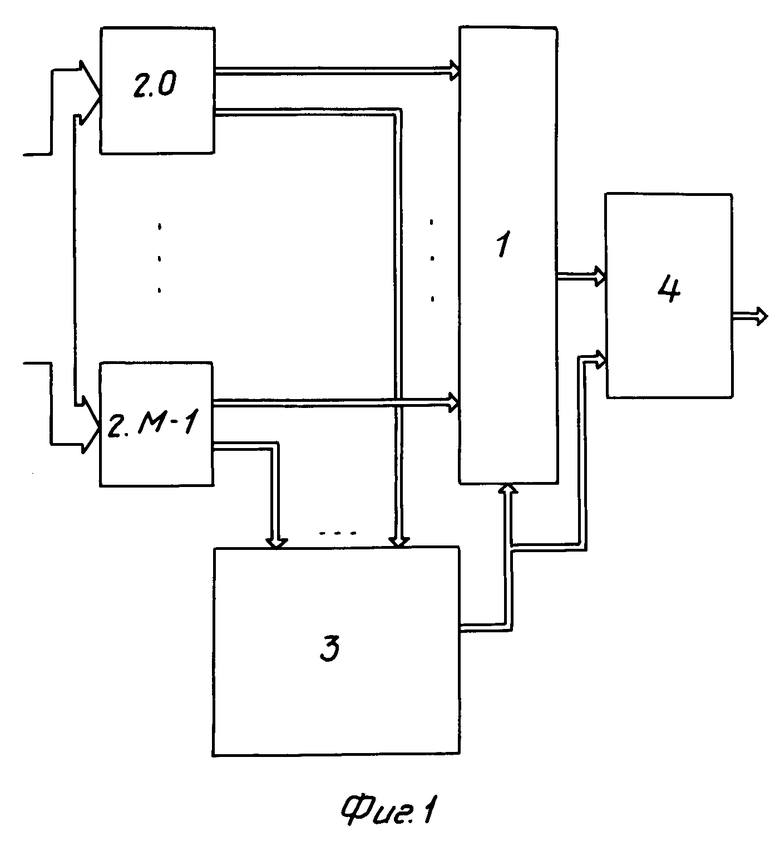

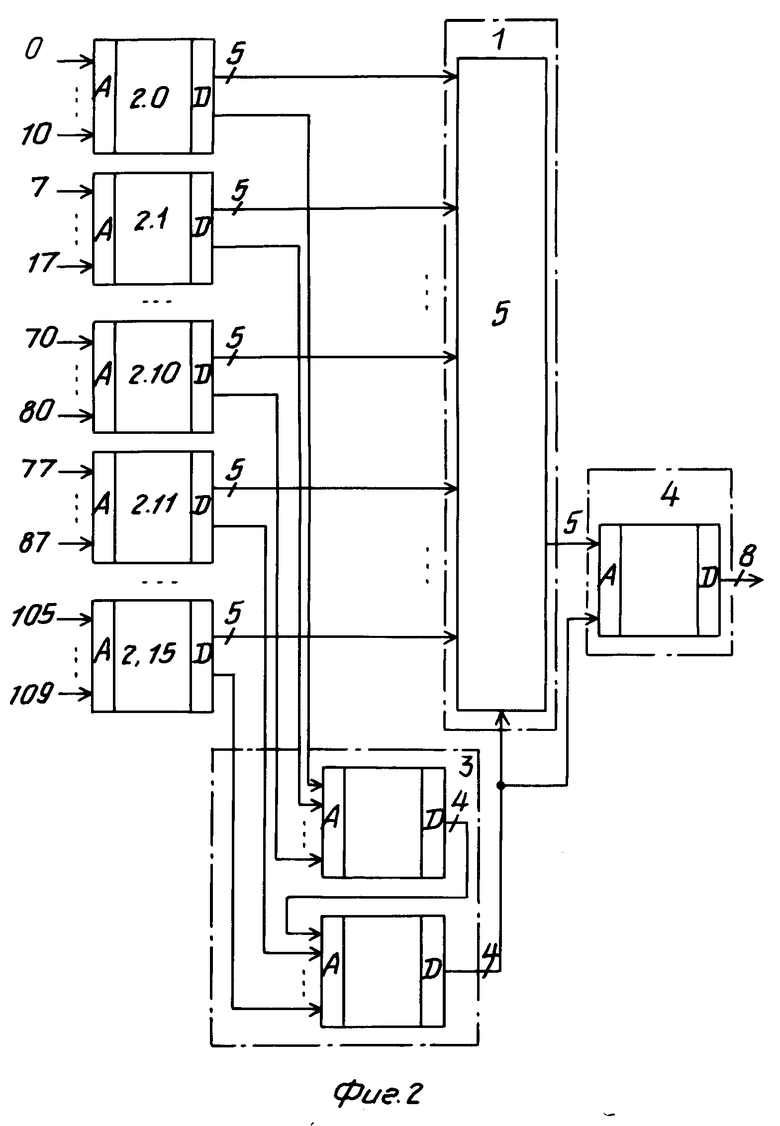

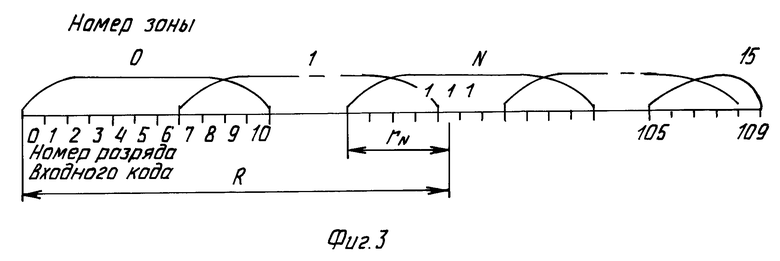

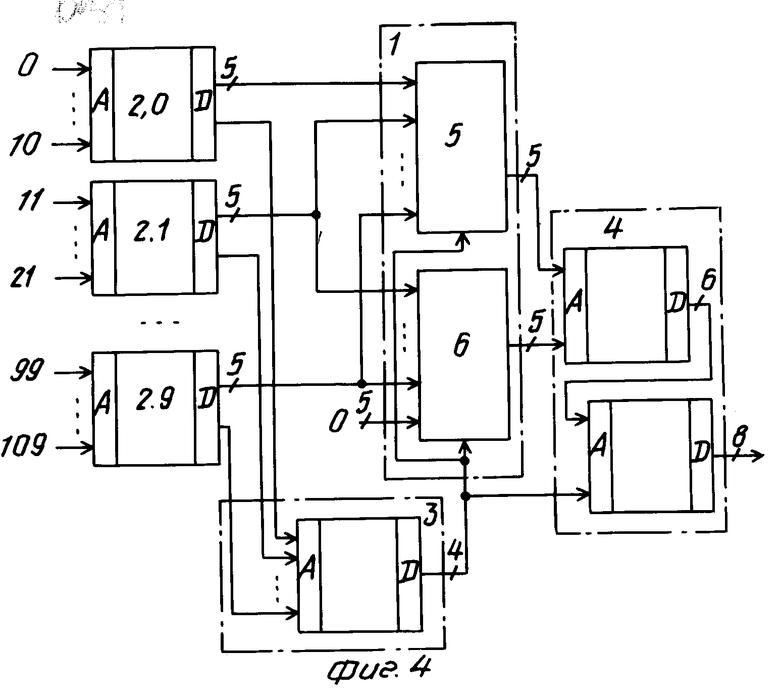

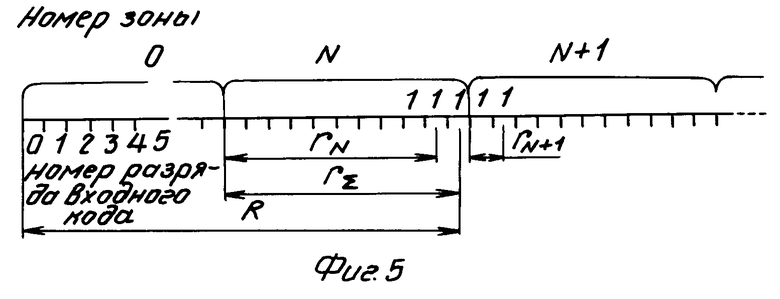

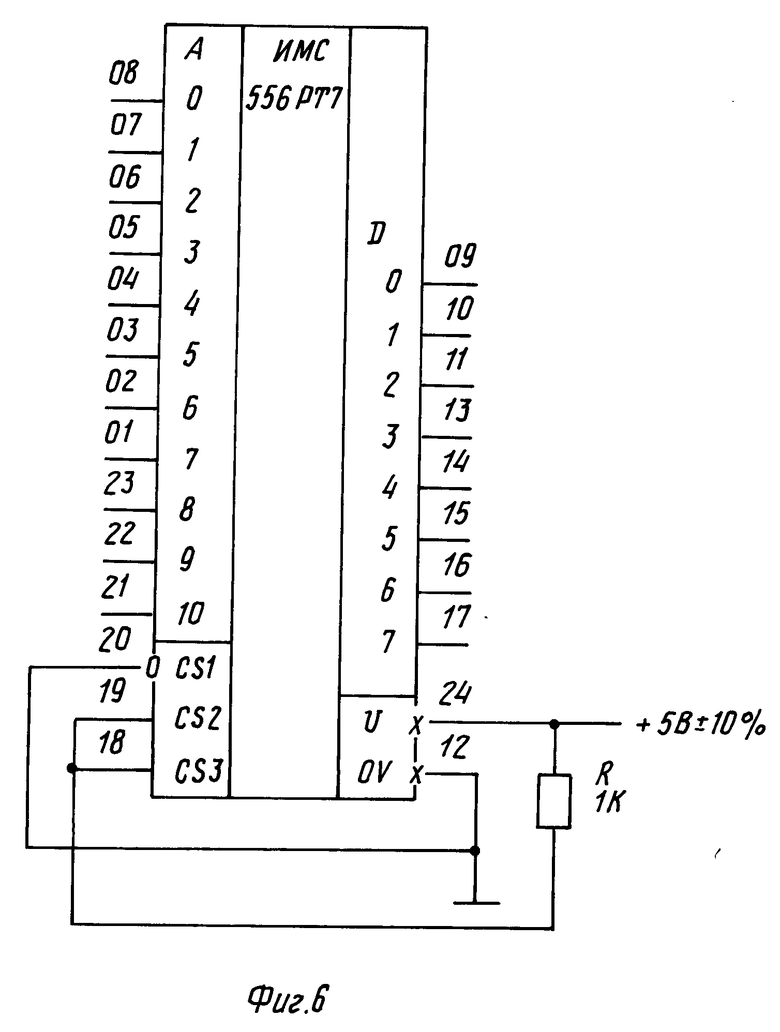

На фиг.1 приведена общая схема устройства; на фиг.2 и 3 показаны схема устройства и расположение зон разрядов входного кода для первого частного случая выполнения устройства; на фиг.4 и 5 - схема устройства и расположение зон разрядов входного кода для второго частного случая выполнения устройства; на фиг. 6 показана схема подключения управляющих входов и выводов питания интегральной микросхемы (ИМС) 556РТ7.

Устройство содержит блок 1 мультиплексирования, М шифраторов 2.0,...,2. (М-1), каждый из которых представляет собой ПЗУ, блок 3 формирования адреса мультиплексирования и блок 4 преобразования кода.

Все входы устройства разделены на М групп, перекрывающихся или неперекрывающихся между собой в различных частных случаях выполнения устройства, и i-я группа входов устройства является входами шифратора 2.i. Первая группа выходов шифратора 2.i соединена с i-й группой информационных входов блока 1 мультиплексирования, адресные входы которого соединены с первой группой входов блока 4 преобразования кода и с выходами блока 3 формирования адреса мультиплексирования, i-я группа входов которого соединена с второй группой выходов шифратора 2. i. Выходы блока 1 мультиплексирования подключены к второй группе входов блока 4 преобразования кода, выходы которого являются выходами устройства.

Устройство работает следующим образом.

При поступлении n-разрядного кода на входы устройства каждый из М шифраторов 2.0,...2.М-1 в соответствии с расположением единиц на тех входах устройства, которые соединены с входами шифратора, выдает на вторую группу своих выходов информацию о единицах на его входах. В соответствии с этой информацией, поступившей от всех шифраторов 2.0,...2.М-1 на входы блока 3 формирования адреса мультиплексирования, последний формирует на своих выходах адрес мультиплексирования, поступающий на адресные входы блока 1 мультиплексирования и соответствующий подключению на выход блока мультиплексирования тех групп (или группы) входов блока мультиплексирования, которые соединены с первыми группами выходов тех из шифраторов 2.0,...2.М-1 (шифратора), на входах которых располагается шифруемая группа единиц.

Таким образом, через блок 1 мультиплексирования на вторую группу входов блока 4 преобразования кода передается информация о группе единиц в пределах совокупности входов выбранных шифраторов, в частности о расположении группы в этих пределах. В блоке 4 эта информация преобразуется в информацию о группе единиц в пределах всего n-разрядного кода, например о расположении группы единиц в пределах n разрядов входного кода, с учетом информации о том, какие именно из шифраторов выбраны, поступающей с выходов блока 3 формирования адреса мультиплексирования на первую группу входов блока 4 преобразования кода.

В предлагаемом устройстве учтена характерная особенность кодов многоканальных измерителей, заключающаяся в том, что размер шифруемой группы ограничен заранее известным количеством разрядов. Конкретное количество разрядов определяется характеристиками самого измерителя и динамическим диапазоном его входного сигнала и обычно не превышает пяти разрядов. С учетом этого в устройстве производится передача через блок 1 мультиплексирования информации тех шифраторов, в совокупность входов которых полностью входит шифруемая группа единиц.

Ниже приведены частные случаи выполнения устройства, в одном из которых через блок 1 мультиплексирования передается информация от одного шифратора, а в другом - информация от двух шифраторов. Затем в блоке 4 преобразования кода производится "перенос" из пределов совокупности входов выбранных шифраторов в пределы всего n-разрядного входного кода устройства и, таким образом, формируется требуемая информация о шифруемой группе единиц, например информация о положении центра этой группы в n разрядах входного кода.

Таким образом, предлагаемое построение устройства для обработки многоканального кода обеспечивает возможность шифрации кодов от многоканальных измерителей, характеризующихся наличием ограниченной совокупности разрядов, содержащей единицы, в частности обеспечивает возможность шифрации положения этой совокупности во входном коде.

В первом частном случае выполнения устройства, обеспечивающего шифрацию положения группы единиц, занимающей не более пяти разрядов 110-разрядного входного кода, (фиг.2 и 3). Оно содержит блок 1 мультиплексирования, выполненный в виде мультиплексора 5 с 16-ю пятиразрядными группами информационных входов, 16 11-входовых шифраторов 2.0,...,2.15, каждый из которых выполнен в виде ПЗУ, блок 3 формирования адреса мультиплексирования и блок 4 преобразования кода, также выполненные в виде ПЗУ. Каждый шифратор может быть реализован на ИМС ПЗУ, имеющей не менее 11-адресных входов и не менее шести выходов, например на ИМС 556РТ7. Мультиплексор 5 может быть реализован на стандартных ИМС мультиплексоров, например, серии 533. Блок 4 преобразования кода реализован на одной ИМС 556РТ7, а блок 3 формирования адреса мультиплексирования - на двух таких же ИМС, как показано на фиг.2.

Вся совокупность разрядов входного кода разбита на 16 зон по 11 разрядов, при этом соседние зоны перекрываются на четыре разряда, как показано на фиг. 3. При таком перекрытии любая группа единиц, занимающая не более пяти разрядов, входит целиком хотя бы в одну из зон. Разряды i-й зоны входного кода являются входами шифратора 2.i.

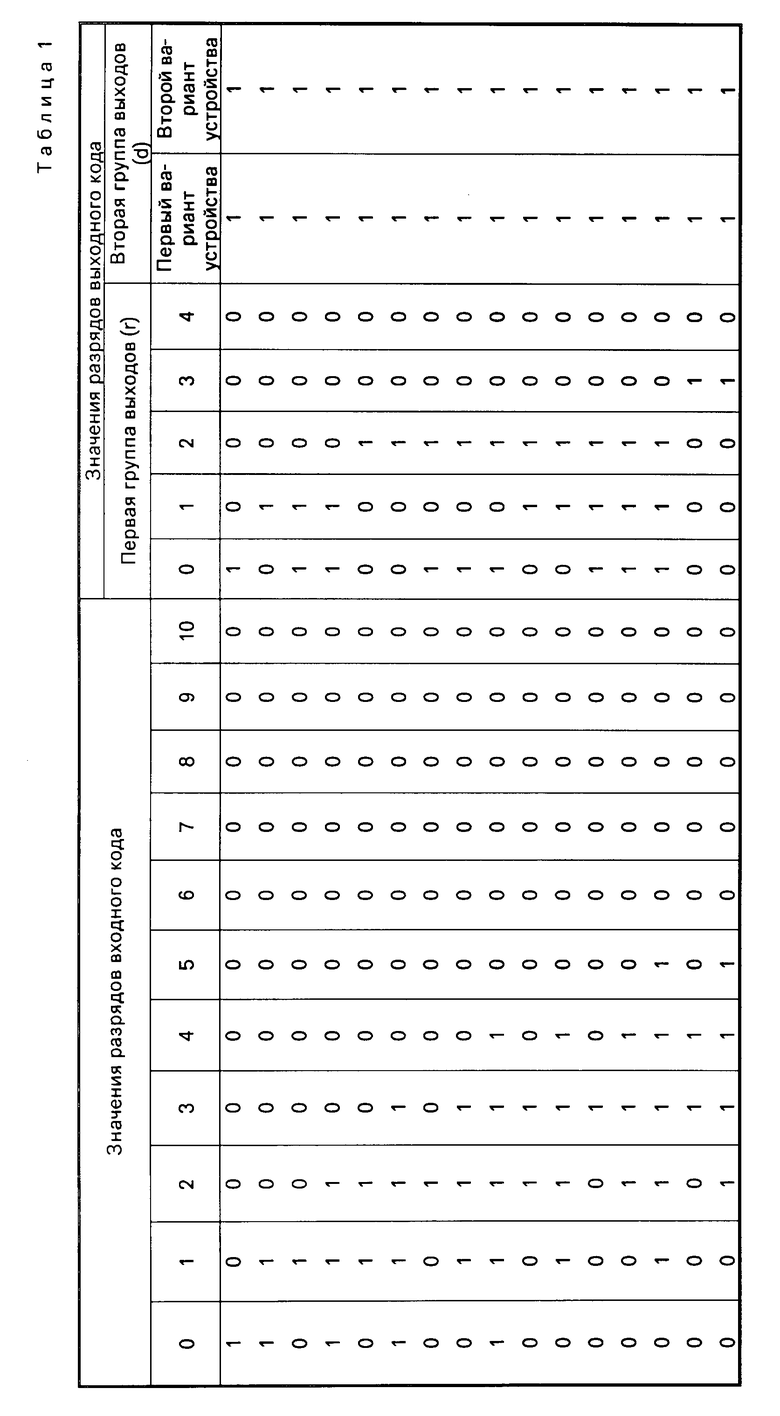

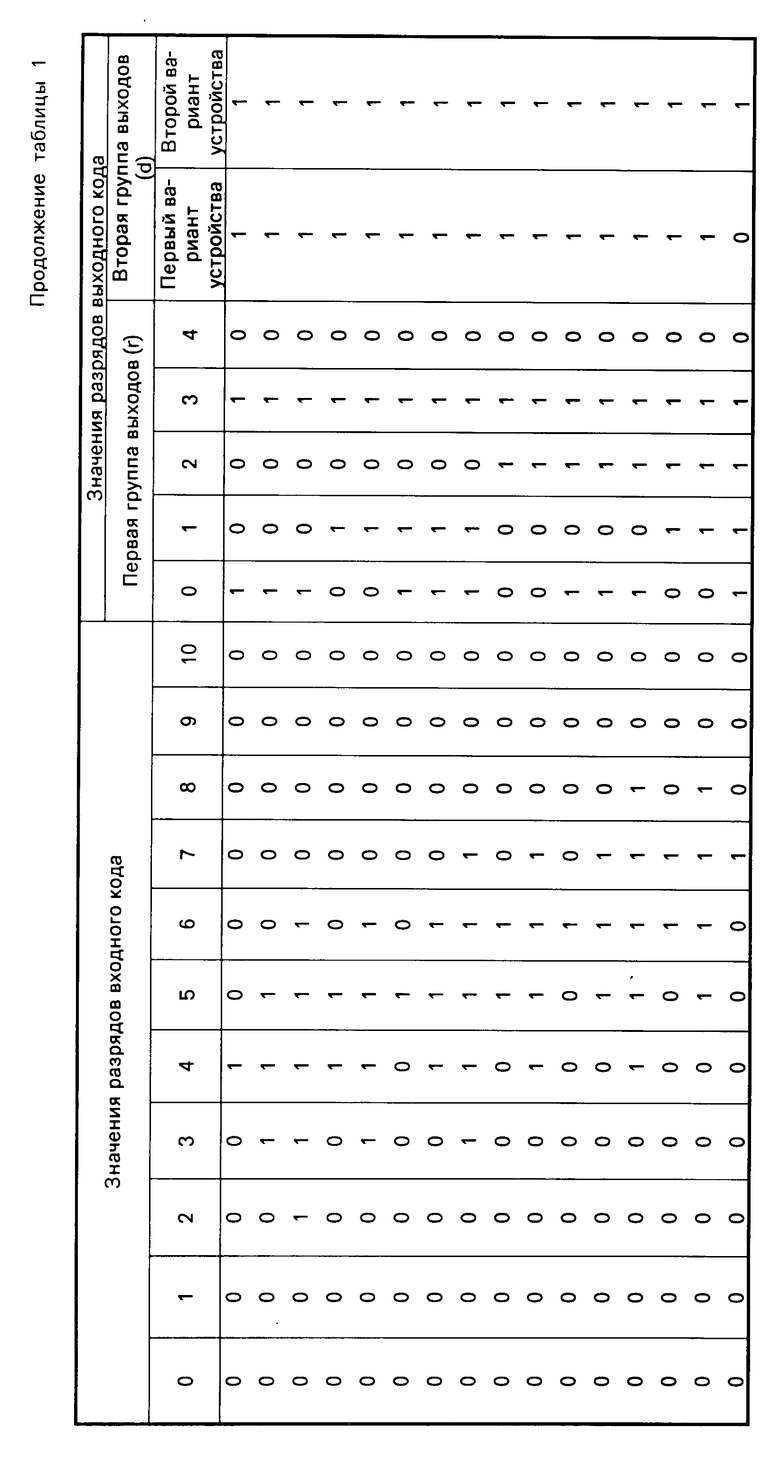

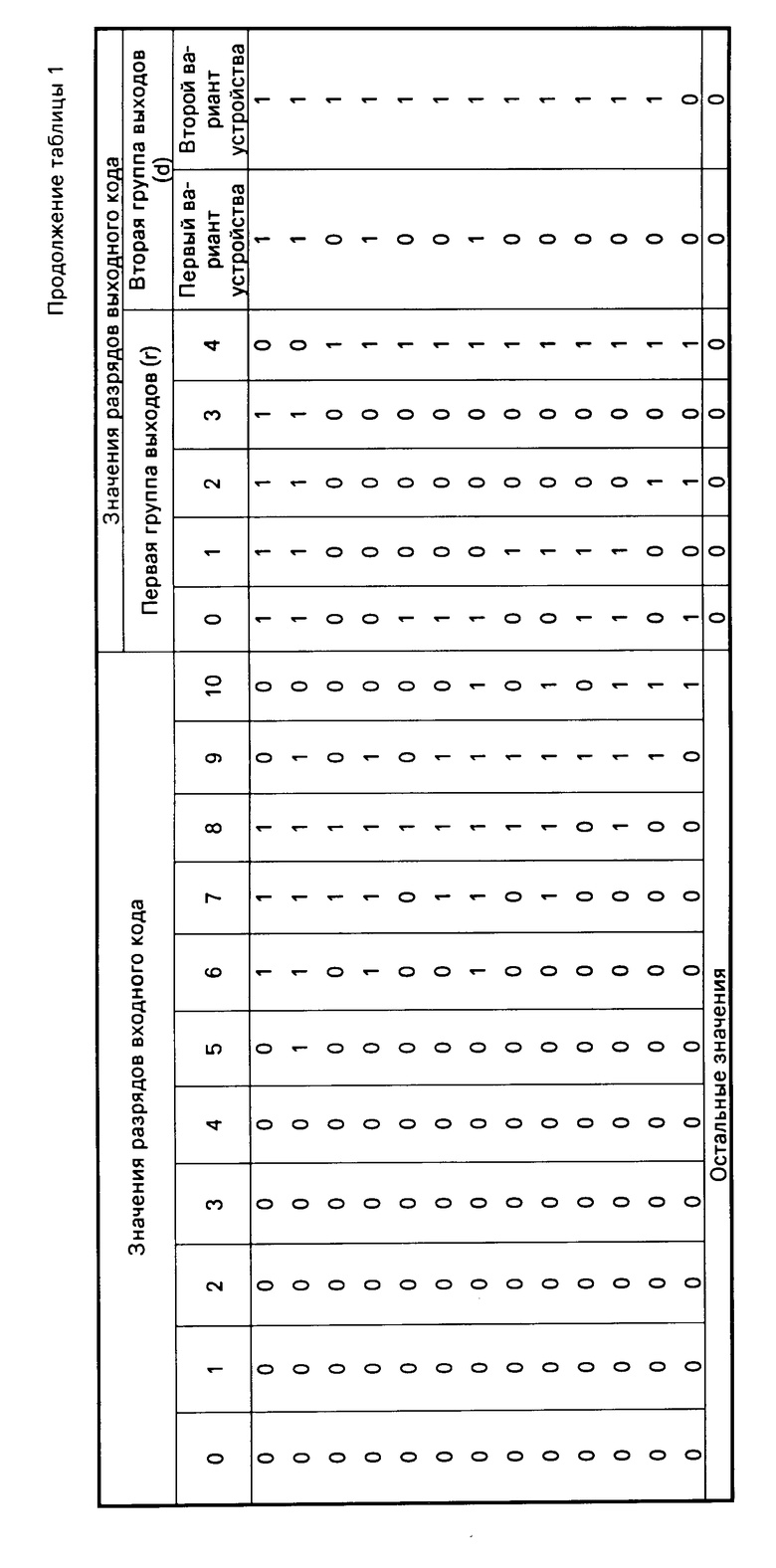

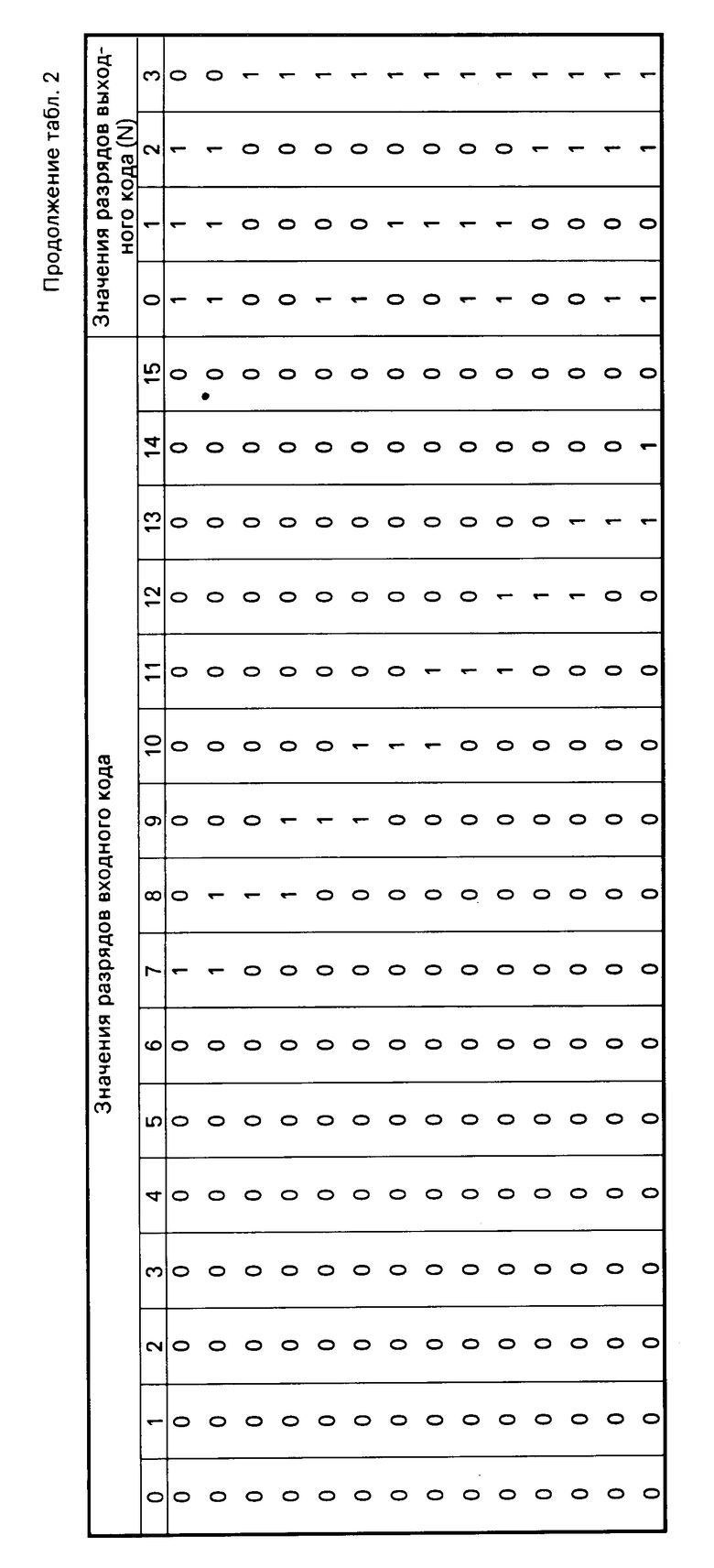

На первой группе выходов шифратора 2.i, соединенной с i-й группой информационных входов мультиплексора 5, формируется пятиразрядный код положения центра группы единиц в пределах 11-ти разрядов входного кода шифратора 2. i относительно младшего разряда этого кода. На второй группе выходов шифратора 2.i формируется одноразрядный признак di наличия на семи младших входных разрядах этого шифратора хотя бы одной единицы. В табл.1 показано соответствие значений входного и выходного кодов шифратора.

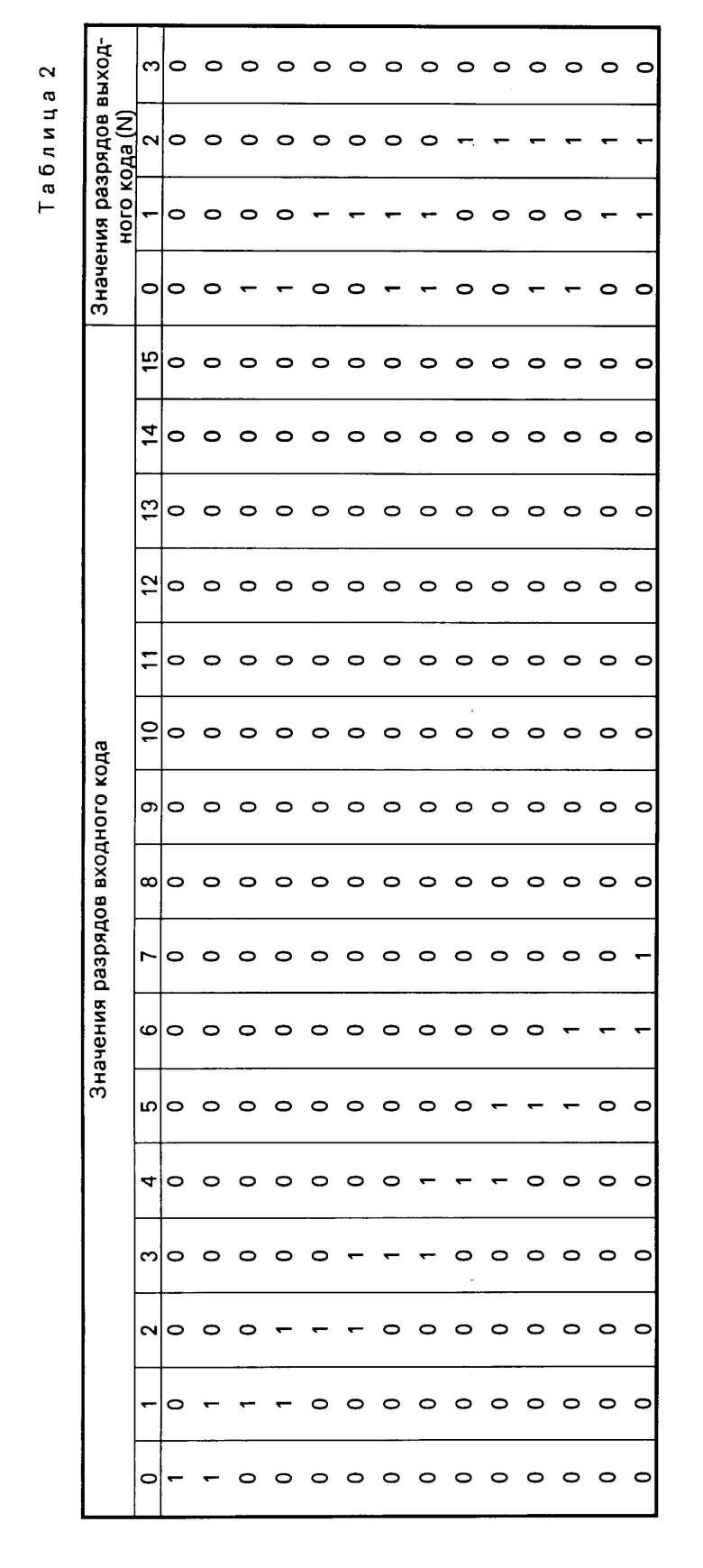

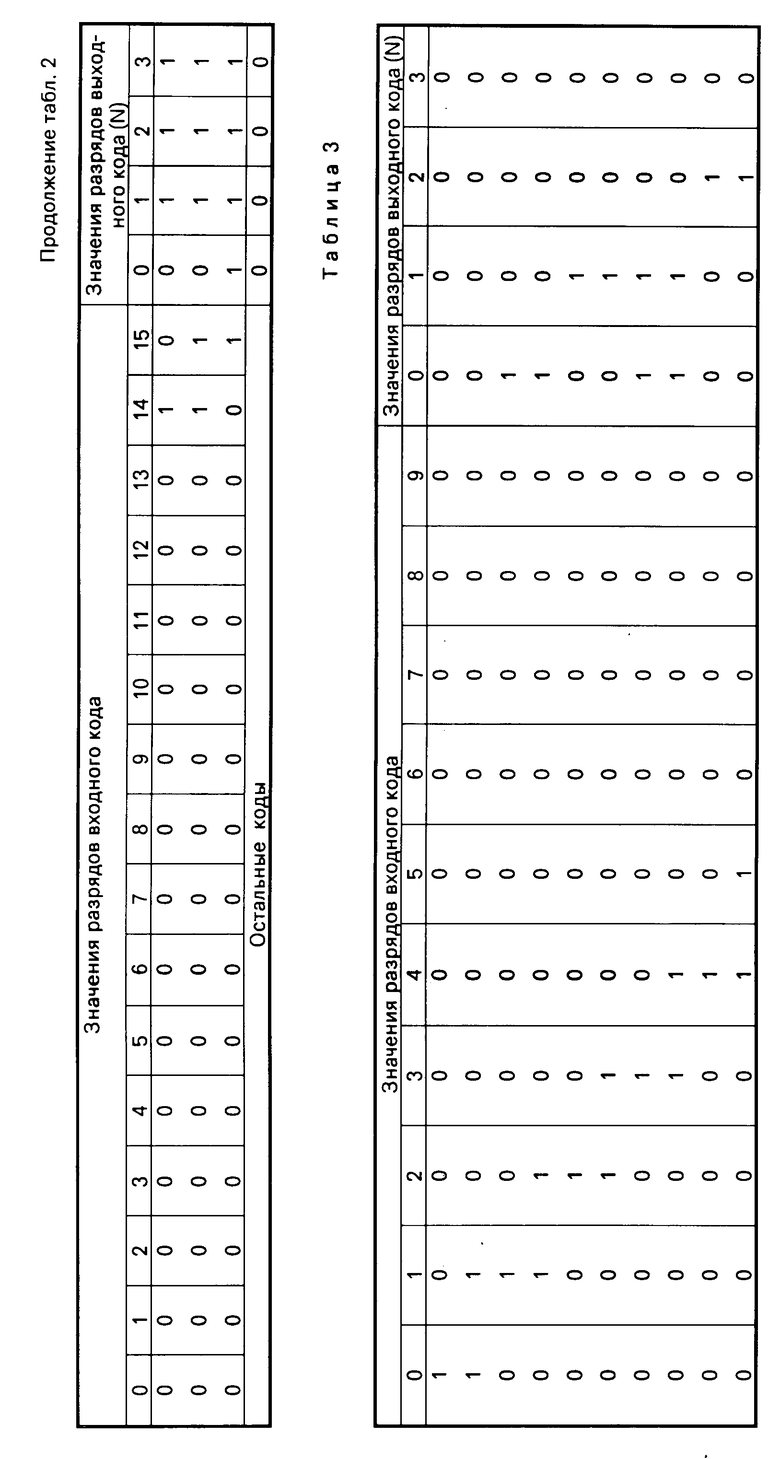

Вся совокупность признаков di (i = 0,1,...,15) поступает на входы блока 3 формирования адреса мультиплексирования, на выходах которого формируется четырехразрядный код N номера младшего из признаков di, равных единице. В табл.2 показано соответствие значений входного и выходного кодов блока формирования адреса мультиплексирования.

Код N поступает на адресные входы мультиплексора 5 и первую группу входов блока 4 преобразования кода. Под управлением кода N мультиплексор 5 коммутирует на свои выходы и соответственно на вторую группу входов блока 4 код rN от N-го шифратора, на входах которого целиком располагается шифруемая группа единиц. На выходах блока 4, представляющего собой ПЗУ, в соответствии со значениями поступивших на адресные входы ПЗУ кодов rN и N, табличным способом формируется код, значение которого

R = rN + 14N.

Код R определяет положение центра группы единиц во входном коде устройства, а именно удаление центра относительно младшего разряда этого кода (фиг.3).

Во втором частном случае выполнения, показанном на фиг.4 и 5, устройство содержит блок мультиплексирования, состоящий из мультиплексоров 5 и 6 с десятью пятиразрядными группами информационных входов, десять 11-входовых шифраторов 2.0, ...2.9, каждый из которых выполнен в виде ПЗУ, блок 3 формирования адреса мультиплексирования и блок 4 преобразования кода, также выполненные в виде ПЗУ.

Каждый шифратор может быть реализован на ИМС 556РТ7, мультиплексоры 5 и 6 - на стандартных ИМС мультиплексоров, блок 3 - на одной ИМС 556РТ7, а блок 4 - на двух таких же ИМС, как показано на фиг.4.

Вся совокупность разрядов входного кода устройства разбита на десять неперекрывающихся зон по 11 разрядов (фиг.5). Шифруемая группа единиц может быть расположена или целиком в одной зоне, или в двух соседних зонах. Разряды i-й зоны (i = 0,1,...,9) являются входами шифратора 2.i.

На первой группе выходов шифратора 2.i формируется пятиразрядный код положения центра группы единиц в пределах 11-ти разрядов входного кода этого шифратора относительно младшего разряда этого кода. В отсутствие единиц на входах шифратора 2.i код имеет нулевое значение. Вторая группа выходов шифратора 2.i представляет собой один выход, на котором формируется признак di наличия на входах этого шифратора хотя бы одной единицы. В табл.1 показано соответствия значений входного и выходного кодов шифратора.

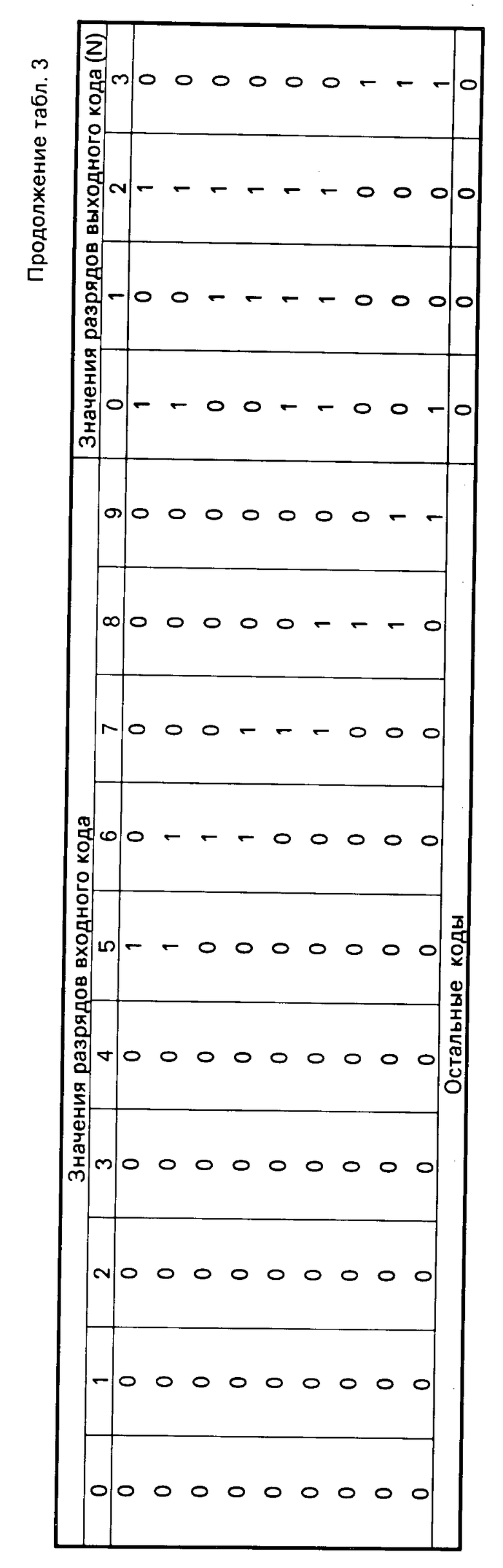

Совокупность признаков di поступает на входы блока 3 формирования адреса мультиплексирования, на выходах которого формируется четырехразрядный код N номера младшего из признаков di, равных единице. В табл.3 показано соответствия значений входного и выходного кодов блока формирования адреса мультиплексирования. Код N поступает на адресные входы мультиплексоров 5 и 6 и первую группу входов блока 4 преобразования кода. На i-ю группу информационных входов мультиплексора 5 передается код с выходов шифратора 2. i. На j-ю группу информационных входов мультиплексора 6 (j = 0,1,...,8) передается код rj+1 с выходов шифратора 2.(j+1). Если входной код устройства для шифрации не замкнут в кольцо, т.е. самый старший и самый младший разряды кода не являются соседними, то на последнюю группу информационных входов мультиплексора 6 подается, как показано на фиг.4, нулевой код, в противном случае подается код r1. Таким образом, мультиплексоры 5 и 6 коммутируют на свои выходы и соответственно на вторую группу входов блока 4 код {rN,rN+1}.

Блок 4 состоит из двух ИМС ПЗУ, как показано на фиг.4. Коды rN и rN+1 поступают на входы первой ИМС ПЗУ, на выходах которой формируется код rΣ положения центра шифруемой группы единиц в пределах 22-х разрядов входного кода шифраторов 2.N и 2.N+1 относительно младшего разряда входного кода шифратора 2.N (фиг.5), при этом значение кода

rΣ = rN + rN+1.

Код rΣ и код N поступают на входы второй ПЗУ, и на ее выходах формируется код, значение которого

R = rΣ + 22N.

Таким образом, на выходах устройства для обработки многоразрядного кода формируется код, определяющий положение центра шифруемой группы единиц во входном коде устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1536384A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для сопряжения каналов ввода-вывода с оперативной памятью | 1986 |

|

SU1322298A2 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1986 |

|

SU1425698A2 |

| Устройство для взаимного установления подлинности абонентов | 1986 |

|

SU1442993A1 |

| Устройство управления процессора двухмерного преобразования Фурье | 1982 |

|

SU1121677A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108449A1 |

| Устройство для сопряжения каналов ввода-вывода с оперативной памятью | 1985 |

|

SU1267427A1 |

| Устройство для вычисления степенной функции | 1989 |

|

SU1711153A1 |

| Устройство для вывода информации на телеграфный аппарат | 1985 |

|

SU1293735A1 |

С целью обеспечения возможности шифрации группы разрядов, имеющих еденичное значение, предлагаемое устройство содержит блок мультиплексирования, M шифраторов, блок формирования адреса мультиплексирования и преобразования кода. Входы i-го шифратора ( i = 0,1,...,M-1 ) соединены с i-й группой входов устройства, выходы шифраторов соединены с входами блока мультиплексирования и блока формирования адреса мультиплексирования, выходы последнего - с входами блока мультиплексирования и блока преобразования кода, а выходы блока мультиплексирования - с входами блока преобразования кода, причем выходы блока преобразования кода являются выходами устройства. 2 з.п.ф-лы, 3 табл., 6 ил.

R = rN + 2KN,

где rN - значение кода на выходах блока мультиплексирования;

K - количество входов i-го шифратора, не являющихся входами (i + 1)-го шифратора;

N - значение кода на выходах блока формирования адреса мультиплексирования.

R = rN + rN+1 + 2mN,

где rN - значение кода на первой группе выходов блока мультиплексирования;

rN+1 - значение кода на второй группе выходов блока мультиплексирования;

m - количество входов шифратора;

N - значение кода на выходах блока формирования адреса мультиплексирования.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Шифратор | 1987 |

|

SU1439748A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

Авторы

Даты

1995-02-20—Публикация

1992-01-27—Подача