Изобретение относится к измерительной и вычислительной технике и может быть использовано для измерения функции взаимной корреляции между двумя случайными процессами, задержанными один относительно другого.

Цель изобретения - расширение частотного диапазона обрабатываемых сигналов.

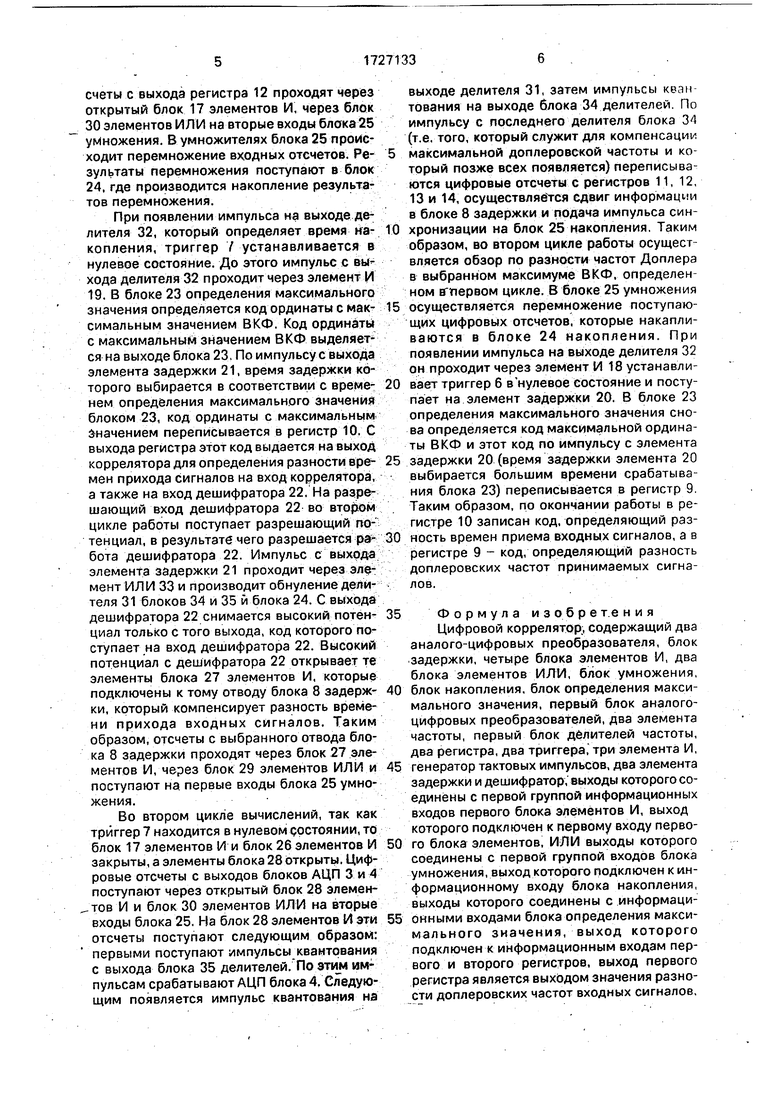

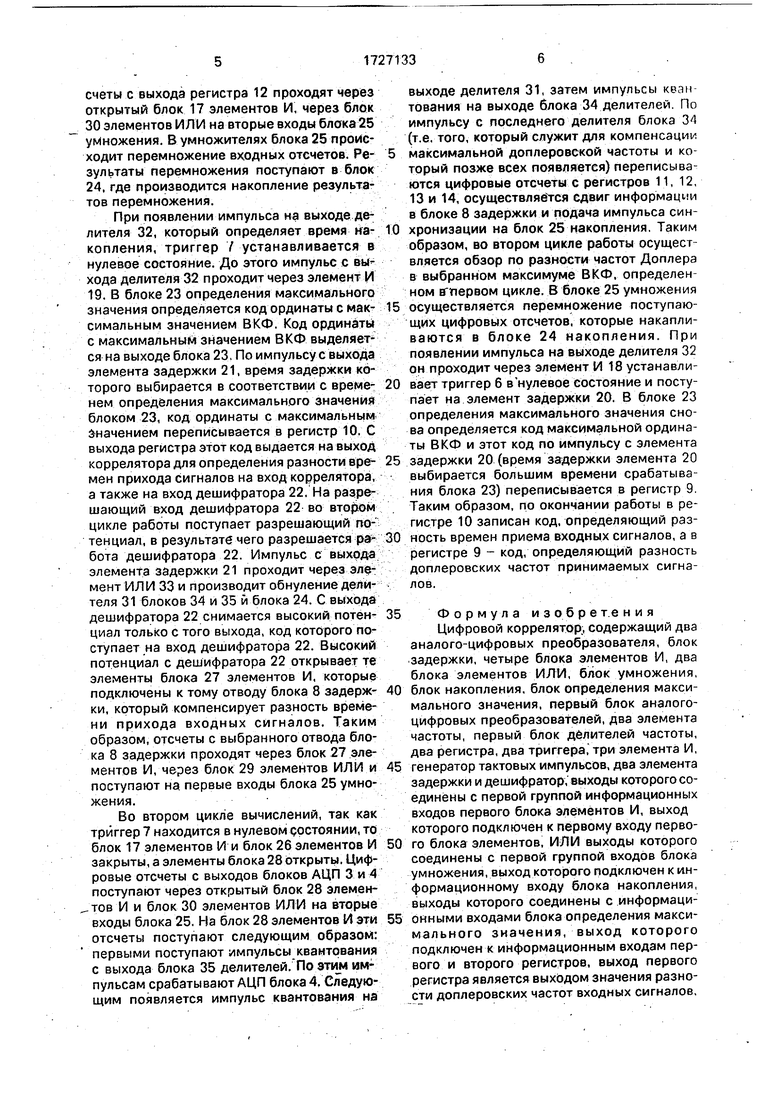

На чертеже показана схема цифрового коррелятора. Цифровой коррелятор содержит первый 1 и второй 2 аналого-цифровые преобразователи, первый и второй блоки 3 и 4 аналого-цифровых преобразователей, генератор 5 тактовых импульсов, первый 6 и второй 7 триггеры, блок 8 задержки, регистры 9-14, вход запуска 15, элемент И 16, блок 17 элементов И, элементы И 18, 19, элементы задержки 20, 21, дешифратор 22, блок 23 определения максимального значения, блок

24 накопления, блок 25 умножения, блоки 26-28 элементов И, блоки 29,30 элементов ИЛИ, делители частоты 31 , 32,, элемент ИЛИ 33, блоки 34, 35 делителей частоты,

Вход запуска коррелятора 15 соединен с S-входами первого 6 и второго 7 триггеров, с входом обнуления делителя 32 и с входом элемента ИЛИ, выход которого соединен с входами обнуления делителя 31 и блоков 34, 35 делителей частоты, блока 24 накопления, входы которого соединены с выходами блока 25 умножения, а выходы - с входами блока 23 определения максимального значения, выходы которого соединены с входами регистров 9, 10, синхровход последнего соединен с первым входом элемента ИЛИ 33 и с выходом элемента задержки 21, а выходы - с первыми выходами коррелятора и с входами дешифратора 22, синхровход которого соединен с вторым входом элемен%sго

XI

ы ы

а И 18, с вторыми входами блока 28 элеменов И, с инверсным входом второго триггера , а выходы - с вторыми входами блока 27 лементов И, первые входы которого соединены с выходами блока 8 задержки и с вхо- 5 ами блока 26 элементов И, выходы которого соединены с первыми входами блока 29 элементов ИЛИ, вторые входы коорого соединены с выходами блока 27 элементов И, а выходы - с первыми входами 10 блока 25 умножения, вторые входы которого соединены с выходами блока 30 элементов ИЛИ, вторые входы которого соединены с выходами блока 28 элементов И, а первые входы - с выходом блока 17 элементов И, 15 второй вход которого соединен с выходом регистра 12, а первый вход-с.вторым входом первого блока .26 элементов И, с прямым выходом второго триггера 7 и с вторым входом элемента И, 19, выход которого сое- 20 динен с входом элемента задержки 21, а первый вход - с R-входом второго триггера 7, а первым входом элемента И 18 и с выходом делителя 32, вход которого соединен со счетными входами делителя 31 и блоков 34 25 и 35 делителей и с выходом элемента И 16, первый вход которого соединен с выходом генератора тактовых имлульсов 5, а второй вход-с прямым выходом первого триггера 6, R-вход которого соединен с выходом эле- 30 мента И 18 и с входом элемента задержки 20, выход которого соединен с синхррвхо- дом регистра 9, выходы которого соединены с вторыми выходами коррелятора, первый вход которого соединен с входом аналоге- 35 цифрового преобразователя (АЦП) 1, синх- ровход которого соединен с синхровходом АЦП 2 и с выходом регистра 3Т, а выход - с входом регистра 11, выход которого соединен с информационным входом блока 8 за- 40 держки, синхровход которого соединен с синхровходом регистра 11, с синхровходом блока 24 накопления, с синхровходом регистра 12, с последним выходом блока делителя 34, с синхровходом регистров 13 и 14, 45 вход последнего соединен с выходом блока 4 АЦП, а выходы - с второй группой первых входов блока 28 элементов И 28, первая группа которых соединена с выходами регистра 13, входы которого соединены с выхо- 50 дамй блока 3 АЦП, вход которого .соединен с вторым входом коррелятора, с входом АЦП 2 и с входом блока 4 АЦП, синхровходы которого соединены с выходами блока 35 делителей, а выходы блока 34 делителей 55 соединены о синхровходами блока 3 АЦП, а выход АЦП 2 соединен с входом регистра

,12.. ; ., ; . .: . : / Цифровой коррелятор работает следующим образом.

В исходном состоянии триггеры б и 7 находятся в нулевом состоянии.

При поступлении на вход 15 импульса запуска производится установление триггеров 6 и 7 в единичное состояние, обнуление делителя 32, а также проходит через элемент ИЛИ 33 и производит обнуление делителя 31 .блоков34и35делителей и блока24 накопления. Установление триггера 6 в единичное состояние открывает элемент И 16, в результате чего импульсы с выхода генератора тактовых импульсов 5 проходят че: рез элемент И 16 и поступают на счетные входы делителей 31 и 32 и блоков 34 и 35 делителей. Установление триггера 7 в единичное состояние открывает элементы И 19. блок элементов И 17 и блок 26 элементов И.

Начинается первый цикл вычислений. В первом цикле вычислений используются коды АЦП 1 и 2 и работа коррелятора по вычислению взаимной корреляционной функции (ВКФ) осуществляется следующим образом. На выходе делителя 31 вырабатываются импульсы квантования, период следования которых выбирается в соответствии с теоремой Котельникова. Эти импульсы поступают на синхровходы АЦП 1 и 2, в которых аналоговые сигналы, поступающие на вход коррелятора, преобразуются в цифровой код. На выходе блоков 34 и 35 делителей вырабатываются импульсы квантования, размноженные по сетке частот дискретизации, т.е. отличающиеся на время возможного сдвига ВКФ вызванного частотой Доплера. При этом импульсы с выхода блока 34 делителей рассчитаны на компенсацию положительного сдвига разности частот Доплера, а с выхода блока 35 делителей на компенсацию отрицательного сдвига разности частот Доплера. Таким образом, импульсы квантования с выходов блока 34 поступают после квантования с делителя 31, ас блока 35 - до импульса квантования с делителя 31. Таким образом, по импульсам квантования с выхода делителя 31 аналоговые сигналы в АЦП 1 и 2 преобразуются в цифровые коды и по импульсу квантования с последнего выхода блока 34 делителей (т.е. с делителя блока 34, на выхода которого получаются импульсы квантования канала, компенсирующего максимальный сдвиг частоты Доплера) переписываются в регистры 11 и 12 соответственно. В дальнейшем коды с регистра 11 поступают в блок 8 задержки, число отводов которого равен М, где М - число вычисляемых ординат ВКФ. Цифровые отсчеты с выходов блока 8 задержки проходят через открытый блок 26 элементов ИЛИ, через блок 29 элементов ИЛ И и поступают на блок 25 умножения. Цифровые отсчеты с выхода регистра 12 проходят через открытый блок 17 элементов И, через блок 30 элементов ИЛИ на вторые входы блока 25 умножения. В умножителях блока 25 происходит перемножение входных отсчетов. Результаты перемножения поступают в блок 24, где производится накопление результатов перемножения.

При появлении импульса на выходе делителя 32, который определяет время накопления, триггер V устанавливается в нулевое состояние. До этого импульс с выхода делителя 32 проходит через элемент И 19. В блоке 23 определения максимального значения определяется код ординаты с максимальным значением ВКФ. Код ординаты с максимальным значением ВКФ выделяется на выходе блока 23, По импульсу с выхода элемента задержки 21, время задержки которого выбирается в соответствии с временем определения максимального значений блоком 23, код ординаты с максимальным, значением переписывается в регистр 10, С выхода регистра этот код выдается на выход коррелятора для определения разности мен прихода сигналов на вход коррелятора, а также на вход дешифратора 22, На разрешающий вход дешифратора 22 во втором цикле работы поступает разрешающий по-- тенциал, в результате чего разрешается ра бота дешифратора 22. Импульс с выхода элемента задержки 21 проходит через элемент ИЛИ 33 и производит обнуление делителя 31 блоков 34 и 35 и блока 24. С выхода дешифратора 22 снимается высокий потенциал только с того выхода, код которого поступает на вход дешифратора 22. Высокий потенциал с дешифратора 22 открывает те элементы блока 27 элементов И, которые подключены к тому отводу блока 8 задержки, который компенсирует разность времени прихода входных сигналов. Таким образом, отсчеты с выбранного отвода блока 8 задержки проходят через блок 27 элементов И/через блок 29 элементов ИЛИ и поступают на. первые входы блока 25 умножения.

Во втором цикле вычислений, так как триггер 7 находится в нулевом состоянии, то блок 17 элементов И и блок 26 элементов И закрыты, а элементы блока 28 открыты. Цифровые отсчеты с выходов блоков АЦП 3 и 4 поступают через открытый блок 28 элементов И и блок 30 элементов ИЛИ на вторые входы блока 25. На блок 28 элементов И эти отсчеты поступают следующим образом: первыми поступают импульсьгквантрвания с выхода блока 35 делителей. По этим импульсам срабатывают АЦП блока 4. Следующим появляется импульс квантования на

выходе делителя 31, затем импульсы квантования на выходе блока 34 делителей. По импульсу с последнего делителя блока 34 (т.е. того, который служит для компенсации 5 максимальной доплеровской частоты и который позже всех появляется) переписываются цифровые отсчеты с регистров 11, 12, 13 и 14, осуществляемся сдвиг информации в блоке 8 задержки и подача импульса син0 хронизации на блок 25 накопления. Таким образом, во втором цикле работы осуществляется обзор по разности частот Доплера в выбранном максимуме ВКФ, определенном в первом цикле. В блоке 25 умножения

5 осуществляется перемножение поступающих цифровых отсчетов, которые накапливаются в блоке 24 накопления. При появлении импульса на выходе делителя 32 он проходит через элемент И 18 устанавли0 вает триггер 6 в нулевое состояние и поступает на элемент задержки 20. В блоке 23 определения максимального значения снова определяется код максимальной ординаты ВКФ и этот код по импульсу с элемента

5 задержки 20 (время задержки элемента 20 выбирается большим времени срабатывания блока 23) переписывается в регистр 9. Таким образом, по окончании работы в регистре 10 записан код, определяющий раз0 ность времен приема входных сигналов, а в регистре 9 - код, определяющий разность доплеровских частот принимаемых сигналов.

5 Формула и з о б р е т.е н и я

Цифровой коррелятор;, содержащий два аналого-цифровых преобразователя, блок задержки, четыре блока элементов И, два блока элементов ИЛИ, блок умножения,

0 блок накопления, блок определения максимального значения, первый блок аналого- цифровых преобразователей, два элемента частоты, первый блок делителей частоты, два регистра, два триггера, три элемента И,

5 генератор тактовых импульсов, два элемента задержки и дешифратор, выходы которого соединены с первой группой информационных входов первого блока элементов И, выход которого подключен к первому входу перво0 го блока элементов, ИЛИ выходы которого соединены с первой группой входов блока умножения, выход которого подключен к информационному входу блока накопления, выходы которого соединены с информаци5 онными входами блока определения максимального значения, выход которого подключен к информационным входам первого и второго регистров, выход первого регистра является выходом значения разности доплеровских частот входных сигналов.

выход второго регистра соединен с входом дешифратора и с выходом ординаты с максимальным значением взаимной корреляционной функции коррелятора, первый информационный вход которого соединен с информационным входом первого аналого- цифрового преобразователя, вход синхронизации которого подключен к выходу первого делителя частоты, соединенному со входом синхронизации второго аналого- цифрового преобразователя, информацион- ный вход которого является вторым информационным входом коррелятора, подключенным к информационному входу первого блока аналого-цифровых преобразователей, вход синхронизации которого соединен с выходом первого блока делителей частоты, информационный вход которого подключен к информационным входам первого и второго делителей частоты и к выходу первого элемента И, первый вход которого соединен с выходом генератора тактовых импульсов, а второй вход подключен к прямому выходу первого триггера, S- вход которого является входом запуска коррелятора и соединен с S-входом второго триггера, прямой выход которого подключен к управляющим входам второго и третьего блоков элементов И, выход второго блока элементов И соединен со вторым входом первого блока элементов ИЛИ, выходы блока задержки подключены ко второй группе информационных входов первого блока элементов И и к информационным входам второго блока элементов И, инверсный выход второго триггера соединен с первым входом второго элемента И, тактовым входом дешифратора и с управляющим входом четвертого блока элементов И, выходы которого и выходы третьего блока элементов И подключены соответственно ко входам второго блока элементов ИЛИ, выходы которого соединены со второй группой входов блока умножения, выход второго делителя частоты соединен с R-входом второго триггера и со вторым входом второго элемента

И, выход которого подключен к R-входу первого триггера и через первый элемент задержки ко входу синхронизации первого регистра, выход второго элемента задержки

подключен ко входу синхронизации второго регистра, о тличающийся тем, что, с целью расширения частотного диапазона обрабатываемых сигналов, в него введены четыре регистра, элемент ИЛИ, второй блок

делителей частоты и второй блок аналого- цифровых преобразователей, информационный вход которого соединен со вторым информационным входом коррелятора, а выход подключен к информационному входу

третьего регистра, выход которого соединен с первым информационным входом четвертого блока элементов И, второй информационный вход которого подключен к выходу четвертого регистра, информационный вход

которого соединен с выходом первого блока аналого-цифровых преобразователей, выход первого аналого-цифрового преобразователя подключен к информационному входу пятого регистра, выход которого соединен с информационным входом блока задержки, тактовый вход которого подключен к старшему разрядному выходу первого блока делителей частоты, соединенному со входами синхронизации блока накопления,

третьего, четвертого, пятого и шестого регистров, информационный вход которого подключен к выходу второго аналого-цифрового преобразователя, а.выход соединен с информационным входом третьего блока элементов И, первый и второй входы третьего элемента И подключены соответственно к выходу второго делителя частоты и к прямому выходу второго триггера, а выход через второй элемент задержки соединен с первым входом элемента ИЛИ, второй вход которого подключен ко входу обнуления второго делителя частоты и ко входу запуска коррелятора, выход элемента ИЛИ соединен со входами обнуления первого делителя

частоты блоков делителей частоты и блока накопления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой коррелятор | 1990 |

|

SU1727132A1 |

| Цифровой коррелятор сигналов различной доплеровской частоты | 1988 |

|

SU1571612A1 |

| Устройство для определения взаимной корреляционной функции | 1990 |

|

SU1751779A1 |

| Цифровой автокоррелятор | 1990 |

|

SU1829042A1 |

| Цифровой коррелятор | 1990 |

|

SU1824642A1 |

| Цифровой коррелятор | 1982 |

|

SU1045233A1 |

| Устройство для измерения расстояния между центрами двух изображений точечного объекта | 1990 |

|

SU1788597A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| Устройство для определения взаимной корреляционной функции | 1986 |

|

SU1406602A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

Изобретение относится к измерительной и вычислительной технике и может быть использовано для измерения функции взаимной корреляции между двумя случайны Wtes-wy- v -, Л.. rrx ми процессами, задержанными один относительно другого. Цель изобретения - расширение частотного диапазона обрабатываемых сигналов. Коррелятор содержит аналого- цифровые преобразователи 1 и 2, блоки 3, А аналого-цифровых преобразователей, генератор тактовых импульсов 5, триггеры 6, 7, блок 8 задержки, регистры 9-14, элементы И 18,19, блоки 17,26-28 элементов И, блоки 29.30 элементов ИЛИ, делители частоты 31, 32, блоки 34, 35 делителей частоты, элементы задержки 20, 21, блок 23 определения максимального значения, блок 24 накопления и блок 25 умножения. 1 ил.

| Взаимокоррелятор | 1984 |

|

SU1201846A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровой коррелятор сигналов различной доплеровской частоты | 1988 |

|

SU1571612A1 |

Авторы

Даты

1992-04-15—Публикация

1990-07-18—Подача