сд

ОЭ

ел

СА5

315

Изобретение от} осится к вычислительной и измерительной технике и может быть использовано для определения корреляционной функщ1И каждого из суммы случайных сигна- юв, по подвергнутых различным масштабно- временным искажениям.

Цель изобретения- повышение точности.

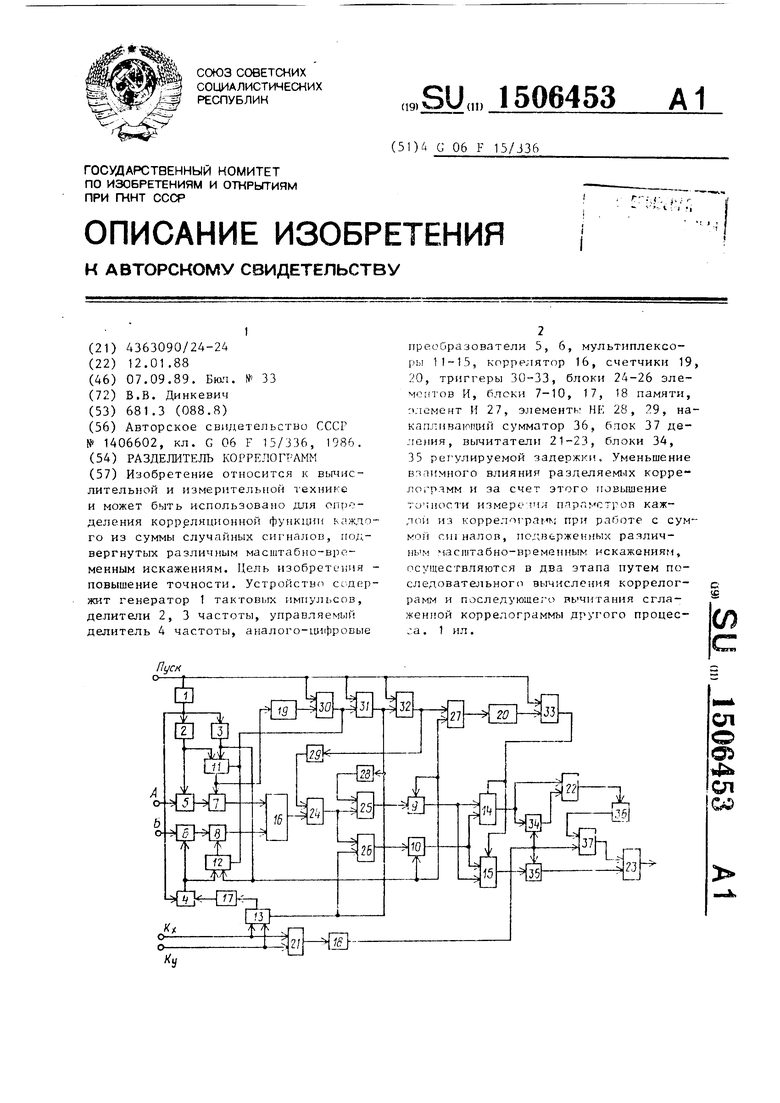

На чертеже изображена блок-схема разделителя коррелограмм.

Разделитель содержит генератор 1 тактовых импульсов, делители 2 и 3 частоты, управляемый делитель А час- тоты, аналого-цифровые преобразователи (АЦП) 5 и 6, блоки 7-10 памяти, мультиплексоры 11-15, коррелятор 16, блоки 17 и 13 памяти, счетчики 19 и 20, вычитатели 21-23, блоки 24-26 элементов И, элемент И 27, элементы НЕ 28 и 29 триггеры 30-33, блоки ЗА и 35 регулируемой задержки, накапливающий сумматор 36 и блок 37 деления.

Разделитель коррелограмм работает следующим образом.

На вход А поступает сигнал x(t)+ y(t), на вход Б - сигнал x()+ y(t+K,t). В первом цикле разделитель настроен на коэффициент К масштабно временных искажений (МВИ) процесса х Б результате выполнения этого цикла в блоке памяти устройства хранится сумма КФ процесса х и сглаженной КФ процесса у. Во втором цикле разделитель настраивается на коэффициент К у МВИ процесса у и определяет сумму КФ процесса у со сглаженной КФ процеса X. Эта сумма тоже запоминается в памяти устройства, чем завершается первый этап его работы.

Улучшить разделение коррелограмм можно, если знать вклад, который вносят сглаженные КФ в результате, по- лученные на первом этапе. Оценка этого вклада для каждой из коррелограмм и его вычитание из сумм, полученных на первом этапе, производятся в двух циклах второго этапа работы разделителя коррелограмм.

В исходном состоянии счетчики 19 и 20, триггеры 30-33 и накапливающий сумматор 36 обнулены. Анализируемые сигналы пост т1ают на входы А и Б, на входах К и К ,, присутствуют коды соответствующих коэффициентов МВИ. Мультиплексор ГЗ подключает код К к входу блока 17 памяти, вьшолняющего

Q

5 0 5

0 Q

0

5

334

функции преобразователя кода. Благодаря- этому на управляющий вход делителя 4 частоты поступает код, соответствующий значению коэффициента К, МВИ процесса х. Объемы памяти блоков 7 и 8 таковы, что в них помещаются выборки входных реализаций, обеспечивающие вычисление коррелог- раммы с необходимым фактором усреднения. идентичных блоков 9 и 10 памяти таков, что каждый их них способен хранить одну коррелограмму.

Первый цикл работы на первом этапе начинается с приходом запускающего импульса, который включает генератор 1 и подтверждает (устанавливает) нулевое состояние триггеров 30-33. Тактовые импульсы проходят через делитель 2 и поступают на вход запуска АЦП 5 и через мультиплексор 11 на синхровход блока 7 памяти. Делитель 4 имеет в первом цикле коэффициент деления, определяемый значением коэффициента К, а именно в /(+К раз меньший, чем делитель 2. Импульсы с его выхода тактируют АЦП 6 и через мультиплексор 12 блок 8 памяти.

Таким образом, входные сигналы А и Б дискретизируются, каждый со своей частотой (сигнал А с частотой Гр, сигнал Б с частотой fo(1+K) и записываются в блоки 7 и 8 памяти. Запись отсчетов продолжается до переполнения счетчика 19, емкость которого определяется объемом выборки входных реализаций, необходимой для построения коррелограммы, и равна количеству отсчетов в выборке. Импульс с выхода счетчика 19 поступает на вход триггера 30 и устанавливает его в состояние 1. При этом мультиплексоры 11 и 12 подключают выход делителя 3 частоты к синхронизирующим входам блоков 7 и 8 памяти и входу счетчика 19.

Начинается считывание выборки из блоков 7 и 8 памяти с частотой следования импульсов на выходе делителя 3. Фиксированный коэффициент деления делителя 3 частоты выбран таким, чтобы за время заполнения импульсами с его вькода счетчика 19 произошло построение коррелограммы коррелятором 16, Поскольку дискретизация входных сигналов выполнялась с различной частотой, а воспроизведение отсчетов из памяти - с одинаковой частотой, то произошло взаимное мае515

штабно-временное преобразование входных сигналов, которое скомпенсирован МВИ процесса х. Отсчеты реализаций сигналов А и Б поступают на входы коррелятора 16, которьп определяет К между ними. Отсчеты КФ через открытые элементы И 24 и 25 записываются в блок 9 памяти. Таким образом, в первом цикле происходит запись в бло

9памяти первичной КФ процесса х, которая, кроме собственно КФ процесса X, содержит сглаженную КФ процесса у

По окончании первого цикла счетчи 19 переполняется и возвращает триг- гер 30 в нулевое состояние. Триггер

31.при этом переходит в состояние 1 и с помощью мультиплексора 13 подключает код Ку к входу блока 17. Работа разделителя коррелограмм во втором цикле протекает аналогично первому за исключением того, что во втором цикле происходит взаимное мас щтабно-временное преобразование входных сигналов, компенсирующее МВИ про цесса у, отсчеты КФ через элементы

И 24 и 26 записываются в блок 10 памяти.

По окончании второго цикла тригге

32переходит в состояние 1, сигнал с его выхода, пройдя через элемент

НЕ 29, блокирует режим записи а блоки 9 и 10 памяти. Так начинается второй этап работы разделителя коррелограмм, на котором блоки 9 и

10памяти работают в режиме считывания.

Триггер 33 находится в состоянии О, благодаря этому содержимое блока 9 памяти, т.е. первичная КФ про- цесса X, через мультиплексор 14 поступает на узел сглаживания, состоящий из блоков 34, 22, 36 и 37. Разность коэффициентов МВИ процессов X и у с выхода вычитателя 21 через преобразователь кода, вьшолнен- ный в виде блока 18 памяти, поступает на управляющие входы двух идентичных блоков 34 и 35 регулируемой задержки. Поэтому каждый из низ за- держивает поступающие на него отсчеты на время (К - Ку)Т, являющееся параметром сглаживания. В силу этого на выходе вычитателя 22 формируется разность между первичной КФ процес- са X и той же КФ задержанной на время (Кд-К)Т. Включенный после накапливающего сумматора 36 блок 37 деления осуществляет масштабирование

ад

5

20 5

0

п с Q с

5

536

сглаженной КФ путем деления на параметр сглаживания, который поступает от блока 18. На выходе блока 37 деления формируется сглаженная первичная КФ процесса. Одновременно происходит считывание блока 10 памяти, хранящего первичную КФ процесса у. Последняя является суммой собственно КФ процесса у и сглаженной КФ процесса х, следовательно, вычитание из нее сглаженной первичной КФ процесса х уменьшает вклад одной коррелограммы в другую. Вычитание происходит с помощью вычитателя 23. Блок 35 регулируемой задержки используется в схеме для синхронизации первичной КФ, поступающей с вьсхода мультиплексора 15,и сглаженной КФ, задержанной на время (К,-К;,)Т. Таким образом, в первом цикле второго этапа на выходе вычитателя 23 формируется коррелограмма процесса у, полностью очищенная от вклада коррелограммы процесса х. По окончании первого цикла происходит переполнение счетчика 20, емкость которого равна объему блока 9 (10) памяти. Триггер 33 устанавливается в состояние 1 и переводит мультиплексоры 14 и 15 в положение, при котором на выход мультиплексора 14 и, следовательно, на схему сглаживания поступает первичная КФ процесса у, т.е. содержимое блока 10 памяти, а на блок 35 регулируемой задержки и далее- вычитатель 23 - содержимое блока 9 памяти, т.е. первичная КФ процесса X. В результате этого во втором цикле второго этапа на выходе вычитателя 23 формируется коррелограмма процесса X, очищенная от вклада коррелограммы процесса у.

формула изобретения

Разделитель коррелограмм, содержащий два аналого-цифровьрс преобразователя, коррелятор, четыре блока памяти, генератор тактовых импульсов, элемент И, три блока элементов И, четыре триггера, два делителя частоты, управляемый делитель частоты, четыре мультиплексора, два счетчика, вычитатель, причем информационные входы первого и второго аналого-цифровых преобразователей являются соответствующими информационными входами разделителя, выходы первого и второго аналого-цифровых преобразователей соединены с информашюкными входами со- отверственно норного и в г()р(,)го блоков памяти, выходы которых (соединены с соответствут1Ц ми входами корре- ляТора, вькод которого соединен с группой информационных входов первого блока элементов И, вход запуска генератора тактовых импульсов соединен с входами установки в О с перво- д мяти, выход которого соединен с уп15

30

го по четвертый триггеров и является входом запуска разделителя, выход генератора тактовых импульсов соединен с входами первого и второго делителей частотл и с входом управляемого делителя частоты, выходы первого делителя частоты и управляемого делителя частоты соединены соответственно с входами запуска первого и второго аналого-цифровых преобразова-120 телей и с первыми информационными входами соответственно первого и второго мультиплексоров, управляющие входы которых соединены с выходом первого триггера, выход первого муль- 25 типлексора соединен с синхронизирующим входом первого блока памяти и со счетным входом первого счетчика, выход переполнения котор лго соединен с выходом установки в 1 первого триггера, выход второго мультиплексора соединен с синхронизирующим второго блока памяти, выход второго делителя частоты соединен с вторыми информационными входами вого и второго мультиплексоров, выход второго триггера соединен с входом установки в 1 третьего триггера, выход элемента И соединен со счетным входом второго счетчика, выход Q переполнения которого соединен с входом установки в 1 четвертого триггера, выход которого сЪединен с управляющим входом третьего мультиплексо- .ра, выходы второго и третьего блоков элементов И соединены с информацион-. ными входами соответственно третьего и четвертого блоков памяти, выход четвертого блока памяти соединен с первым информационным входом четвертого мультиплексора, отличающийся тем, что, с целью повышения точности, в него введены два элемента НЕ, накапливающий сумматор, блок деления, второй и третий вычитатели, два блока регулируемой задержки, пятьп и шестой блоки памяти, лятый мультиплексор, причем первый и второй информационные входы

35

45

50

55

равляющим входом управляемого делите ля частоты, прямой выход первого триггера соединен с входом установки в 1 второго триггера, выход первого блока элементо.в И соединен с группами информационных входов вто рого и третьего блоков элементов И, выход второго триггера соединен с управляющим входом пятого мультиплек сора с управляющим входом третьего блока элементов И и через первый эле мент НЕ с управляющим входом второго блока элементов И, выход третьего триггера соединен с первым входом элемента И и через второй элемент НЕ с управляю цим входом первого блока элементов И, выход второго делителя частоты соединен с синхронизирующими входами третьего и четвертого блоков памяти и вторым входом элемента И, выход четвертого блока памяти соединен с первым информационным входом третьего мультиплексора, второй информационный вход которого соединен с вторым информационным входом четвертого мультиплексора и выходом третьего блока памяти, выход четвертого триггера соединен с управляющим входом четвертого мультиплексора, вы ход которого соединен с информационным входом первого блока регулируемой задержки, выход которого соединен с входом уменьшаемого второго вы читателя, вход вычитаемого которого соединен с выходом блока деления, вход делителя которого соединен с входами задания временного параметра первого и второго блоков регулируемой задержки и выходом шестого блока памяти, адресный вход которого со единен с выходом первого вычитателя, выход третьего мультиплексора соединен с входом уменьшаемого третьего вычитателя и информационным входом второго блока регулируемой задержки, выход которого соединен с входом вычитаемого третьего вычитателя, выход которого соединен с входом накап ливаюшего сумматора, выход которого

пятого мультиплексора c(eдинeны соответственно с входаьш уменьшаемого и вычитаемого первого вычитателя и являются входами задания коэффициен- тов искажений соответственно первого и второго сигналов разделителя, выход пятого мультиплексора соединен с синхронизирующим входом пятого блока па5

0

0 5 Q 5

5

0

5

равляющим входом управляемого делителя частоты, прямой выход первого триггера соединен с входом установки в 1 второго триггера, выход первого блока элементо.в И соединен с группами информационных входов второго и третьего блоков элементов И, выход второго триггера соединен с управляющим входом пятого мультиплексора с управляющим входом третьего блока элементов И и через первый элемент НЕ с управляющим входом второго блока элементов И, выход третьего триггера соединен с первым входом элемента И и через второй элемент НЕ с управляю цим входом первого блока элементов И, выход второго делителя частоты соединен с синхронизирующими входами третьего и четвертого блоков памяти и вторым входом элемента И, выход четвертого блока памяти соединен с первым информационным входом третьего мультиплексора, второй информационный вход которого соединен с вторым информационным входом четвертого мультиплексора и выходом третьего блока памяти, выход четвертого триггера соединен с управляющим входом четвертого мультиплексора, выход которого соединен с информационным входом первого блока регулируемой задержки, выход которого соединен с входом уменьшаемого второго вычитателя, вход вычитаемого которого соединен с выходом блока деления, вход делителя которого соединен с входами задания временного параметра первого и второго блоков регулируемой задержки и выходом шестого блока памяти, адресный вход которого соединен с выходом первого вычитателя, выход третьего мультиплексора соединен с входом уменьшаемого третьего вычитателя и информационным входом второго блока регулируемой задержки, выход которого соединен с входом вычитаемого третьего вычитателя, выход которого соединен с входом накап- ливаюшего сумматора, выход которого

9150645310

соединен с входом делимого блока де- ется выходом разделителя, ления, выход второго вычитателя явля

| название | год | авторы | номер документа |

|---|---|---|---|

| Разделитель коррелограмм | 1988 |

|

SU1624478A1 |

| Устройство для определения взаимной корреляционной функции | 1986 |

|

SU1406602A1 |

| Устройство для определения взаимной корреляционной функции | 1990 |

|

SU1751779A1 |

| Устройство для разделения коррелограмм | 1987 |

|

SU1432558A1 |

| Устройство для разделения коррелограмм | 1987 |

|

SU1439619A1 |

| Устройство для определения взаимных корреляционных функций | 1981 |

|

SU1016791A1 |

| Коррелометр | 1989 |

|

SU1644159A1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2446454C1 |

| Устройство для определения взаимной корреляционной функции | 1983 |

|

SU1108463A1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ И ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2449350C1 |

Изобретение относится к вычислительной и измерительной технике и может быть использовано для определения корреляционной функции каждого из суммы случайных сигналов, подвергнутых различным масштабно-временным искажениям. Цель изобретения - повышение точности. Устройство содержит генератор 1 тактовых импульсов, делители 2, 3 частоты, управляемый делитель 4 частоты, аналого-цифровые преобразователи 5, 6, мультиплексоры 11-15, коррелятор 16, счетчики 19, 20, триггеры 30-33, блоки 24-26 элементов И, блоки 7-10, 17, 18 памяти, элемент И 27, элементы НЕ 28, 29, накапливающий сумматор 36, блок 37 деления, вычитатели 21-23, блоки 34, 35 регулируемой задержки. Уменьшение взаимного влияния разделяемых коррелограмм и за счет этого повышение точности измерения параметров каждой из коррелограмм при работе с суммой сигналов, подверженных различным масштабно-временным искажениям, осуществляются в два этапа путем последовательного вычисления коррелограмм и последующего вычитания сглаженной коррелограммы другого процесса. 1 ил.

| Устройство для определения взаимной корреляционной функции | 1986 |

|

SU1406602A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-09-07—Публикация

1988-01-12—Подача