Изобретение относится к автоматике и вычислительной технике и может быть использовано при разработке устройств отображения координатной информации для автоматизированных систем управления и систем автоматического проектирования.

Цель изобретения - повышение точности устройства.

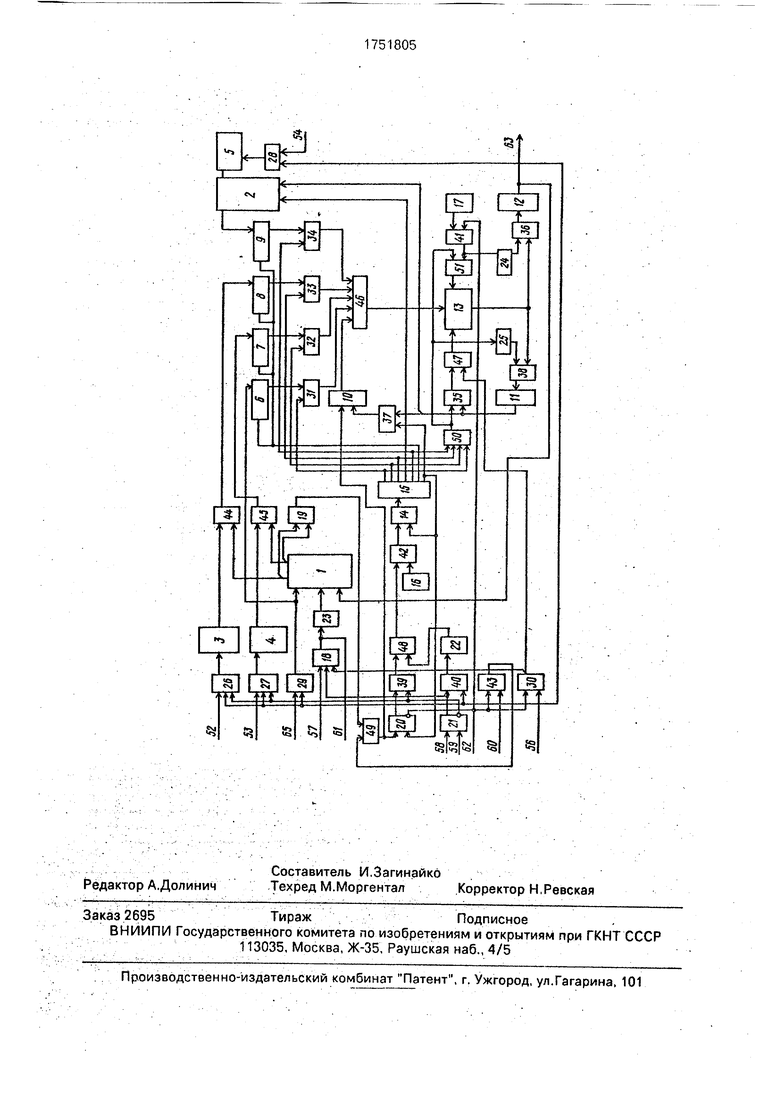

На чертеже представлена функциональная схема.

Устройство содержит первый 1 и второй 2 вычислители, первый 3, второй 4 и третий 5 синусно-косинусные преобразователи, с первого по шестой блоки 6-11 памяти, регистр 12, умножитель 13, счетчик 14, дешифратор 15, первый 16 и второй 17 генераторы тактовых импульсов, первый 18 и второй 19 блоки сравнения, первый 20 и второй 21 триггеры, с первого по четвертый элементы 22-25 задержки, с первого по тринадцатый блоки 26-38 элементов И, с первого по пятый элементы 39-43 И, с первого по четвертый блоки 44-47 элементов ИЛИ, с первого по четвертый элементы 48-51 ИЛИ.

Позициями с 52-57 обозначены соответственно с первого по шестой информационные входы, с 58-60 - с первого по третий управляющие входы, 61 и 62 - первый и второй управляющие выходы, а 63 - информационный выход устройства.

Вычислитель 1 предназначен для вычисления значений sin и cos углов поворота изображений вокруг осей X и Z в режиме слежения по формулам, приведенным в описании устройства-прототипа.

Вычислительный блок 2 предназначен для вычисления значений sin и с.с$ угла поворота изображения вокруг оси в соответствии со следующими выражениями

cos/ - cos a cos pv - sin a sin #v ,

sin / - cos a sin v - sin a cos #v, где

-S31

cos a - -VSSi +Sib

СЛ

с

VJ ел

00

о

СЛ

slna --Ј

5зз

+ s33

где Sij - элементы результирующей матрицы S: sin ( и cos py соответствующие тригонометрические функции, определяемые управляемым значением угла поворота вокруг оси Y, поступающим на вход устройства 54.

Вычислители 1 и 2 могут быть реализованы в виде микропроцессоров, программно выполняющих данные преобразования информации или спецвычислителей для аппаратной реализации указанных математических соотношений.

Умножитель 13 предназначен для выполнения операции перемножения матриц и умножения матрицы на вектор.

Синусно-косинусные преобразователи информации 3-5 предназначены для вычисления значений sin и cos по входящему значению угла р,

Блоки 6-11 памяти предназначены для упорядоченного хранения значений элементов матриц размером 4x4, В исходном состоянии в блоках памяти хранятся значения единичных матриц.

Устройство работает следующим образом.

В исходном состоянии в блоках 6-9 памяти хранятся элементы единичных матриц, а в блоках 10, 11 памяти хранятся элементы результирующей матрицы преобразования, полученные в предшествующем цикле изменения ракурса наблюдения или при начальной установке ракурса. Триггеры 20 и 21 находятся в нулевом состоянии и единичный сигнал с инверсного выхода триггера 20 разрешает прохождедие информации о текущих координатах (X)i, отображаемых объектов через блок 30 элементов И и блок 47 элементов ИЛИ на первый информационный вход умножителя 13. Этим же сигналом с инверсного выхода триггера 20 разрешается прием управляющего сигнала начала установки нового ракурса наблюдения на вход 60 и прохождение тактовых импульсов с выхода генератора 17 через элементы И 41 и ИЛИ 51 на управляющий вход умножителя 13. Импульсы с генератора 17 определяют периодичность выполнения операции умножения входящего вектора Х| на результирующую матрицы Sp, хранящуюся в блоке 10 памяти, связанном со вторым информационным входом умножителя 13 через блок элементов 46 ИЛИ. При этом частота следования импульсов с выхода генератора 17 должна быть согласована с частотой поступления информации о текущих координатах хТ.

Результат перемножения лГ Sp поступает в регистр 12 через блок 36 элементов

И. Разрешением на выдачу результата перемножения в регистр 12 является сигнал генератора 17, задержанный на элементе 24 задержки на время перемножения операндов в умножителе 13. Выход регистра 12 непосредственно связан с информационным выходом устройства 63.

При изменении ракурса наблюдения на информационные входы 52-55 поступают

соответственно значения р , fy, , D (Dx, Dy, Dz), определяющие параметры нового ракурса наблюдения, Указанные данные могут поступать, например, с пульта ввода информации оператора, Процесс установки нового ракурса начинается после поступления управляющего сигнала на вход 60 устройства, По этому сигналу триггер 20 через элемент 43 И и элемент 49 ИЛИ устанавливается в единичное состояние. Тем самым запрещается прохождение информации через блок 30 элементов И и элемент 41 И и разрешается выдача информации о значениях р , ,p/ через блоки 26, 27, 28 элементов И соответственно на

входы синусно-косинусных преобразователей 3, 4 и 5, а нформация о значении величин сдвигов D - через блок 29 элементов И на вход блока 6 памяти. Кроме того, сигналом с выхода элемента 49 ИЛИ осуществляется обнуление регистров блока 10 памяти и выдается осведомителъный сигнал на выход 62 устройства. ЗначенияТТзаписывают- ся в соответствующие ячейки (регистры) блока 6 памяти таким образом, что в нем

формируется матрица вида

1000

Ао 0 1 00

0010

-Dx Dy-Dz 1

На выходах синусно-косинусных преобразователей 3-5 формируются значения sin и cos соответствующих аргументов. Полученные значения с выходов преобразова- телей 3 и 4 поступают на информационные входы блоков 7 и 8 памяти через соответствующие блоки 44 и 45 элементов. В результате в блоках 7 и 8 памяти будут сформированы следующие матрицы соответственно 0 , О ОО

Az 0 01 Ч0

О 0 01

100О

0 slnpx О

Ах 0 cospx О 0001

Единичный сигнал триггера 20 через элемент 39 И (открытый единичным сигналом с инверсного выхода тригера 21), элемент 48 ИЛИ разрешает прохождение тактовых импульсов гененаторэ 16 через элемент 42 И на счетный вход счетчика 14. На выходах дешифратора 15 в зависимоси от состояния счетчика 14 формируются единичные сигналы, управляющие работой устройства в режиме вычисления значений результирующей матрицы преобразования Sp.

По первому сигналу дешифратора 15 разрешается прохождение информации из блока б памяти на первый информационный вход умножителя 13 (через блок 46 элементов ИЛИ). Этим же сигналом дешифратора разрешается поступление на второй информационный вход умножителя элементов результирующей матрицы Sp, хранящейся в блоке 11 памяти (через блок 35 элементов И и блок 47 элементов ИЛИ). Кроме того, этот же сигнал дешифратора является управляющим сигналом, инициирующим запуск работы умножителя 13 (через элементы 50 и 51 ИЛИ). Результат перемножения Sp АО с выхода умножителя через блок 38 элемен- тов И, открытый задержанным на элементе 25 задержки сигналом с первого выхода дешифратора 15, записывается в блок 11 памяти. По поступлении сигналов со второго и третьего выходов дешифратора 15 произво- дятся аналогичные преобразования информации, в результате которых в блоке 11 памяти будет сформирован результат перемножения Sp AD AZ Ах.

По сигналу с четвертого выхода дешиф- ратора инициируется работа вычислителя 2, на первый информационный вход которого поступают значения sin ру и cos py с выхода преобразователя 5, а на второй информационный вход вычислителя 2 поступают значения 5з1, 5зз результирующей матрицы из блока 11 памяти. В результате работы вычислителя 2 в блоке 9 памяти будет сформирована матрица вида

cos/ у О -slnfi О

О 1 О О

sin/3

О cos/3

О

О О О

1

где sin/, cos ft вычисляются по формулам, приведенным в описании назначения вычислителя 2.

По сигналу с пятого выхода дешифрато- ра 15 открывается блок 34 элементов И и разрешается выполнение операции перемножения матриц умножителем 13 аналогично вышеописанному по сигналам с первого, второго и третьего выходов дешиф510

15 20 25 30

5 0

5

0

5

ратора 15. В результате этого в блока 11 памяти будет сформирован результат перемножения Sp AD Az Ах Ау. Содержимое блоки 11 памяти представляет собой новое значение результирующей матрицы преобразования информации Sp.

По сигналу с шестого выхода дешифра- тора 15 производится стирание информации в блоках 6-9 памяти и формирование в них единичных матриц. По сигналу с седьмого выхода дешифратора разрешается запись содержимого блока 11 памяти в блок 10 памяти через блок 37 элементов И. Этим же сигналом дешифратора производится сброс счетчика 14 и триггера 20. Тем самым запрещается прохождение тактовых импульсов генератора 16 и разрешается прием информации о текущих координатах X объектов изображения через блок 30 элементов И. Кроме того, разрешается прохождение тактовых импульсов генератора 17 через элемент 41 И и элемент 51 ИЛИ в качестве сигналов управления (запуска) умножителем 13. Таким образом, устройство вновь переводится в режим преобразования Sp текущих координат X в соответствии с параметрами, задаваемыми вновь рассчитанной результирующей матрицы преобразования.

При поступлении на управляющий вход 58 единичного сигнала (сигнала о переводе устройства в режим слежения) триггер 21 устанавливается в единичное состояние. Единичным сигналом с прямого выхода триггера 21 разрешается выполнение блоком 18 операции сравнения эталонных атрибутов FЈT объекта (точки) слежения с атрибутами объектов RI, поступающих на информационный вход 56 устройства. Такими атрибутами могут быть либо номера объектов, либо их координаты, либо и то и другое. При устройство продолжает осуществлять преобразование текущих координат )Гв соответствии с параметрами, задаваемыми результирующей матрицы преобразования Sp. В тоже время нулевым сигналом с инверсного выхода триггера 21 осуществляется блокировка изменения информации о PX,. , , поступающей на информационные входы 52 и 53, Тем самым после выбора точки слежения оператор лишается возможности сканировать линией визирования по углам р и pz , что исключает возможность визуальной потери им выбранной точки слежения до окончательного перевода устройства в режим слежения.

При поступлении на вход Сб информа- ции об объекте (точке) с Нэт - RI с выхода блока 18 снимается единичный сигнал, который выдается на упрапляющий выход 61 устройства. Этот же сигнал через элемент 23 задержки разрешает выполнение операции вычислителем 1. На информационные входы вычислителя поступают значения величин смещения D и значения ьювого вектора координат объекта слежения Хс, полученного в результате перемножения входящих координат объекта слежения Хс на результирующую матрицу преобразования Sp. Время задержки распространения сигнала на элементе 23 определяется временем перемножения Хс Sp в умножителе 13 и записи результата в регистр 12.

Вычислитель 1 осуществляет расчет значений sin ($.

cosy

поступающих для

запоминания в блок 7, и значений sin {% , ,

cos ($. , поступающих для запоминания в блок 8 (соответственно через блоки 45 и 44 элементов ИЛИ). Информация означениях sin

{Ј ,, (f% , , поступающих на входы блока 19, используется для определения необходимости корректировки результирующей матрицы преобразования координат в режиме

слежения. Так, если sin /% , , 0, то точка слежения не изменила свое место-положение и необходимость корректировки отсутствует, В противном случае с выхода блока 19 снимается единичный сигнал, поступающий через элемент 49 ИЛИ на установочный вход триггера 20 и переводит его в единичное состояние. Устройство переводится в режим изменения (корректировки) результирующей матрицы преобразования Sp. Одновременно запрещается прием входящей информации через блок 30 элементов И, о чем сообщается единичным сигналом на управляющий выход 62.

Сброс режима слежения осуществляется подачей единичного сигнала на управляющий вход 59 устройства.

Таким образом, устройство в режиме преобразования координат X осуществляет их пересчет в соответствии с параметрами, задаваемыми результирующей матрицей преобразования Sp. Изменение параметров преобразования может осуществляться ре- куррентно как при ручном изменении параметров ракурса при ручном наблюдения, зада- ваемых значениями сдвигов точки наблюдения вдоль Соответствующих осей координат и поворотов изображения вокруг осей X, Y, Z, так и автоматически при переводе устройства в специальный режим слежения за заданной (произвольной) точкой отображаемого процесса. При этом в устройстве осуществляется автоматическая компенсация неконтролируемого вращения изображения вокруг оси Y.

Устройство обладает широкими функциональными возможностями и при этом обеспечивает высокую точность пересчета координат отображаемых объектов за счет

исключения возможности неконтролируемого вращения отображаемых объектов вокруг оси, т.е. исключения паразитного крена изображения, что приводит к повышению качества информации, представляемой

оператору, что приводит к принятию им более качественных и обоснованных решений. Область применения такого устройства для вычисления координат практически не ограничена в рамках использования

средств отображения информации в АСУ самого различного назначения. Наибольший эффект от внедрения такого устройства может быть получен в АСУ, где от качества отображаемой информации и возможностей по ее представлению во многом зависит алгоритм работы оператора такой АСУ. Формула изобретения Устройство для вычисления координат отображаемых объектов, содержащее с первого по пятый блоки памяти, с первого по третий синусно-косинусные преобразователи, с первого по одиннадцатый блоки элементов И, первый и второй блоки элементов ИЛИ, с первого по четвертый элементы И,

первый и второй элементы ИЛИ, первый и второй генераторы тактовых импульсов, первый и второй триггеры, регистр, с первого по третий элементы задержки, первый и второй блоки сравнения и первый вычислитель, первые входы соответственно первого - четвертого блоков элементов И являются с первого по четвертый информационными входами устройства, а вторые входы соединены с прямым выходом первого триггера,

подключенным к первым входам первого и второго элементов И, инверсный выход первого триггера соединен с первыми входами третьего элемента И и пятого блока элементов И, второй вход которого является пятым

информационным входом устройства, шестым информационным входом которого является первый информационный вход первого блока сравнения, второй информационный вход которого соединен с прямым

выходом второго триггера, подключенным к первому входу второго элемента И, выход которого через первый элемент задержки подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с

выходом первого элемента И, второй вход которого подключен к инверсному выходу второго триггера, соединенному с третьими входами первого и второго блоков элементов И, выходы которых подключены соответ твенно к входам первого и второго

синусно-косинусного преобразователя, выходы которых подключены к первым входам соответственно первого и второго блоков элементов ИЛИ, вторые входы которых соединены соответственно с первым и вторым выходами первого вычислителя, которые подключены к входам второго блока сравнения, выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с установочным входом первого триггера, вход сброса которого соединен с первым выходом дешифратора, подключенным к входу сброса счетчика, счетный вход которого соединен с выходом четвертого элемента И, первый вход которого подключен к выходу первого генератора тактовых импульсов, а второй вход - к выходу первого элемента ИЛИ, выход счетчика соединен с входом дешифратора, выход четвертого блока элементов И - с первым информационным входом первого вычислителя, управляющий вход которого соединен через второй элемент задержки с выходом первого блока сравнения, который является первым управляющим выходом устройства, второй информационный вход первого вычислителя соединен с выходом регистра, адресный вход первого и адресные входы второго и третьего блоков памяти соединены соответственно с выходами второго и первого блоков элементов ИЛИ, выходы первого - четвертого блоков памяти подключены к первым входам соответственно шестого - девятого блоков элементов И, выход второго генератора тактовых импульсов соединен с вторым входом третьего элемента И, выход третьего блока элементов И подключен к входу третьего синусно-косинусного преобразователя, установочный вход и вход сброса второго триггера являются первым и вторым управляющими входами устройства, управляющий вход первого блока сравнения соединен с выходом пятого блока элементов И, отличающееся тем, что, с целью повышения точности устройства, оно содержит второй вычислитель, шестой блок памяти, двенадцатый и тринадцатый блоки элементов И, третий и четвертый блоки элементов ИЛИ, четвертый элемент задержки, пятый элемент И, третий и четвертый элементы ИЛИ, выход третьго синусно-косинусного преобразователя соединен с первым информационным входом второго вычислителя, выход которого соединен с адресным входом четвертого блока памяти, второй - пятый выходы дешифратора соединены с вторыми входами с шестого по девятый блоков элементов И и входами 5 третьего элемента ИЛИ, выход которого подключен к первым входам десятого блока элементов И и четвертого элемента ИЛИ, выход которого соединен с управляющим входом умножителя, первый и второй ин0 формационные входы которого подключены соответственно к выходам четвертого и третьего блоков элементов ИЛИ, выход умножителя - к первым входам одиннадцатого и тринадцатого блоков элементов И, вторые

5 входы которых подключены соответственно к выходу третьего элемента И, соединенному с вторым входом четвертого элемента ИЛИ, и выходу третьего элемента ИЛИ, выход тринадцатого блока элементов И соеди0 нен с входом шестого блока памяти, выход которого подключен к второму входу десятого блока элементов И. первому входу двенадцатого блока элементов И и второму информационному входу второго вычисли5 теля, второй вход двенадцатого блока элементов И соединен с первым выходом дешифратора, шестой выход которого подключен к управляющим входам с первого по четвертый блоков памяти, а седьмой выход

0 - к управляющему входу второго вычислите-, ля, выход одиннадцатого блока элементов И подключен к входу регистра, выход которого является информационным выходом устройства, выход пятого блока элементов И

5 соединен с первым входом четвертого блока элементов ИЛИ, второй вход которого подключен к выходу десятого блока элементов И, первый вход пятого элемента И соединен с инверсным выходом первого триггера,

0 второй вход является третьим управляющим входом устройства, выход пятого элемента И соединен с вторым входом второго элемента ИЛИ, выход которого подключен к адресному входу пятого блока памяти, уп5 равляющий вход которого подключен к выходу двенадцатого блока элементов И, выход пятого блока памяти соединен с первым входом третьего блока элементов ИЛИ, второй - пятый входы которого соединены с

0 выходами соответственно с шестого по девятый блоков элементов И, инверсный выход первого триггера является вторым управляющим выходом устройства.

55

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления координат отображаемых объектов | 1987 |

|

SU1444875A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1986 |

|

SU1357996A1 |

| Устройство для формирования информации на телевизионном индикаторе | 1981 |

|

SU1075298A1 |

| ИМПУЛЬСНО-ДОПЛЕРОВСКАЯ РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1990 |

|

RU2037844C1 |

| Устройство для отображения графической информации на газоразрядной индикаторной панели | 1982 |

|

SU1108488A1 |

| ПРИЕМОИНДИКАТОР РАДИОНАВИГАЦИОННОЙ СИСТЕМЫ | 1991 |

|

RU2027196C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ НИЗКОЧАСТОТНЫХ ДОПЛЕРОВСКИХ СИГНАЛОВ | 1985 |

|

SU1281125A1 |

| Устройство для моделирования удара твердых тел | 1988 |

|

SU1567889A2 |

| БОРТОВАЯ СТАНЦИЯ ОПРЕДЕЛЕНИЯ КООРДИНАТ ДВИЖУЩИХСЯ ИСТОЧНИКОВ ИЗЛУЧЕНИЯ | 1989 |

|

SU1841039A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU983707A1 |

Сущность изобретения: устройство содержит: два вычислителя, три синусно-коси- нусных преобразователя, шесть блоков памяти, регистр, умножитель, счетчик, дешифратор, два генератора тактовых импульсов,, два блока сравнения, два триггера, че- тыре элемента задержки, 13 блоков элементов И, пять элементов И, четыре блока элементов ИЛИ, четыре элемента ИЛИ. 26-3-44-8-33-46-13-36-12-1-45-7-32-46, 27-4- 45, 29-19-49-10-46, 49-20-26, 20-29-6-31-46, 20-27, 20-43-49, 20-30-18-23-1-44, 21-39-48- 42-14-15-20, 15-14, 16-42,21-40-22-48,30-47- 13, 15-50-35-47, 15-31, 15-32, 15-33, 15-34, 20-40, 20-28-5-2-9-34-46, 13-38-11-37-10, 50- 25, 50-51-13, 50-25-38, 17-41-51, 41-24-36, 11-2, 15-2, 11-35,15-6,15-7, 15-8, 15-9,21-18, 21-27,21-26. 1 ил.

| Устройство для вычисления координат отображаемых объектов | 1988 |

|

SU1539823A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-07-30—Публикация

1990-01-18—Подача