Изобретение относится к электротехнике, в частности к диагностированию электрической связи, и может быть использовано для контроля качества питания вычислительной и другой сложной электронной техники.

Известно устройство для обнаружения предельных значений, содержащее триггер Шмитта, конденсатор, стабилитрон, тиристор.

Недостатком данного устройства является то, что оно не позволяет обнаруживать провалы и пропажу напряжения, а следовательно, не позволяет провести классификацию сетевых помех.

Наиболее близкой к заявляемой по технической сущности является схема для определения падения напряжения сети ниже допустимого уровня, содержащая транс- Форматор, двухполупериодный выпрямитель, делитель напряжения, стабилитрон,

первый и втЬрой RS-триггеры, первый и второй одновибраторы, коммутатор, элемент И, триггер Шмитта. .

Недостатком данного устройства является то, что оно не позволяет обнаружить возникновение в сети всплесков перенапряжения и провалов напряжения, а следовательно, не позволяет провести классификацию сетевых помех.

Целью изобретения является расширение функциональных возможностей устройства за счет возможности классификации сетевых помех путем анализа интенсивности всплесков перенапряжения, провалов напряжения и пропажи напряжения.

Указанная цель достигается тем, что в анализатор качества сети, содержащий выпрямительный блок, RS-триггер, одновибратор, элемент И, компаратор, триггер Шмитта, введенные второй триггер Шмитта, второй компаратор, второй и третий элеменСА

ты И, элемент НЕ, элемент ИЛИ-НЕ, первый и второй элементы ИЛИ, первый и второй элементы задержки, генератор, первый, второй и третий счетчики, реверсивный счетчик, первый, второй и третий дешифраторы, первый, второй и третий блоки индикации, первый, второй и третий регистры, первый и второй элементы индикации, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем первый выход выпрямительного блока соединен с первым входом второго компаратора, второй вход которого является входом первого опорного напряжения, первый выход выпрямительного блока соединен с первым входом первого компаратора, второй вход которого явл тется входом второго опорного напряжения, а выход соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с входом элемента НЕ и с выходом первого элемента И, а выход соединен со счетным входом реверсивного счетчика, вход переключения счета которого соединен с выходом элемента НЕ, а выходы соединены с D-входами первого регистра, выходы которого соединены со входами первого дешифратора, первые выходы которого соединены с соответствующими входами первого блока индикации, а второй выход соединен с первым входом первого элемента ИЛИ и с первым входом второго элемента И, второй вход которого соединен со вторым входом первого элемента ИЛИ и с первым выходом второго дешифратора, вторые выходы которого соединены с входами второго блока индикации, а входы с выходами второго регистра, D-входы которого соединены с выходами первого счетчика, счетный вход которого соединен с выходом второго компаратора и с первым входом второго элемента ИЛИ, второй вход которогб соединен с выходом второго разряда реверсивного счетчика, а выход с S-входом RS-триггера, выход которого соединен через одновибра- тор с входами начальной установки первого,второго, третьего и реверсивного счетчиков, R-вход RS-триггера соединен с входами синхронизации первого, второго и третьего регистров и с выходом второго счетчика, счетный вход которого соединен с выходом генератора и с первым входом третьего элемента И, второй вход которого соединен с выходом элемента ИЛИ-НЕ, первый Фход которогб соединен с выходом первого элемента задержки и с первым входом первого элемента И, второй вход которого соединен со вторым входом элемента ИЛИ-НЕ и с выходом второго элемента задержки, вход которого соединен с выходом первого триггера Шмитта, соединенного

входом со вторым выходом выпрямительного блока, вход которого является входом анализатора, а третий выход соединен со входом второго триггера Шмитта, выход которого соединен со входом первого элемента задержки, выход третьего элемента И соединен со счетным входом третьего счетчика, выходы которого соединены с D-входами третьего регистра, выходы которого

0 соединены со входами третьего дешифратора, первые выходы которого соединены с соответствующими входами третьего блока индикации, а второй выход с третьим входом первого элемента ИЛИ и с третьим вхо5 дом второго элемента И, выход второго элемента И является выходом Авария анализатора и входом первого элемента индикации, а выход первого элемента ИЛИ является выходом Предупреждение анализатора и

0 входом второго элемента индикации.

Отличительными признаками предлагаемого устройства является введение второго триггера Шмитта. второго компаратора, второго и третьего элементов И, элемента

5 НЕ, элемента ИЛИ-НЕ, первого и второго элементов ИЛИ, первого и второго элементов задержки, генератора, первого, второго, третьего и реверсивного счетчиков, первого, второго и третьего дешифраторов, пер0 вого, второго и третьего блоков индикации, первого, второго и третьего регистров, первого и второго элементов индикации, элемента исключающее ИЛИ с их связями с остальными элементами.

5 Введение элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и третьего реверсивного счетчика-с их связями с другими элементами позволило отличать провалы напряжения от переходов через О напряжения сети.

0 Введение первого, второго и третьего дешифраторов с их связями позволило перестраивать пороги.интенсивности соответственно пропажи напряжения, провалов напряжения и всплесков перенапряжения

5 для различных типов электронного оборудования в зависимости от уровня их помехозащищенности.

Введение второго элемента ИЛИ с его связями с остальными элементами позволя0 ет получить информацию о выходе за порог интенсивности по одному из видов помех (пропажа напряжения или провалы напряжения, или всплески перенапряжения). Введение первого элемента индикации

5 позволяет получить сигнал Предупреждение о выходе за порог интенсивности по одному из видов помех.

Введение третьего элемента И с его связями позволяет получить информацию о выходе за порог интенсивности по всем видам

помех для данного типа электронного оборудования.

Введение первого, второго и третьего блоков индикации с их связями позволяет отобразить интенсивность пропаж напря- жения, провалов напряжения и всплесков перенапряжения соответственно.

Введение всех вышеперечисленных блоков анализатора с их связями позволяет провести классификацию действующей в сети помехи за счет анализа интенсивности провалов напряжения, всплесков перенапряжения и пропаж напряжения.

Известные устройства предполагают лишь контроль за отдельными помехами, действующими в электрической сети, и не пригодны для анализа качества сети и классификации действующей в сети помехи.

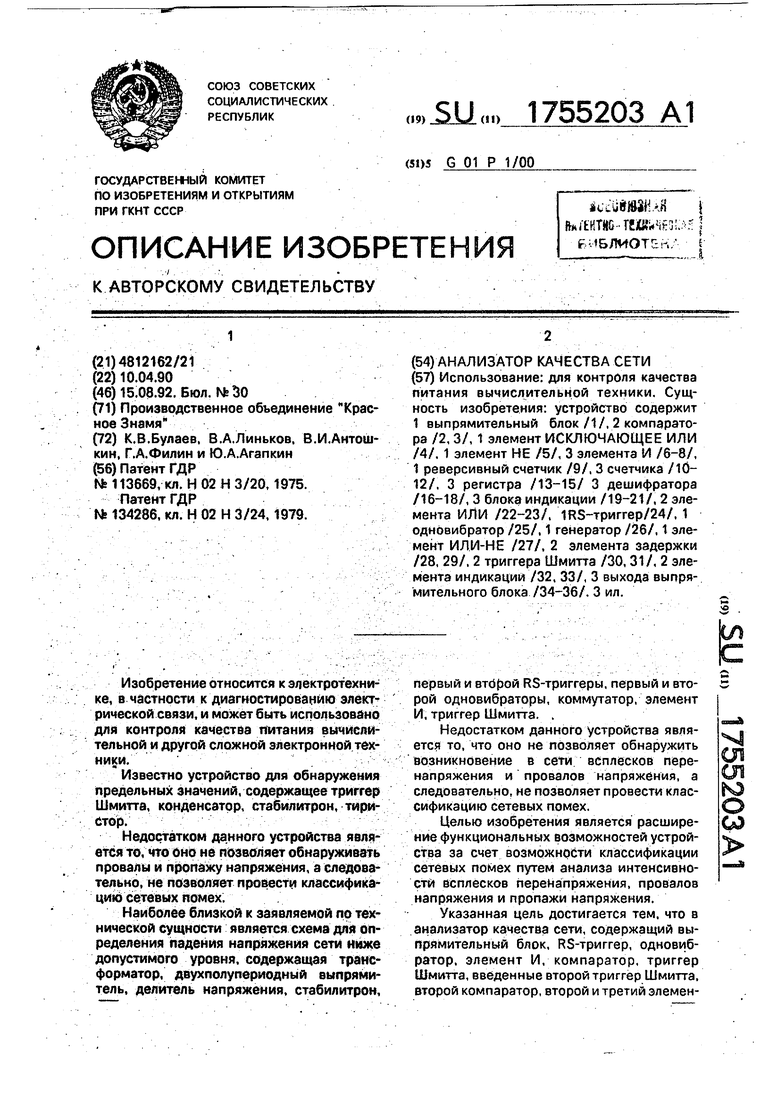

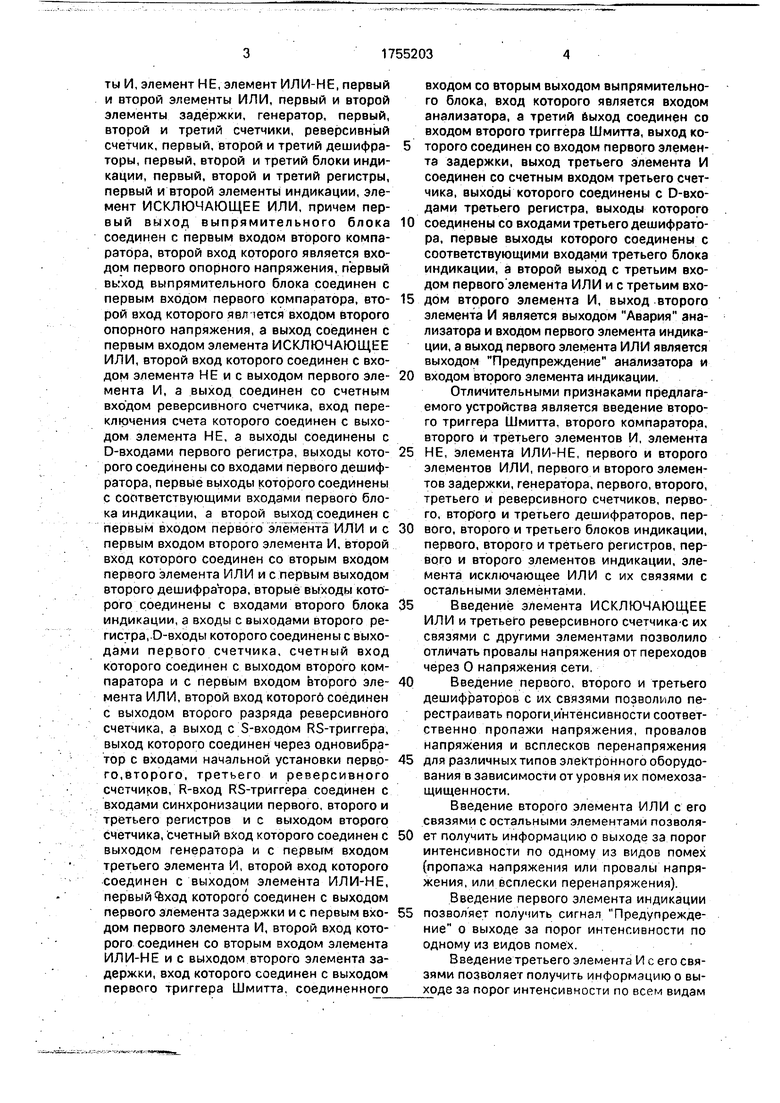

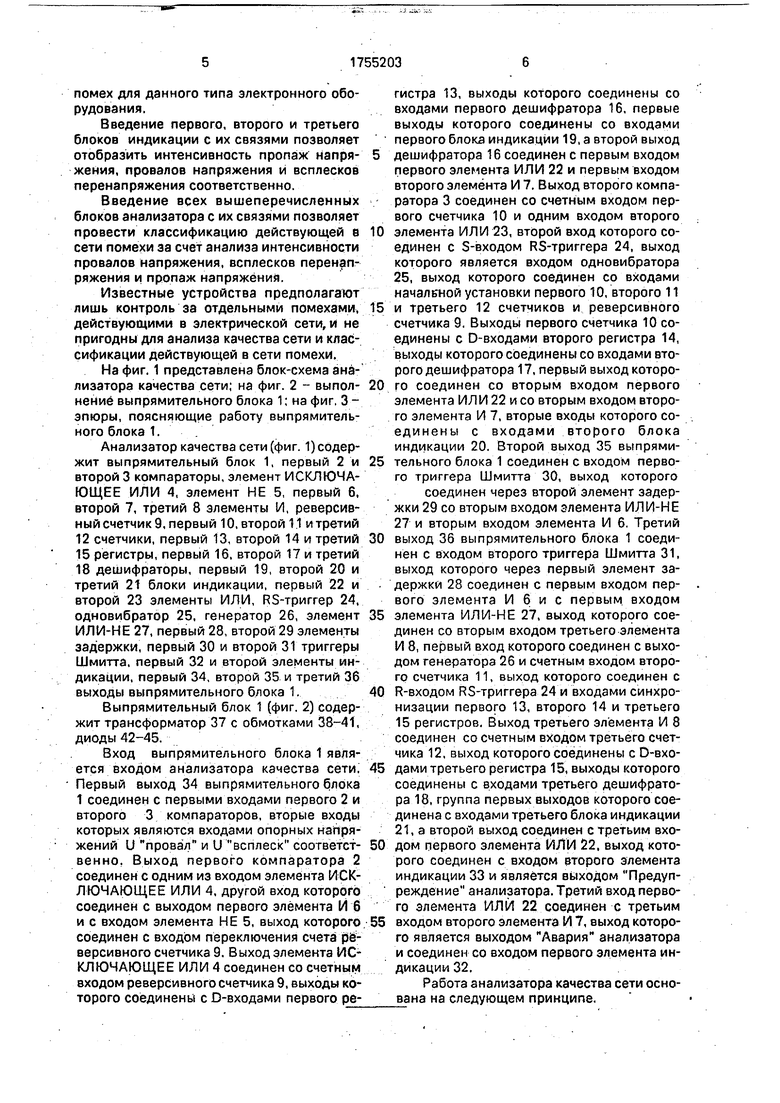

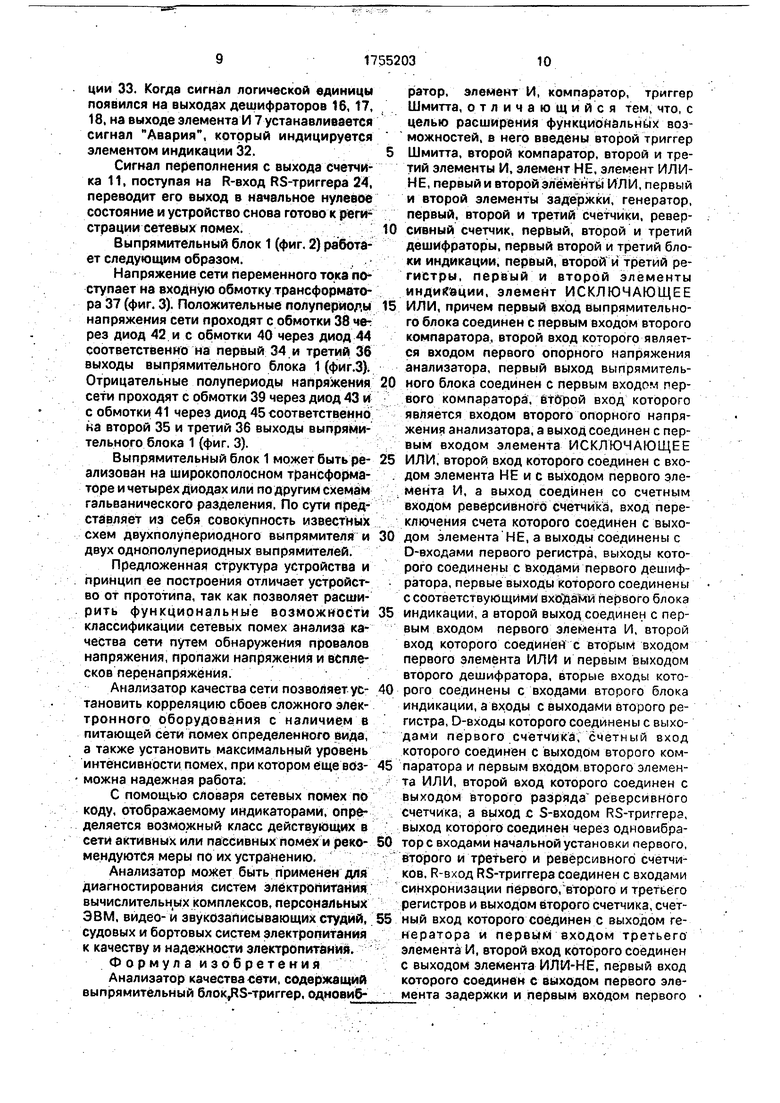

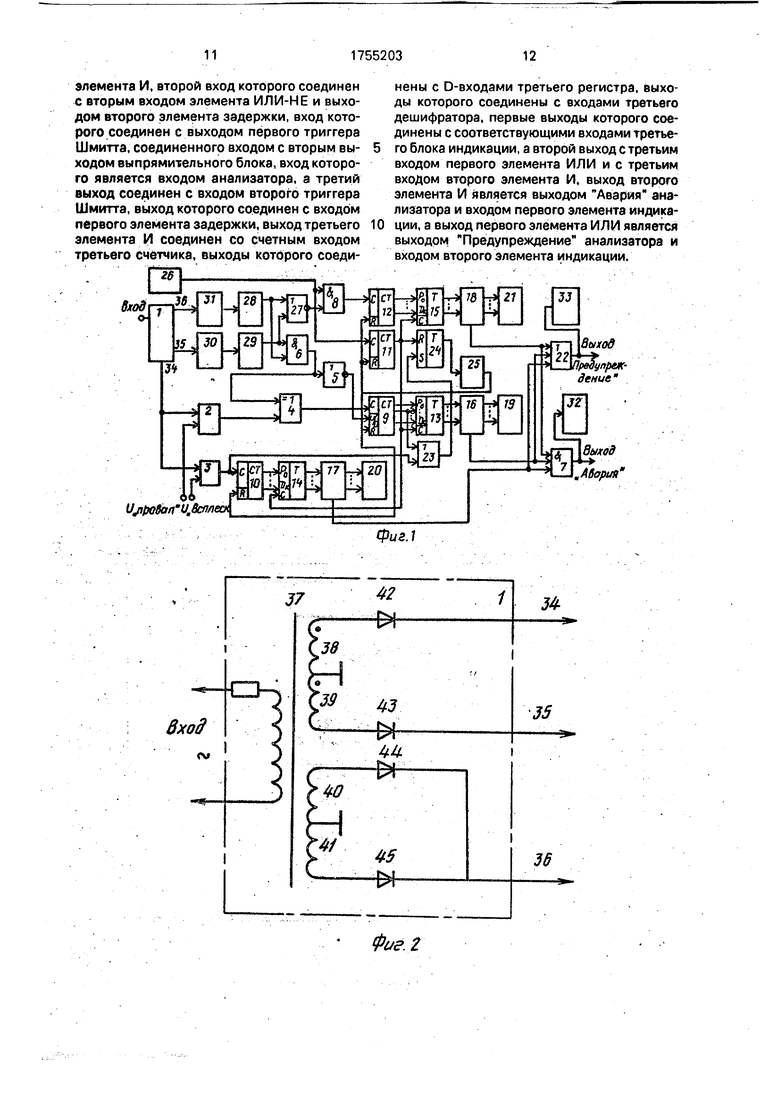

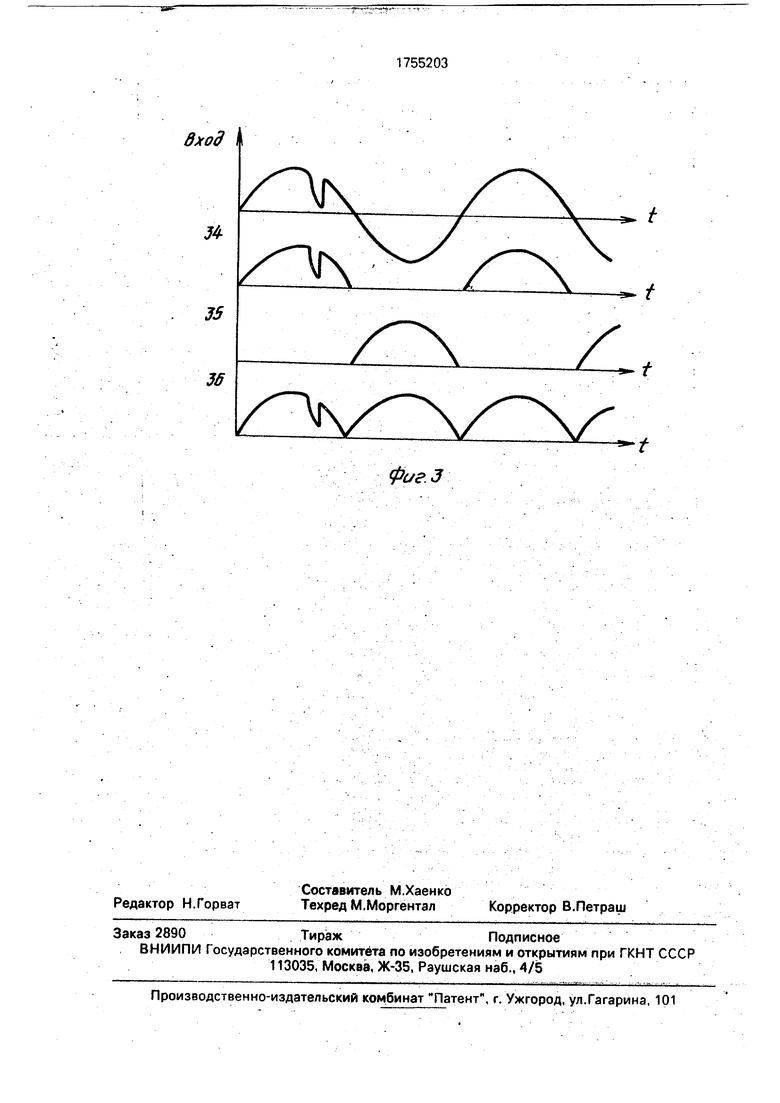

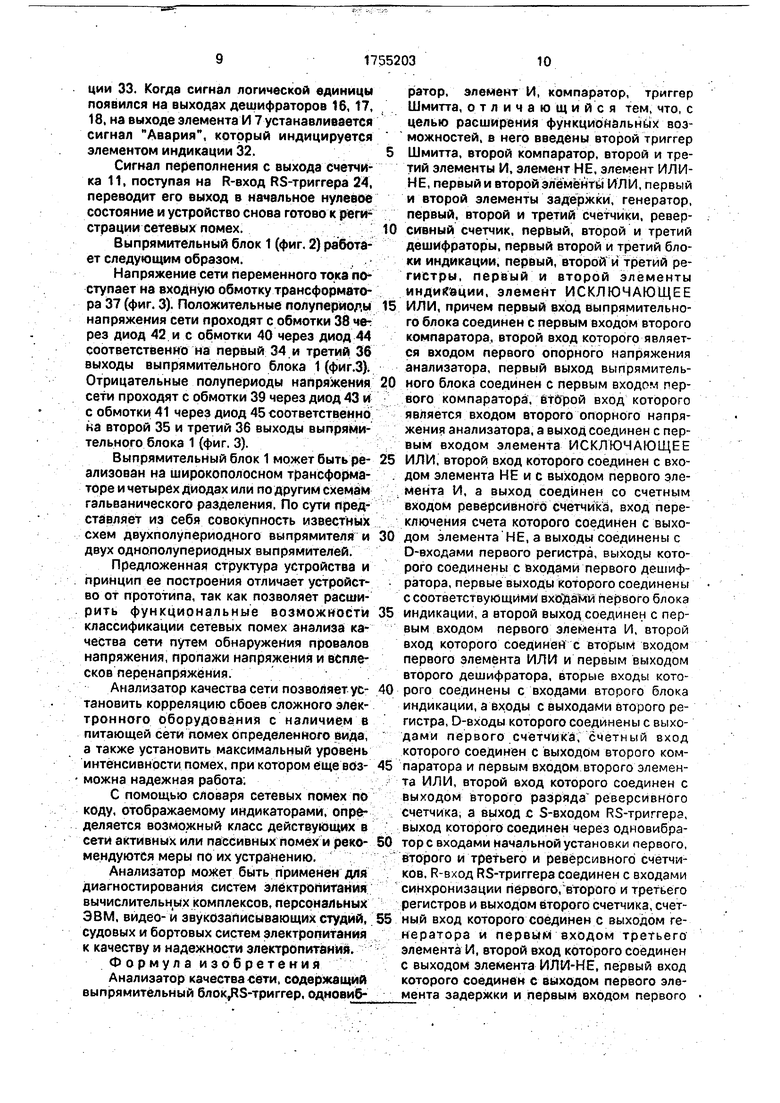

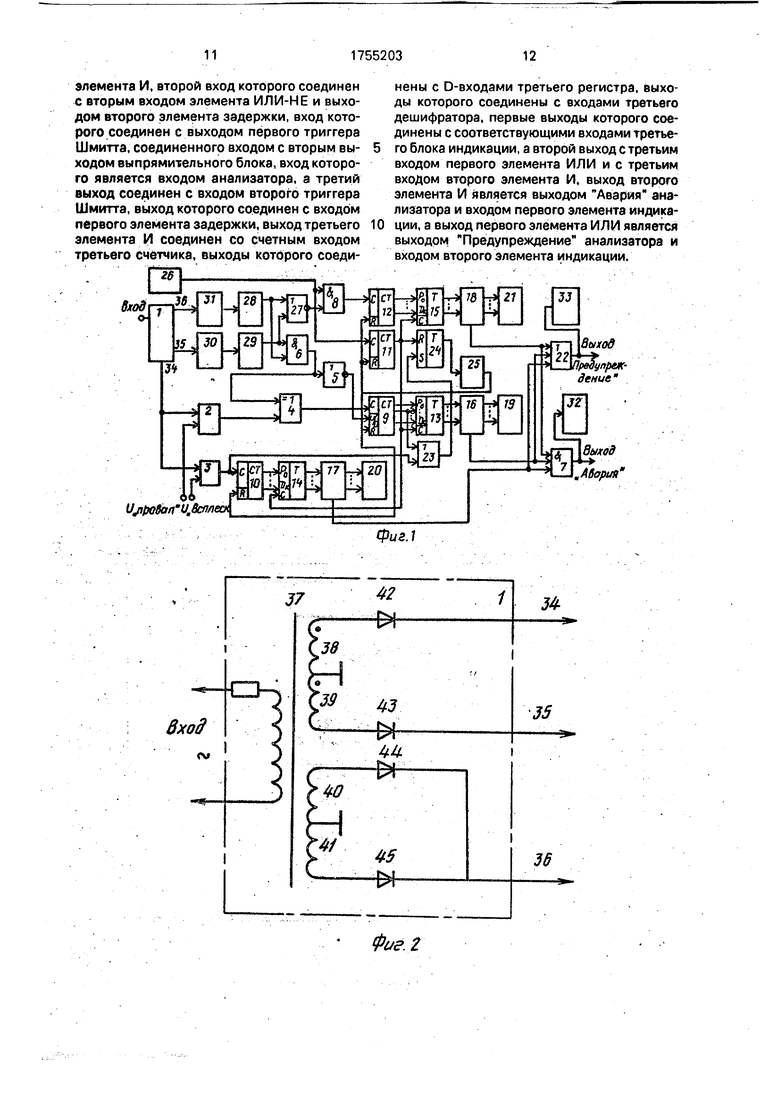

На фиг. 1 представлена блок-схема анализатора качества сети; на фиг. 2 - выпол- нение выпрямительного блока 1; на фиг. 3 - эпюры, поясняющие работу выпрямительного блока 1.

Анализатор качества сети (фиг. содержит выпрямительный блок 1, первый 2 и второй 3 компараторы, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4, элемент НЕ 5, первый 6, второй 7, третий 8 элементы И, реверсивный счетчик 9, первый 10, второй 11 и третий 12 счетчики, первый 13, второй 14 и третий 15 регистры, первый 16, второй 17 и третий 18 дешифраторы, первый 19, второй 20 и третий 21 блоки индикации, первый 22 и второй 23 элементы ИЛИ, RS-триггер 24, одновибратор 25, генератор 26, элемент ИЛИ-НЕ 27, первый 28, второй 29 элементы задержки, первый 30 и второй 31 триггеры Шмитта, первый 32 и второй элементы индикации, первый 34, второй 35 и третий 36 выходы выпрямительного блока 1.

Выпрямительный блок 1 (фиг. 2) содержит трансформатор 37 с обмотками 38-41, диоды 42-45.

Вход выпрямительного блока 1 является входом анализатора качества сети. Первый выход 34 выпрямительного блока 1 соединен с первыми входами первого 2 и второго 3 компараторов, вторые входы которых являются входами опорных напряжений U провал и U всплеск соответст- венно. Выход первого компаратора 2 соединен с одним из входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4, другой вход которого соединен с выходом первого элемента И б и с входом элемента НЕ 5, выход которого соединен с входом переключения счета реверсивного счетчика 9. Выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4 соединен со счетным входом реверсивного счетчика 9, выходы которого соединены с D-входами первого регистра 13, выходы которого соединены со входами первого дешифратора 16, первые выходы которого соединены со входами первого блока индикации 19, а второй выход дешифратора 16 соединен с первым входом первого элемента ИЛИ 22 и первым входом второго элемента И 7. Выход второго компаратора 3 соединен со счетным входом первого счетчика 10 и одним входом второго элемента ИЛИ 23, второй вход которого соединен с S-входом RS-триггера 24, выход которого является входом одновибратора 25, выход которого соединен со входами начальной установки первого 10, второго 11 и третьего 12 счетчиков и реверсивного счетчика 9. Выходы первого счетчика 10 соединены с D-входами второго регистра 14, выходы которого соединены со входами второго дешифратора 17, первый выход которого соединен со вторым входом первого элемента ИЛИ 22 и со вторым входом второго элемента И 7, вторые входы которого со- единены с входами второго блока индикации 20. Второй выход 35 выпрямительного блока 1 соединен с входом первого триггера Шмитта 30, выход которого

соединен через второй элемент задержки 29 со вторым входом элемента ИЛИ-НЕ 27 и вторым входом элемента И 6. Третий выход 36 выпрямительного блока 1 соединен с входом второго триггера Шмитта 31, выход которого через первый элемент задержки 28 соединен с первым входом первого элемента Ибис первым входом элемента ИЛИ-НЕ 27, выход которого соединен со вторым входом третьего элемента И 8, первый вход которого соединен с выходом генератора 26 и счетным входом второго счетчика 11, выход которого соединен с R-входом RS-триггера 24 и входами синхронизации первого 13, второго 14 и третьего 15 регистров. Выход третьего элемента И 8 соединен со счетным входом третьего счетчика 12, выход которого соединены с D-входами третьего регистра 15, выходы которого соединены с входами третьего дешифратора 18, группа первых выходов которого соединена с входами третьего блока индикации 21, а второй выход соединен с третьим входом первого элемента ИЛИ 22, выход которого соединен с входом второго элемента индикации 33 и является выходом Предупреждение анализатора. Третий вход первого элемента ИЛИ 22 соединен с третьим входом второго элемента И 7, выход которого является выходом Авария анализатора и соединен со входом первого элемента индикации 32.

Работа анализатора качества сети основана на следующем принципе.

Действующие в электрической сети помехи делятся на всплески перенапряжения, провалы напряжения и пропажу напряжения, по интенсивности и совокупности который можно отнести действующую в сети помеху к тому или иному классу.

Анализатор качества сети подсчитывает количество, провалов напряжения, времени пропажи напряжения и всплесков перенапряжения за фиксированное время, что по- зволяет по словарю помех отнести действующую в сети помеху к тому или иному классу.

Устройство работает следующим образом.

Перед началом работы каждый дешифратор 16-18 программируется на предельные величины интенсивности, составляющих помехи (всплеска перенапряжения, провала напряжения, пропажи напряжения), вызывающие сбой того или иного электронного оборудования. При включении анализатора обнуляется содержимое счетчиков 10-12 и реверсивного счетчика 9, устанавливается в нулевое со- стояние RS-триггер 24. Эти цепи на чертеже не показаны (последующие циклы обнуления происходят автоматически).

Напряжение сети переменного тока подается на вход выпрямительного блока 1, который служит для гальванической развязки и выпрямления напряжения сети, Выпрямленное напряжение сети с выхода 34 выпрямительного блока 1 поступает на входы компараторов 2 и 3. При возникновении в сети помехи в виде провалов напряжения, пропажи напряжения или всплесков перенапряжения сигналов с выхода второго разряда реверсивного счетчика 9 или сигналом с выхода компаратора 3 на выхо де элемента ИЛИ 23 формируется сигнал логической единицы, который, поступая на S-вход RS- триггсра 24, устанавливает на его выходе сигнал логической единицы. Одновибратор 25 формирует на выходе короткий сигнал начальной установки, который обнуляет содержимое счетчиков 10-12 и реверсивного счетчика 9. Начинается цикл регистрации сетевых помех.

При возникновении в сети всплесков перенапряжения, превышающих опорное напряжение U всплеск, компаратор 3 формирует на выходе сигнал логической единицы, счетЯик 10 срабатывает и увеличивает свое состояние на единицу.

С выхода 36 выпрямительного блока 1 на вход триггера Шмитта 31 подаются только положительные полупериоды напряжения сети. С выхода триггера Шмитта 31 логический сигнал подается на вход элемента задержки 28, который, не изменяя переднего фронта сигнала, задерживает его спад на некоторое время t. Аналогично с выхода 35 выпрямительного блока 1 на вход триггера Шмитта 30 подаются только отрицательные полупериоды напряжения сети. С выход триггера Шмитта 30 логический сигнал поступает на вход элемента задержки 29, который задерживает спад этого сигнала на время t. При исчезновении напряжения сети на время, большее t, на выходе элемента ИЛИ-НЕ 27 устанавливается сигнал логической единицы, который разрешает прохождение с генератора 26 тактовых импульсов на счетный вход счетчика 12. При этом счетчик 12 устанавливает свое состояние. Элемент И 6 и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4 служат для отличия провалов напряжения от переходов через ноль напряжения сети. Элемент НЕ 5 служит для инверсии сигнала с выхода элемента И 6 и для повышения устойчивости работы.

При опускании напряжения сети ниже опорного напряжения U провал на выходе компаратора формируется сигнал логической единицы. Если этот сигнал совпал по времени с сигналом логической единицы на. выходе элемента И 6, то это означает, что напряжение сети в данный момент времени переходит с отрицательного полупериода на положительный или наоборот. В этом случае на счетный вход реверсивного счетчика 9 поступают два импульса так, что передний фронт второго импульса совпадает с сигналом логической единицы на входе переключения счета реверсивного счетчика 9. Реверсивный счетчик 9 сначала увеличивает свое состояние на 1, а потом на 1 уменьшает, т.е. фактически не изменяет свое состояние.

Если возник провал напряжения, то реверсивный счетчик 9 просто увеличивает свое состояние на 1.

Окончание цикла регистрации сетевых помех осуществляется в момент переполнения счетчика 11, который производит счет тактовых импульсов. Сигнал переполнения поступает на синхронизирующие входы регистров 13-15, которые устанавливают на своих выходах логические уровни, соответствующие входам счетчика 12, реверсивного счетчика 9, счетчика 10 соответственно. С групп выходов дешифраторов 18, 16, Пин- формация отображается блоками индикации 21, 19, 20 соответственно. В случае появления на одном или нескольких выходах дешифраторов 18, 16, 17 сигнала логической единицы на выходе элемента ИЛИ 22 устанавливается сигнал Предупреждение, который индицируется элементом индикации 33. Когда сигнал логической единицы появился на выходах дешифраторов 16, 17, 18, на выходе элемента И 7 устанавливается сигнал Авария, который индицируется элементом индикации 32.

Сигнал переполнения с выхода счетчика 11, поступая на R-вход RS-триггера 24, переводит его выход в начальное нулевое состояние и устройство снова готово к регистрации сетевых помех.

Выпрямительный блок 1 (фиг. 2) работает следующим образом.

Напряжение сети переменного тока поступает на входную обмотку трансформатора 37 (фиг. 3). Положительные полупериоды напряжения сети проходят с обмотки 38 через диод 42 и с обмотки 40 через диод 44 соответственно на первый 34 и третий 36 выходы выпрямительного блока 1 (фиг.З). Отрицательные полупериоды напряжения сети проходят с обмотки 39 через диод 43 и с обмотки 41 через диод 45 соответственно на второй 35 и третий 36 выходы выпрямительного блока 1 (фиг. 3).

Выпрямительный блок 1 может быть ре- ализован на широкополосном трансформаторе и четырех диодах или по другим схемам гальванического разделения. По сути представляет из себя совокупность известных схем двухлолупериодного выпрямителя и двух однополупериодных выпрямителей.

Предложенная структура устройства и принцип ее построения отличает устройство от прототипа, так как позволяет расширить функциональные возможности классификации сетевых помех анализа качества сети путем обнаружения провалов напряжения, пропажи напряжения и всплесков перенапряжения.

Анализатор качества сети позволяет ус- тановить корреляцию сбоев сложного элек- тронного оборудования с наличием в питающей сети помех определенного вида, а также установить максимальный уровень интенсивности помех, при котором еще воз- можна надежная работа.

С помощью словаря сетевых помех по коду, отображаемому индикаторами, определяется возможный класс действующих в сети активных или пассивных помех и реко- мендуютСя меры по их устранению.

Анализатор может быть применен для диагностирования систем электропитания вычислительных комплексов, персональных ЭВМ, видео- и звукозаписывающих студий, судовых и бортовых систем электропитания к качеству и надежности электропитания.

Формула изобретения

Анализатор качества сети, содержащий выпрямительный блок З-триггер, одновибратор, элемент И, компаратор, триггер Шмитта, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены второй триггер Шмитта, второй компаратор, второй и третий элементы И, элемент НЕ, элемент ИЛИ- НЕ, первый и второй элементы ИЛИ, первый и второй элементы задержки, генератор, первый, второй и третий счетчики, реверсивный счетчик, первый, второй и третий дешифраторы, первый второй и третий блоки индикации, первый, второй и третий регистры, первый и второй элементы индикации, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем первый вход выпрямительного блока соединен с первым входом второго компаратора, второй вход которого является входом первого опорного напряжения анализатора, первый выход выпрямительного блока соединен с первым входом первого компаратора, втброй вход которого является входом второго опорного напряжения анализатора, а выход соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с входом элемента НЕ и с выходом первого элемента И, а выход соединен со счетным входом реверсивного счетчика, вход переключения счета которого соединен с выходом элемента НЕ, а выходы соединены с D-входами первого регистра, выходы которого соединены с входами первого дешифратора, первые выходы которого соединены с соответствующими входами первого блока индикации, а второй выход соединен с первым входом первого элемента И, второй вход которого соединен с вторым входом первого элемента ИЛИ и первым выходом второго дешифратора, вторые входы которого соединены с входами второго блока индикации, а входы с выходами второго регистра, D-входы которого соединены с выходами первого счетчика, счетный вход которого соединен с выходом второго компаратора и первым входом второго элемента ИЛИ, второй вход которого соединен с выходом второго разряда реверсивного счетчика, а выход с S-входом RS-триггера, выход которого соединен через одновибра- торс входами начальной установки первого, второго и третьего и реверсивного счетчиков, R-вход RS-триггера соединен с входами синхронизации первого, второго и третьего регистров и выходом второго счетчика, счетный вход которого соединен с выходом генератора и первым входом третьего элемента И, второй вход которого соединен с выходом элемента ИЛИ-НЕ, первый вход которого соединен с выходом первого элемента задержки и первым входом первого

элемента И, второй вход которого соединен с вторым входом элемента ИЛИ-НЕ и выходом второго элемента задержки, вход которого соединен с выходом первого триггера Шмитта, соединенного входом с вторым выходом выпрямительного блока, вход которого является входом анализатора, а третий выход соединен с входом второго триггера Шмитта, выход которого соединен с входом первого элемента задержки, выход третьего элемента И соединен со счетным входом третьего счетчика, выходы которого соеди аГ

0

нены с D-входами третьего регистра, выходы которого соединены с входами третьего дешифратора, первые выходы которого соединены с соответствующими входами третьего блока индикации, а второй выход с третьим входом первого элемента ИЛИ и с третьим входом второго элемента И, выход второго элемента И является выходом Авария анализатора и входом первого элемента индикации, а выход первого элемента ИЛИ является выходом Предупреждение анализатора и входом второго элемента индикации.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ОПРЕДЕЛЕНИЯ ВРЕМЕНИ ВОЗНИКНОВЕНИЯ ПРЕДПОЖАРНОЙ СИТУАЦИИ ОТ ИСКРЕНИЯ В ЭЛЕКТРИЧЕСКОЙ СЕТИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2005 |

|

RU2309461C1 |

| Статистический анализатор выбросов и провалов напряжения | 1990 |

|

SU1837325A1 |

| Анализатор длительности выбросов и провалов напряжения | 1988 |

|

SU1674156A1 |

| МНОГОМЕРНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ВЫБРОСОВ И ПРОВАЛОВ НЕСТАЦИОНАРНОГО НАПРЯЖЕНИЯ | 2000 |

|

RU2189631C2 |

| МНОГОУРОВНЕВЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ДЛИТЕЛЬНОСТИ ВЫБРОСОВ И ПРОВАЛОВ НАПРЯЖЕНИЯ | 1991 |

|

RU2054195C1 |

| Устройство измерения отклонения сопротивления от заданного значения | 1990 |

|

SU1737360A1 |

| Следящий аналого-цифровой преобразователь | 1985 |

|

SU1283971A1 |

| Устройство для подсчета пассажиров транспортного средства | 1987 |

|

SU1441427A2 |

| Устройство для выдачи команд об изменении движения транспорта | 1986 |

|

SU1446640A1 |

| Преобразователь угла поворота вала в код | 1982 |

|

SU1020845A1 |

Использование: для контроля качества питания вычислительной техники. Сущность изобретения: устройство содержит 1 выпрямительный блок/1/, 2 компаратора /2, 3/, 1 элемент ИСКЛЮЧАЮЩЕЕ ИЛИ /4/, 1 элемент НЕ /5/, 3 элемента И /6-8/, 1 реверсивный счетчик /9/, 3 счетчика /10- 12/, 3 регистра /13-15/ 3 дешифратора /16-18/, 3 блока индикации /19-21/, 2 элемента ИЛИ /22-23/, 1К8-триггер/24/, 1 одновибратор/25/.1 генератор/26/, 1 элемент ИЛИ-НЕ /27/, 2 элемента задержки /28, 29/, 2 триггера Шмитта /30,31/, 2 элемента индикации /32, 33/, 3 выхода выпрямительного блока /34-36/. 3 ил.

J7

Вход

42

-БИЯ

35

45

-Ј

36

Фие.2

вход

J4

35

t

фигЗ

| Способ определения в органических соединениях серы и галоидов (хлора, брома, йода) и прибор для его осуществления | 1955 |

|

SU113669A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ регистрации характеристических моментов модуляции телеграфных сигналов на экране электронно-лучевой трубки | 1960 |

|

SU134286A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1992-08-15—Публикация

1990-04-10—Подача