Изобретение относится к вьмислительной технике, предназначено для вьпшсления логарифма чисел, представленных параллельным двоичным кодом, может быть использовано, например, в технологических (специальных) электронных расчетных машинах, предназначенных для нормирования и выбора режимов резания металлообрабатывающих станков, и является усовершенствованием известного устройства по авт.св.№1156067.

Цель изобретения является расширение функциональных возможностей устройства за счет дополнительной возможности вычисления натурального логарифма.

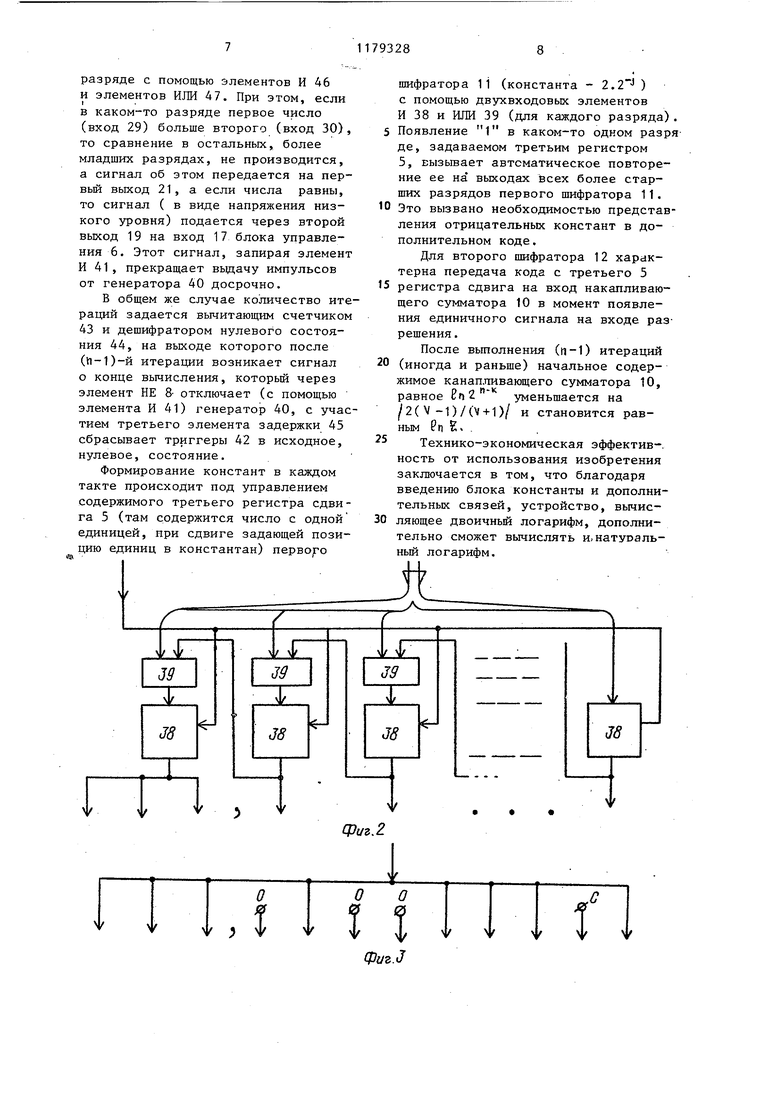

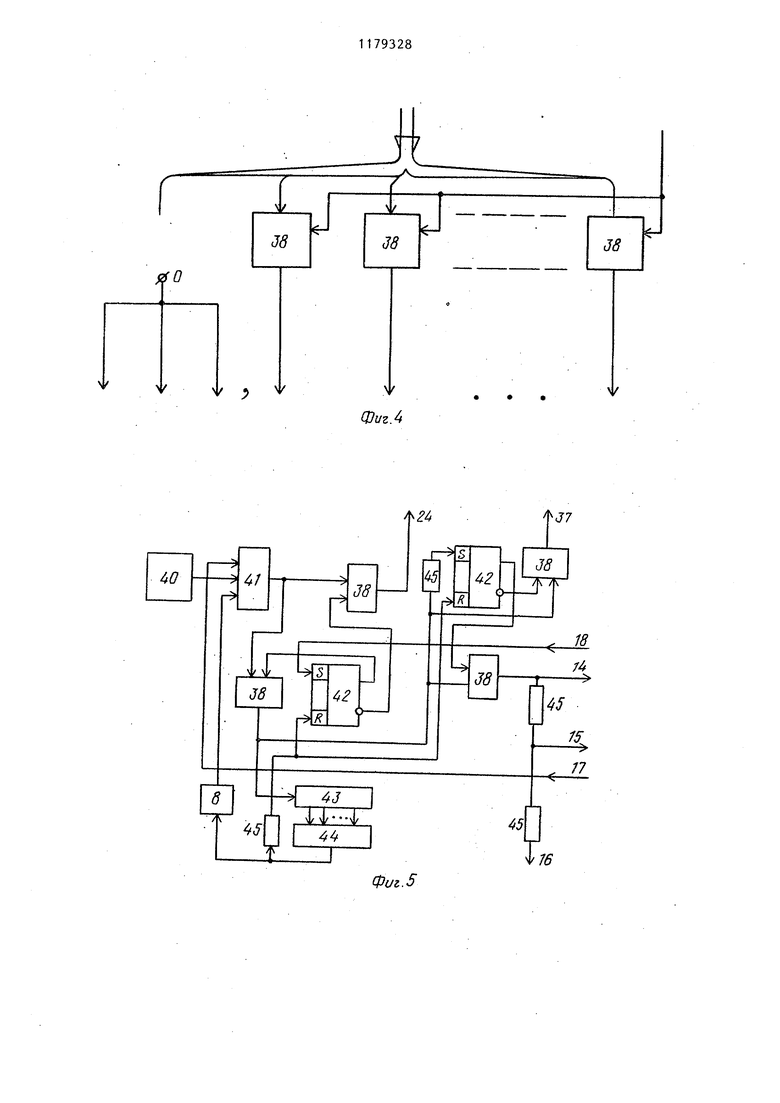

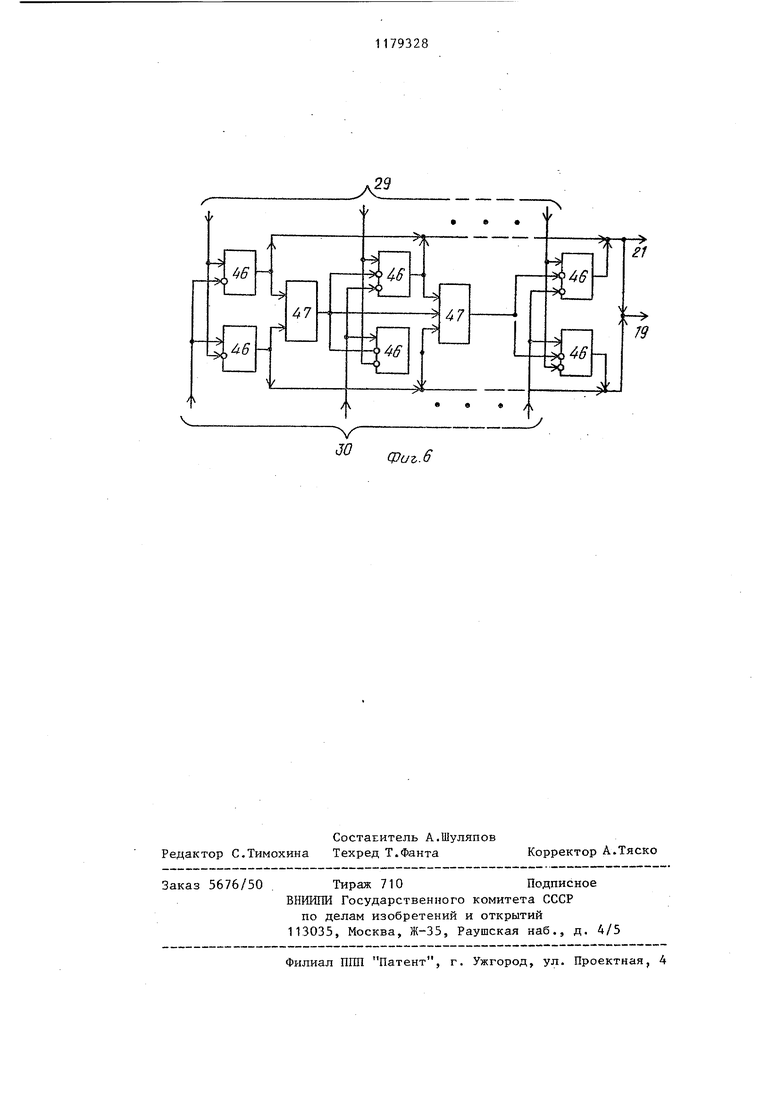

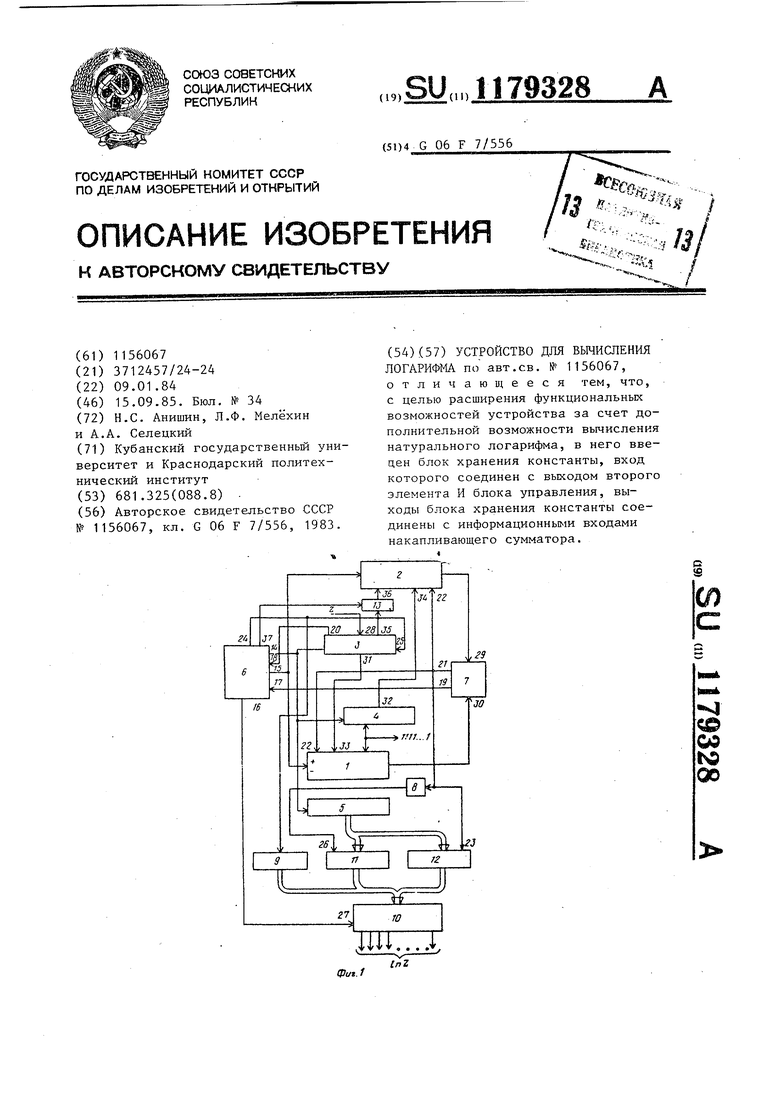

На фиг. 1 представлена блок-схем устройства для вьиисления логарифма; на фиг. 2-6 - принципиальные схемы соответственно первого шифратора, блока константы, второго шифратора, блока управления и блока сравнения.

Устройство для вычисления логарифма (фиг. 1) содержит первый и второй сумматоры-вычитатели 1 и 2, первьй, второй и третий регистры 3-5 сдвига, блок управления 6, блок сравнения 7, элемент НЕ 8, блок хранения константы 9, накапливающий сумматор 10, первый и второй шифраторы 11 и 12, группу . элементов И 13, причем первый 14 выход блока управления 6 связан со входами сдвига вправо всех регистров 3-5 сдвига, второй выход 15 блока управления 6 соединен с входо синхронизации обоих сумматоров-вычитателей 1 и 2, третий выход 16 блока управления 6 соединен с входо синхронизации накапливающего сумматора 10, первьй 17 и второй 18 вход блока управления 6 соединены со вторым 19 вькодом блока сравнения 7 и с выходом 20 старшего разряда первого регистра сдвига 3 соответственно. Первьй выход 21 блока сравнения 7 связан со входами 22 режима работы (сложение или вычитание) обоих сумматоров-вычитателей 1 и 2, а также со входом элемента НЕ 8 и с разрешающим входом 23 второго шифратора 12. Четвертый выход 24 блока управления 6 связан со входом 25 сдвига влево первого регистра сдвига 3.

Вход блока хранения константы 9 связан с четвертым выходом 24 блока управления 6. Выход-элемента НЕ 8 соединен с разрешавшем входом 26 первого шифратора 11. Выходы блока константы 9, первого 11 и второго 12 шифраторов поразрядно объединены логически (логическое монтажное ИЛИ и поданы на вход накапливающего сумматора 10, работающего в дополнительном коде. Синхронизация его работы осуществляется по входу 27, связанному с третьим выходом 16 блока управления 6.

Входом устройства является вход 28 первого регистра 3 сдвига, куда заносится целое двоичное число Z .

Кроме того, входы 29 и 30 блока сравнения 7 связаны с выходами второго 2 и первого 1 сумматороввычитателей. Выходы 31 и 32 первого и второго регистров сдвига 3 и 4 связаны со входами 33 и 34 сложения одноименных сумматоров-вычитателей 1 и 2. Выход 35 первого регистра сдвига 3 соединен со входом 36 нанесения второго сумматора-вычитателя через группу элементов И 13, вход управления которой связан с пятьм выходом 37 блока управления 6

Первьй 11 (фиг. 2) и второй 12 (фиг. 4) шифраторы содержат по одному двухвходовому элементу И 38 на каждьй разряд. В первом шифратор 11, кроме того, есть по одному двухвходовому элементу ИЛИ 39 на каждый разряд (кроме младшего), выход которого связан со входом элемента И 38, а взводы которого образованы разрядным входом группы элементов И и выходом элементов И 3 предыдущего, более младшего разряда При этом выходы трех старших разрядов (старшая часть логарифма) продублированы от выхода одного элемента И (для первого) и от нулевой шины (для второго шифратора).

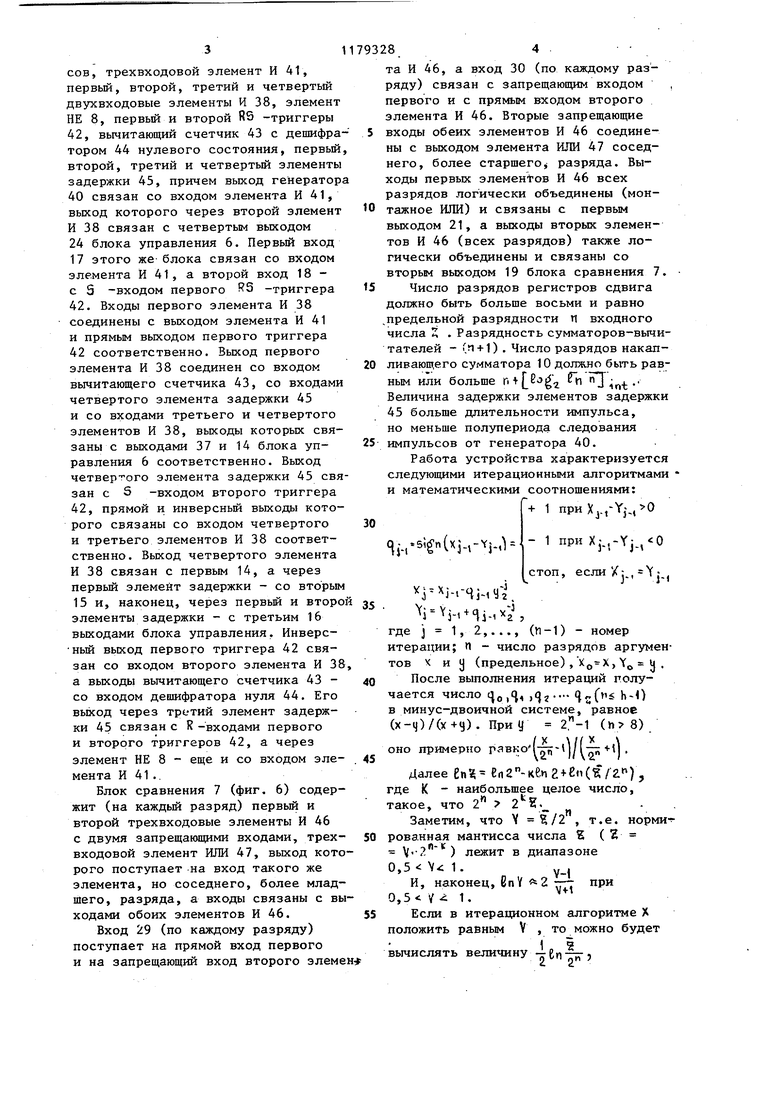

Блок 9 (фиг. 3) представляет собой кондуктивньй многополюсник с одним входом и несколькими (разрядными) выходами, причем разряды целой части логарифма, а также второй, пятьй, шестой, седьмой и девятьй (после запятой) разряды дробной части соединены со входом блока 9, а остальные - с уровнем О.

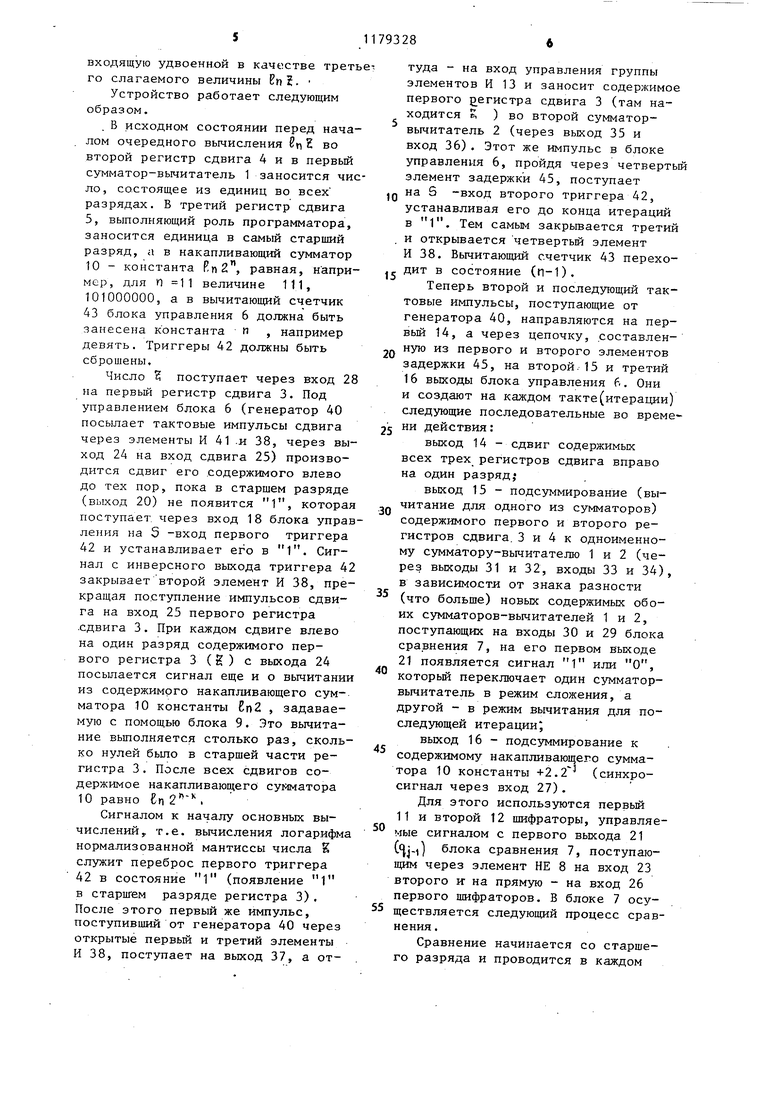

Блок управления 6 (фиг. 5) содержит генератор 40 тактовых импульсов, трехвходовой элемент И 41, первый, второй, третий и четвертый двухвходовые элементы И 38, элемент НЕ 8, первый и второй RS -триггеры 42, вычитающий счетчик 43 с дешифра тором 44 нулевого состояния, первьй второй, третий и четвертьй элементы задержки 45, причем выход генератор 40 связан со входом элемента И 41, выход которого через второй элемент И 38 связан с четвертым выходом 24 блока управления 6. Первый вход 17 этого же блока связан со входом элемента И 41, а второй вход 18 с 3 -входом первого -триггера 42. Входы первого элемента И 38 соединены с выходом элемента И 41 и прямым выходом первого триггера 42 соответственно. Выход первого элемента И 38 соединен со входом вычитающего счетчика 43, со входами четвертого элемента задержки 45 и со входами третьего и четвертого элементов И 38, выходы которых связаны с выходами 37 и 14 блока управления 6 соответственно. Выход четвертого элемента задержки 45 связан с S -входом второго триггера 42, прямой и инверсный выходы которого связаны со входом четвертого и третьего элементов И 38 соответственно. Выход четвертого элемента И 38 связан с первым 14, а через первьй элемейт задержки - со вторым 15 и, наконец, через первьй и второ элементы задержки - с третьим 16 выходами блока управления. Инверсньй выход первого триггера 42 связан со входом второго элемента И 38 а выходы вычитающего счетчика 43 со входом дешифратора нуля 44. Его выход через третий элемент задержки 45 связан с R-входами первого и второго триггеров 42, а через элемент НЕ 8 - еще и со входом элемента И 41 ..

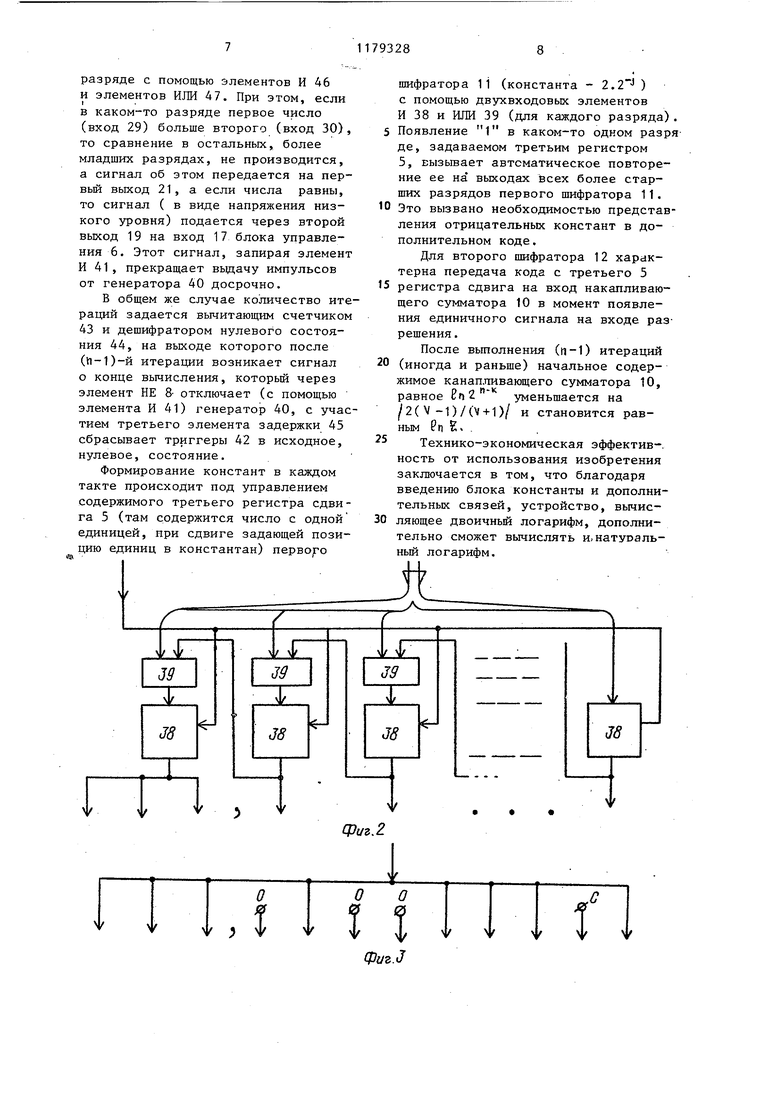

Блок сравнения 7 (фиг. 6) содержит (на каждьй разряд) первый и второй трехвходовые элементы И 46 с двумя запрещающими входами, трехвходовой элемент ИЛИ 47, выход которого поступает на вход такого же элемента, но соседнего, более младщего, разряда, а входы связаны с выходами обоих элементов И 46.

Вход 29 (по каждому разряду) поступает на прямой вход первого и на запрещающий вход второго элеме

та И 46, а вход 30 (по каждому разряду) связан с запрещающим входом первого и с прямым входом второго элемента И 46. Вторые запрещающие входы обеих элементов И 46 соединены с выходом элемента ИЛИ 47 соседнего, более старшегоj разряда. Выходы первых элементов И 46 всех разрядов логически объединены (монтажное ИЛИ) и связаны с первым выходом 21, а выходы вторых элементов И 46 (всех разрядов) также логически объединены и связаны со вторым выходом 19 блока сравнения 7.

Число разрядов регистров сдвига должно быть больше восьми и равно ,предельной разрядности И входного числа . Разрядность сумматоров-вычитателей - (я + 1) . Число разрядов накапливающего сумматора 10 должно быть равным или больше fn 3in-fc Величина задержки элементов задержки 45 больше длительности импульса, но меньше полупериода следования импульсов от генератора 40.

Работа устройства характеризуется следующими итерационными алгоритмами и математическими соотношениями:

+ 1 пpиXj.,-VJ,0

JMC(

- 1 при Xj-..-Yj.,0 стоп, если/- 4ч-J

r i-t-4H42

j YHMi-,;S

где j 1,2,..., (M-l) - номер итерации; П - число разрядов аргументов X и у (предельное) ,Хо Х, YO tj .

После выполнения итераций получается число (jo,q, ,5,--tsO Ь-0 в минус-двоичной системе, равное (х-ч)/(х+ч). При у 2,-1 ()

/X / у оно примерно равко|- - |Д--;;+1| .

Далее «55 .h г + Й(€/г) , где К - наибольшее целое число, такое, что 2 2 .

Заметим, что V /2 , т.е. нормированная мантисса числа S (Z - V- ) лежит в диапазоне 0,. у,

И, наконец, ВпУ 2 rj-r при 0,5 V 1.

Если в итерационном алгоритме X положить равным V , то можно будет

1 i

вычислять величину - ,

входящую удвоенной в качестве третьго слагаемого величины Еп.

Устройство работает следующим образом.

В исходном состоянии перед началом очередного вычисления бп Н во второй регистр сдвига 4 и в первый сумматор-вычитатель 1 заносится число, состоящее из единиц во всех разрядах. В третий регистр сдвига 5, выполняющий роль программатора, заносится единица в самый старший разряд, а в накапливающий сумматор 10 - константа Rn2, равная, например, для П 11 величине 111, 101000000, а в вычитающий счетчик 43 блока управления 6 должна быть занесена константа п , например девять. Триггеры 42 должны быть сброшены.

Число поступает через вход 28 на первый регистр сдвига 3. Под управлением блока 6 (генератор 40 посылает тактовые импульсы сдвига через элементы И 41 .и 38, через выход 24 на вход сдвига 25) производится сдвиг его содержимого влево до тех пор, пока в старшем разряде (выход 20) не появится 1, которая поступает через вход 18 блока управления на 5 -вход первого триггера 42 и устанавливает его в 1. Сигнал с инверсного выхода триггера 42 закрывает второй элемент И 38, прекращая поступление импульсов сдвига на вход 25 первого регистра .сдвига 3. При каждом сдвиге влево на один разряд содержимого первого регистра 3 (Н ) с выхода 24 посылается сигнал еще и о вычитании из содержимого накапливающего сумматора 10 константы Еп2 , задаваемую с помощью блока 9. Это вычитание вьшолняется столько раз, сколько нулей было в старшей части регистра 3. После всех сдвигов содержимое накапливающего сумматора 10 равно п .

Сигналом к началу основных вычислений т.е. вычисления логарифма нормализованной мантиссы числа К служит переброс первого триггера 42 в состояние 1 (появление 1 в старшем разряде регистра 3) , После этого первый же импульс, поступивший от генератора 40 через открытые первый и третий элементы И 38, поступает на вькод 37, а оттуда - на вход управления группы элементов И 13 и заносит содержимое первого регистра сдвига 3 (там находится fc, ) во второй сумматорвычитатель 2 (через выход 35 и вход 36). Этот же импульс в блоке управления 6, пройдя через четвертью элемент задержки 45, поступает g на 6 -вход второго триггера 42, устанавливая его до конца итераций в 1. Тем самым закрывается третий и открывается четвертьй элемент И 38. Вычитающий счетчик 43 переходит в состояние (п-1).

Теперь второй и последующий тактовые импульсы, поступающие от генератора 40, направляются на первый 14, а через цепочку, составленQ ную из первого и второго элементов задержки 45, на второй.15 и третий 16 выходы блока управления 6. Они и создают на каждом такте(итерации) следующие последовательные во времени действия:

выход 14 - сдвиг содержимых всех трех регистров сдвига вправо на один разряд,

выход 15 - подсуммирование (вы- читание для одного из сумматоров) содержимого первого и второго регистров сдвига. 3 и 4 к одноименному сумматору-вычитателю 1 и 2 (через выходы 31 и 32, входы 33 и 34), в зависимости от знака разности (что больше) новых содержимых обоих сумматоров-вычитателей 1 и 2, поступающих на входы 30 и 29 блока сравнения 7, на его первом выходе 21 появляется сигнал 1 или О, которьй переключает один сумматорвычитатель в режим сложения, а другой - в режим вычитания для последующей итерации

выход 16 - подсуммирование к содержимому накапливающего сумматора 10 константы +2.2 (синхросигнал через вход 27).

Для этого используются первьй 11 и второй 12 пшфраторы, управляемые сигналом с первого выхода 21 (;,,) блока сравнения 7, поступаю1ЦИМ через элемент НЕ 8 на вход 23 второго и- на прямую - на вход 26 первого шифраторов. В блоке 7 осуществляется следующий процесс сравнения .

Сравнение начинается со старшего разряда и проводится в каждом

разряде с помощью элементов И 46 и элементов ИЛИ 47. При этом, если в каком-то разряде первое число (вход 29) больше второго (вход 30), то сравнение в остальных, более младших разрядах, не производится, а сигнал об этом передается на первьй выход 21, а если числа равны, то сигнал ( в виде напряжения низкого уровня) подается через второй выход 19 на вход 17 блока управления 6. Этот сигнал, запирая элемент И 41, прекращает вьщачу импульсов от генератора 40 досрочно.

В общем же случае количество итераций задается вычитающим счетчиком 43 и дешифратором нулевого состояния 44, на выходе которого после (11-1)-й итерации возникает сигнал о конце вычисления, который через элемент НЕ 8- отключает (с помощью элемента И 41) генератор 40, с участием третьего элемента задержки 45 сбрасывает триггеры 42 в исходное, нулевое, состояние.

Формирование констант в каждом такте происходит под управлением содержимого третьего регистра сдвига 5 (там содержится число с одной единицей, при сдвиге задающей позицию единиц в константан) перво :о

шифратора 11 (константа - 2. ) с помощью двухвходовьк элементов И 38 и ИЛИ 39 (для каждого разряда). 5 Появление 1 в каком-то одном разря де, задаваемом третьим регистром 5, Еызьтает автоматическое повторение ее на выходах всех более старших разрядов первого шифратора 11. 0 Это вызвано необходимостью представления отрицательных констант в дополнительном коде.

Для второго шифратора 12 характерна передача кода с третьего 5 5 регистра сдвига на вход накапливающего сумматора 10 в момент появления единичного сигнала на входе разрешения .

После выполнения (n-l) итераций (иногда и раньше) начальное содержимое канап-пивающего сумматора 10, равное 8п 2 уменьшается на 2( V-1)/(V+1)/ и становится равным Рп К .

Технико-экономическая эффективность от использования изобретения заключается в том, что благодаря введению блока константы и дополнительных связей, устройство, вычис- ляющее двоичный логарифм, дополнительно сможет вычислять и, натуоальный логарифм.

.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМА | 1991 |

|

RU2006916C1 |

| Цифровой функциональный преобразователь Анишина | 1983 |

|

SU1157543A1 |

| Цифровой функциональный преобразователь (его варианты) | 1981 |

|

SU1019443A1 |

| Устройство для извлечения квадратного корня | 1985 |

|

SU1259257A1 |

| Цифровой функциональный преобразователь | 1984 |

|

SU1188750A1 |

| Преобразователь координат | 1988 |

|

SU1566345A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ arctg(y/x) | 2015 |

|

RU2595486C1 |

| Устройство для вычисления тангенса | 1984 |

|

SU1187162A1 |

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМА по авт.св. № 1156067, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет дополнительной возможности вычисления натурального логарифма, в него ввецен блок хранения константы, вход которого соединен с выходом второго элемента И блока управления, выходы блока хранения константы соединены с информационными входами накапливающего сумматора. С ч О9 tsd 00

Фиг.

Фиг А

Фиг. 5

х

лг

Фаг.6

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-15—Публикация

1984-01-09—Подача