Изобретение относится к моделированию технологических процессов обогащения полезных ископаемых и может быть использовано в качестве приставки к вычислительной машине при проведении исследований разделительных операций в реальном масштабе времени.

Цель изобретения - расширение функциональных возможностей путем воспроизведения значений дискретно заданной сепарационной характеристики разделительной операции процесса обогащения полезных ископаемых в реальном масштабе времени.

Устройство для моделирования разделительной операции процесса обогащения полезных ископаемых по дискретной сепарационной характеристике (фиг, 1) содержит генератор 1 случайных чисел, выход которого подключен к первой выходной шине всего устройства, к первому входу блока 2 вычисления текущего значения сепарационной характеристики, к первому входу схемы 3 сравнения и через дешифратор 4 - к установочному входу счетчика 5 адреса.

Дешифратор 4 преобразует многорйз- рядное число на своем входе в одиночный импульс на выходе. Выход счетчика 5 адреса подключен к информационному входу коммутатора 6 и первому входу схемы 7 сравнения. Второй вход схемы 7 сравнения соединен с выходом регистра 8 адреса. Этот же выход регистра 8 адреса подключен к информационному входу коммутатора 9. Разрешающие входы коммутаторов 6 и 9 соответственно соединены с первым и вторым выходами схемы сравнения.

Импульс на первом выходе схемы 7 сравнения воспроизводится в том случае, когда содержимое счетчика 5 адреса не превосходит содержимое регистра 8 адреса. Импульс на втором выходе схемы 7 сравнения воспроизводится в том случае, когда содержимое счетчика 5 адреса превосходит содержимое регистра 8 адреса.

Выходы коммутаторов 6 и 9 через блок элементов ИЛИ 10 соединены с адресным входом блока 11 памяти значений сепарационной характеристики. Второй вход блока 11 памяти соединен с первым выходом схемы 3 сравнения. Первый выход блока 11 памяти соединен с вторым входом схемы 3 сравнения. Второй выход схемы сравнения подключен к счетному входу счетчика 5 адреса.

Импульс на первом выходе схемы 3 сравнения воспроизводится, если число, прогенерированное генератором 1 случайных чисел не меньше числа на первом выходе блока 11 памяти, В противном случае

вырабатывается импульс на второй выходной шине схемы 3 сравнения и, соответственно, на счетном входе -четчика 5 адреса.

Второй, третий, четвертый и пятый выходы блока 11 памяти подключены к соответствующим входам блока 2 вычисления. Выход блока 2 вычисления соединен с второй выходной шиной всего устройства.

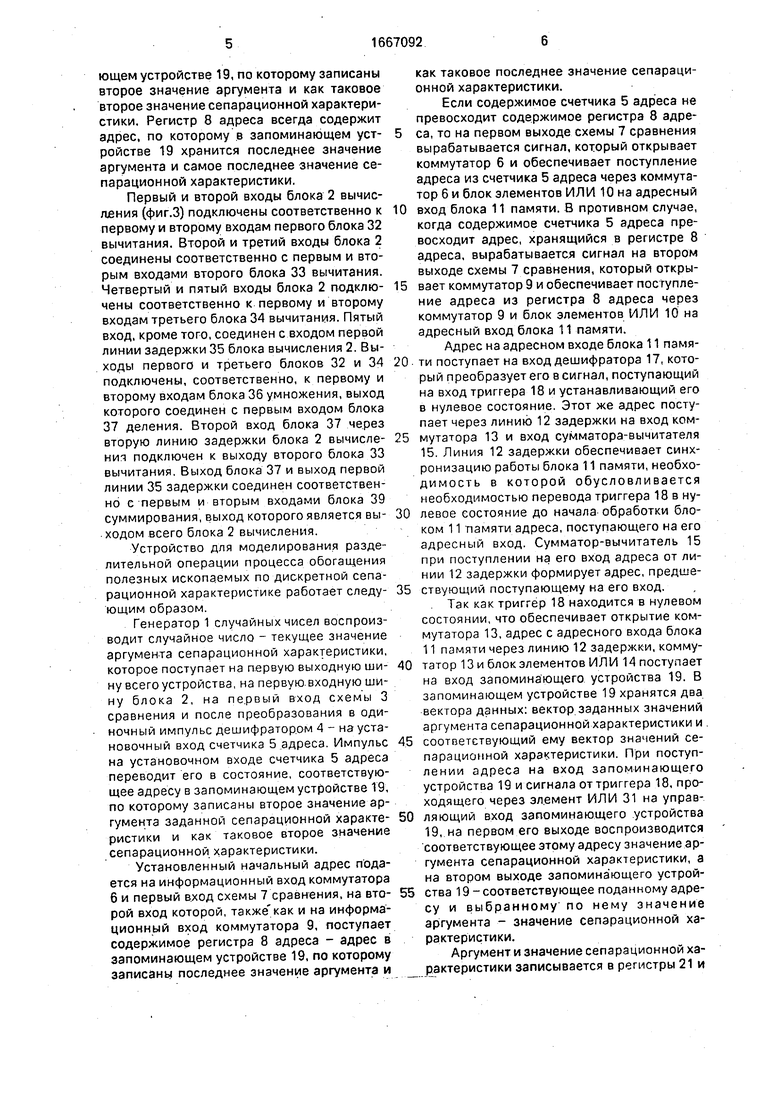

Адресный вход блока 11 памяти (фиг.2)

подключен через линию 12 задержки и информационный вход коммутатора 13 к первому входу блока элементов ИЛИ 14, через линию 12 задержки, сумматор-вычитатель

15 и информационный вход коммутатора 16- к второму входу блока элементов ИЛИ 14 и через дешифратор 17 (назначение которого аналогично назначению дешифратора 4)- к установочному входу в нулевое состояние

триггера 18. Установочный в единичное состояние вход триггера 18 соединен с вторым входом блока 11 памяти.

Выход блока элементов ИЛИ 14 под- ключей к адресному входу запоминающего

устройства 19. Первый информационный выход запоминающего устройства 19 соединен через инфоромационный вход коммутатора 20 с первой выходной шиной блока 11 памяти и через регистр 21 памяти - с информационными входами коммутаторов 22 и 23.

Второй информационный выход запоминающего устройства 19 через регистр 24 памяти подключен к информационным входам коммутаторов 25 и 26. Выходы коммутаторов 22, 23, 25 и 26 через регистры 27, 28, 29 и 30 памяти соединены, соответственно, с второй, третьей, четвертой и пятой выходными шинами блока 11 памяти. Разрешающие входы коммутаторов 13, 20, 23 и 25 подключены к нулевому выходу триггера 18, а коммутаторов 16, 22 и 26 - к единичному выходу триггера 18 через элемент ИЛИ 31 подключены к управляющему входу запоминающего устройства 19.

Запоминающее устройство 19 позволяет хранить два вектора данных: дискретные значения аргумента сепарационной характеристики и соответствующие им тактовые

дискретные значения сепарационной характеристики. При этом поступление адреса на вход запоминающего устройства 19обес- печивает выдачу на первый его выходной шине аргумента сепарационной характеристики, а на второй выходной шине - значений сепарационной характеристики. Адрес формируется в счетчике 5 адреса. Импульс на установочном входе счетчика 5 адреса обеспечивает установку его в нулевое состояние, соответствующее адресу в запоминающем устройстве 19, по которому записаны второе значение аргумента и как таковое второе значение сепарационной характеристики. Регистр 8 адреса всегда содержит адрес, по которому в запоминающем уст- ройстве 19 хранится последнее значение аргумента и самое последнее значение сепарационной характеристики.

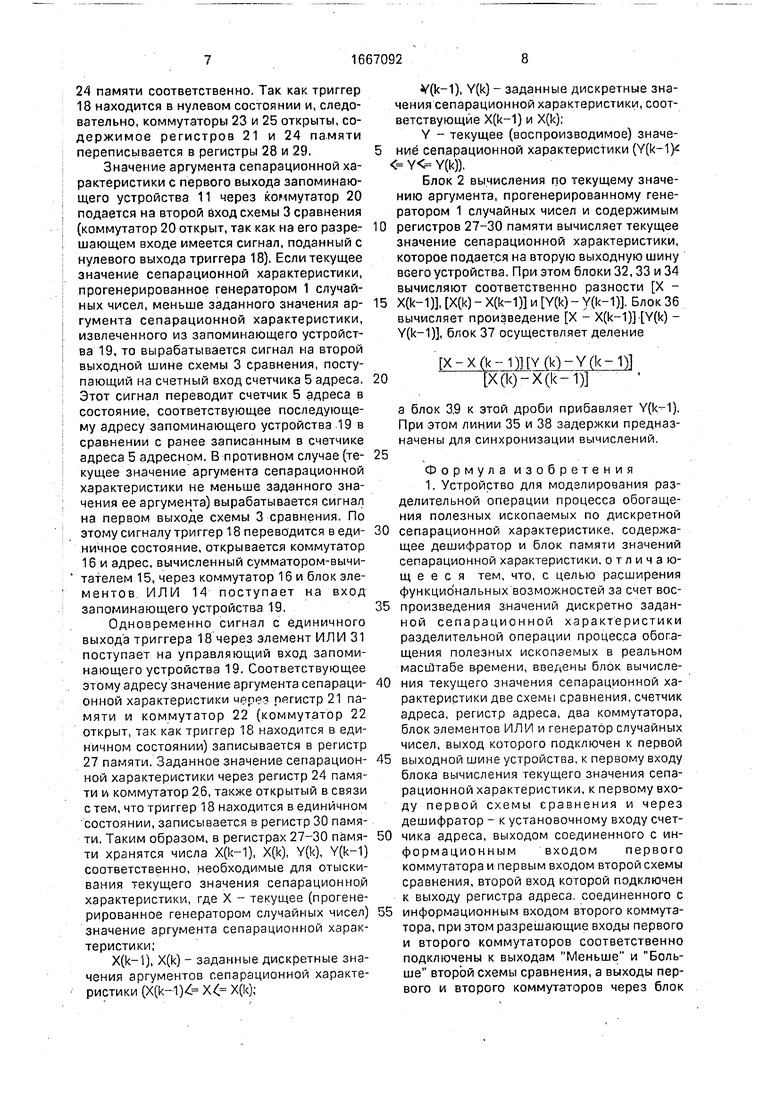

Первый и второй входы блока 2 вычисления (фиг.З) подключены соответственно к первому и второму входам первого блока 32 вычитания. Второй и третий входы блока 2 соединены соответственно с первым и вторым входами второго блока 33 вычитания. Четвертый и пятый входы блока 2 подклю- чены соответственно к первому и второму входам третьего блока 34 вычитания. Пятый вход, кроме того, соединен с входом первой линии задержки 35 блока вычисления 2. Выходы первого и третьего блоков 32 и 34 подключены, соответственно, к первому и второму входам блока 36 умножения, выход которого соединен с первым входом блока 37 деления. Второй вход блока 37 через вторую линию задержки блока 2 вычисле- нит подключен к выходу второго блока 33 вычитания. Выход блока 37 и выход первой линии 35 задержки соединен соответственно с первым и вторым входами блока 39 суммирования, выход которого является вы- ходом всего блока 2 вычисления,

Устройство для моделирования разделительной операции процесса обогащения полезных ископаемых по дискретной сепарационной характеристике работает следу- ющим образом.

Генератор 1 случайных чисел воспроизводит случайное число - текущее значение аргумента сепарационной характеристики, которое поступает на первую выходную ши- ну все го устройства, на первую входную шину блока 2, на первый вход схемы 3 сравнения и после преобразования в одиночный импульс дешифратором 4 - на установочный вход счетчика 5 адреса. Импульс на установочном входе счетчика 5 адреса переводит его в состояние, соответствующее адресу в запоминающем устройстве 19. по которому записаны второе значение аргумента заданной сепарационной характе- ристики и как таковое второе значение сепарационной характеристики.

Установленный начальный адрес подается на информационный вход коммутатора 6 и первый вход схемы 7 сравнения, на вто- рой вход которой, также как и на информационный вход коммутатора 9, поступает содержимое регистра 8 адреса - адрес в запоминающем устройстве 19, по которому записаны последнее значение аргумента и

как таковое последнее значение сепарационной характеристики.

Если содержимое счетчика 5 адреса не превосходит содержимое регистра 8 адреса, то на первом выходе схемы 7 сравнения вырабатывается сигнал, который открывает коммутатор 6 и обеспечивает поступление адреса из счетчика 5 адреса через коммутатор 6 и блок элементов ИЛИ 10 на адресный вход блока 11 памяти. В противном случае, когда содержимое счетчика 5 адреса превосходит адрес, хранящийся в регистре 8 адреса, вырабатывается сигнал на втором выходе схемы 7 сравнения, который открывает коммутатор 9 и обеспечивает поступление адреса из регистра 8 адреса через коммутатор 9 и блок элементов ИЛИ 10 на адресный вход блока 11 памяти.

Адрес на адресном входе блока 11 памяти поступает на вход дешифратора 17, который преобразует его в сигнал, поступающий на вход триггера 18 и устанавливающий его в нулевое состояние. Этот же адрес поступает через линию 12 задержки на вход коммутатора 13 и вход сумматора-вычитателя 15. Линия 12 задержки обеспечивает синхронизацию работы блока 11 памяти, необхо- димость в которой обусловливается необходимостью перевода триггера 18 в нулевое состояние до начала обработки блоком 11 памяти адреса, поступающего на его адресный вход. Сумматор-вычитатель 15 при поступлении на его вход адреса от линии 12 задержки формирует адрес, предшествующий поступающему на его вход.

Так как триггер 18 находится в нулевом состоянии, что обеспечивает открытие коммутатора 13, адрес с адресного входа блока 11 памяти через линию 12 задержки, коммутатор 13 и блок элементов ИЛИ 14 поступает на вход запоминающего устройства 19. В запоминающем устройстве 19 хранятся два вектора данных: вектор заданных значений аргумента сепарационной характеристики и соответствующий ему вектор значений сепарационной характеристики. При поступлении адреса на вход запоминающего устройства 19 и сигнала от триггера 18, проходящего через элемент ИЛИ 31 на управляющий вход запоминающего устройства 19, на первом его выходе воспроизводится соответствующее этому адресу значение аргумента сепарационной характеристики, а на втором выходе запоминающего устройства 19 -соответствующее поданному адресу и выбранному по нему значение аргумента - значение сепарационной характеристики.

Аргумент и значение сепарационной характеристики записывается в регистры 21 и

24 памяти соответственно. Так как триггер 18 находится в нулевом состоянии и, следовательно, коммутаторы 23 и 25 открыты, содержимое регистров 21 и 24 памяти переписывается в регистры 28 и 29.

Значение аргумента сепарационной характеристики с первого выхода запоминающего устройства 11 через коммутатор 20 подается на второй вход схемы 3 сравнения (коммутатор 20 открыт, так как на его разрешающем входе имеется сигнал, поданный с нулевого выхода триггера 18). Если текущее значение сепарационной характеристики, прогенерированное генератором 1 случайных чисел, меньше заданного значения аргумента сепарационной характеристики, извлеченного из запоминающего устройства 19, то вырабатывается сигнал на второй выходной шине схемы 3 сравнения, поступающий на счетный вход счетчика 5 адреса. Этот сигнал переводит счетчик 5 адреса в состояние, соответствующее последующему адресу запоминающего устройства 19 в сравнении с ранее записанным в счетчике адреса 5 адресном. В противном случае (текущее значение аргумента сепарационной характеристики не меньше заданного значения ее аргумента) вырабатывается сигнал на первом выходе схемы 3 сравнения. По этому сигналу триггер 18 переводится в единичное состояние, открывается коммутатор 16 и адрес, вычисленный сумматором-вычи- тателем 15, через коммутатор 16 и блок элементов ИЛИ 14 поступает на вход запоминающего устройства 19.

Одновременно сигнал с единичного выхода триггера 18 через элемент ИЛИ 31 поступает на управляющий вход запоминающего устройства 19. Соответствующее этому адресу значение аргумента сепарационной характеристики ЧРПРЧ рргистр 21 памяти и коммутатор 22 (коммутатор 22 открыт, так как триггер 18 находится в единичном состоянии) записывается в регистр 27 памяти. Заданное значение сепарационной характеристики через регистр 24 памяти и коммутатор 26, также открытый в связи с тем, что триггер 18 находится в единичном состоянии, записывается в регистр 30 памяти. Таким образом, в регистрах 27-30 памяти хранятся числа X(k-1). X(k). Y(k). Y(k-1) соответственно, необходимые для отыскивания текущего значения сепарационной характеристики, где X - текущее (прогенерированное генератором случайных чисел) значение аргумента сепарационной характеристики;

X(k-1), X(k) - заданные дискретные значения аргументов сепарационной характеристики (X(k-lK X X(k);

Y(k-1), Y(k) - заданные дискретные значения сепарационной характеристики, соответствующие X(k-1) и X(k):

Y - текущее (воспроизводимое) значе- ниё сепарационной характеристики (Y(k-iy Y Y0c)).

Блок 2 вычисления по текущему значению аргумента, прогенерированному генератором 1 случайных чисел и содержимым регистров 27-30 памяти вычисляет текущее значение сепарационной характеристики, которое подается на вторую выходную шину всего устройства. При этом блоки 32, 33 и 34 вычисляют соответственно разности X - X(k-1),X(k)-X(k-1)(k)- Y(k-1). Блок 36 вычисляет произведение X - X(k-1) Y(k) - Y(k-1), блок 37 осуществляет деление

X-X(k-1)Y(k)-Y(k-1) X(k)-X(k-1)j

а блок 39 к этой дроби прибавляет Y(k-1) При этом линии 35 и 38 задержки предназначены для синхронизации вычислений.

Формула изобретения 1. Устройство для моделирования разделительной операции процесса обогащения полезных ископаемых по дискретной

0 сепарационной характеристике, содержащее дешифратор и блок памяти значений сепарационной характеристики, отличающееся тем, что, с целью расширения функциональных возможностей за счет вос5 произведения значений дискретно заданной сепарационной характеристики разделительной операции процесса обогащения полезных ископаемых в реальном масштабе времени, введены блок вычисле0 ния текущего значения сепарационной характеристики две схемы сравнения, счетчик адреса, регистр адреса, два коммутатора, блок элементов ИЛИ и генератор случайных чисел, выход которого подключен к первой

5 выходной шине устройства, к первому входу блока вычисления текущего значения сепарационной характеристики, к первому входу первой схемы сравнения и через дешифратор - к установочному входу счет0 чика адреса, выходом соединенного с информационным входом первого коммутатора и первым входом второй схемы сравнения, второй вход которой подключен к выходу регистра адреса, соединенного с

5 информационным входом второго коммутатора, при этом разрешающие входы первого и второго коммутаторов соответственно подключены к выходам Меньше и Больше второй схемы сравнения, а выходы первого и второго коммутаторов через блок

элементов ИЛИ соединены с адресным входом блока памяти значений сепарационной характеристики, тактовый вход которого подключен к выходу Больше первой схемы сравнения, выходом Меньше соединенной со счетным входом счетчика адреса, при этом первый информационный выход блока памяти значений сепарационной характеристики подключен к второму информационному входу первой схемы сравнения, а с второго по пятый информационные выходы блока памяти значений сепарационной характеристики подключены соответственно к одноименным входам блока вычисления текущего значения сепарационной характеристики, выход которого соединен с второй выходной шиной устройства.

2. Устройство поп.1.отличающее- с я тем, что блок памяти значений сепарационной характеристики содержит триггер, дешифратор, сумматор-вычитатель, шесть регистров памяти, семь коммутаторов, элемент ИЛИ и блок элементов ИЛИ, линию задержки и запоминающее устройство, при этом адресный вход блока памяти значений сепарационной характеристики подключен через линию задержки и информационный вход первого коммутатора к первому входу блока элементов ИЛИ, через линию задержки, сумматор-вычитатель и информационный вход второго коммутатора - к второму входу блока элементов ИЛИ и через дешифратор - к установочному в нулевое состояние входу триггера, установочный в единичное состояние вход которого соединен с тактовым входом блока памяти значений сепарационной характеристики, а выход блока элементов ИЛИ подключен к адресному входу запоминающего устройства, первый информационный выход которого соединен с информационным входом третьего коммутатора, выход которого соединен с первой выходной шиной блока памяти значений сепарационной характеристики и через первый регистр памяти - с информационными входами четвертого и пятого коммутаторов, второй информационный выход запоминающего устройства через второй регистр памяти подключен к информационным входам шестого и седьмого коммутаторов, а выходы с четвертого по седьмой коммутаторов через соответственно третий - шестой регистры памяти соединены с второго по пятый информационными выходами блока памяти значений сепарационной характеристики, причем разрешающие входы первого, третьего, пятого и шестого коммутаторов подключены к нулевому выходу триггера, разрешающие входы второго, четвертого и седьмого коммутаторов - с единичным выходом триггера,

а тактовый вход запоминающего устройства через элемент ИЛИ соединен с нулевым и единичным выходами триггера.

3. Устройство поп.1,отличающее- с я тем, что блок вычисления текущего значения сепарационной характеристики содержит три блока вычитания, блок умножения, блок деления, блок суммирования и две линии задержки, при этом первый вход блока вычисления текущего значения

сепарационной характеристики подключен к первому входу первого блока вычитания, второй вход которого соединен с вторым входом блока вычисления текущего значения сепарационной характеристики, подключенного к первому входу второго блока вычитания, второй вход которого соединен с третьим входом блока вычисления текущего значения сепарационной характеристики, четвертый вход которого подключен к

первому входу третьего блока вычитания, второй вход которого соединен с пятым входом блока вычисления текущего значения сепарационной характеристики, связанным также с входом первой линии задержки блока вычисления текущего значения сепарационной характеристики,а выходы первого и третьего блоков вычитания соединены соответственно с первым и вторым входами блока умножения, выход которого подключен к первому входу блока деления, второй вход которого через вторую линию задержки блока вычисления текущего значения сепарационной характеристики соединен с выходом второго блока вычитания, а выход

блока деления подключен к первому входу блока суммирования, второй вход которого через первую линию задержки блока вычисления текущего значения сепарационной характеристики соединен с пятым входом

блока вычисления текущего значения сепарационной характеристики, выход которого подключен к выходу блока суммирования.

i

//

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для воспроизведения функций | 1984 |

|

SU1182539A1 |

| Программируемый контроллер | 1987 |

|

SU1448338A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1035604A1 |

| Устройство для вычисления ядер Винера нелинейных объектов | 1984 |

|

SU1196896A1 |

| Устройство для исследования графов | 1984 |

|

SU1238099A1 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

| Вычислительное устройство | 1986 |

|

SU1432510A1 |

| Устройство для вычисления коэффициентов интерполирующего полинома | 1990 |

|

SU1748158A1 |

Изобретение относится к технике моделирования технологических процессов обогащения полезных ископаемых и может быть использовано при исследовании разделительных операций в реальном масштабе времени. Цель изобретения - расширение функциональных возможностей за счет воспроизведения значений дискретно заданной сепарационной характеристики разделительной операции процесса обогащения полезных ископаемых в реальном масштабе времени. Для моделирования генератором случайных чисел 1 воспроизводится случайное число-аргумент дискретной сепарационной характеристики и по заданным дискретным значениям самой сепарационной характеристики в блоках 2 и 11 вычисляется текущее моделируемое значение сепарационной характеристики. 3 ил.

±

Фиг. 2 25

| Авторское свидетельство СССР № 1367741 | |||

| кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для управления производственным процессом ремонта машин | 1985 |

|

SU1314305A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-07-30—Публикация

1989-07-14—Подача