1

Изобретение относится к специали-. Зированным устройствам вычислительной Техники и может быть использовано реализации процедуры двухальтер- ативной классификации нестационарных Случайных процессов, Цель изобретения - повьппение до- йтоверйости классификации.

Принцип функционирования устрой

ства основан на процедуре вычисления

разделяющей функции , которая строится на -основании оценок многомерных маргинальных функций плотности вероятности слу 1айных процессов. Первого и второго классов

Р; (г i+ed «« ) )

: i 1, 2,

йрошедтих предварительно преобразование следующего вида: каждая точка йроцесса, очищенного с помощью высокочастотного фильтра от нестационарной; составляклцей: }Гп X(dtn), п 1, N, преобразуется в последовательность

из .d чисел Y-, j (n-l)d, nd-l. Следующим образом:

л

Y,- 1 при j-(n-l)d-l Хп; , ,

YJ О, при j-(n-l)d-l Хп, лри этом предполагается, что значения Х„ лежат в диапазоне для всех п ,N (величина d равна максимальной кодовой комбинации аналого-цифрового преобразователя).

Разделяющая функция строится следующим образом:

, , р,IYU YI. ed JI...iY/:HdJ ° Т , (Yi7vV J -f

(2)

Решение о принадлежности наблю- даемой реализации Х, п 1, N,

5

10

20

25

30

5

0

к первому классу принимается при 7/Ъ, рещение о принадлежности к второму классу - в случае ;L, где L. - фиксированный порог.

Для квазипериодических процессов первого и второго классов i 1,2, величины P,(Y., ,,-.., Yjvjgj ) в общем случае различны, что является условием, обеспечивающим возможность построения разделяющей функции в виде (2).

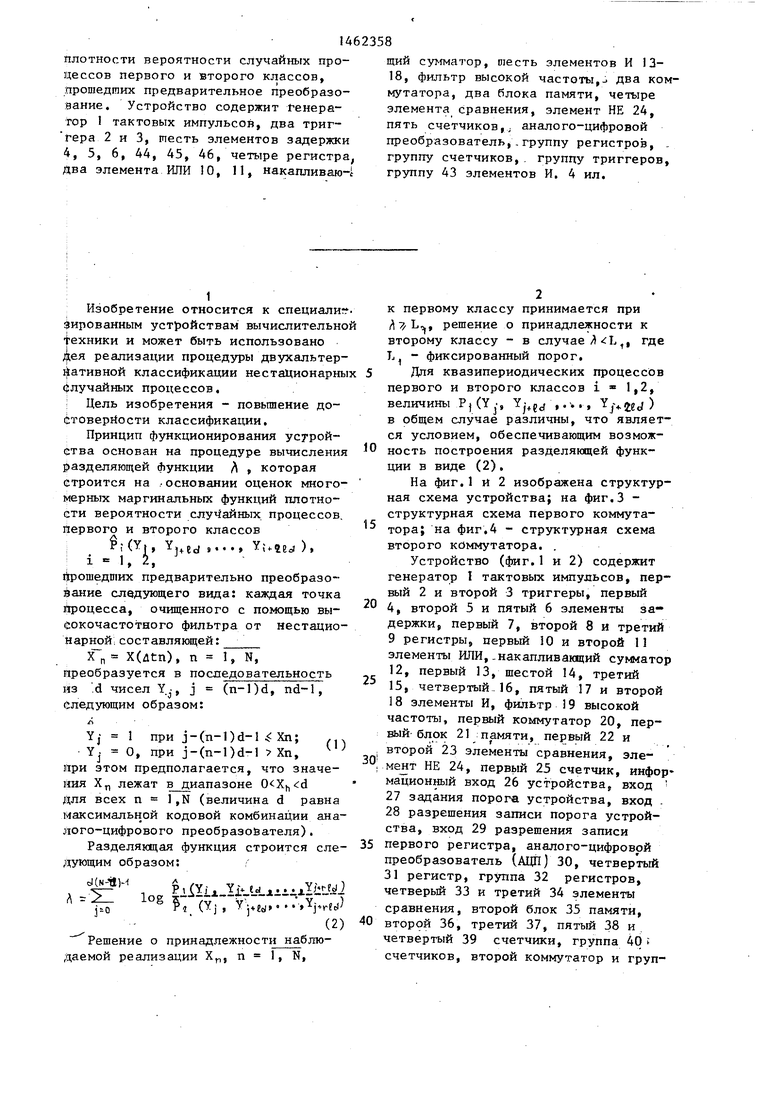

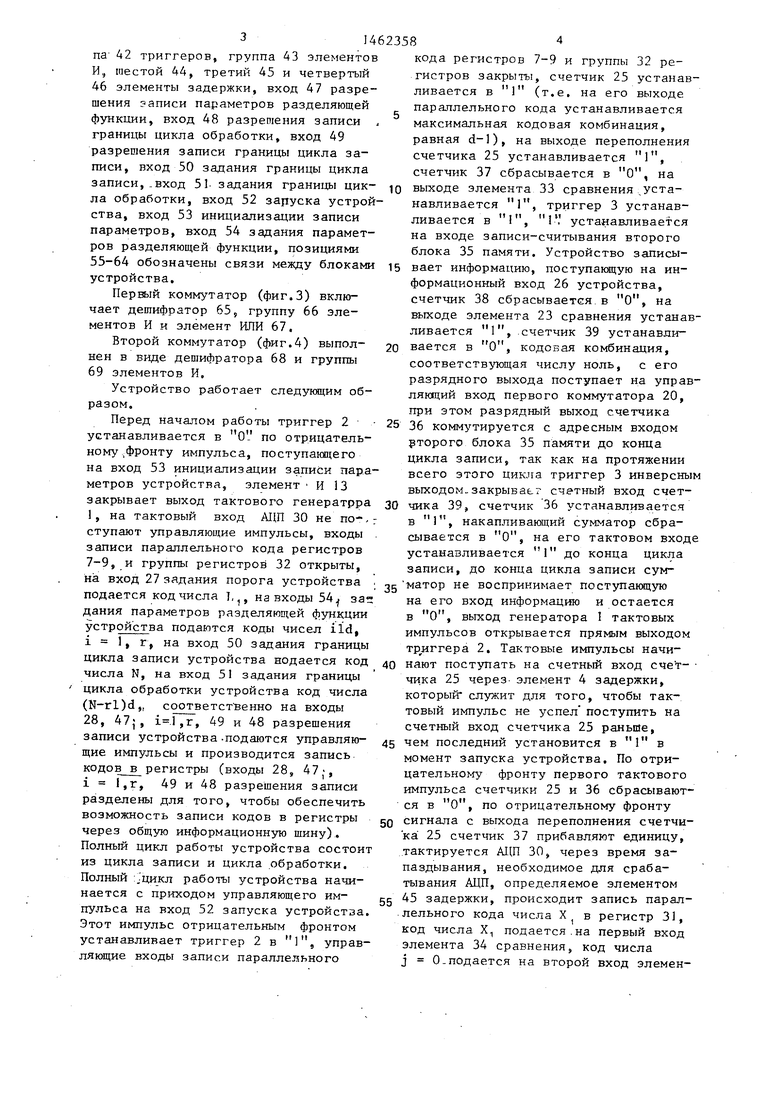

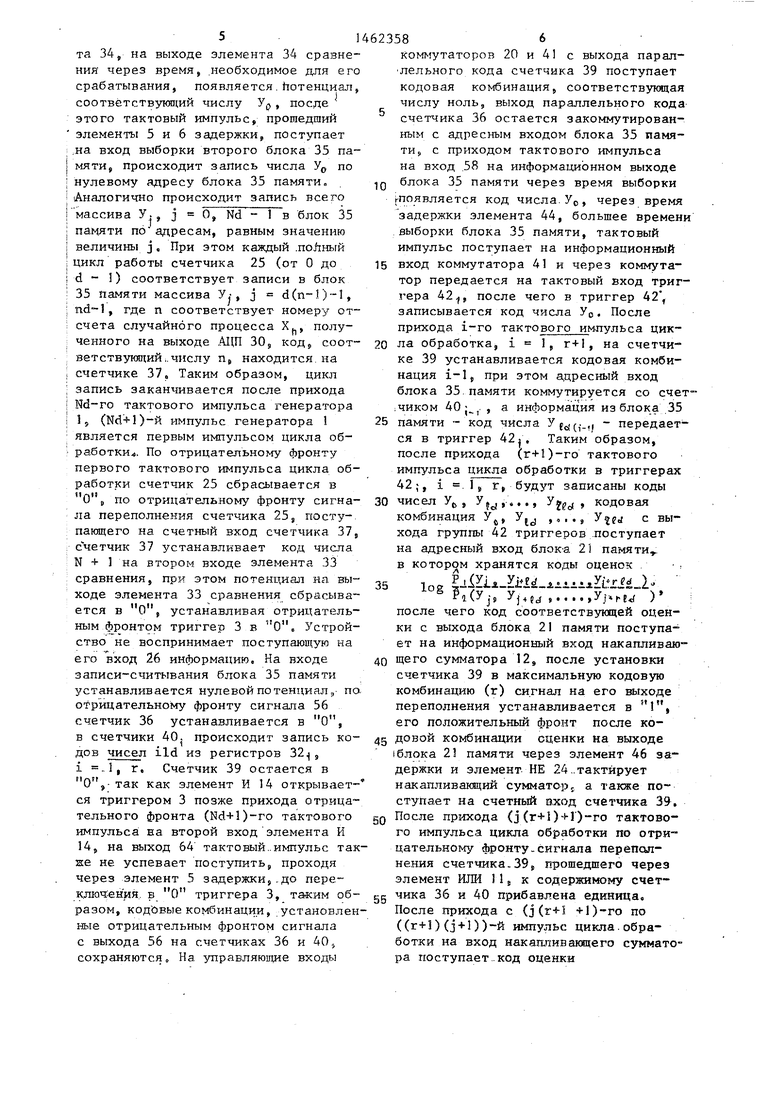

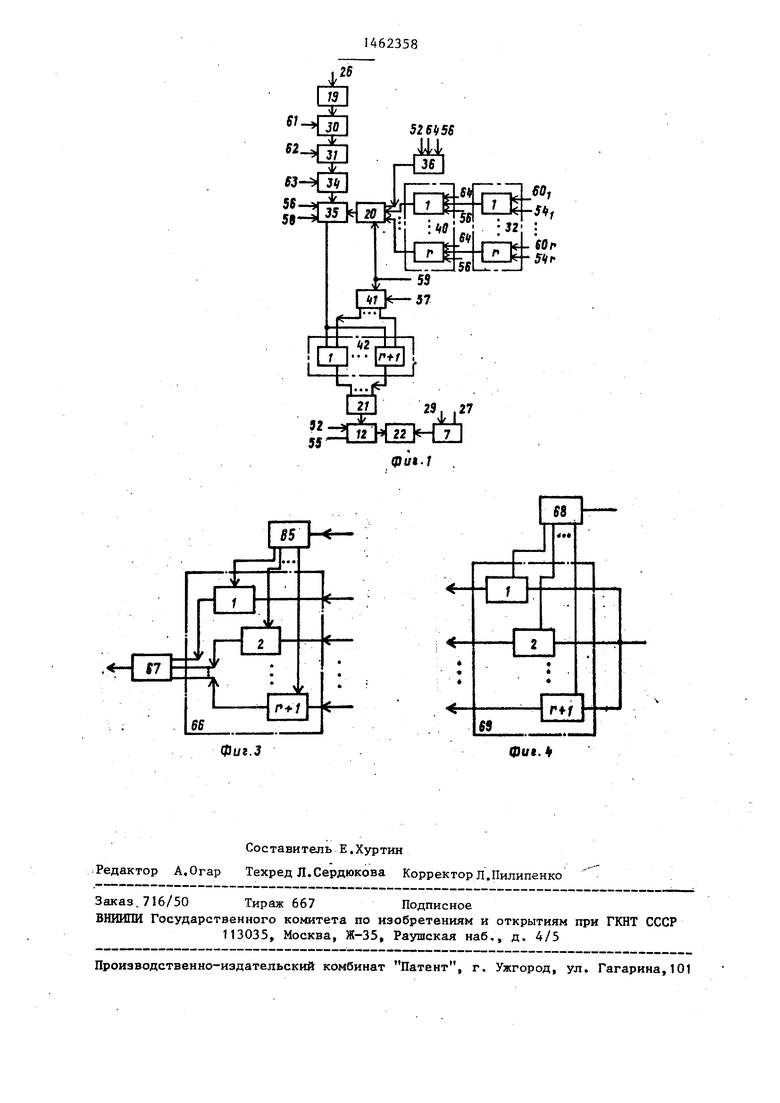

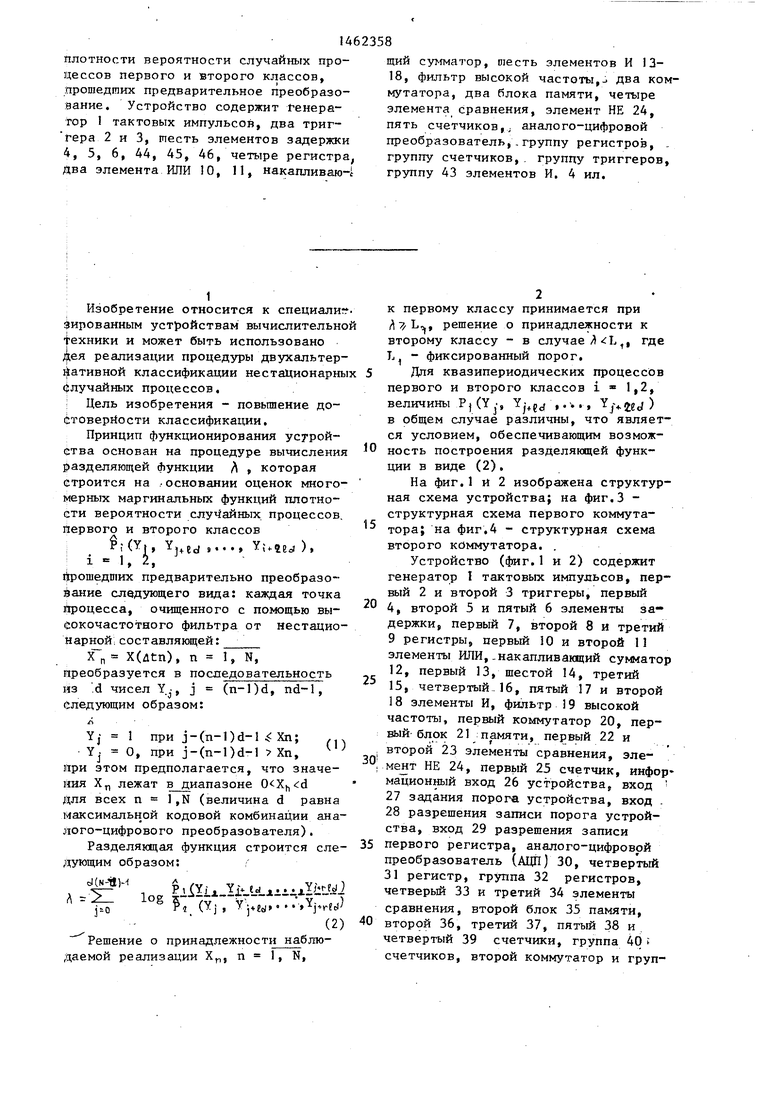

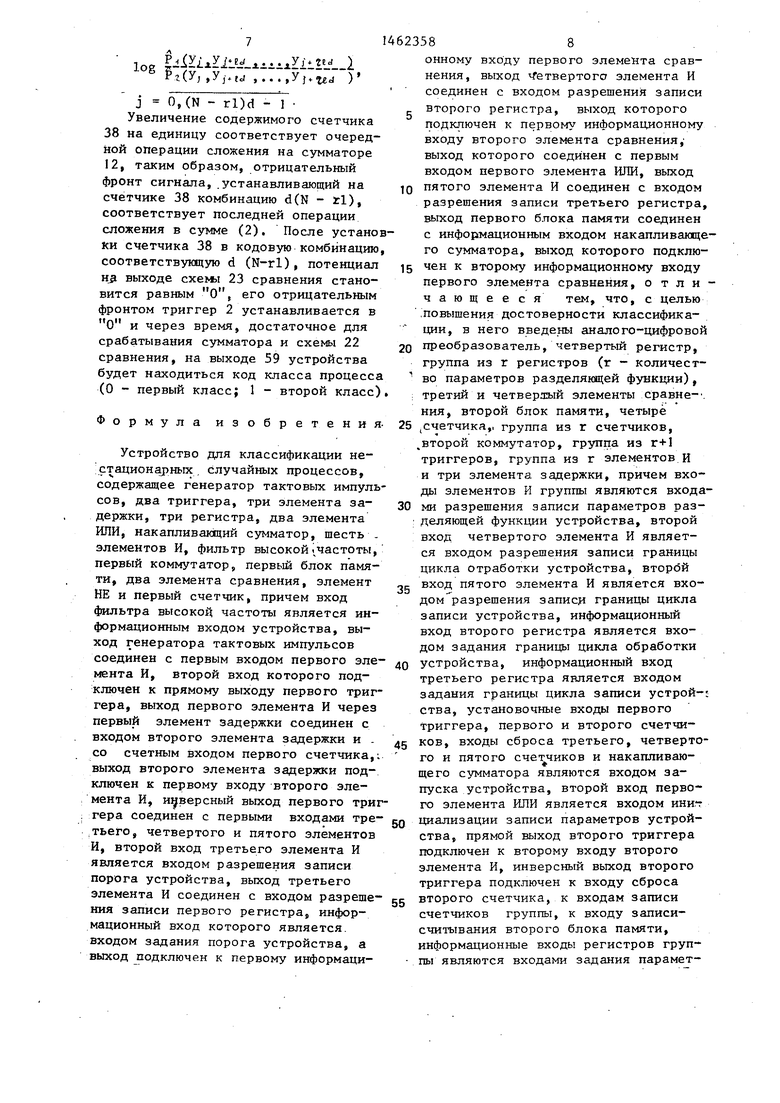

На фиг.1 и 2 изображена структурная схема устройства; на фиг.З - структурная схема первого коммутатора; на фиг.4 - структурная схема второго коммутатора.

Устройство (фиг.1 и 2) содержит генератор 1 тактовых импульсов, первый 2 и второй 3 триггеры, первый 4, второй 5 и пятый 6 элементы задержки, первый 7, второй 8 и третий 9 регистры, первый 10 и второй П элементы ИЛИ,.накапливающий сумматор 12, первый 13, шестой 14, третий 15, четвертый.16, пятый 17 и второй 18 элементы И, фильтр 19 высокой частоты, первый коммутатор 20, первый блок 21 памяти, первый 22 и второй 23 элементы сравнения, эле- мент НЕ 24, первый 25 счетчик, информационный вход 26 устройства, вход

27задания порога устройства, вход

28разрещения записи порога устройства, вход 29 разрещения записи первого регистра, аналого-цифровой преобразователь (АЦП) 30, четвертый 31 регистр, группа 32 регистров, четверый 33 и третий 34 элементы сравнения, второй блок 35 памяти, второй 36, третий 37, пятый 38 и четвертый 39 счетчики, группа 40 f счетчиков, второй коммутатор и группа- 42 триггеров, группа 43 элементо И, шестой 44, третий 45 и четвертый 46 элементы задержки, вход 47 разрешения записи параметров разделяющей функции, вход 48 разрешения записи границы цикла обработки, вход 49 разрешения записи границы цикла записи, вход 50 задания границы цикла записи, .вход 51- задания границы цикла обработки, вход 52 запуска устройства, вход 53 инициализации записи

параметров, вход 54 задания параметров разделяющей функции, позициями 55-64 обозначены связи между блоками устройства.

Первый коммутатор (фиг.З) включает дешифратор 65, группу 66 элементов И и элемент ИЛИ 67.

Второй коммутатор (фиг.4) выполнен в виде дешифратора 68 и группы 69 элементов И.

Устройство работает следующим образом.

Перед началом работы триггер 2 - устанавливается в О по отрицательному .Фронту импульса, поступакщего на вход 53 инициализации записи параметров устройства, элемент И 13 закрывает выход тактового генератрра 1, на тактовый вход А1Ш 30 не по-, ступают управляющие импульсы, входы записи параллельного кода регистров 7-9, и группы регистров 32 открыты, на вход 27 задания порога устройства подается код числа 1,, на входы 54 за Дания параметров разделяющей функции устройства подаются коды чисел ild, i 1, г, на вход 50 задания границы цикла записи устройства подается код числа N, на вход 51 задания границы цикла обработки устройства код числа (N-rl)d,, соответст венно на входы 28, 47J, i-l,r, 49 и 48 разрешения записи устройства -подаются управляющие импульсы и производится запись кодов в регистры (входы 28, 47-, 1 - , 49 и 48 разрешения записи разделены для того, чтобы обеспечить возможность записи кодов в регистры через общую информационную шину). Полный цикл работы устройства состоит из цикла записи и цикла обработки. Полный :, цикл работы устройства начинается с приходом управляющего импульса на вход 52 запуска устройства. Этот импульс отрицательным фронтом устанавливает триггер 2 в 1, управляющие входы записи параллельного

кода регистров 7-9 и группы 32 регистров закрыты, счетчик 25 устанавливается в 1 (т.е. на его выходе параллельного кода устанавливается максимальная кодовая комбинация, равная d-l), на выходе переполнения счетчика 25 устанавливается 1, счетчик 37 сбрасывается в О, на выходе элемента 33 сравнения устанавливается 1, триггер 3 устанавливается в I, I устанавливается

0

на входе записи-считывания второго блока 35 памяти. Устройство записы- 15 вает информацию, поступающую на информационный вход 26 устройства, счетчик 38 сбрасывается в О, на выходе элемента 23 сравнения устанавливается 1, счетчик 39 устанавли- 20 вается в О, кодовая комбинация, соответствующая числу ноль, с его разрядного выхода поступает на управ- лякщий вход первого коммутатора 20, при этом разрядный выход счетчика 25 36 коммутируется с адресным входом второго блока 35 памяти до конца цикла записи, так как на протяжении всего этого цикла триггер 3 инверсным выходом.закрывает счетный вход счетчика 39, счетчик 36 устанавливается в 1, накапливающий сумматор сбрасывается в О, на его тактовом входе устанавливается 1 до конца цикла записи, до конца цикла записи сум- 5 матор не воспринимает поступающую на его вход информацию и остается в О, выход генератора 1 тактовых импульсов открывается прямым выходом триггера 2. Тактовые импульсы начи- 0 нают поступать на счетный вход счет- чика 25 через- элемент 4 задержки, который служит для того, чтобы тактовый импульс не успел поступить на счетный вход счетчика 25 раньше, 5 чем последний установится в 1 в момент запуска устройства. По отрицательному фронту первого тактового импульса счетчики 25 и 36 сбрасываются в О, по отрицательному фронту сигнала с выхода переполнения счетчика 25 счетчик 37 прибавляют единицу, тактируется АЦП 30, через время запаздывания, необходимое для срабатывания АЦП, определяемое элементом 45 задержки, происходит запись парал- .лельного кода числа X в регистр 31, код числа Х, подается.на первый вход элемента 34 сравнения, код числа j 0.подается на второй вход элемен0

5

та 34, на выходе элемента 34 сравнения через время, .необходимое для его срабатывания, появляется.йотенциал, соотвётствукнций числу Ур, после этого тактовый импульс, прошедший элементы 5 и 6 задержкиj поступает ,на вход выборки второго блока 35 памяти, происходит запись числа У по нулевому адресу блока 35 памяти Аналогично происходит запись всего массива Yj, j О, Nd - 1 в блок 35 памяти по адресам, равным значению величины j. При этом каждый .полный цикл работы счетчика 25 (от О до d - ) соответствует записи в блок 35 памяти массива У,-, j d(n-l)-1, , где n соответствует номеру от счета случайного процесса Xj, полукоммутаторов 20 и 41 с выхода парал- лельного кода счетчика 39 поступает кодовая комбинация, соответствукнцая числу ноль9 выход параллельного кода счетчика 36 остается закоммутированным с адресным входом блока 35 памяти с приходом тактового импульса на вход 58 на информационном выходе

д блока 35 памяти через время выборки -появляется код числа. УС, через время задержки элемента 44, большее времени выборки блока 35 памяти, тактовый импульс поступает на информационный

15 вход коммутатора 41 и через коммутатор передается на тактовый вход триггера 42 .J, после чего в триггер 42, записывается код числа УО. После прихода i-ro тактового импульса цикченного на выходе А1Щ 30, код, соот- 20 ла обработка, i , г+1, на счетчи: нетствукшшй..числу п находится, на j счетчике 37, Таким образом, цикл : запись заканчивается после прихода I Nd-ro тактового импульса генератора i Ij (Nd+l)-й импульс генератора является первым импульсом цикла об- - работки. По отрицательному фронту первого тактового импульса цикла обработки счетчик 25 сбрасывается в

ке 39 устанавливается кодовая комбинация 1-15 при этом адресный вход блока 35.памяти коммутируется со счет ;Чиком 40;,. J а информация из блока 35 25 памяти - код числа У{о,(,--,| передается в триггер 42j. Таким образом, после прихода (г+1)-го тактового импульса цикла обработки в триггерах 42;, i .lj г, будут записаны коды

, по отрицательному фронту сигна- 30 чисел У , У}..., df кодовая

ла переполнения счетчика 25, посту-. пающего на счетный вход счетчика 37, с четчик 37 устанавливает код чиста N + 1 на втором входе элемента 33 сравнения, при этом потенциал на выходе элемента 33 сравнения сбрасывается в О, устанавливая отрицательным фронтом триггер 3 в О. Устройство не воспринимает поступающую на его вход 26 информацию. На входе записи-считывания блока 35 памяти З станавливается нуле вой потенциал,,- по отрицательному фронту сигнала 56 счетчик 36 устанавливается в О,

комбинация У

35

,91., С выхода группы 42 триггеров .поступает на адресный вход блок-а 21 памяти в котором хранятся коды оценок

log j...i-..l

Pa (У 9 s f «f ) после чего код соответствующей оценки с выхода блока 21 памяти поступает на информационный вход накапливаю- 40 щего сумматора 12, после установки счетчика 39 в максимальную кодовую комбинацию (г) сигнал на его выходе

Hjl

переполнения устанавливается в i , его положительный фронт после ко- в счетчики 40. происходит запись ко- 45 довой комбинации сценки на выходе дов чисел ild из регистров 32, (блока 21 памяти через элемент 46 задержки и элемент НЕ 24..тактирует накапливагаций сумматорj а также поступает на счетный эход счетчика 39, gg После прихода (j (г+1)-ь1)-го тактового импульса цикла обработки по отри1 -1, г. Счетчик 39 остается в О,-так как элемент И 14 открывает- ся триггером 3 позже прихода отрицательного фронта (Nd+l)-ro тактового импульса на второй вход элемента И 14, на выход 64 тактовый..импульс так- se не успевает поступить, проходя через элемент 5 задержки,.до пере к.люч:ен ия.. в О триггера 3, таким об- gg разом, код овые комбинации, .установленные отрицательным фронтом сигнала с выхода 56 на счетчиках 36 и 40, сохраняются На управляюище входы

цательному фронту.сигнала переполнения счетчика.39J гфошедшего через элемент ИЛИ П j к содержимому счетчика 36 и 40 прибавлена единица, После прихода с (j(r+l +1)го по ((г+1)(J+1))-й импульс цикла.обработки на вход накаапивающего сумматора поступает..код оценки

коммутаторов 20 и 41 с выхода парал- лельного кода счетчика 39 поступает кодовая комбинация, соответствукнцая числу ноль9 выход параллельного кода счетчика 36 остается закоммутированным с адресным входом блока 35 памяти с приходом тактового импульса на вход 58 на информационном выходе

блока 35 памяти через время выборки -появляется код числа. УС, через время задержки элемента 44, большее времени выборки блока 35 памяти, тактовый импульс поступает на информационный

вход коммутатора 41 и через коммутатор передается на тактовый вход триггера 42 .J, после чего в триггер 42, записывается код числа УО. После прихода i-ro тактового импульса цикке 39 устанавливается кодовая комбинация 1-15 при этом адресный вход блока 35.памяти коммутируется со счет- Чиком 40;,. J а информация из блока 35 памяти - код числа У{о,(,--,| передается в триггер 42j. Таким образом, после прихода (г+1)-го тактового импульса цикла обработки в триггерах 42;, i .lj г, будут записаны коды

чисел У , У}..., df кодовая

чисел У , У}..., df кодовая

комбинация У

,91., С выхода группы 42 триггеров .поступает на адресный вход блок-а 21 памяти в котором хранятся коды оценок

log j...i-..l

Pa (У 9 s f «f ) после чего код соответствующей оценки с выхода блока 21 памяти поступает на информационный вход накапливаю- щего сумматора 12, после установки счетчика 39 в максимальную кодовую комбинацию (г) сигнал на его выходе

Hjl

переполнения устанавливается в i , его положительный фронт после ко- довой комбинации сценки на выходе блока 21 памяти через элемент 46 задержки и элемент НЕ 24..тактирует накапливагаций сумматорj а также поступает на счетный эход счетчика 39, После прихода (j (г+1)-ь1)-го тактового импульса цикла обработки по отрицательному фронту.сигнала переполнения счетчика.39J гфошедшего через элемент ИЛИ П j к содержимому счетчика 36 и 40 прибавлена единица, После прихода с (j(r+l +1)го по ((г+1)(J+1))-й импульс цикла.обработки на вход накаапивающего сумматора поступает..код оценки

lop | i iAniL :tiiiAnii l. 1

Рг(У;,Уу.ы ,..., )

j 0,(N - rl)d - 1 Увеличение содержимого счетчика 38 на единицу соответствует очередной операции сложения на сумматоре 12, таким образом, отрицательный фронт сигнала,.устанавливающий на счетчике 38 комбинацию d(N - П), соответствует последней операции сложения в сумме (2). После установки счетчика 38 в кодовую комбинацию, соответствукщую d (N-rl), потенциал Hj3 выходе схемы 23 сравнения становится равным О, его отрицательным фронтом триггер 2 устанавливается в О и через время, достаточное для срабатывания сумматора и схемы 22 сравнения, на выходе 59 устройства будет находиться код класса процесса (О - первый класс; 1 - второй класс).

14

Формула изобретения. 25

10 15

Устройство для классификации нестационарных , случайных процессов, содержащее генератор тактовых импульсов, два триггера, три элемента задержки, три регистра, два элемента РШИ, накапливающий сумматор, шесть - элементов И, фильтр высокой ,частоты, первый коммутатор, первый блок памяти, два элемента сравнения, элемент НЕ и первый счетчик, причем вход фильтра высокой частоты является информационным входом устройства, выход генератора тактовых импульсов соединен с первым входом первого элемента И, Второй вход которого подключен к прямому выходу первого триггера, выход первого элемента И через первый элемент задержки соединен с входом второго элемента задержки и . со счетным входом первого счетчика,; выход второго элемента задержки подключен к первому входу второго элемента И, инверсный выход первого триггера соединен с первыми входами тре- тьего, четвертого и пятого элементов И, второй вход третьего элемента И является входом разрешения записи порога устройства, выход третьего элемента И соединен с входом разрешения записи первого регистра, информационный вход которого является, входом задания порога устройства, а выход подключен к первому информаци20

25

4623588

онному входу первого элемента сравнения, выход г етвертого элемента И соединен с входом разрешени я записи второго регистра, выход которого подключен к первому информационному входу второго элемента сравнения, выход которого соединен с первым входом первого элемента ИЛИ, выход 10 пятого элемента И соединен с входом разрешения записи третьего регистра, выход первого блока памяти соединен с информационным входом накапливающего сумматора, выход которого подклю- 15 чен к второму информационному входу первого элемента сравнения, отличающееся тем, что, с целью .повышения достоверности классификации, в него введены аналого-цифровой преобразователь, четвертый регистр, группа из г регистров (г - количество параметров разделяющей функции), третий и четверлзый элементы сравне- . ния, второй блок памяти, четыре счетчика,, группа из г счетчиков, ,второй коммутатор, группа из г+1 триггеров, группа из г элементов И и три элемента задержки, причем входы элементов И группы являются входами разрешения записи параметров разделяющей функции устройства, второй вход четвертого элемента И является входом разрешения записи границы цикла отработки устройства, второй вход пятого элемента И является входом разрешения записи границы цикла записи устройства, информационньш вход второго регистра является входом задания границы цикла обработки устройства, информационный вход третьего регистра является входом задания границы цикла записи устрой-; ства, установочные входы первого Триггера, первого и второго счетчиков, входы сброса третьего, четвертого и пятого счетчиков и накапливающего сумматора являются входом запуска устройства, второй вход первого элемента ИЛИ является входом инкт циализации записи параметров устройства, прямой выход второго триггера подключен к второму входу второго элемента И, инверсный выход второго триггера подключен к входу сброса второго счетчика, к входам записи счетчиков группы, к входу записи- считывания второго блока памяти, информационные входы регистров группы являются входами задания парамет30

35

40

45

50

55

ров разделяющей функции устройства, выход п ервого элемента сравнения является выходом устройства, .выходы элементов И группы соединень соответ ственно с входами разрешения записи регистров группы, выход переполнения первого счетчика подключен к тактовому входу.аналого-цифрового преобразователя, к счетному входу третье- то счетчика и к входу третьего элемента зядержки, выход которого соединен с входом разрешения записи ;чётвертого регистра,, разрядный вы- |ход первого счетчика соединен с первым информационньш входом третьего элемента сравнр.ния, выход фильтра высокой частоты соединен с информационным входом аналого-цифрового преобразователя, выход которого под- ключен к инфор-мационному входу чет- (Вертого регистра, выход которого соединен с вторым информацион ным |входом третьего элемента сравнения, выход которого соединен с информа- ционным входом второго блока памяти, адресный вход которого подключен к выходу первого коммутатора, выход первого элемента ИПИ соединен с входом сброса первого триггера, инверс- ный выход которого соединен с вторыми входами элементов И группы, выход третьего регистра подключен к первому информационному входу четвертого элемента сравнения, второй информа- ционный бход которого соединен с разрядным выходом третьего счетчика, выход четвертого сравнения соединен с входом сброса второго триггера, инверсный выход которого соединен с первым входом шестого элемента И, второй вход которого соединен с выходом первого элемента задержки.

а ныход - со счетгп м входом четнер- того счетчика, выход переполнения которого подключен к первому входу второго элемента ИЛИ и через последовательно соединенные четвертый элемент задержки и элемент НЕ к тактовому входу накапливающего сумматора и к счетному входу пятого счетчика, разрядный выход которого соединен с вторым информационным входом второго элемента сравнения, выход второго элемента И соединен с вторым входом второго элемента ИЛИ, выход которого соединен со счетным входом второго счетчика, и со счетными входами счетчиков группы счетчиков, разрядные входы которых соединены соответственно с выходами регистров группы, первый информационный вход первого коммутатора соединен с..разрядным выходом второго счетчика, (1+1)-й информационный вход первого коммутатора соединен с разрядным выходом 1-го счетчика грзшпы, управляющие входы первого и второго коммутаторов соединены с разрядным выходом четвертого счетчика, выход второго элемента задержки подключен к входу пятого элемента задержки, выход.которого соединен с входом выборки второго блока памяти и с входом шестого элемента задержки, выход которого соединен с информационным входом второго коммутатора, i-й выход второго коммутатора соединен с тактовым входом i-ro триггера группы прямой выход i-ro триггера группы соединен с i-м разрядным адресным входом первого блока памяти, выход второго блока памяти соединен с информационными входами триггеров группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для имитации технической системы конвейерного типа | 1988 |

|

SU1522159A1 |

| Таймер | 1985 |

|

SU1357939A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| СИСТЕМА ДЛЯ ШИФРАЦИИ И ДЕШИФРАЦИИ КОМАНД | 1991 |

|

RU2043699C1 |

| Устройство для приема и обработки команд телеуправления | 1989 |

|

SU1667137A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Устройство декодирования циклических кодов | 1990 |

|

SU1735996A2 |

| Цифровой фильтр | 1990 |

|

SU1730718A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Устройство для имитации технической системы конвейерного типа | 1990 |

|

SU1741102A1 |

Изобретение относится к специализированным устройствам вычислительной техники и может быть использовано для двухальтернативной-класси- фикации нестационарных случайных процессов. Цель изобретения - повышение достоверности классификации. Устройство осзществляет вычисление разде- ляклцей функции на основании оценок многомерных маргинальных функций

.j7

SB

r jj-e-

Фиг.З

фал.1

-LLJS9

rff

Фил.

| Устройство для анализа распреде-лЕНий СлучАйНыХ пРОцЕССОВ | 1979 |

|

SU830399A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обнаружения момента изменения свойств случайного процесса | 1980 |

|

SU888133A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для классификации нестационарных случайных процессов | 1985 |

|

SU1267435A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-02-28—Публикация

1987-07-03—Подача