Изобретение относится к устройствам для обработки данных и может быть использовано в устройствах вывода инфромации ЦВМ на экран телевизионного приемника.

Известно устройство отображения информации на экране телевизионного приемника, позволяющее осуществлять поворот изображения.

Указанное устройство содержит синх- рогенератор, соединенный со счетчиком по координате X и логическим формирователем, а также делителем частоты, блок ввода и цифроаналоговый -преобразователь, соединенный с телевизионным индикатором, блок преобразования координат, два вычислительных блока, коммутаторы, суммирующие счетчики, синтезатор вращающихся изображений и блок приоритета цветового кодирования. Это устройство не позволяет осуществлять поворот цифробуквенной информации без доработки и значительных аппаратурных затрат.

Наиболее близким к предлагаемому является устройство поворота изображения на экране телевизионного приемника, содержащее два регистра, четыре ПЗУ, блок мультиплексоров с памятью, содержащий три мультиплексора, три сумматора, блок коррекции, содержащий два мультиплексора, два накапливающих сумматора и схему коррекции, блок формирования дискретных приращений, знаков и квадранта, состоящий из схемы выработки знаков и квадранта и формирователя дискретных приращений, преобразователь, ОЗУ и схему управления, первый выход которой подключен к первым входам первого и второго сумматоров, выходы которых соединены с входами преобразователя, подключенного к первому входу ОЗУ/первый выход которого является выходом устройства, второй выход подключен к девятому входу схемы управления, второй вход соединен с третьим выходом схемы управления, а к третьим входам ОЗУ и блока

коррекции подключен шестой выход схемы управления, второй выход которой соединен с первым входом первого ПЗУ итретьим входом блока мультиплексоров, пятый выход через счетчик подключен к третьему ПЗУ, первый выход которого соединен с шестым входом схемы управления, седьмой выход которой подключен к третьему входу блока формирования дискретных приращений, знаков и квадранта, первый вход которого, а также второй вход блока коррекции подключены к выходу третьего сумматора, второй вход блока формирования дискретных приращений, знаков и квадранта, а также первый вход четвертого сумматора и третий вход треть.го сумматора соединены с выходом второго регистра, пятый вход соединен с выходом третьего ПЗУ, четвертый вход - с вторым выходом блока коррекции, первый вход которого подключен к выходу четвертого ПЗУ, первый выход соединен с седьмым входом схемы управления, а четвертый вход подключен к первому выходу блока формирования дискретных приращений, знаков и квадранта, четвертый выход которого соединен с восьмым входом схемы управления, а второй и третий выходы подключены ко вторым входам первого и второго сумматоров соответственно, третьи входы которых, г также второй и третий входы схемы управления и вторые входы первого и второго регистров являются внешними входами устройства, а первый вход схемы управления, явпяющийся также внешним входом устройства, соединен с четвертым входом блока мультиплексоров, выход которого подключен к первому входу второго ПЗУ и вторым входам третьего и четвертого сумматоров, а второй вход блока мультиплексоров подключен к второму выходу первого ПЗУ, первый выход которого является выходом устройства, а второй вход соединэн с выходом первого регистра, первый вход которого, а также первые входы блока мультиплексоров, второго регистра, пе звого и второго сумматоров являются внешними входами устройства.

Недостатком известного устройства является ограниченность функциональных возможностей и значительные аппаратные затраты. Устройство позволяет отображать на экране телевизионного индикатора информацию, заданную только в векторной форме. В настоящее время требуется отображать кривые в орого порядка (окружности, эллипсы, дуги;, представленные в виде аппроксимирующих отрезков, заданных приращейиями по осям X и V. Кроме того, в известном устройстве суммирование углов

организовано табличным способом с использованием ПЗУ и интерполятор, обеспе- чивающий разложение векторов на составляющие их точки, также построен на

ПЗУ. Если минимальный угол поворота равен одному градусу, а суммирование производится только в первом квадранте, т.е. углы заданы семиразрядным кодом, то на табличный сумматор поступает четырнздцатираз0 рядный адрес Если организовать табличный сумматор на микросхемах серии 556 РТ7, то потребуется шесть корпусов. При построении сумматора обычным путем потребуется два корп/са. Кроме того, для

5 организации интерполятора векторов, адрес которого формируется из семиразрядного кода угла, четырехразрядного, например, кода длины вектора и трех разрядов счетчика интерполятора требуется во0 семь корпусов ПЗУ серии 556 РТ7. При увеличении разрядности длины вектора количество корпусов ПЗУ резко возрастает.

изобретения является расширение области применения.

5 Указанная цель достигается тем, что в устройство поворота изображения на экране телевизионного приемника, содержащее два регистра, два сумматора, четыре блока постоянной памяти, слетчик, блокоператив0 ной памяти, преобразователь координат, блок мультиплексоров, блок управления, блок формирования угла и квадранта, блок формирования дискретных приращений, знаков и квадранта, причем информацион5 ный вход устройства подключен к первым информационным входам блока мультиплексоров и первого, второго сумматора и к информационным входам первого и второго регистров, к управляющим входам которых

0 подключены соответственно вход разрешения записи кода симпола или отрезка и вход записи кода угла поюрота устройства, входы записи кода координат X и Y соединены соответственно с пеовыми управляющими

5 входами первого и вт jporo сумматоров, выходы которых подключены к входам преобразователя координат, выход которого подключен к адресному входу блока оперативной памяти, к первому и второму управ0 ляющим входам которого подключены соответственно первый и второй выходы блока управления, третий выход которого подключен к вторым управляющим входам первого и второго сумматоров, вторые информационные в:;оды которых подключены

5 соответственно к первому и второму выходам блока формирования дискретных приращений, знаков и квадранта, третий и четвертый выходы которого подключены соответственно к первому входу блока коррекции и к первому входу блока управления, второй, третий и четвертый входы которого подключены соответственно к входам признака символ, запуска и тактовой частоты устройства, выход первого регистра соеди- нен с адресным входом первого блока постоянной памяти, управляющий вход которого соединен с первым управляющим входом блока мультиплексоров и с четвертым выходом блока управления, пятый и шестой выходы которого подключены соответственно к счетному входу счетчика и к первому входу блока формирования дискретных приращений, знаков и квадранета, второй вход которого соединен с выходом второго регистра и с первым входом блока формирования угла и квадранта, второй вход которого соединен с выходом блока мультиплексоров, второй управляющий вход которого соединен с входом признака Символ устройства, а второй информационный - с первым выходом первого блока постоянной памяти, второй выход которого соединен с управляющим выходом устройства, адресный вход второго блока постоян- ной памяти подключен к выходу блока мультиплексоров, второй выход которого подключен к третьему входу блока формирования дискретных приращений, знаков и квадранта и к второму входу блока коррек- ции, третий и четвертый входы которого подключены соответственно к второму выходу блока управления, и к выходу третьего блока постоянной памяти, адресный вход которого соединен с первым выходом блока формирования угла и квадранта и вторым адресным входом второго блока постоянной памяти, первый и второй выходы блока коррекции подключены соответственно к пятому входу блока управления и к четв ер- тому входу блока формирования дискретных приращений, знаков и квадранта, пятый вход которого подключен к первому выходу четвертого блока постоянной памяти, второй выход которого соединен с шее- тым входом блока управления, седьмой вход которого соединен с первым выходом блока оперативной памяти, второй выход которого подключен к информационному выходу устройства, выход счетчика соеди- нен с входом младших разрядов адреса четвертого блока постоянной памяти, введены блок переключения режимов, причем восьмой, девятый и десятый входы блока управления соединены соответственно с входом признака вектора и входом признака приращений устройства и с первым выходом блока переключения режимов, первый, второй и четвертый входы которого соединены соответственно с входом признака Символ

устройства, с первым выходом блока оперативной памяти, со вторым и седьмым выходами блока управления, второй выход блока переключения режимов соединен с другим управляющим входом первого регистра и с управляющими входами третьего и второго блоков постоянной памяти, выход которого подключен к входам старших разрядов адреса четвертого блока постоянной памяти и объединен с адресным входом первого блока постоянной памяти.

Введение указанных блоков и связей позволяет расширить область применения устройства за счет того, что второе ПЗУ стало выполнять функции преобразования векторов в приращении по осям X и Y, а третье ПЗУ стало выполнять функции интерполятора приращений, что позволило принимать и обрабатывать кроме векторной информации информацию, представленную в приращениях по осям X и Y. Кроме того, использование второго ПЗУ для преобразования векторов в приращения и третьего ПЗУ для интерполятора приращений, а также замена табличного сумматора обычным сумматором с введением анализатора угла позволяет значительно сократить аппаратурные затраты.

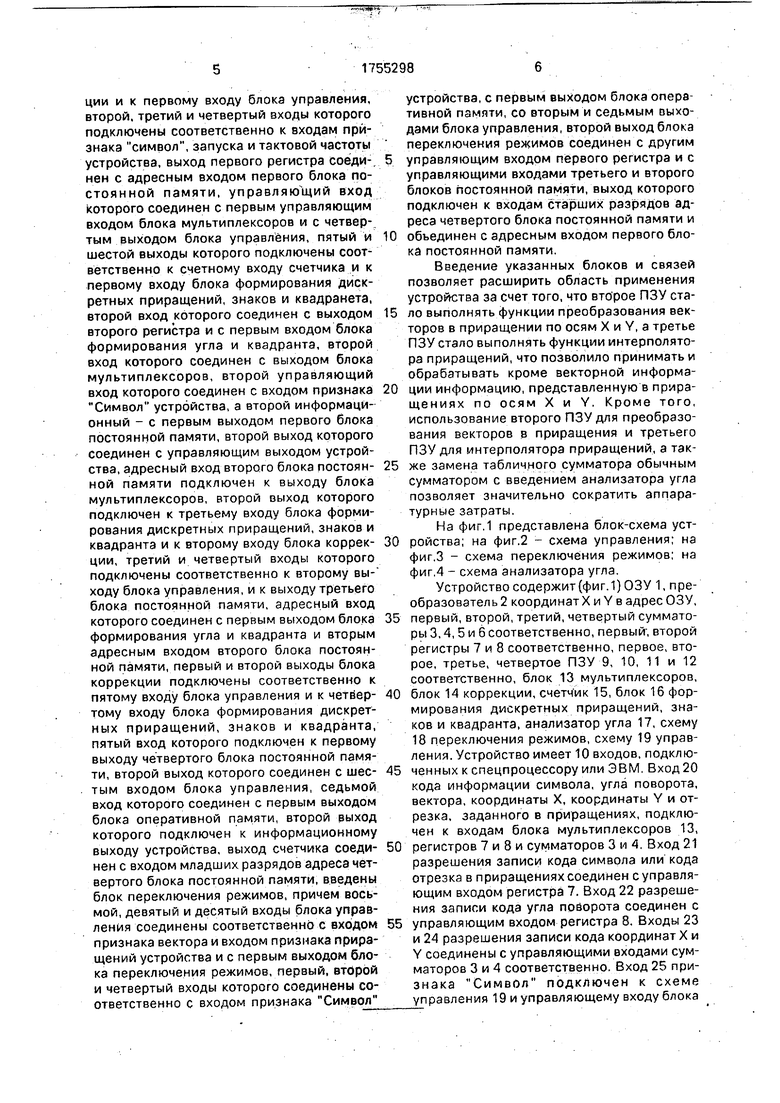

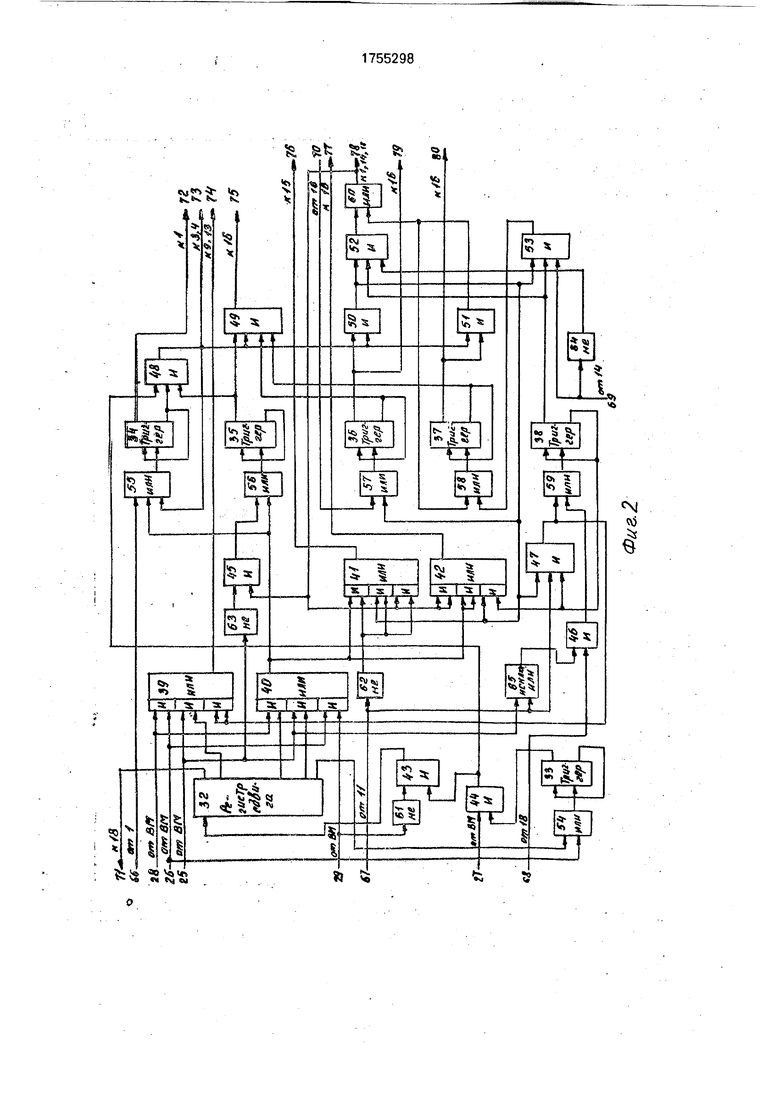

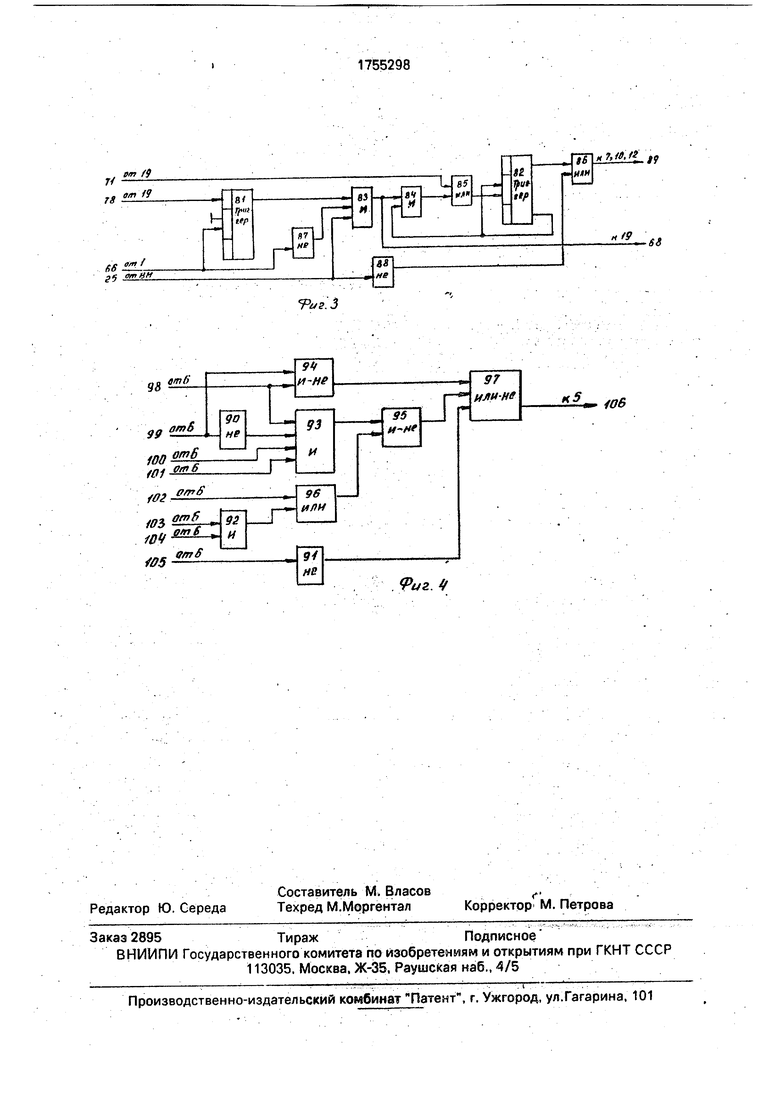

На фиг.1 представлена блок-схема устройства; на фиг.2 - схема управления; на фиг.З - схема переключения режимов; на фиг,4 - схема анализатора угла.

Устройство содержит (фиг.1) ОЗУ 1, преобразователь 2 координат X и Y в адрес ОЗУ, первый, второй, третий, четвертый сумматоры 3,4,5 и 6 соответственно, первый, второй регистры 7 и 8 соответственно, первое, второе, третье, четвертое ПЗУ 9, 10, 11 и 12 соответственно, блок 13 мультиплексоров, блок 14 коррекции, счетчик 15, блок 16 формирования дискретных приращений, знаков и квадранта, анализатор угла 17, схему 18 переключения режимов, схему 19 управления. Устройство имеет 10 входов, подключенных к спецпроцессору или ЭВМ. Вход 20 кода информации символа, угла поворота, вектора, координаты X, координаты Y и отрезка, заданного в приращениях, подключен к входам блока мультиплексоров 13, регистров 7 и 8 и сумматоров 3 и 4. Вход 21 разрешения записи кода символа или кода отрезка в приращениях соединен с управляющим входом регистра 7. Вход 22 разрешения записи кода угла поворота соединен с управляющим входом регистра 8. Входы 23 и 24 разрешения записи кода координат X и Y соединены с управляющими входами сумматоров 3 и 4 соответственно. Вход 25 признака Символ подключен к схеме управления 19 и управляющему входу блока

мультиплексоров 13, а также к входу схемы переключения режимов 18, Вход 26 запуска схемы, вход 27 тактовой частоты, вход 28 признака графика в векторной форме, вход 29 признака графика в приращениях подключены к схеме управления 19. Выходами устройства является зыход 30 ОЗУ 1, подключенный к входу телевизионного индикатора, и управляющий выход 31, подключенный к процессору.

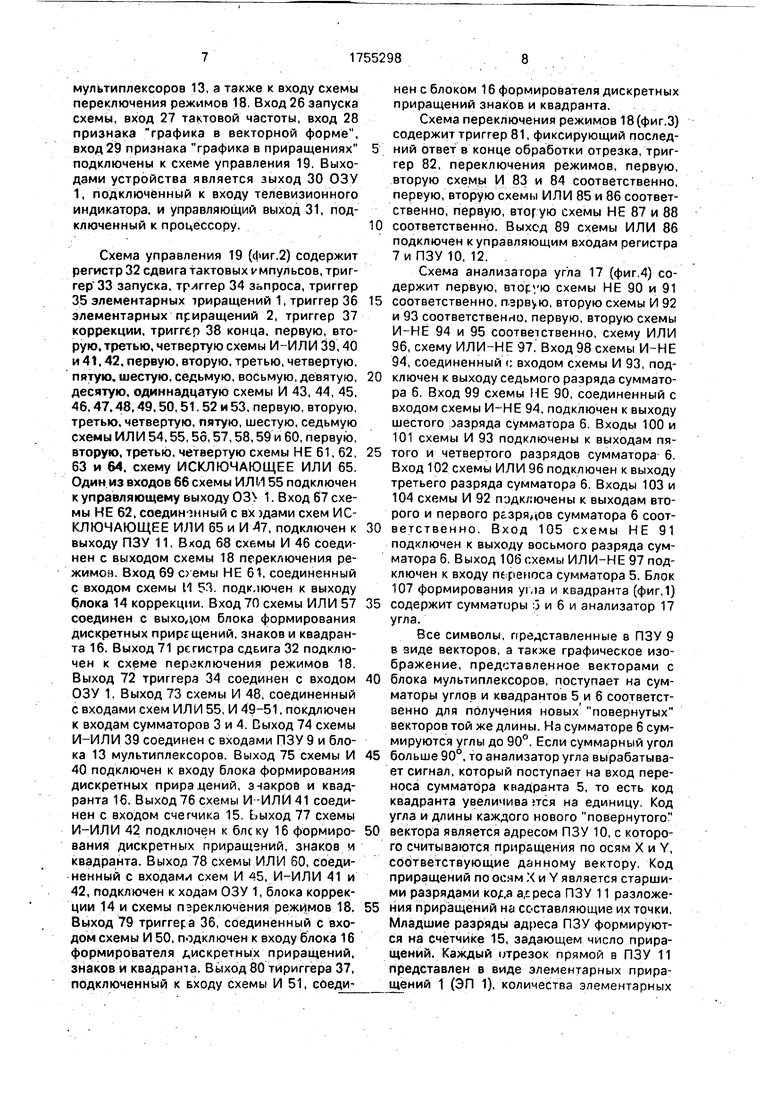

Схема управления 19 (фиг.2) содержит регистр 32 сдвига тактовых импульсов, триггер 33 запуска, триггер 34 запроса, триггер 35 элементарных триращений 1, триггер 36 элементарных приращений 2, триггер 37 коррекции, триггер 38 конца, первую, вторую, третью, четвертую схемы И-ИЛИ 39,40 и 41,42. первую, вторую, третью, четвертую, пятую, шестую, седьмую, восьмую, девятую, десятую, одиннадцатую схемы И 43, 44, 45, 46,47,48,49.50,51,52 и 53, первую, вторую, третью, четвертую, пятую, шестую, седьмую схемы ИЛИ 54,55,56,57,58,59 и 60, первую, вторую, третью, четвертую схемы НЕ 61, 62, 63 и 64. схему ИСКЛЮЧАЮЩЕЕ ИЛИ 65. Один из входов 66 схемы ИЛИ 55 подключен к управляющему выходу 03 1. Вход 67 схемы НЕ 62, соединенный с вх дами схем ИСКЛЮЧАЮЩЕЕ ИЛИ 65 и И 47, подключен к выходу ПЗУ 11. Вход 68 схемы И 46 соединен с выходом схемы 18 переключения режимов. Вход 69 оемы НЕ 61, соединенный с входом схемы И 53. подключен к выходу блока 14 коррекции. Вход 70 схемы ИЛИ 57 соединен с выходом блока формирования дискретных приргщений, знаков и квадранта 16. Выход 71 регистра сдьига 32 подключен к схеме переключения режимов 18. Выход 72 триггера 34 соединен с входом ОЗУ 1. Выход 73 схемы И 48, соединенный с входами схем ИЛИ 55, И 49-51, покдлючен к входам сумматоров 3 и 4. Выход 74 схемы И-ИЛИ 39 соединен с входами ПЗУ 9 и блока 13 мультиплексоров. Выход 75 схемы И 40 подключен к входу блока формирования дискретных прирадений, з чакрой и квадранта 16. Выход 76 схемы И -ИЛИ 41 соединен с входом счегчика 15. Ьыход 77 схемы И-ИЛИ 42 подключен к блску 16 формирования дискретных приращений, знаков и квадранта. Выход 78 схемы ИЛИ 60, соединенный с входами схем И Л5, И-ИЛИ 41 и 42, подключен к ходам ОЗУ 1, блока коррекции 14 и схемы пэреключения режимов 18. Выход 79 триггера 36, соединенный с входом схемы И 50, подключен к входу блока 16 формирователя дискретных приращений, знаков и квадранта. Выход 80 тириггера 37, подключенный к входу схемы И 51, соединен с блоком 16 формирователя дискретных приращений знаков и квадранта.

Схема переключения режимов 18(фиг.З) содержит триггер 81, фиксирующий последний ответ в конце обработки отрезка, триггер 82, переключения режимов, первую, вторую схемы И 83 и 84 соответственно, первую, вторую схемы ИЛИ 85 и 86 соответственно, первую, втогую схемы НЕ 87 и 88

0 соответственно. Выход 89 схемы ИЛИ 86 подключен к управляющим входам регистра 7 и ПЗУ 10, 12.

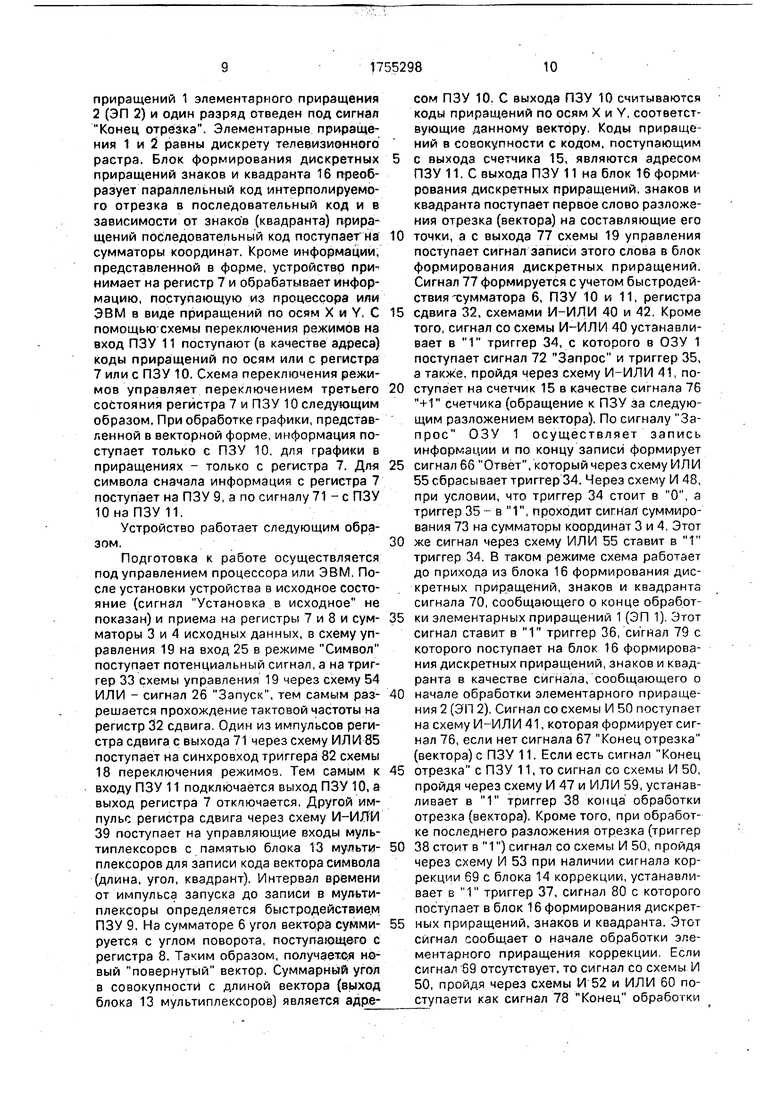

Схема анализатора угла 17 (фиг.4) содержит первую, вторую схемы НЕ 90 и 91

5 соответственно, п.эрвую, вторую схемы И 92 и 93 соответственно, первую, вторую схемы И-НЕ 94 и 95 соответственно, схему ИЛИ 96, схему ИЛИ-НЕ 97, Вход 98 схемы И-НЕ 94, соединенный с входом схемы И 93, под0 ключей к выходу седьмого разряда сумматора 6. Вход 99 схемы НЕ 90, соединенный с входом схемы И-НЕ 94, подключен к выходу шестого разряда сумматора 6. Входы 100 и 101 схемы И 93 подключены к выходам пя5 того и четвертого разрядов сумматора 6. Вход 102 схемы ИЛИ 96 подключен к выходу третьего разряда сумматора 6. Входы 103 и 104 схемы И 92 подключены к выходам второго и первого рг.зря,ов сумматора 6 соот0 ветственно. Вход 105 схемы НЕ 91 подключен к выходу восьмого разряда сумматора 6. Выход 106 схемы ИЛИ-НЕ 97 подключен к входу переноса сумматора 5. Блок 107 формирования уыа и квадранта (фиг,1)

5 содержит сумматоры :5 и 6 и анализатор 17 угла.

Все символы, представленные в ПЗУ 9 в зиде векторов, а также графическое изображение, представленное векторами с

0 блока мультиплексоров, поступает на сумматоры углов и квадрантов 5 и 6 соответственно для получения новых повернутых векторов той же длины. На сумматоре 6 суммируются углы до 90°. Если суммарный угол

5 больше 90°, то анализатор угла вырабатывает сигнал, который поступает на вход переноса сумматора квадранта 5, то есть код квадранта увеличива ггся на единицу. Код угла и длины каждого нового повернутого

0 вектора является адресом ПЗУ 10, с которого считываются приращения по осям X и Y, соответствующие данному вектору. Код приращений по осям X и Y является старшими разрядами кода адреса ПЗУ 11 разложе5 ния приращений на составляющие их точки. Младшие разряды адреса ПЗУ формируются на счетчике 15, задающем число приращений. Каждый отрезок прямой в ПЗУ 11 представлен в виде элементарных приращений 1 (ЭП 1), количества элементарных

приращений 1 элементарного приращения 2 (ЭП 2) и один разряд отведен под сигнал Конец отрезка. Элементарные приращения 1 и 2 равны дискрету телевизионного растра. Блок формирования дискретных приращений знаков и квадранта 16 преобразует параллельный код интерполируемого отрезка в последовательный код и в зависимости от знаков (квадранта) приращений последовательный код поступает на сумматоры координат. Кроме информации, представленной в форме, устройство принимает на регистр 7 и обрабатывает информацию, поступающую из процессора или ЭВМ в виде приращений по осям X и Y, С помощью схемы переключения режимов на вход ПЗУ 11 поступают (в качестве адреса) коды приращений по осям или с регистра 7 или с ПЗУ 10. Схема переключения режимов управляет переключением третьего состояния регистра 7 и ПЗУ 10 следующим образом. При обработке графики, представленной в векторной форме, информация поступает только с ПЗУ 10, для графики в приращениях - только с регистра 7. Для символа сначала информация с регистра 7 поступает на ПЗУ 9, а по сигналу 71 - с ПЗУ Юна ПЗУ 11.

Устройство работает следующим образом,

Подготовка к работе осуществляется под управлением процессора или ЭВМ. После установки устройства в исходное состояние (сигнал Установка в исходное не показан) и приема на регистры 7 и 8 и сумматоры 3 и 4 исходных данных, в схему управления 19 на вход 25 в режиме Символ поступает потенциальный сигнал, а на триггер 33 схемы управления 19 через схему 54 ИЛИ - сигнал 26 Запуск, тем самым разрешается прохождение тактовой частоты на регистр 32 сдвига. Один из импульсов регистра сдвига с выхода 71 через схему ИЛИ 85 поступает на синхровход триггера 82 схемы 18 переключения режимов. Тем самым к входу ПЗУ 11 подключается выход ПЗУ 10, а выход регистра 7 откпючается. Другой импульс регистра сдвига через схему И-ИЛИ 39 поступает на управляющие входы мультиплексоров с памятью блока 13 мультиплексоров для записи кода вектора символа (длина, угол, квадрант). Интервал времени от импульса запуска до записи в мультиплексоры определяется быстродействием ПЗУ 9. На сумматоре 6 угол вектора суммируется с углом поворота, поступающего с регистра 8. Таким образом, получается новый повернутый вектор. Суммарный угол в совокупности с длиной вектора (выход блока 13 мультиплексоров) являетсй адресом ПЗУ 10, С выхода ПЗУ 10 считываются коды приращений по осям X и Y, соответствующие данному вектору. Коды приращений в совокупности с кодом, поступающим с выхода счетчика 15, являются адресом ПЗУ 11. С выхода ПЗУ 11 на блок Сформирования дискретных приращений, знаков и квадранта поступает первое слово разложения отрезка (вектора) на составляющие его

0 точки, а с выхода 77 схемы 19 управления поступает сигнал записи этого слова в блок формирования дискретных приращений. Сигнал 77 формируется с учетом быстродействия-сумматора 6, ПЗУ 10 и 11, регистра

5 сдвига 32, схемами И-ИЛИ 40 и 42. Кроме того, сигнал со схемы И-ИЛИ 40 устанавливает в 1 триггер 34, с которого в ОЗУ 1 поступает сигнал 72 Запрос и триггер 35, а также, пройдя через схему И-ИЛИ 41, по0 ступает на счетчик 15 в качестве сигнала 76 -Н счетчика (обращение к ПЗУ за следующим разложением вектора). По сигналу Запрос ОЗУ 1 осуществляет запись информации и по концу записи формирует

5 сигнал 66 Ответ, который через схему ИЛИ 55 сбрасывает триггер 34. Через схему И 48, при условии, что триггер 34 стоит в О, а триггер 35 - в 1, проходит сигнал суммирования 73 на сумматоры координат 3 и 4 Этот

0 же сигнал через схему ИЛИ 55 ставит в 1 триггер 34. В таком режиме схема работает до прихода из блока 16 формирования дискретных приращений, знаков и квадранта сигнала 70, сообщающего о конце обработ5 ки элементарных приращений 1 (ЭП 1) Этот сигнал ставит в 1 триггер 36, сигнал 79 с которого поступает на блок 16 формирования дискретных приращений, знаков и квадранта в качестве сигнала, сообщающего о

0 начале обработки элементарного приращения 2 (ЭП 2). Сигнал со схемы И 50 поступает на схему И-ИЛИ 41, которая формирует сигнал 76, если нет сигнала 67 Конец отрезка (вектора) с ПЗУ 11. Если есть сигнал Конец

5 отрезка с ПЗУ 11, то сигнал со схемы И 50, пройдя через схему И 47 и ИЛИ 59, устанавливает в 1 триггер 38 конца обработки отрезка (вектора). Кроме того, при обработке последнего разложения отрезка (триггер

0 38 стоит в 1) сигнал со схемы И 50, пройдя через схему И 53 при наличии сигнала коррекции 69 с блока 14 коррекции,устанавливает в 1 триггер 37, сигнал 80 с которого поступает в блок 16 формирования дискрет5 ных приращений, знаков и квадранта. Этот сигнал сообщает о начале обработки элементарного приращения коррекции Если сигнал 69 отсутствует, то сигнал со схемы И 50, пройдя через схемы И 52 и ИЛИ 60 по- ступаети как сигнал 78 Конец обработки

последнего элементарного приращения в блок 14 коррекции, в схему 18 перерключе- ния режимов и в ОЗУ 1. Этот сигнал устанав- ливает в 1 триггер 81 схемы 18 переключения режимов. Тем самым фиксируется, что в ОЗУ 1 записывается последнее элементарное разложение отрезка (вектора). Кроме того, сигнал со схемы 60 ИЛИ, пройдя через схемы И-ИЛИ 42 и 41, поступает в блок формирования дискретных приращений, знаков и квадранта для записи считанного с ПЗУ 11 первого разложения следующего отрезка (вектора) (сигнал 77) и задает адрес второго разложения (сигнал 76). Если в конце обработки отрезка вырабатывается сигнал 69 коррекции, то сигналом Конец отрезка является сигнал, поступающий на вход схемы ИЛИ 60 с выхода схемы И 51. При обработке последнего вектора символа с ПЗУ 9 в процессор поступает сигнал 31 Конец символа. По этому сигналу процессор снимает признак символа с входа 25, При этом сигнал Конец отрезка (вектора) со схемы ИЛИ 60, пройдя через схемы И 45 и ИЛИ 56, сбрасывает триггер 35, а сигнал 66 Ответ, пройдя через схему НЕ 87 и И 83 схемы 18 переключения режимов (сигнал 68), сбрасывает триггер 82 переключения режимов в О, а также поступает в схему 19 управления как сигнал Конец работы, который через схему И 46 и ИЛИ 59 ставит в О триггер 38 конца. Работа схемы прекращается до следующего запуска.

Если на вход 28 из процессора поступает сигнал Графика в векторной форме, то сигнал запуска 26, пройдя через схему И- ИЛИ 39, осуществляет прием информации в мультиплексоры с памятью блока 13 мультиплексоров. Далее вектор обрабатывается как последний вектор символа.

Если на вход 29 из процессора поступает сигнал Графика в приращениях, то сигнал 26 Запуск, пройдя через схему И-ИЛИ 40 и ИЛИ 56, ставит в 1 триггер 35. При этом регистр сдвига 32 не запускается, так как с помощью схемы НЕ 61 запрещается поступление тактовой частоты. Далее схема работает аналогично.

Формула изобретения Устройство поворота изображения на экране телевизионного приемника, содержащее даа регистра, два сумматора, четыре блока постоянной памяти, счетчик, блок оперативной памяти, преобразователь координат, блок мультиплексоров, блок управ- ления, блок формирования угла и квадранта, блок коррекции, блок формирования дискретных приращений, знаков ji

квадранта, причем информационный вход устройства подключен к первым информационным входам блока мультиплексоров и первого, второго сумматора и к информационным входам первого и второго регистров, к управляющим входам которых подключены соответственно вход разрешения записи кода символа или кода отрезка и вход записи кода угла поворота устройства, входы

0 записи кода координат X и Y соединены соответственно с первыми управляющими входами первого и второго сумматоров, выходы которых подключены к входам преобразователя координат, выход которого

5 подключен к адресному входу блока оперативной памяти, к первому и второму управляющим входам которого подключены соответственно первый и второй выходы блока управления, третий выход которого

0 подключен к вторым управляющим входам первого и второго сумматоров, вторые информационные входы которых подключены соответственно к первому и второму выходам блока формирования дискретных при5 ращений, знаков и квадранта, третий и четвертый выходы которого подключены соответственно к первому входу блока коррекции и к первому входу блока управления, второй, третий и четвертый входы которого

0 подключены соответственно к входам признака Символ, запуска и тактовой частоты устройства, выход первого регистра соединен с адресным входом первого блока постоянной памяти, управляющий вход

5 которого соединен с первым управляющим входом блока мультиплексоров и с четвертым выходом блока управления, пятый и шестой выходы которого подключены соответственно к счетному входу счетчика и

0 к первому входу блока формирования дискретных приращений, знаков и квадранта, второй вход которого соединен с выходом второго регистра и с первым входом блока формирования угла и квадранта, второй

5 вход которого соединен с выходом блока мультиплексоров, второй управляющий вход которого соединен-с входом признака Символ устройства, а второй информационный - с первым выходом первого блока

0 постоянной памяти, второй выход которого соединен с управляющим выходом устройства, первый и второй адресные входы второго блока постоянной памяти подключены к выходу блока мультиплексоров и к перво5 му выходу блока формирования угла и квадранта, второй выход которого подключен к третьему входу блока формирования дискретных приращений, знаков и квадранта и к второму входу блока коррекции, третий и четвертый входы которого подключены соответственно к второму выходу блока управления и к выходу третьего блока постоянной памяти, адресный вход которого соединен с первым выходом блока формирования угла и квадранта, первый и второй выходы блока коррекции подключены соответственно к пятому входу блока управления и к четвертому входу блока формирования дискретных приращений знаков и квадранта, пятый вход которого подключен к первому выходу четвертого блока постоянной памяти, второй выход которого соединен с шестым входом блока управления, седьмой вход которого соединен с первым выходом блока оперативной памяти, второй выход кото- рого подключен к информационному выходу устройства, выход счетчика соединен с входом младших разрядов адреса четвертого блока постоянной памяти, отличающееся тем, что, с целью расширения области применения за счет обработки информации, заданной в форме приращений, оно дополнительно содержит блок переключения режимов, причем восьмой, девятый и десятый входы блока управления соединены соответственно с входом признака вектора, входом признака приращений устройства и с первым выходом блока переключения режимов, первый, второй, третий и четвертый входы которого соединены соответственно с входом признака Символ устройства, с первым выходом блока оперативной памяти, с вторым и седьмым выходами блока управления, второй выход блока переключения режимов соединен с другим управляющим входом первого регистра и с управляющими входами третьего и второго блоков постоянной памяти, выход которого подключен к входам старших разрядов адреса четвертого блока постоянной памяти и объединен с адресным входом первого блока постоянной памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство поворота изображения на экране телевизионного приемника | 1987 |

|

SU1424028A1 |

| Устройство для отображения графической информации на газоразрядной индикаторной панели | 1982 |

|

SU1108488A1 |

| Устройство для формирования окружностей | 1984 |

|

SU1221678A2 |

| Устройство для формирования окружностей | 1981 |

|

SU991486A1 |

| Цифровой линейный интерполятор | 1990 |

|

SU1805449A1 |

| Линейный интерполятор | 1987 |

|

SU1418751A1 |

| Устройство для формирования окружностей | 1983 |

|

SU1096688A2 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Линейный интерполятор | 1987 |

|

SU1439532A1 |

| Калибратор сигналов, нормированных по коэффициенту гармоник | 1988 |

|

SU1555677A1 |

Изобретение относится к устройствам для обработки данных и может быть использовано в устройствах вывода информации ЦВМ на экран телевизионного приемника. Устройство содержит ОЗУ, четыре сумматора, преобразователь координат в адрес ОЗУ, два регистра, четыре ПЗУ, блок мультиплексоров, блок коррекции, счетчик, блок формирования дискретных приращений, знаков и квадранта, анализатор угла, схему переключения режимов, схему управления. Перечисленные элементы и наличие функциональных связей между ними позволяют расширить область применения устройства. 4 ил. w W Ё

т f ffmS

И

91 не

Фиг./

| Устройство для отображения информации на экране телевизионного индикатора | 1978 |

|

SU723624A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство поворота изображения на экране телевизионного приемника | 1987 |

|

SU1424028A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-08-15—Публикация

1989-11-09—Подача